Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

E·XF

| Product Status             | Active                                                                      |

|----------------------------|-----------------------------------------------------------------------------|

| Core Processor             | PIC                                                                         |

| Core Size                  | 8-Bit                                                                       |

| Speed                      | 40MHz                                                                       |

| Connectivity               | I <sup>2</sup> C, SPI, UART/USART                                           |

| Peripherals                | Brown-out Detect/Reset, HLVD, POR, PWM, WDT                                 |

| Number of I/O              | 25                                                                          |

| Program Memory Size        | 8KB (4K x 16)                                                               |

| Program Memory Type        | FLASH                                                                       |

| EEPROM Size                | 256 x 8                                                                     |

| RAM Size                   | 512 x 8                                                                     |

| Voltage - Supply (Vcc/Vdd) | 2V ~ 5.5V                                                                   |

| Data Converters            | A/D 10x10b                                                                  |

| Oscillator Type            | Internal                                                                    |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                           |

| Mounting Type              | Surface Mount                                                               |

| Package / Case             | 28-VQFN Exposed Pad                                                         |

| Supplier Device Package    | 28-QFN (6x6)                                                                |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic18lf2321t-i-ml |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

## 10.2 PIR Registers

The PIR registers contain the individual flag bits for the peripheral interrupts. Due to the number of peripheral interrupt sources, there are two Peripheral Interrupt Request (Flag) registers (PIR1 and PIR2).

- Note 1: Interrupt flag bits are set when an interrupt condition occurs, regardless of the state of its corresponding enable bit or the Global Interrupt Enable bit, GIE (INTCON<7>).

- 2: User software should ensure the appropriate interrupt flag bits are cleared prior to enabling an interrupt and after servicing that interrupt.

#### REGISTER 10-4: PIR1: PERIPHERAL INTERRUPT REQUEST (FLAG) REGISTER 1

| R/W-0                | R/W-0 | R-0  | R-0  | R/W-0 | R/W-0  | R/W-0  | R/W-0  |

|----------------------|-------|------|------|-------|--------|--------|--------|

| PSPIF <sup>(1)</sup> | ADIF  | RCIF | TXIF | SSPIF | CCP1IF | TMR2IF | TMR1IF |

| bit 7                |       |      |      |       |        |        | bit 0  |

|       | bit /                                                                                                                                                                                                                                                                                                                                                                 | DILU |

|-------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------|

| bit 7 | <ul> <li><b>PSPIF:</b> Parallel Slave Port Read/Write Interrupt Flag bit<sup>(1)</sup></li> <li>1 = A read or a write operation has taken place (must be cleared in software)</li> <li>0 = No read or write has occurred</li> </ul>                                                                                                                                   |      |

|       | Note 1: This bit is unimplemented on 28-pin devices and will read as '0'.                                                                                                                                                                                                                                                                                             |      |

| bit 6 | <ul> <li>ADIF: A/D Converter Interrupt Flag bit</li> <li>1 = An A/D conversion completed (must be cleared in software)</li> <li>0 = The A/D conversion is not complete</li> </ul>                                                                                                                                                                                     |      |

| bit 5 | <b>RCIF:</b> EUSART Receive Interrupt Flag bit<br>1 = The EUSART receive buffer, RCREG, is full (cleared when RCREG is read)<br>0 = The EUSART receive buffer is empty                                                                                                                                                                                                |      |

| bit 4 | <b>TXIF:</b> EUSART Transmit Interrupt Flag bit<br>1 = The EUSART transmit buffer, TXREG, is empty (cleared when TXREG is written)<br>0 = The EUSART transmit buffer is full                                                                                                                                                                                          |      |

| bit 3 | <ul> <li>SSPIF: Master Synchronous Serial Port Interrupt Flag bit</li> <li>1 = The transmission/reception is complete (must be cleared in software)</li> <li>0 = Waiting to transmit/receive</li> </ul>                                                                                                                                                               |      |

| bit 2 | CCP1IF: CCP1 Interrupt Flag bit<br><u>Capture mode:</u><br>1 = A TMR1 register capture occurred (must be cleared in software)<br>0 = No TMR1 register capture occurred<br><u>Compare mode:</u><br>1 = A TMR1 register compare match occurred (must be cleared in software)<br>0 = No TMR1 register compare match occurred<br><u>PWM mode:</u><br>Unused in this mode. |      |

| bit 1 | <ul> <li>TMR2IF: TMR2 to PR2 Match Interrupt Flag bit</li> <li>1 = TMR2 to PR2 match occurred (must be cleared in software)</li> <li>0 = No TMR2 to PR2 match occurred</li> </ul>                                                                                                                                                                                     |      |

| bit 0 | <ul> <li>TMR1IF: TMR1 Overflow Interrupt Flag bit</li> <li>1 = TMR1 register overflowed (must be cleared in software)</li> <li>0 = TMR1 register did not overflow</li> </ul>                                                                                                                                                                                          |      |

|       | Legend:                                                                                                                                                                                                                                                                                                                                                               |      |

| Legend:           |                  |                        |                    |

|-------------------|------------------|------------------------|--------------------|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, | read as '0'        |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared   | x = Bit is unknown |

NOTES:

# 17.0 ENHANCED CAPTURE/ COMPARE/PWM (ECCP) MODULE

| Note: | The ECCP module is implemented only in |

|-------|----------------------------------------|

|       | 40/44-pin devices.                     |

In PIC18F4221/4321 devices, CCP1 is implemented as a standard CCP module with Enhanced PWM capabilities. These include the provision for 2 or 4 output channels, user-selectable polarity, dead-band control and automatic shutdown and restart. The Enhanced features are discussed in detail in **Section 17.4 "Enhanced PWM Mode"**. Capture, Compare and single-output PWM functions of the ECCP module are the same as described for the standard CCP module.

The control register for the Enhanced CCP module is shown in Register 17-1. It differs from the CCPxCON registers in PIC18F2221/2321 devices in that the two Most Significant bits are implemented to control PWM functionality.

#### **REGISTER 17-1: CCP1CON REGISTER (ECCP1 MODULE, 40/44-PIN DEVICES)**

| R/W-0 | R/W-0 | R/W-0 | R/W-0 | R/W-0  | R/W-0  | R/W-0  | R/W-0  |

|-------|-------|-------|-------|--------|--------|--------|--------|

| P1M1  | P1M0  | DC1B1 | DC1B0 | CCP1M3 | CCP1M2 | CCP1M1 | CCP1M0 |

| bit 7 |       |       |       |        |        |        | bit 0  |

#### bit 7-6 P1M<1:0>: Enhanced PWM Output Configuration bits

#### If CCP1M<3:2> = 00, 01, 10:

xx = P1A assigned as Capture/Compare input/output; P1B, P1C, P1D assigned as port pins

If CCP1M<3:2> = 11:

- 00 = Single output: P1A modulated; P1B, P1C, P1D assigned as port pins

- 01 = Full-bridge output forward: P1D modulated; P1A active; P1B, P1C inactive

- 10 = Half-bridge output: P1A, P1B modulated with dead-band control; P1C, P1D assigned as port pins

- 11 = Full-bridge output reverse: P1B modulated; P1C active; P1A, P1D inactive

- bit 5-4 **DC1B<1:0>**: PWM Duty Cycle bit 1 and bit 0

Capture mode:

Unused.

Compare mode:

#### Unused.

PWM mode:

These bits are the two LSbs of the 10-bit PWM duty cycle. The eight MSbs of the duty cycle are found in CCPR1L.

#### bit 3-0 **CCP1M<3:0>**: Enhanced CCP Mode Select bits

- 0000 = Capture/Compare/PWM off (resets ECCP module)

- 0001 = Reserved

- 0010 = Compare mode, toggle output on match

- 0011 = Capture mode

- 0100 = Capture mode, every falling edge

- 0101 = Capture mode, every rising edge

- 0110 = Capture mode, every 4th rising edge

- 0111 = Capture mode, every 16th rising edge

- 1000 = Compare mode, initialize CCP1 pin low, set output on compare match (set CCP1IF)

- 1001 = Compare mode, initialize CCP1 pin high, clear output on compare match (set CCP1IF)

- 1010 = Compare mode, generate software interrupt only, CCP1 pin reverts to I/O state

- 1011 = Compare mode, trigger special event (ECCP resets TMR1 or TMR3, sets CC1IF bit)

- 1100 = PWM mode; P1A, P1C active-high; P1B, P1D active-high

- 1101 = PWM mode; P1A, P1C active-high; P1B, P1D active-low

- 1110 = PWM mode; P1A, P1C active-low; P1B, P1D active-high

- 1111 = PWM mode; P1A, P1C active-low; P1B, P1D active-low

| Legend:           |                  |                      |                    |

|-------------------|------------------|----------------------|--------------------|

| R = Readable bit  | W = Writable bit | U = Unimplemented    | bit, read as '0'   |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared | x = Bit is unknown |

| REGISTER 19-2: | RCSTA: R                        |                                                        | TATUS AN       |                |              | TER           |              |              |

|----------------|---------------------------------|--------------------------------------------------------|----------------|----------------|--------------|---------------|--------------|--------------|

|                | R/W-0                           | R/W-0                                                  | R/W-0          | R/W-0          | R/W-0        | R-0           | R-0          | R-x          |

|                | SPEN                            | RX9                                                    | SREN           | CREN           | ADDEN        | FERR          | OERR         | RX9D         |

|                | bit 7                           |                                                        |                |                |              |               |              | bit 0        |

| bit 7          |                                 | ial Dart Enal                                          | bla bit        |                |              |               |              |              |

| bit 7          |                                 | ial Port Enal                                          |                | DV/DT and      | TV/CK pipe   | an aprial pa  | rt nina)     |              |

|                |                                 | oort disabled                                          |                |                | TX/CK pins   | as senai po   | it pins)     |              |

| bit 6          | <b>RX9:</b> 9-bit               | Receive Ena                                            | able bit       |                |              |               |              |              |

|                |                                 | <ul> <li>9-bit recept</li> <li>8-bit recept</li> </ul> |                |                |              |               |              |              |

| bit 5          | SREN: Sin                       | gle Receive                                            | Enable bit     |                |              |               |              |              |

|                | <u>Asynchron</u><br>Don't care. |                                                        |                |                |              |               |              |              |

|                | Synchrono                       | us mode – N                                            | /laster:       |                |              |               |              |              |

|                |                                 | s single rece                                          |                |                |              |               |              |              |

|                |                                 | es single rec                                          |                |                |              |               |              |              |

|                |                                 | leared after                                           | -              | complete.      |              |               |              |              |

|                | Don't care.                     | <u>us mode – S</u>                                     | <u>blave:</u>  |                |              |               |              |              |

| bit 4          |                                 | ntinuous Re                                            | ceive Enable   | e bit          |              |               |              |              |

|                | Asynchron                       |                                                        |                |                |              |               |              |              |

|                | 1 = Enable                      |                                                        |                |                |              |               |              |              |

|                | 0 = Disable                     | es receiver                                            |                |                |              |               |              |              |

|                | Synchrono                       |                                                        |                |                | ODEN         |               |              |              |

|                |                                 | s continuous<br>es continuou                           |                | til enable bit | CREN is cle  | eared (CREI   | N overrides  | SREN)        |

| bit 3          |                                 | ddress Dete                                            |                | t              |              |               |              |              |

| bit o          |                                 | ous mode 9-                                            |                |                |              |               |              |              |

|                |                                 |                                                        |                |                | upt and load | s the receiv  | e buffer whe | en RSR<8>    |

|                | 0 = Disabl                      | es address o                                           | detection, all | bytes are r    | eceived and  | ninth bit car | n be used as | s parity bit |

|                |                                 | ous mode 9-                                            | bit (RX9 = c   | ) <u>):</u>    |              |               |              |              |

|                | Don't care.                     |                                                        |                |                |              |               |              |              |

| bit 2          |                                 | ming Error b                                           |                |                |              |               |              |              |

|                | 1 = Framin<br>0 = No fran       |                                                        | be updated     | by reading     | RCREG regi   | ister and rec | eiving next  | valid byte)  |

| bit 1          | OERR: OV                        | errun Error b                                          | pit            |                |              |               |              |              |

|                |                                 | n error (can                                           | be cleared b   | by clearing b  | oit CREN)    |               |              |              |

|                | 0 = No ove                      |                                                        |                |                |              |               |              |              |

| bit 0          |                                 | bit of Receiv                                          |                |                |              |               | <b>C</b>     | _            |

|                | I his can be                    | e address/da                                           | ata bit or a p | arity bit and  | must be cal  | culated by u  | ser tirmware | 9.           |

|                | Legend:                         |                                                        |                |                |              |               |              |              |

|                | R = Reada                       | ble bit                                                | W = W          | /ritable bit   | U = Unin     | nplemented    | bit, read as | ʻ0'          |

|                | -n = Value                      |                                                        | '1' = B        | it is set      |              | s cleared     | x = Bit is u |              |

|                |                                 |                                                        | i – D          |                |              |               |              |              |

#### 20.4 Operation in Power-Managed Modes

The selection of the automatic acquisition time and A/D conversion clock is determined in part by the clock source and frequency while in a power-managed mode.

If the A/D is expected to operate while the device is in a power-managed mode, the ACQT<2:0> and ADCS<2:0> bits in ADCON2 should be updated in accordance with the clock source to be used in that mode. After entering the mode, an A/D acquisition or conversion may be started. Once started, the device should continue to be clocked by the same clock source until the conversion has been completed.

If desired, the device may be placed into the corresponding Idle mode during the conversion. If the device clock frequency is less than 1 MHz, the A/D RC clock source should be selected.

Operation in Sleep mode requires the A/D FRC clock to be selected. If bits ACQT<2:0> are set to '000' and a conversion is started, the conversion will be delayed one instruction cycle to allow execution of the SLEEP instruction and entry to Sleep mode. The IDLEN bit (OSCCON<7>) must have already been cleared prior to starting the conversion.

# 20.5 Configuring Analog Port Pins

The ADCON1, TRISA, TRISB and TRISE registers all configure the A/D port pins. The port pins needed as analog inputs must have their corresponding TRIS bits set (input). If the TRIS bit is cleared (output), the digital output level (VOH or VOL) will be converted.

The A/D operation is independent of the state of the CHS<3:0> bits and the TRIS bits.

- Note 1: When reading the Port register, all pins configured as analog input channels will read as cleared (a low level). Pins configured as digital inputs will convert as analog inputs. Analog levels on a digitally configured input will be accurately converted.

- 2: Analog levels on any pin defined as a digital input may cause the digital input buffer to consume current out of the device's specification limits.

- 3: The PBADEN bit in Configuration Register 3H configures PORTB pins to reset as analog or digital pins by controlling how the PCFG<3:0> bits in ADCON1 are reset.

## 20.6 A/D Conversions

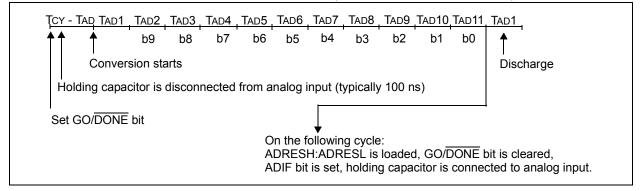

Figure 20-4 shows the operation of the A/D converter after the GO/DONE bit has been set and the ACQT<2:0> bits are cleared. A conversion is started after the following instruction to allow entry into Sleep mode before the conversion begins.

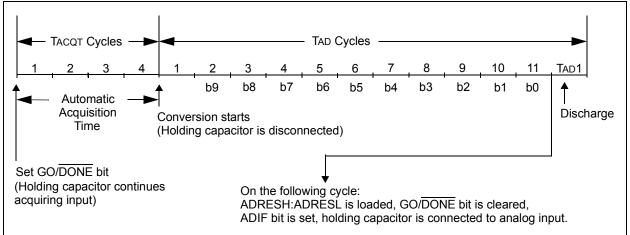

Figure 20-5 shows the operation of the A/D converter after the GO/DONE bit has been set and the ACQT<2:0> bits are set to '010' and selecting a 4 TAD acquisition time before the conversion starts.

Clearing the GO/DONE bit during a conversion will abort the current conversion. The A/D Result register pair will NOT be updated with the partially completed A/D conversion sample. This means the ADRESH:ADRESL registers will continue to contain the value of the last completed conversion (or the last value written to the ADRESH:ADRESL registers). After the A/D conversion is completed or aborted, a 2 TAD wait is required before the next acquisition can be started. After this wait, acquisition on the selected channel is automatically started.

| Note: | The GO/DONE bit should NOT be set in        |

|-------|---------------------------------------------|

|       | the same instruction that turns on the A/D. |

#### 20.7 Discharge

The discharge phase is used to initialize the value of the capacitor array. The array is discharged before every sample. This feature helps to optimize the unitygain amplifier, as the circuit always needs to charge the capacitor array, rather than charge/discharge based on previous measure values.

#### FIGURE 20-4: A/D CONVERSION TAD CYCLES (ACQT<2:0> = 000, TACQ = 0)

# FIGURE 20-5: A/D CONVERSION TAD CYCLES (ACQT<2:0> = 010, TACQ = 4 TAD)

# REGISTER 24-6: CONFIG5L: CONFIGURATION REGISTER 5 LOW (BYTE ADDRESS 300008h) U-0 U-0 U-0 U-0 R/C-1 R/C-1 — — — — — CP1 CP0 bit 7 bit 0 bit 0 bit 0 D D D D

- bit 7-2 Unimplemented: Read as '0'

- bit 1 CP1: Code Protection bit

- 1 = Block 1 not code-protected<sup>(1)</sup>

- 0 = Block 1 code-protected<sup>(1)</sup>

- bit 0 **CP0:** Code Protection bit

- 1 = Block 0 not code-protected<sup>(1)</sup>

- 0 = Block 0 code-protected<sup>(1)</sup>

| Legend:              |                    |                                     |

|----------------------|--------------------|-------------------------------------|

| R = Readable bit     | C = Clearable bit  | U = Unimplemented bit, read as '0'  |

| -n = Value when devi | ce is unprogrammed | u = Unchanged from programmed state |

#### REGISTER 24-7: CONFIG5H: CONFIGURATION REGISTER 5 HIGH (BYTE ADDRESS 300009h)

| R/C-1 | R/C-1 | U-0 | U-0 | U-0 | U-0 | U-0 | U-0   |

|-------|-------|-----|-----|-----|-----|-----|-------|

| CPD   | CPB   | _   | _   | _   | —   | _   | _     |

| bit 7 |       |     |     |     |     |     | bit 0 |

- bit 7 CPD: Data EEPROM Code Protection bit

- 1 = Data EEPROM not code-protected

- 0 = Data EEPROM code-protected

- bit 6 CPB: Boot Block Code Protection bit

- 1 = Boot block not code-protected<sup>(1)</sup>

- 0 = Boot block code-protected<sup>(1)</sup>

- bit 5-0 Unimplemented: Read as '0'

Note 1: See Figure 24-5 for variable block boundaries.

| Legend:              |                    |                                     |

|----------------------|--------------------|-------------------------------------|

| R = Readable bit     | C = Clearable bit  | U = Unimplemented bit, read as '0'  |

| -n = Value when devi | ce is unprogrammed | u = Unchanged from programmed state |

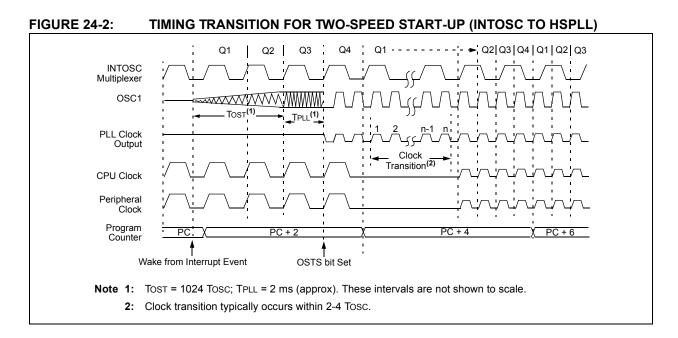

## 24.3 Two-Speed Start-up

The Two-Speed Start-up feature helps to minimize the latency period from oscillator start-up to code execution by allowing the microcontroller to use the INTOSC oscillator as a clock source until the primary clock source is available. It is enabled by setting the IESO Configuration bit.

Two-Speed Start-up should be enabled only if the primary oscillator mode is LP, XT, HS or HSPLL (crystal-based modes). Other sources do not require an OST start-up delay; for these, Two-Speed Start-up should be disabled.

When enabled, Resets and wake-ups from Sleep mode cause the device to configure itself to run from the internal oscillator block as the clock source, following the time-out of the Power-up Timer after a Power-on Reset is enabled. This allows almost immediate code execution while the primary oscillator starts and the OST is running. Once the OST times out, the device automatically switches to PRI\_RUN mode.

To use a higher clock speed on wake-up, the INTOSC or postscaler clock sources can be selected to provide a higher clock speed by setting bits, IRCF<2:0>, immediately after Reset. For wake-ups from Sleep, the INTOSC or postscaler clock sources can be selected by setting the IRCF<2:0> bits prior to entering Sleep mode.

In all other power-managed modes, Two-Speed Startup is not used. The device will be clocked by the currently selected clock source until the primary clock source becomes available. The setting of the IESO bit is ignored.

#### 24.3.1 SPECIAL CONSIDERATIONS FOR USING TWO-SPEED START-UP

While using the INTOSC oscillator in Two-Speed Startup, the device still obeys the normal command sequences for entering power-managed modes, including multiple SLEEP instructions (refer to **Section 4.1.4 "Multiple Sleep Commands"**). In practice, this means that user code can change the SCS<1:0> bit settings or issue SLEEP instructions before the OST times out. This would allow an application to briefly wake-up, perform routine "housekeeping" tasks and return to Sleep before the device starts to operate from the primary oscillator.

User code can also check if the primary clock source is currently providing the device clocking by checking the status of the OSTS bit (OSCCON<3>). If the bit is set, the primary oscillator is providing the clock. Otherwise, the internal oscillator block is providing the clock during wake-up from Reset or Sleep mode.

| BCF                                                                                                                                                                                                                                                                                                       | Bit Clear f                                                               | BN                                                     | Branch if Negative                                                                                                                                                                                                                                                                         |

|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------|--------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Syntax:                                                                                                                                                                                                                                                                                                   | BCF f, b {,a}                                                             | Syntax:                                                | BN n                                                                                                                                                                                                                                                                                       |

| Operands:                                                                                                                                                                                                                                                                                                 | $0 \le f \le 255$                                                         | Operands:                                              | $-128 \le n \le 127$                                                                                                                                                                                                                                                                       |

|                                                                                                                                                                                                                                                                                                           | 0 ≤ b ≤ 7<br>a ∈ [0,1]                                                    | Operation:                                             | If Negative bit is '1',<br>(PC) + 2 + 2n $\rightarrow$ PC                                                                                                                                                                                                                                  |

| Operation:                                                                                                                                                                                                                                                                                                | $0 \rightarrow f < b >$                                                   | Status Affected:                                       | None                                                                                                                                                                                                                                                                                       |

| Status Affected:                                                                                                                                                                                                                                                                                          | None                                                                      | Encoding:                                              | 1110 0110 nnnn nnnn                                                                                                                                                                                                                                                                        |

| Encoding:1001bbbaffffffffDescription:Bit 'b' in register 'f' is cleared.If 'a' is '0', the Access Bank is selected.If 'a' is '1', the BSR is used to select theGPR bank (default).If 'a' is '0' and the extended instructionset is enabled, this instruction operatesin Indexed Literal Offset Addressing |                                                                           | Description:                                           | If the Negative bit is '1', then the<br>program will branch.<br>The 2's complement number '2n' is<br>added to the PC. Since the PC will have<br>incremented to fetch the next<br>instruction, the new address will be<br>PC + 2 + 2n. This instruction is then a<br>two-cycle instruction. |

|                                                                                                                                                                                                                                                                                                           | mode whenever f $\leq$ 95 (5Fh). See<br>Section 25.2.3 "Byte-Oriented and | Words:                                                 | 1                                                                                                                                                                                                                                                                                          |

|                                                                                                                                                                                                                                                                                                           | Bit-Oriented Instructions in Indexed                                      | Cycles:                                                | 1(2)                                                                                                                                                                                                                                                                                       |

| Words:                                                                                                                                                                                                                                                                                                    | Literal Offset Mode" for details.                                         | Q Cycle Activity:<br>If Jump:                          |                                                                                                                                                                                                                                                                                            |

| Cycles:                                                                                                                                                                                                                                                                                                   | 1                                                                         | Q1                                                     | Q2 Q3 Q4                                                                                                                                                                                                                                                                                   |

| Q Cycle Activity:                                                                                                                                                                                                                                                                                         |                                                                           | Decode                                                 | Read literalProcessWrite to'n'DataPC                                                                                                                                                                                                                                                       |

| Q1<br>Decode                                                                                                                                                                                                                                                                                              | Q2 Q3 Q4<br>Read Process Write                                            | No<br>operation                                        | No No No<br>operation operation                                                                                                                                                                                                                                                            |

|                                                                                                                                                                                                                                                                                                           | register 'f' Data register 'f'                                            | If No Jump:                                            |                                                                                                                                                                                                                                                                                            |

| - ·                                                                                                                                                                                                                                                                                                       |                                                                           | Q1                                                     | Q2 Q3 Q4                                                                                                                                                                                                                                                                                   |

| Example:<br>Before Instruct                                                                                                                                                                                                                                                                               | BCF FLAG_REG, 7, 0                                                        | Decode                                                 | Read literalProcessNo'n'Dataoperation                                                                                                                                                                                                                                                      |

| FLAG_R                                                                                                                                                                                                                                                                                                    |                                                                           |                                                        |                                                                                                                                                                                                                                                                                            |

| After Instructio                                                                                                                                                                                                                                                                                          |                                                                           | Example:                                               | HERE BN Jump                                                                                                                                                                                                                                                                               |

| FLAG_RI                                                                                                                                                                                                                                                                                                   | EG = 47h                                                                  | Before Instruc<br>PC<br>After Instructic<br>If Negativ | = address (HERE)                                                                                                                                                                                                                                                                           |

|                                                                                                                                                                                                                                                                                                           |                                                                           | If Negativ<br>P(<br>If Negativ<br>P(                   | C = address (Jump)<br>ve = 0;                                                                                                                                                                                                                                                              |

| SUBWFB                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | Sı        | W from            | f with                   | Borrow  |             |  |  |  |  |  |

|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------|-------------------|--------------------------|---------|-------------|--|--|--|--|--|

| Syntax:                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | Sl        | JBWFB             | f {,d {,a                | }}      |             |  |  |  |  |  |

| Operands:                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | 0 ≤       | ≤ f ≤ 255         |                          |         |             |  |  |  |  |  |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |           | d ∈ [0, 1]        |                          |         |             |  |  |  |  |  |

| •                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |           | <b>a</b> ∈ [0, 1] |                          |         |             |  |  |  |  |  |

| Operation:                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | • • •     |                   | $(C) \rightarrow des$    | st      |             |  |  |  |  |  |

| Status Affected:                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | _         | OV, C, D          | 1                        |         |             |  |  |  |  |  |

| Encoding:                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |           | 0101              | 10da                     | fff     |             |  |  |  |  |  |

| Description:       0101       100a       1111       111         Description:       Subtract W and the Carry flag (borro from register 'f' (2's complement method). If 'd' is '0', the result is stored bain register 'f' (default).         If 'a' is '0', the result is stored bain register 'f' (default).         If 'a' is '0', the Access Bank is selecter of GPR bank (default).         If 'a' is '1', the BSR is used to select if GPR bank (default).         If 'a' is '0' and the extended instruction set is enabled, this instruction operation in Indexed Literal Offset Addressing mode whenever f ≤ 95 (5Fh). See         Section 25.2.3 "Byte-Oriented and Bit-Oriented Instructions in Indexed Literal Offset Mode" for details. |           |                   |                          |         |             |  |  |  |  |  |

| Words:                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | LI1<br>1  | teral Offs        | set Mode                 | " tor c | letalis.    |  |  |  |  |  |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | 1         |                   |                          |         |             |  |  |  |  |  |

| Cycles:<br>Q Cycle Activity:                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | I         |                   |                          |         |             |  |  |  |  |  |

| Q Cycle Activity.<br>Q1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |           | Q2                | Q3                       |         | Q4          |  |  |  |  |  |

| Decode                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |           | Read              | Process                  |         | Write to    |  |  |  |  |  |

| 200040                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |           | gister 'f'        | Data                     |         | destination |  |  |  |  |  |

| Example 1:                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | S         | SUBWFB            | REG, 1                   | , 0     |             |  |  |  |  |  |

| Before Instruc                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |           |                   |                          |         |             |  |  |  |  |  |

| REG<br>W                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | =         | 19h<br>0Dh        | (0001                    |         |             |  |  |  |  |  |

| С                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | =         | 1                 | (                        |         | _ /         |  |  |  |  |  |

| After Instructio<br>REG                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | n<br>=    | 0Ch               | (0000                    | 101     | 1)          |  |  |  |  |  |

| W                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | =         | 0Dh               | (0000                    |         |             |  |  |  |  |  |

| C<br>Z<br>N                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | =         | 1<br>0            |                          |         |             |  |  |  |  |  |

| N                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | =         | 0                 | ; resul                  |         | sitive      |  |  |  |  |  |

| Example 2:                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |           | SUBWFB            | REG, 0,                  | 0       |             |  |  |  |  |  |

| Before Instruc<br>REG                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | tion<br>= | 1Bh               | (0001                    | . 101   | 1)          |  |  |  |  |  |

| W                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | =         | 1Ah               | (0001                    |         |             |  |  |  |  |  |

| C<br>After Instructio                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |           | 0                 |                          |         |             |  |  |  |  |  |

| REG                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | =         | 1Bh               | (0001                    | . 101   | 1)          |  |  |  |  |  |

| W<br>C                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | =         | 00h<br>1          |                          |         |             |  |  |  |  |  |

| Z<br>N                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | =         | 1<br>0            | ; resul                  | t is ze | ro          |  |  |  |  |  |

| Example 3:                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |           | SUBWFB            | REG, 1                   | , 0     |             |  |  |  |  |  |

| Before Instruc                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |           | JODWID            | 100, 1                   | , 0     |             |  |  |  |  |  |

| REG                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | =         | 03h               | (0000                    |         |             |  |  |  |  |  |

| W<br>C                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | =         | 0Eh<br>1          | (0000                    | ) 110   | 1)          |  |  |  |  |  |

| After Instructio                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | n<br>=    | EEh               | / 1 1 1 1                | 010     | 0)          |  |  |  |  |  |

| REG                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | -         | F5h               | (1111<br>; <b>[2's c</b> |         | 0)          |  |  |  |  |  |

| W<br>C                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | =         | 0Eh<br>0          | (0000                    | ) 110   | 1)          |  |  |  |  |  |

| Z<br>N                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | =         | 0                 |                          | . :     |             |  |  |  |  |  |

| N                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | =         | 1                 | ; resul                  | i is ne | gative      |  |  |  |  |  |

| SWAPF                                                        | Swap f                                                                                                                                                              |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |      |                        |  |  |  |  |

|--------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------|------------------------|--|--|--|--|