Welcome to **E-XFL.COM**

What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded - Microcontrollers</u>"

| Details                    |                                                                             |

|----------------------------|-----------------------------------------------------------------------------|

| Product Status             | Active                                                                      |

| Core Processor             | PIC                                                                         |

| Core Size                  | 8-Bit                                                                       |

| Speed                      | 40MHz                                                                       |

| Connectivity               | I <sup>2</sup> C, SPI, UART/USART                                           |

| Peripherals                | Brown-out Detect/Reset, HLVD, POR, PWM, WDT                                 |

| Number of I/O              | 25                                                                          |

| Program Memory Size        | 8KB (4K x 16)                                                               |

| Program Memory Type        | FLASH                                                                       |

| EEPROM Size                | 256 x 8                                                                     |

| RAM Size                   | 512 x 8                                                                     |

| Voltage - Supply (Vcc/Vdd) | 2V ~ 5.5V                                                                   |

| Data Converters            | A/D 10x10b                                                                  |

| Oscillator Type            | Internal                                                                    |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                           |

| Mounting Type              | Surface Mount                                                               |

| Package / Case             | 28-SSOP (0.209", 5.30mm Width)                                              |

| Supplier Device Package    | 28-SSOP                                                                     |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic18lf2321t-i-ss |

TABLE 1-3: PIC18F4221/4321 PINOUT I/O DESCRIPTIONS

| Pin Name              | Piı  | n Numb | er   | Pin    | Buffer | Description                                                                                                                         |

|-----------------------|------|--------|------|--------|--------|-------------------------------------------------------------------------------------------------------------------------------------|

| Pili Name             | PDIP | QFN    | TQFP | Туре   | Type   | Description                                                                                                                         |

| MCLR/VPP/RE3<br>MCLR  | 1    | 18     | 18   | ı      | ST     | Master Clear (input) or programming voltage (input).  Master Clear (Reset) input. This pin is an active-low Reset to the device.    |

| VPP<br>RE3            |      |        |      | P<br>I | ST     | Programming voltage input. Digital input.                                                                                           |

| OSC1/CLKI/RA7<br>OSC1 | 13   | 32     | 30   | ı      | Analog | ST buffer when configured in RC mode;                                                                                               |

| CLKI                  |      |        |      | I      | Analog | analog otherwise.  External clock source input. Always associated with pin function OSC1. (See related OSC1/CLKI, OSC2/CLKO pins.)  |

| RA7                   |      |        |      | I/O    | TTL    | General purpose I/O pin.                                                                                                            |

| OSC2/CLKO/RA6<br>OSC2 | 14   | 33     | 31   | 0      | _      | Oscillator crystal or clock output. Oscillator crystal output. Connects to crystal or resonator in Crystal Oscillator mode.         |

| CLKO                  |      |        |      | 0      | _      | In RC, EC and INTIO modes, OSC2 pin outputs CLKO which has one-fourth the frequency of OSC1 and denotes the instruction cycle rate. |

| RA6                   |      |        |      | I/O    | TTL    | General purpose I/O pin.                                                                                                            |

**Legend:** TTL = TTL compatible input

ST = Schmitt Trigger input with CMOS levels

$I^2C = ST \text{ with } I^2C^{TM} \text{ or SMB levels}$

CMOS = CMOS compatible input or output I = Input P = Power

O = Output

Note 1: Default assignment for CCP2 when Configuration bit, CCP2MX, is set.

2: Alternate assignment for CCP2 when Configuration bit, CCP2MX, is cleared.

The PLUSW register can be used to implement a form of indexed addressing in the data memory space. By manipulating the value in the W register, users can reach addresses that are fixed offsets from pointer addresses. In some applications, this can be used to implement some powerful program control structure, such as software stacks, inside of data memory.

### 6.4.3.3 Operations by FSRs on FSRs

Indirect addressing operations that target other FSRs or virtual registers represent special cases. For example, using an FSR to point to one of the virtual registers will not result in successful operations. As a specific case, assume that FSR0H:FSR0L contains FE7h, the address of INDF1. Attempts to read the value of the INDF1 using INDF0 as an operand will return 00h. Attempts to write to INDF1 using INDF0 as the operand will result in a NOP.

On the other hand, using the virtual registers to write to an FSR pair may not occur as planned. In these cases, the value will be written to the FSR pair but without any incrementing or decrementing. Thus, writing to INDF2 or POSTDEC2 will write the same value to the FSR2H:FSR2L.

Since the FSRs are physical registers mapped in the SFR space, they can be manipulated through all direct operations. Users should proceed cautiously when working on these registers, particularly if their code uses indirect addressing.

Similarly, operations by indirect addressing are generally permitted on all other SFRs. Users should exercise the appropriate caution that they do not inadvertently change settings that might affect the operation of the device.

# 6.5 Data Memory and the Extended Instruction Set

Enabling the PIC18 extended instruction set (XINST Configuration bit = 1) significantly changes certain aspects of data memory and its addressing. Specifically, the use of the Access Bank for many of the core PIC18 instructions is different. This is due to the introduction of a new addressing mode for the data memory space.

What does not change is just as important. The size of the data memory space is unchanged, as well as its linear addressing. The SFR map remains the same. Core PIC18 instructions can still operate in both Direct and Indirect Addressing mode; inherent and literal instructions do not change at all. Indirect addressing with FSR0 and FSR1 also remain unchanged.

# 6.5.1 INDEXED ADDRESSING WITH LITERAL OFFSET

Enabling the PIC18 extended instruction set changes the behavior of indirect addressing using the FSR2 register pair within Access RAM. Under the proper conditions, instructions that use the Access Bank – that is, most bit-oriented and byte-oriented instructions – can invoke a form of indexed addressing using an offset specified in the instruction. This special addressing mode is known as Indexed Addressing with Literal Offset, or Indexed Literal Offset mode.

When using the extended instruction set, this addressing mode requires the following:

- The use of the Access Bank is forced ('a' = 0); and

- The file address argument is less than or equal to 5Fh.

Under these conditions, the file address of the instruction is not interpreted as the lower byte of an address (used with the BSR in direct addressing), or as an 8-bit address in the Access Bank. Instead, the value is interpreted as an offset value to an Address Pointer, specified by FSR2. The offset and the contents of FSR2 are added to obtain the target address of the operation.

# 6.5.2 INSTRUCTIONS AFFECTED BY INDEXED LITERAL OFFSET MODE

Any of the core PIC18 instructions that can use direct addressing are potentially affected by the Indexed Literal Offset Addressing mode. This includes all byte-oriented and bit-oriented instructions, or almost one-half of the standard PIC18 instruction set. Instructions that only use Inherent or Literal Addressing modes are unaffected.

Additionally, byte-oriented and bit-oriented instructions are not affected if they do not use the Access Bank (Access RAM bit is '1'), or include a file address of 60h or above. Instructions meeting these criteria will continue to execute as before. A comparison of the different possible addressing modes when the extended instruction set is enabled is shown in Figure 6-8.

Those who desire to use bit-oriented or byte-oriented instructions in the Indexed Literal Offset mode should note the changes to assembler syntax for this mode. This is described in more detail in **Section 24.2.1** "Extended Instruction Syntax".

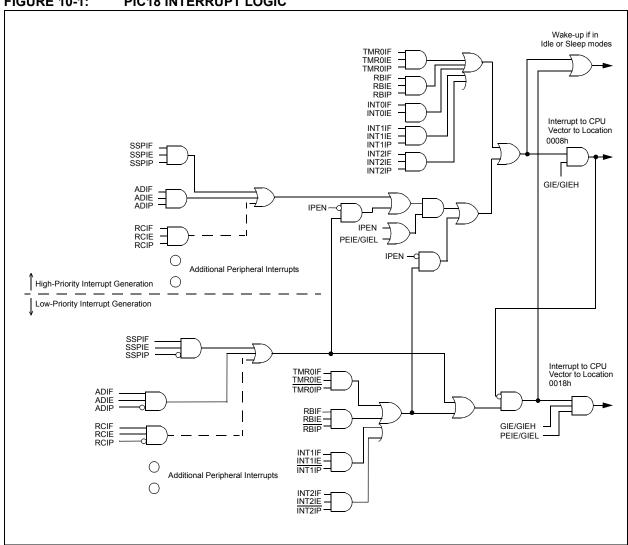

**FIGURE 10-1:** PIC18 INTERRUPT LOGIC

TABLE 11-7: PORTD I/O SUMMARY

| Pin          | Function                      | TRIS<br>Setting | I/O                   | I/O<br>Type | Description                                                                                                                                       |

|--------------|-------------------------------|-----------------|-----------------------|-------------|---------------------------------------------------------------------------------------------------------------------------------------------------|

| RD0/PSP0     | RD0                           | 0               | 0                     | DIG         | LATD<0> data output.                                                                                                                              |

|              |                               | 1               | 1                     | ST          | PORTD<0> data input.                                                                                                                              |

|              | PSP0                          | Х               | 0                     | DIG         | PSP read data output (LATD<0>); takes priority over port data.                                                                                    |

|              |                               | Х               | ı                     | TTL         | PSP write data input.                                                                                                                             |

| RD1/PSP1     | RD1                           | 0               | 0                     | DIG         | LATD<1> data output.                                                                                                                              |

|              |                               | 1               | I                     | ST          | PORTD<1> data input.                                                                                                                              |

|              | PSP1                          | Х               | 0                     | DIG         | PSP read data output (LATD<1>); takes priority over port data.                                                                                    |

|              |                               | Х               | I                     | TTL         | PSP write data input.                                                                                                                             |

| RD2/PSP2     | RD2                           | 0               | 0                     | DIG         | LATD<2> data output.                                                                                                                              |

|              | 1 I ST PORTD<2> data input.   |                 | PORTD<2> data input.  |             |                                                                                                                                                   |

|              | PSP2                          | Х               | 0                     | DIG         | PSP read data output (LATD<2>); takes priority over port data.                                                                                    |

|              |                               | Х               | 1                     | TTL         | PSP write data input.                                                                                                                             |

| RD3/PSP3     | RD3                           | 0               | 0                     | DIG         | LATD<3> data output.                                                                                                                              |

|              |                               | 1               | I                     | ST          | PORTD<3> data input.                                                                                                                              |

|              | PSP3                          | Х               | 0                     | DIG         | PSP read data output (LATD<3>); takes priority over port data.                                                                                    |

|              |                               | Х               | I                     | TTL         | PSP write data input.                                                                                                                             |

| RD4/PSP4     | RD4                           | 0               | 0                     | DIG         | LATD<4> data output.                                                                                                                              |

|              |                               | 1               | 1                     | ST          | PORTD<4> data input.                                                                                                                              |

| PSP4         |                               | Х               | 0                     | DIG         | PSP read data output (LATD<4>); takes priority over port data.                                                                                    |

|              | x I TTL PSP write data input. |                 | PSP write data input. |             |                                                                                                                                                   |

| RD5/PSP5/P1B | RD5                           | 0               | 0                     | DIG         | LATD<5> data output.                                                                                                                              |

|              |                               | 1               | 1                     | ST          | PORTD<5> data input.                                                                                                                              |

|              | PSP5                          | Х               | 0                     | DIG         | PSP read data output (LATD<5>); takes priority over port data.                                                                                    |

|              |                               | Х               | -                     | TTL         | PSP write data input.                                                                                                                             |

|              | P1B                           | 0               | 0                     | DIG         | ECCP1 Enhanced PWM output, Channel B; takes priority over port and PSP data. May be configured for tri-state during Enhanced PWM shutdown events. |

| RD6/PSP6/P1C | RD6                           | 0               | 0                     | DIG         | LATD<6> data output.                                                                                                                              |

|              |                               | 1               | 1                     | ST          | PORTD<6> data input.                                                                                                                              |

|              | PSP6                          | Х               | 0                     | DIG         | PSP read data output (LATD<6>); takes priority over port data.                                                                                    |

|              |                               | Х               | 1                     | TTL         | PSP write data input.                                                                                                                             |

|              | P1C                           | 0               | 0                     | DIG         | ECCP1 Enhanced PWM output, channel C; takes priority over port and PSP data. May be configured for tri-state during Enhanced PWM shutdown events. |

| RD7/PSP7/P1D | RD7                           | 0               | 0                     | DIG         | LATD<7> data output.                                                                                                                              |

|              |                               | 1               | I                     | ST          | PORTD<7> data input.                                                                                                                              |

|              | PSP7                          | Х               | 0                     | DIG         | PSP read data output (LATD<7>); takes priority over port data.                                                                                    |

|              |                               | Х               | I                     | TTL         | PSP write data input.                                                                                                                             |

|              | P1D                           | 0               | 0                     | DIG         | ECCP1 Enhanced PWM output, Channel D; takes priority over port and PSP data. May be configured for tri-state during Enhanced PWM shutdown events. |

**Legend:** DIG = Digital level output; TTL = TTL input buffer; ST = Schmitt Trigger input buffer; x = Don't care (TRIS bit does not affect port direction or is overridden for this option).

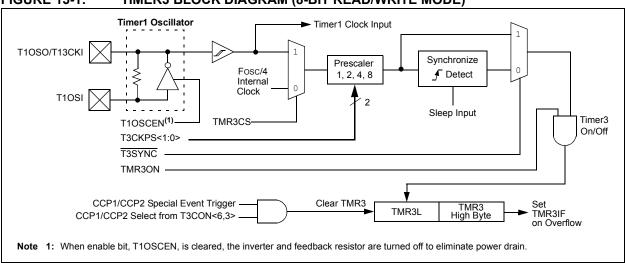

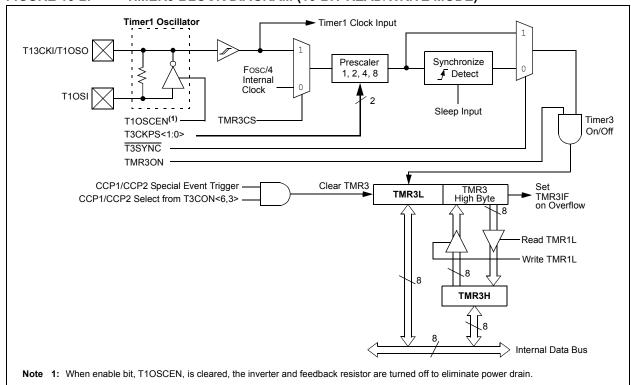

### 15.1 Timer3 Operation

Timer3 can operate in one of three modes:

- Timer

- · Synchronous Counter

- · Asynchronous Counter

The operating mode is determined by the clock select bit, TMR3CS (T3CON<1>). When TMR3CS is cleared (= 0), Timer3 increments on every internal instruction cycle (Fosc/4). When the bit is set, Timer3 increments on every rising edge of the Timer1 external clock input or the Timer1 oscillator, if enabled.

As with Timer1, the RC1/T1OSI and RC0/T1OSO/T13CKI pins become inputs when the Timer1 oscillator is enabled. This means the values of TRISC<1:0> are ignored and the pins are read as '0'.

### FIGURE 15-1: TIMER3 BLOCK DIAGRAM (8-BIT READ/WRITE MODE)

## FIGURE 15-2: TIMER3 BLOCK DIAGRAM (16-BIT READ/WRITE MODE)

#### 18.4.3.3 Reception

When the  $R/\overline{W}$  bit of the address byte is clear and an address match occurs, the  $R/\overline{W}$  bit of the SSPSTAT register is cleared. The received address is loaded into the SSPBUF register and the SDA line is held low  $(\overline{ACK})$ .

When the address byte overflow condition exists, then the no Acknowledge (ACK) pulse is given. An overflow condition is defined as either bit BF (SSPSTAT<0>) is set, or bit SSPOV (SSPCON1<6>) is set.

An MSSP interrupt is generated for each data transfer byte. Flag bit, SSPIF (PIR1<3>), must be cleared in software. The SSPSTAT register is used to determine the status of the byte.

If SEN is enabled (SSPCON2<0> = 1), RC3/SCK/SCL will be held low (clock stretch) following each data transfer. The clock must be released by setting bit, CKP (SSPCON1<4>). See **Section 18.4.4 "Clock Stretching"** for more detail.

#### 18.4.3.4 Transmission

When the  $R/\overline{W}$  bit of the incoming address byte is set and an address match occurs, the R/W bit of the SSPSTAT register is set. The received address is loaded into the SSPBUF register. The ACK pulse will be sent on the ninth bit and pin RC3/SCK/SCL is held low regardless of SEN (see Section 18.4.4 "Clock Stretching" for more detail). By stretching the clock, the master will be unable to assert another clock pulse until the slave is done preparing the transmit data. The transmit data must be loaded into the SSPBUF register which also loads the SSPSR register. Then pin RC3/ SCK/SCL should be enabled by setting bit, CKP (SSPCON1<4>). The eight data bits are shifted out on the falling edge of the SCL input. This ensures that the SDA signal is valid during the SCL high time (Figure 18-10).

The  $\overline{ACK}$  pulse from the master-receiver is latched on the rising edge of the ninth SCL input pulse. If the SDA line is high (not  $\overline{ACK}$ ), then the data transfer is complete. In this case, when the  $\overline{ACK}$  is latched by the slave, the slave logic is reset and the slave monitors for another occurrence of the Start bit. If the SDA line was low ( $\overline{ACK}$ ), the next transmit data must be loaded into the SSPBUF register. Again, pin RC3/SCK/SCL must be enabled by setting bit CKP.

An MSSP interrupt is generated for each data transfer byte. The SSPIF bit must be cleared in software and the SSPSTAT register is used to determine the status of the byte. The SSPIF bit is set on the falling edge of the ninth clock pulse.

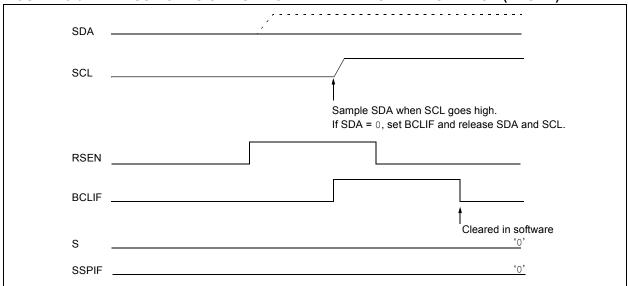

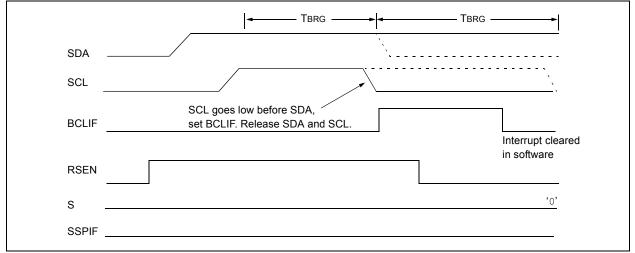

# 18.4.17.2 Bus Collision During a Repeated Start Condition

During a Repeated Start condition, a bus collision occurs if:

- A low level is sampled on SDA when SCL goes from low level to high level.

- SCL goes low before SDA is asserted low, indicating that another master is attempting to transmit a data '1'.

When the user deasserts SDA and the pin is allowed to float high, the BRG is loaded with SSPADD<6:0> and counts down to 0. The SCL pin is then deasserted and when sampled high, the SDA pin is sampled.

If SDA is low, a bus collision has occurred (i.e., another master is attempting to transmit a data '0', Figure 18-31). If SDA is sampled high, the BRG is reloaded and begins counting. If SDA goes from high-to-low before the BRG times out, no bus collision occurs because no two masters can assert SDA at exactly the same time.

If SCL goes from high-to-low before the BRG times out and SDA has not already been asserted, a bus collision occurs. In this case, another master is attempting to transmit a data '1' during the Repeated Start condition, see Figure 18-32.

If, at the end of the BRG time-out, both SCL and SDA are still high, the SDA pin is driven low and the BRG is reloaded and begins counting. At the end of the count, regardless of the status of the SCL pin, the SCL pin is driven low and the Repeated Start condition is complete.

FIGURE 18-31: BUS COLLISION DURING A REPEATED START CONDITION (CASE 1)

FIGURE 18-32: BUS COLLISION DURING REPEATED START CONDITION (CASE 2)

TABLE 19-3: BAUD RATES FOR ASYNCHRONOUS MODES

|       |                       |            |                             |                       | SYNC       | = 0, BRGH                   | 1 = 0, BRG            | <b>316 =</b> 0 |                             |                       |            |                             |

|-------|-----------------------|------------|-----------------------------|-----------------------|------------|-----------------------------|-----------------------|----------------|-----------------------------|-----------------------|------------|-----------------------------|

| BAUD  | Fosc = 40.000 MHz     |            | ) MHz                       | Fosc = 20.000 MHz     |            |                             | Fosc = 10.000 MHz     |                |                             | Fosc = 8.000 MHz      |            |                             |

| (K)   | Actual<br>Rate<br>(K) | %<br>Error | SPBRG<br>value<br>(decimal) | Actual<br>Rate<br>(K) | %<br>Error | SPBRG<br>value<br>(decimal) | Actual<br>Rate<br>(K) | %<br>Error     | SPBRG<br>value<br>(decimal) | Actual<br>Rate<br>(K) | %<br>Error | SPBRG<br>value<br>(decimal) |

| 0.3   | _                     | _          | _                           | _                     | _          | _                           | _                     | _              | _                           |                       | _          | _                           |

| 1.2   | _                     | _          | _                           | 1.221                 | 1.73       | 255                         | 1.202                 | 0.16           | 129                         | 1.201                 | -0.16      | 103                         |

| 2.4   | 2.441                 | 1.73       | 255                         | 2.404                 | 0.16       | 129                         | 2.404                 | 0.16           | 64                          | 2.403                 | -0.16      | 51                          |

| 9.6   | 9.615                 | 0.16       | 64                          | 9.766                 | 1.73       | 31                          | 9.766                 | 1.73           | 15                          | 9.615                 | -0.16      | 12                          |

| 19.2  | 19.531                | 1.73       | 31                          | 19.531                | 1.73       | 15                          | 19.531                | 1.73           | 7                           | _                     | _          | _                           |

| 57.6  | 56.818                | -1.36      | 10                          | 62.500                | 8.51       | 4                           | 52.083                | -9.58          | 2                           | _                     | _          | _                           |

| 115.2 | 125.000               | 8.51       | 4                           | 104.167               | -9.58      | 2                           | 78.125                | -32.18         | 1                           |                       | _          | _                           |

|             |                       |            | s                           | YNC = 0, E            | BRGH = 0   | o, BRG16 =                  | 0                     |            |                             |  |

|-------------|-----------------------|------------|-----------------------------|-----------------------|------------|-----------------------------|-----------------------|------------|-----------------------------|--|

| BAUD        | Fos                   | c = 4.000  | MHz                         | Fos                   | c = 2.000  | MHz                         | Fosc = 1.000 MHz      |            |                             |  |

| RATE<br>(K) | Actual<br>Rate<br>(K) | %<br>Error | SPBRG<br>value<br>(decimal) | Actual<br>Rate<br>(K) | %<br>Error | SPBRG<br>value<br>(decimal) | Actual<br>Rate<br>(K) | %<br>Error | SPBRG<br>value<br>(decimal) |  |

| 0.3         | 0.300                 | 0.16       | 207                         | 0.300                 | -0.16      | 103                         | 0.300                 | -0.16      | 51                          |  |

| 1.2         | 1.202                 | 0.16       | 51                          | 1.201                 | -0.16      | 25                          | 1.201                 | -0.16      | 12                          |  |

| 2.4         | 2.404                 | 0.16       | 25                          | 2.403                 | -0.16      | 12                          | _                     | _          | _                           |  |

| 9.6         | 8.929                 | -6.99      | 6                           | _                     | _          | _                           | _                     | _          | _                           |  |

| 19.2        | 20.833                | 8.51       | 2                           | _                     | _          | _                           | _                     | _          | _                           |  |

| 57.6        | 62.500                | 8.51       | 0                           | _                     | _          | _                           | _                     | _          | _                           |  |

| 115.2       | 62.500                | -45.75     | 0                           | -                     | _          | _                           | -                     | _          | _                           |  |

|             |                       |            |                             |                       | SYNC       | = 0, BRGH                   | l = 1, BRG            | <b>16 =</b> 0 |                             |                       |            |                             |

|-------------|-----------------------|------------|-----------------------------|-----------------------|------------|-----------------------------|-----------------------|---------------|-----------------------------|-----------------------|------------|-----------------------------|

| BAUD        | Fosc                  | = 40.000   | ) MHz                       | Fosc = 20.000 MHz     |            |                             | Fosc = 10.000 MHz     |               |                             | Fosc = 8.000 MHz      |            |                             |

| RATE<br>(K) | Actual<br>Rate<br>(K) | %<br>Error | SPBRG<br>value<br>(decimal) | Actual<br>Rate<br>(K) | %<br>Error | SPBRG<br>value<br>(decimal) | Actual<br>Rate<br>(K) | %<br>Error    | SPBRG<br>value<br>(decimal) | Actual<br>Rate<br>(K) | %<br>Error | SPBRG<br>value<br>(decimal) |

| 0.3         | _                     | _          | _                           | _                     | _          | _                           | _                     | _             | _                           | _                     | _          | _                           |

| 1.2         | _                     | _          | _                           | _                     | _          | _                           | _                     | _             | _                           | _                     | _          | _                           |

| 2.4         | _                     | _          | _                           | _                     | _          | _                           | 2.441                 | 1.73          | 255                         | 2.403                 | -0.16      | 207                         |

| 9.6         | 9.766                 | 1.73       | 255                         | 9.615                 | 0.16       | 129                         | 9.615                 | 0.16          | 64                          | 9.615                 | -0.16      | 51                          |

| 19.2        | 19.231                | 0.16       | 129                         | 19.231                | 0.16       | 64                          | 19.531                | 1.73          | 31                          | 19.230                | -0.16      | 25                          |

| 57.6        | 58.140                | 0.94       | 42                          | 56.818                | -1.36      | 21                          | 56.818                | -1.36         | 10                          | 55.555                | 3.55       | 8                           |

| 115.2       | 113.636               | -1.36      | 21                          | 113.636               | -1.36      | 10                          | 125.000               | 8.51          | 4                           | _                     | _          | _                           |

|              |                       |            | S'                          | YNC = 0, E | BRGH = 1  | , BRG16 =                   | 0                     |            |                             |  |

|--------------|-----------------------|------------|-----------------------------|------------|-----------|-----------------------------|-----------------------|------------|-----------------------------|--|

| BAUD<br>RATE | Fosc                  | = 4.000    | MHz                         | Fos        | c = 2.000 | MHz                         | Fosc = 1.000 MHz      |            |                             |  |

| (K)          | Actual<br>Rate<br>(K) | %<br>Error | SPBRG<br>value<br>(decimal) | Rate Error |           | SPBRG<br>value<br>(decimal) | Actual<br>Rate<br>(K) | %<br>Error | SPBRG<br>value<br>(decimal) |  |

| 0.3          | _                     | _          | _                           |            | _         | _                           | 0.300                 | -0.16      | 207                         |  |

| 1.2          | 1.202                 | 0.16       | 207                         | 1.201      | -0.16     | 103                         | 1.201                 | -0.16      | 51                          |  |

| 2.4          | 2.404                 | 0.16       | 103                         | 2.403      | -0.16     | 51                          | 2.403                 | -0.16      | 25                          |  |

| 9.6          | 9.615                 | 0.16       | 25                          | 9.615      | -0.16     | 12                          | _                     | _          | _                           |  |

| 19.2         | 19.231                | 0.16       | 12                          | _          | _         | _                           | _                     | _          | _                           |  |

| 57.6         | 62.500                | 8.51       | 3                           | _          | _         | _                           | _                     | _          | _                           |  |

| 115.2        | 125.000               | 8.51       | 1                           | _          | _         | _                           | _                     | _          | _                           |  |

TABLE 19-5: REGISTERS ASSOCIATED WITH ASYNCHRONOUS TRANSMISSION

| Name    | Bit 7                | Bit 6                                         | Bit 5  | Bit 4  | Bit 3 | Bit 2  | Bit 1  | Bit 0  | Reset<br>Values<br>on page |

|---------|----------------------|-----------------------------------------------|--------|--------|-------|--------|--------|--------|----------------------------|

| INTCON  | GIE/GIEH             | PEIE/GIEL                                     | TMR0IE | INT0IE | RBIE  | TMR0IF | INT0IF | RBIF   | 55                         |

| PIR1    | PSPIF <sup>(1)</sup> | ADIF                                          | RCIF   | TXIF   | SSPIF | CCP1IF | TMR2IF | TMR1IF | 58                         |

| PIE1    | PSPIE <sup>(1)</sup> | ADIE                                          | RCIE   | TXIE   | SSPIE | CCP1IE | TMR2IE | TMR1IE | 58                         |

| IPR1    | PSPIP <sup>(1)</sup> | ADIP                                          | RCIP   | TXIP   | SSPIP | CCP1IP | TMR2IP | TMR1IP | 58                         |

| RCSTA   | SPEN                 | RX9                                           | SREN   | CREN   | ADDEN | FERR   | OERR   | RX9D   | 57                         |

| TXREG   | EUSART T             | ransmit Reg                                   | ister  |        |       |        |        |        | 57                         |

| TXSTA   | CSRC                 | TX9                                           | TXEN   | SYNC   | SENDB | BRGH   | TRMT   | TX9D   | 57                         |

| BAUDCON | ABDOVF               | RCIDL                                         | RXDTP  | TXCKP  | BRG16 | _      | WUE    | ABDEN  | 57                         |

| SPBRGH  | EUSART B             | EUSART Baud Rate Generator Register High Byte |        |        |       |        |        |        | 57                         |

| SPBRG   | EUSART B             | USART Baud Rate Generator Register Low Byte   |        |        |       |        |        |        | 57                         |

**Legend:** — = unimplemented locations read as '0'. Shaded cells are not used for asynchronous transmission.

Note 1: These bits are unimplemented on 28-pin devices and read as '0'.

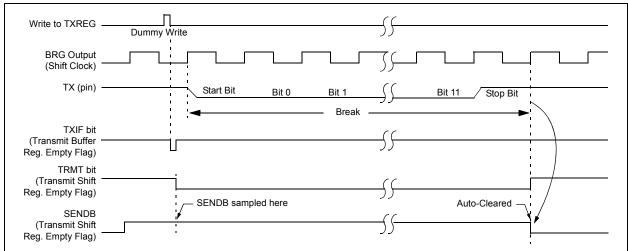

#### 19.2.5 BREAK CHARACTER SEQUENCE

The EUSART module has the capability of sending the special Break character sequences that are required by the LIN/J2602 bus standard. The Break character transmit consists of a Start bit, followed by twelve '0' bits and a Stop bit. The Frame Break character is sent whenever the SENDB and TXEN bits (TXSTA<3> and TXSTA<5>) are set while the Transmit Shift register is loaded with data. Note that the value of data written to TXREG will be ignored and all '0's will be transmitted.

The SENDB bit is automatically reset by hardware after the corresponding Stop bit is sent. This allows the user to preload the transmit FIFO with the next transmit byte following the Break character (typically, the Sync character in the LIN/J2602 specification).

Note that the data value written to the TXREG for the Break character is ignored. The write simply serves the purpose of initiating the proper sequence.

The TRMT bit indicates when the transmit operation is active or Idle, just as it does during normal transmission. See Figure 19-10 for the timing of the Break character sequence.

### 19.2.5.1 Break and Sync Transmit Sequence

The following sequence will send a message frame header made up of a Break, followed by an Auto-Baud Sync byte. This sequence is typical of a LIN/J2602 bus master.

- Configure the EUSART for the desired mode.

- Set the TXEN and SENDB bits to set up the Break character.

- 3. Load the TXREG with a dummy character to initiate transmission (the value is ignored).

- Write '55h' to TXREG to load the Sync character into the transmit FIFO buffer.

- After the Break has been sent, the SENDB bit is reset by hardware. The Sync character now transmits in the preconfigured mode.

When the TXREG becomes empty, as indicated by the TXIF, the next data byte can be written to TXREG.

#### 19.2.6 RECEIVING A BREAK CHARACTER

The Enhanced USART module can receive a Break character in two ways.

The first method forces configuration of the baud rate at a frequency of 9/13 the typical speed. This allows for the Stop bit transition to be at the correct sampling location (13 bits for Break versus Start bit and 8 data bits for typical data).

The second method uses the auto-wake-up feature described in **Section 19.2.4 "Auto-Wake-up on Sync Break Character"**. By enabling this feature, the EUSART will sample the next two transitions on RX/DT, cause an RCIF interrupt and receive the next data byte followed by another interrupt.

Note that following a Break character, the user will typically want to enable the Auto-Baud Rate Detect feature. For both methods, the user can set the ABD bit once the TXIF interrupt is observed.

FIGURE 19-10: SEND BREAK CHARACTER SEQUENCE

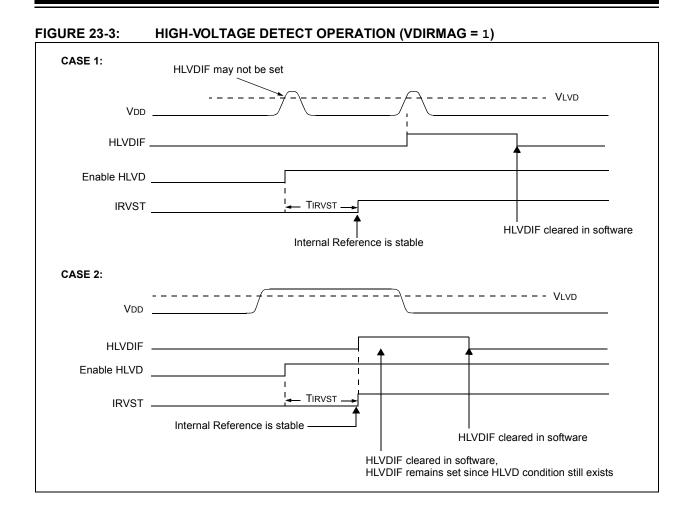

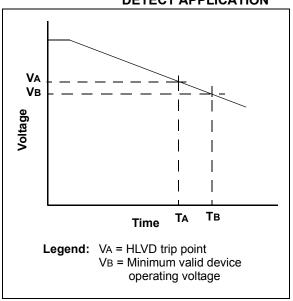

## 23.5 Applications

In many applications, the ability to detect a drop below or rise above a particular threshold is desirable. For example, the HLVD module could be periodically enabled to detect a Universal Serial Bus (USB) attach or detach. This assumes the device is powered by a lower voltage source than the USB when detached. An attach would indicate a high-voltage detect from, for example, 3.3V to 5V (the voltage on USB) and vice versa for a detach. This feature could save a design a few extra components and an attach signal (input pin).

For general battery applications, Figure 23-4 shows a possible voltage curve. Over time, the device voltage decreases. When the device voltage reaches voltage VA, the HLVD logic generates an interrupt at time TA. The interrupt could cause the execution of an ISR, which would allow the application to perform "house-keeping tasks" and perform a controlled shutdown before the device voltage exits the valid operating range at TB. The HLVD, thus, would give the application a time window, represented by the difference between TA and TB, to safely exit.

### REGISTER 24-2: CONFIG2L: CONFIGURATION REGISTER 2 LOW (BYTE ADDRESS 300002h)

| U-0   | U-0 | U-0 | R/P-1                | R/P-1                | R/P-1                 | R/P-1                 | R/P-1                 |

|-------|-----|-----|----------------------|----------------------|-----------------------|-----------------------|-----------------------|

|       |     |     | BORV1 <sup>(1)</sup> | BORV0 <sup>(1)</sup> | BOREN1 <sup>(2)</sup> | BORENO <sup>(2)</sup> | PWRTEN <sup>(2)</sup> |

| bit 7 |     |     |                      |                      |                       |                       | bit 0                 |

bit 7-5 Unimplemented: Read as '0'

bit 4-3 **BORV<1:0>:** Brown-out Reset Voltage bits<sup>(1)</sup>

11 = Minimum setting

.

00 = Maximum setting

- bit 2-1 BOREN<1:0>: Brown-out Reset Enable bits(2)

- 11 = Brown-out Reset enabled in hardware only (SBOREN is disabled)

- 10 = Brown-out Reset enabled in hardware only and disabled in Sleep mode (SBOREN is disabled)

- 01 = Brown-out Reset enabled and controlled by software (SBOREN is enabled)

- 00 = Brown-out Reset disabled in hardware and software

- bit 0 **PWRTEN**: Power-up Timer Enable bit<sup>(2)</sup>

- 1 = PWRT disabled

- 0 = PWRT enabled

- Note 1: See Section 27.1 "DC Characteristics" for the specifications.

- 2: The Power-up Timer is decoupled from Brown-out Reset, allowing these features to be independently controlled.

### Legend:

R = Readable bit P = Programmable bit U = Unimplemented bit, read as '0'

-n = Value when device is unprogrammed u = Unchanged from programmed state

### REGISTER 24-8: CONFIG6L: CONFIGURATION REGISTER 6 LOW (BYTE ADDRESS 30000Ah)

| U-0   | U-0 | U-0 | U-0 | U-0 | U-0 | R/C-1 | R/C-1 |

|-------|-----|-----|-----|-----|-----|-------|-------|

| _     | _   | _   | _   | _   | _   | WRT1  | WRT0  |

| bit 7 |     |     |     |     |     |       | bit 0 |

bit 7-2 Unimplemented: Read as '0'

bit 1 WRT1: Write Protection bit

1 = Block 1 not write-protected<sup>(1)</sup>

0 = Block 1 write-protected<sup>(1)</sup>

bit 0 WRT0: Write Protection bit

1 = Block 0 not write-protected<sup>(1)</sup>

0 = Block 0 write-protected(1)

Note 1: See Figure 24-5 for variable block boundaries.

#### Legend:

R = Readable bit C = Clearable bit U = Unimplemented bit, read as '0'

-n = Value when device is unprogrammed u = Unchanged from programmed state

### REGISTER 24-9: CONFIG6H: CONFIGURATION REGISTER 6 HIGH (BYTE ADDRESS 30000Bh)

| R/C-1 | R/C-1 | R-1                 | U-0 | U-0 | U-0 | U-0 | U-0   |

|-------|-------|---------------------|-----|-----|-----|-----|-------|

| WRTD  | WRTB  | WRTC <sup>(1)</sup> | _   | _   | _   | _   | _     |

| bit 7 |       |                     |     |     |     |     | bit 0 |

- bit 7 WRTD: Data EEPROM Write Protection bit

- 1 = Data EEPROM not write-protected

- 0 = Data EEPROM write-protected

- bit 6 WRTB: Boot Block Write Protection bit

- 1 = Boot block not write-protected(2)

- 0 = Boot block write-protected<sup>(2)</sup>

- bit 5 **WRTC:** Configuration Register Write Protection bit<sup>(1)</sup>

- 1 = Configuration registers (300000-3000FFh) not write-protected

- 0 = Configuration registers (300000-3000FFh) write-protected

- bit 4-0 Unimplemented: Read as '0'

- Note 1: This bit is read-only in normal execution mode; it can be written only in Program mode.

- 2: See Figure 24-5 for block boundaries.

#### Legend:

R = Readable bit C = Clearable bit U = Unimplemented bit, read as '0'

-n = Value when device is unprogrammed u = Unchanged from programmed state

## TABLE 25-1: OPCODE FIELD DESCRIPTIONS

| Field           | Description                                                                                                                                                                  |

|-----------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| a               | RAM access bit                                                                                                                                                               |

|                 | a = 0: RAM location in Access RAM (BSR register is ignored)                                                                                                                  |

|                 | a = 1: RAM bank is specified by BSR register                                                                                                                                 |

| bbb             | Bit address within an 8-bit file register (0 to 7).                                                                                                                          |

| BSR             | Bank Select Register. Used to select the current RAM bank.                                                                                                                   |

| C, DC, Z, OV, N | ALU Status bits: Carry, Digit Carry, Zero, Overflow, Negative.                                                                                                               |

| d               | Destination select bit                                                                                                                                                       |

|                 | d = 0: store result in WREG d = 1: store result in file register f                                                                                                           |

| J+              |                                                                                                                                                                              |

| dest            | Destination: either the WREG register or the specified register file location.  8-bit Register file address (00h to FFh) or 2-bit FSR designator (0h to 3h).                 |

|                 |                                                                                                                                                                              |

| f <sub>s</sub>  | 12-bit Register file address (000h to FFFh). This is the source address.  12-bit Register file address (000h to FFFh). This is the destination address.                      |

| f <sub>d</sub>  |                                                                                                                                                                              |

| GIE             | Global Interrupt Enable bit.                                                                                                                                                 |

| k               | Literal field, constant data or label (may be either an 8-bit, 12-bit or a 20-bit value).                                                                                    |

| label           | Label name.                                                                                                                                                                  |

| mm              | The mode of the TBLPTR register for the table read and table write instructions.  Only used with table read and table write instructions:                                    |

| *               | No change to register (such as TBLPTR with table reads and writes)                                                                                                           |

| *+              | Post-Increment register (such as TBLPTR with table reads and writes)                                                                                                         |

| ^ +<br>* -      | · · · · · · · · · · · · · · · · · · ·                                                                                                                                        |

|                 | Post-Decrement register (such as TBLPTR with table reads and writes)                                                                                                         |

| +*              | Pre-Increment register (such as TBLPTR with table reads and writes)  The relative address (2's complement number) for relative breach instructions as the direct address for |

| n               | The relative address (2's complement number) for relative branch instructions or the direct address for Call/Branch and Return instructions.                                 |

| PC              | Program Counter.                                                                                                                                                             |

| PCL             | Program Counter Low Byte.                                                                                                                                                    |

| PCH             | Program Counter High Byte.                                                                                                                                                   |

| PCLATH          | Program Counter High Byte Latch.                                                                                                                                             |

| PCLATU          | Program Counter Upper Byte Latch.                                                                                                                                            |

| PD              | Power-Down bit.                                                                                                                                                              |

| PRODH           | Product of Multiply High Byte.                                                                                                                                               |

| PRODL           | Product of Multiply Low Byte.                                                                                                                                                |

| s               | Fast Call/Return mode select bit                                                                                                                                             |

|                 | s = 0: do not update into/from shadow registers                                                                                                                              |

|                 | s = 1: certain registers loaded into/from shadow registers (Fast mode)                                                                                                       |

| TBLPTR          | 21-bit Table Pointer (points to a program memory location).                                                                                                                  |

| TABLAT          | 8-bit Table Latch.                                                                                                                                                           |

| TO              | Time-out bit.                                                                                                                                                                |

| TOS             | Top-of-Stack.                                                                                                                                                                |

| u               | Unused or unchanged.                                                                                                                                                         |

| WDT             | Watchdog Timer.                                                                                                                                                              |

| WREG            | Working register (accumulator).                                                                                                                                              |

| х               | Don't care ('0' or '1'). The assembler will generate code with $x = 0$ . It is the recommended form of use for                                                               |

|                 | compatibility with all Microchip software tools.                                                                                                                             |

| Z <sub>S</sub>  | 7-bit offset value for indirect addressing of register files (source).                                                                                                       |

| z <sub>d</sub>  | 7-bit offset value for indirect addressing of register files (destination).                                                                                                  |

| { }             | Optional argument.                                                                                                                                                           |

| [text]          | Indicates an indexed address.                                                                                                                                                |

| (text)          | The contents of text.                                                                                                                                                        |

| [expr] <n></n>  | Specifies bit n of the register indicated by the pointer expr.                                                                                                               |

| $\rightarrow$   | Assigned to.                                                                                                                                                                 |

| < >             | Register bit field.                                                                                                                                                          |

| €               | In the set of.                                                                                                                                                               |

| italics         | User-defined term (font is Courier New).                                                                                                                                     |

### FIGURE 25-1: GENERAL FORMAT FOR INSTRUCTIONS

#### Byte-oriented file register operations **Example Instruction** 15 10 9 8 7 OPCODE d а f (FILE #) ADDWF MYREG, W, B d = 0 for result destination to be WREG register d = 1 for result destination to be file register (f) a = 0 to force Access Bank a = 1 for BSR to select bank f = 8-bit file register address Byte to Byte move operations (2-word) 12 11 OPCODE f (Source FILE #) MOVFF MYREG1, MYREG2 0 15 f (Destination FILE #) 1111 f = 12-bit file register address Bit-oriented file register operations 987 12 11 OPCODE b (BIT #) f (FILE #) BSF MYREG, bit, B а b = 3-bit position of bit in file register (f) a = 0 to force Access Bank a = 1 for BSR to select bank f = 8-bit file register address **Literal** operations 15 **OPCODE** MOVLW 7Fh k (literal) k = 8-bit immediate value **Control** operations CALL, GOTO and Branch operations 15 0 **OPCODE** n<7:0> (literal) GOTO Label 15 12 11 0 1111 n<19:8> (literal) n = 20-bit immediate value 15 OPCODE n<7:0> (literal) CALL MYFUNC 12 11 15 n<19:8> (literal) 1111 S = Fast bit 11 10 15 0 OPCODE BRA MYFUNC n<10:0> (literal) 8 7 15 BC MYFUNC **OPCODE** n<7:0> (literal)

27.2 DC Characteristics: Power-Down and Supply Current

PIC18F2221/2321/4221/4321 (Industrial)

PIC18LF2221/2321/4221/4321 (Industrial) (Continued)

| PIC18LF2221/2321/4221/4321<br>(Industrial) |                                     | Standard Operating Conditions (unless otherwise stated) Operating temperature $-40^{\circ}\text{C} \le \text{Ta} \le +85^{\circ}\text{C}$ for industrial  Standard Operating Conditions (unless otherwise stated) Operating temperature $-40^{\circ}\text{C} \le \text{Ta} \le +85^{\circ}\text{C}$ for industrial $-40^{\circ}\text{C} \le \text{Ta} \le +125^{\circ}\text{C}$ for extended |     |       |            |            |                                                  |  |  |

|--------------------------------------------|-------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|-------|------------|------------|--------------------------------------------------|--|--|

| PIC18F22<br>(Indus                         |                                     |                                                                                                                                                                                                                                                                                                                                                                                              |     |       |            |            |                                                  |  |  |

| Param<br>No.                               | Device                              | Тур                                                                                                                                                                                                                                                                                                                                                                                          | Max | Units | Conditions |            |                                                  |  |  |

|                                            | Supply Current (IDD) <sup>(2)</sup> |                                                                                                                                                                                                                                                                                                                                                                                              |     |       |            |            |                                                  |  |  |

|                                            | All Devices                         | 7                                                                                                                                                                                                                                                                                                                                                                                            | 10  | mA    | -40°C      |            |                                                  |  |  |

|                                            |                                     | 6                                                                                                                                                                                                                                                                                                                                                                                            | 10  | mA    | +25°C      | VDD = 4.2V | Fosc = 4 MHz,<br>16 MHz internal                 |  |  |

|                                            |                                     | 6                                                                                                                                                                                                                                                                                                                                                                                            | 10  | mA    | +85°C      |            | (PRI RUN HS+PLL)                                 |  |  |

|                                            | Extended Devices Only               | 6                                                                                                                                                                                                                                                                                                                                                                                            | 10  | mA    | +125°C     |            | (* *** <u>_</u> ******************************** |  |  |

|                                            | All Devices                         | 10                                                                                                                                                                                                                                                                                                                                                                                           | 12  | mA    | -40°C      |            |                                                  |  |  |

|                                            |                                     | 9                                                                                                                                                                                                                                                                                                                                                                                            | 12  | mA    | +25°C      | VDD = 5.0V | Fosc = 4 MHz,<br>16 MHz internal                 |  |  |

|                                            |                                     | 9                                                                                                                                                                                                                                                                                                                                                                                            | 12  | mA    | +85°C      | VDD = 5.0V | (PRI RUN HS+PLL)                                 |  |  |

|                                            | Extended Devices Only               | 9                                                                                                                                                                                                                                                                                                                                                                                            | 12  | mA    | +125°C     |            | (                                                |  |  |

|                                            | All Devices                         | 17                                                                                                                                                                                                                                                                                                                                                                                           | 19  | mA    | -40°C      |            | Fosc = 10 MHz,                                   |  |  |

|                                            |                                     | 15                                                                                                                                                                                                                                                                                                                                                                                           | 19  | mA    | +25°C      | VDD = 4.2V | 40 MHz internal                                  |  |  |

|                                            |                                     | 15                                                                                                                                                                                                                                                                                                                                                                                           | 19  | mA    | +85°C      |            | (PRI_RUN HS+PLL)                                 |  |  |

|                                            | All Devices                         | 18                                                                                                                                                                                                                                                                                                                                                                                           | 23  | mA    | -40°C      |            | Fosc = 10 MHz,                                   |  |  |

|                                            |                                     | 18                                                                                                                                                                                                                                                                                                                                                                                           | 23  | mA    | +25°C      | VDD = 5.0V | 40 MHz internal                                  |  |  |

|                                            |                                     | 18                                                                                                                                                                                                                                                                                                                                                                                           | 23  | mA    | +85°C      |            | (PRI_RUN HS+PLL)                                 |  |  |

**Legend:** Shading of rows is to assist in readability of the table.

Note 1: The power-down current in Sleep mode does not depend on the oscillator type. Power-down current is measured with the part in Sleep mode, with all I/O pins in high-impedance state and tied to VDD or Vss, and all features that add delta current disabled (such as WDT, Timer1 Oscillator, BOR, etc.).

2: The supply current is mainly a function of operating voltage, frequency and mode. Other factors, such as I/O pin loading and switching rate, oscillator type and circuit, internal code execution pattern and temperature, also have an impact on the current consumption.

The test conditions for all IDD measurements in active operation mode are:

OSC1 = external square wave, from rail-to-rail; all I/O pins tri-stated, pulled to VDD or Vss;

MCLR = VDD; WDT enabled/disabled as specified.

- 3: Low-power, Timer1 oscillator is selected unless otherwise indicated, where LPT1OSC (CONFIG3H<2>) = 1.

- **4:** BOR and HLVD enable internal band gap reference. With both modules enabled, current consumption will be less than the sum of both specifications.

- 5: When operation below -10°C is expected, use T1OSC High-Power mode, where LPT1OSC (CONFIG3H<2>) = 0.

27.2 DC Characteristics: Power-Down and Supply Current

PIC18F2221/2321/4221/4321 (Industrial)

PIC18LF2221/2321/4221/4321 (Industrial) (Continued)

| PIC18LF2221/2321/4221/4321<br>(Industrial)          |                                | Standard Operating Conditions (unless otherwise stated)<br>Operating temperature $-40^{\circ}\text{C} \le \text{TA} \le +85^{\circ}\text{C}$ for industrial                                                                        |          |          |                                        |                 |                 |  |  |

|-----------------------------------------------------|--------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------|----------|----------------------------------------|-----------------|-----------------|--|--|

| PIC18F2221/2321/4221/4321<br>(Industrial, Extended) |                                | Standard Operating Conditions (unless otherwise stated) Operating temperature $-40^{\circ}\text{C} \le \text{Ta} \le +85^{\circ}\text{C}$ for industrial $-40^{\circ}\text{C} \le \text{Ta} \le +125^{\circ}\text{C}$ for extended |          |          |                                        |                 |                 |  |  |

| Param<br>No.                                        | Device                         | Тур                                                                                                                                                                                                                                | Max      | Units    | Conditions                             |                 |                 |  |  |

|                                                     | Module Differential Currer     | nts (∆lw                                                                                                                                                                                                                           | DT, ∆lBC | or, ∆llv | D, $\triangle$ IOSCB, $\triangle$ IAD) |                 |                 |  |  |

| D022                                                | Watchdog Timer                 | 1.6                                                                                                                                                                                                                                | 2.5      | μА       | -40°C                                  |                 |                 |  |  |

| (∆lwdt)                                             |                                | 1.6                                                                                                                                                                                                                                | 2.5      | μА       | +25°C                                  | $V_{DD} = 2.0V$ |                 |  |  |

|                                                     |                                | 1.5                                                                                                                                                                                                                                | 2.5      | μΑ       | +85°C                                  |                 |                 |  |  |

|                                                     |                                | 2.3                                                                                                                                                                                                                                | 3.5      | μΑ       | -40°C                                  |                 |                 |  |  |

|                                                     |                                | 2.2                                                                                                                                                                                                                                | 3.5      | μΑ       | +25°C                                  | VDD = 3.0V      |                 |  |  |

|                                                     |                                | 2.1                                                                                                                                                                                                                                | 3        | μΑ       | +85°C                                  |                 |                 |  |  |

|                                                     |                                | 3.4                                                                                                                                                                                                                                | 7.4      | μΑ       | -40°C                                  |                 |                 |  |  |

|                                                     |                                | 3.9                                                                                                                                                                                                                                | 7.4      | μΑ       | +25°C                                  | Vpp = 5.0V      |                 |  |  |

|                                                     |                                | 4.4                                                                                                                                                                                                                                | 7.4      | μΑ       | +85°C                                  | V DD — 3.0 V    |                 |  |  |

|                                                     |                                | 4.5                                                                                                                                                                                                                                | 7.4      | μΑ       | +125°C                                 |                 |                 |  |  |

| D022A                                               | Brown-out Reset <sup>(4)</sup> | 34                                                                                                                                                                                                                                 | 45       | μΑ       | -40°C to +85°C                         | VDD = 3.0V      |                 |  |  |

| (∆lbor)                                             |                                | 40                                                                                                                                                                                                                                 | 62.6     | μΑ       | -40°C to +85°C                         | VDD = 5.0V      |                 |  |  |

|                                                     |                                | 42                                                                                                                                                                                                                                 | 62.6     | μΑ       | -40°C to +125°C                        | V DD - 3.0 V    |                 |  |  |

|                                                     |                                | 0                                                                                                                                                                                                                                  | 2        | μΑ       | -40°C to +85°C                         | VDD = 3.0V      | Sleep mode,     |  |  |

|                                                     |                                | 0                                                                                                                                                                                                                                  | 5        | μΑ       | -40°C to +125°C                        | VDD = 5.0V      | BOREN<1:0> = 10 |  |  |