#### Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

#### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Product Status             | Active                                                                    |

|----------------------------|---------------------------------------------------------------------------|

| Core Processor             | PIC                                                                       |

| Core Size                  | 8-Bit                                                                     |

| Speed                      | 40MHz                                                                     |

| Connectivity               | I <sup>2</sup> C, SPI, UART/USART                                         |

| Peripherals                | Brown-out Detect/Reset, HLVD, POR, PWM, WDT                               |

| Number of I/O              | 36                                                                        |

| Program Memory Size        | 4KB (2K x 16)                                                             |

| Program Memory Type        | FLASH                                                                     |

| EEPROM Size                | 256 x 8                                                                   |

| RAM Size                   | 512 x 8                                                                   |

| Voltage - Supply (Vcc/Vdd) | 2V ~ 5.5V                                                                 |

| Data Converters            | A/D 13x10b                                                                |

| Oscillator Type            | Internal                                                                  |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                         |

| Mounting Type              | Through Hole                                                              |

| Package / Case             | 40-DIP (0.600", 15.24mm)                                                  |

| Supplier Device Package    | 40-PDIP                                                                   |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic18lf4221-i-p |

|                            |                                                                           |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

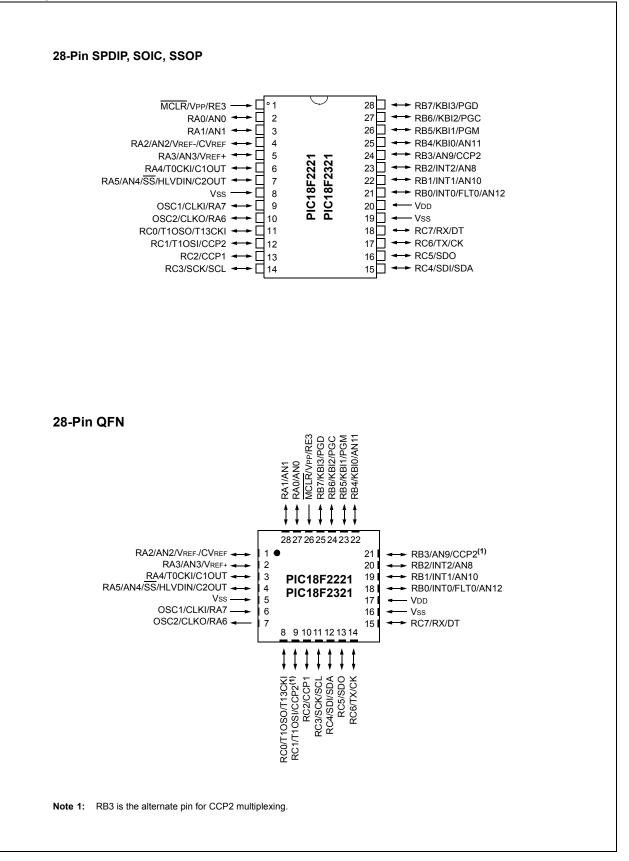

#### **Pin Diagrams**

| TABLE 1-3: PIC1                                                                                                                                                                         |            |     |      | 1 1/01          | JESCRI    |                                                                                                                                                                                       |  |  |

|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------|-----|------|-----------------|-----------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|

| Pin Name                                                                                                                                                                                | Pin Number |     |      | Pin             | Buffer    | Description                                                                                                                                                                           |  |  |

|                                                                                                                                                                                         | PDIP       | QFN | TQFP | Туре            | Туре      | Description                                                                                                                                                                           |  |  |

|                                                                                                                                                                                         |            |     |      |                 |           | PORTD is a bidirectional I/O port or a Parallel Slave<br>Port (PSP) for interfacing to a microprocessor port.<br>These pins have TTL input buffers when the PSP<br>module is enabled. |  |  |

| RD0/PSP0<br>RD0<br>PSP0                                                                                                                                                                 | 19         | 38  | 38   | I/O<br>I/O      | ST<br>TTL | Digital I/O.<br>Parallel Slave Port data.                                                                                                                                             |  |  |

| RD1/PSP1<br>RD1<br>PSP1                                                                                                                                                                 | 20         | 39  | 39   | I/O<br>I/O      | ST<br>TTL | Digital I/O.<br>Parallel Slave Port data.                                                                                                                                             |  |  |

| RD2/PSP2<br>RD2<br>PSP2                                                                                                                                                                 | 21         | 40  | 40   | I/O<br>I/O      | ST<br>TTL | Digital I/O.<br>Parallel Slave Port data.                                                                                                                                             |  |  |

| RD3/PSP3<br>RD3<br>PSP3                                                                                                                                                                 | 22         | 41  | 41   | I/O<br>I/O      | ST<br>TTL | Digital I/O.<br>Parallel Slave Port data.                                                                                                                                             |  |  |

| RD4/PSP4<br>RD4<br>PSP4                                                                                                                                                                 | 27         | 2   | 2    | I/O<br>I/O      | ST<br>TTL | Digital I/O.<br>Parallel Slave Port data.                                                                                                                                             |  |  |

| RD5/PSP5/P1B<br>RD5<br>PSP5<br>P1B                                                                                                                                                      | 28         | 3   | 3    | I/O<br>I/O<br>O | ST<br>TTL | Digital I/O.<br>Parallel Slave Port data.<br>Enhanced CCP1 output.                                                                                                                    |  |  |

| RD6/PSP6/P1C<br>RD6<br>PSP6<br>P1C                                                                                                                                                      | 29         | 4   | 4    | I/O<br>I/O<br>O | ST<br>TTL | Digital I/O.<br>Parallel Slave Port data.<br>Enhanced CCP1 output.                                                                                                                    |  |  |

| RD7/PSP7/P1D<br>RD7<br>PSP7<br>P1D                                                                                                                                                      | 30         | 5   | 5    | I/O<br>I/O<br>O | ST<br>TTL | Digital I/O.<br>Parallel Slave Port data.<br>Enhanced CCP1 output.                                                                                                                    |  |  |

| Legend:TTL = TTL compatible inputCMOS = CMOS compatible input or outputST = Schmitt Trigger input with CMOS levelsI= InputP = Power $I^2C$ = ST with $I^2C^{TM}$ or SMB levelsO= Output |            |     |      |                 |           |                                                                                                                                                                                       |  |  |

#### TABLE 1-3: PIC18F4221/4321 PINOUT I/O DESCRIPTIONS (CONTINUED)

**Note 1:** Default assignment for CCP2 when Configuration bit, CCP2MX, is set.

2: Alternate assignment for CCP2 when Configuration bit, CCP2MX, is cleared.

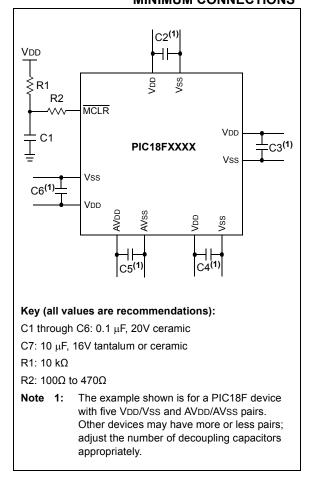

## 2.0 GUIDELINES FOR GETTING STARTED WITH PIC18F MICROCONTROLLERS

### 2.1 Basic Connection Requirements

Getting started with the PIC18F2221/2321/4221/4321 family family of 8-bit microcontrollers requires attention to a minimal set of device pin connections before proceeding with development.

The following pins must always be connected:

- All VDD and Vss pins (see Section 2.2 "Power Supply Pins")

- All AVDD and AVss pins, regardless of whether or not the analog device features are used (see Section 2.2 "Power Supply Pins")

- MCLR pin

(see Section 2.3 "Master Clear (MCLR) Pin")

These pins must also be connected if they are being used in the end application:

- PGC/PGD pins used for In-Circuit Serial Programming<sup>™</sup> (ICSP<sup>™</sup>) and debugging purposes (see **Section 2.4 "ICSP Pins"**)

- OSCI and OSCO pins when an external oscillator source is used

(see Section 2.5 "External Oscillator Pins")

Additionally, the following pins may be required:

• VREF+/VREF- pins used when external voltage reference for analog modules is implemented

| Note: | The AVDD and AVSS pins must always be  |  |  |  |  |  |  |  |

|-------|----------------------------------------|--|--|--|--|--|--|--|

|       | connected, regardless of whether any o |  |  |  |  |  |  |  |

|       | the analog modules are being used.     |  |  |  |  |  |  |  |

The minimum mandatory connections are shown in Figure 2-1.

### FIGURE 2-1: RECOMMENDED MINIMUM CONNECTIONS

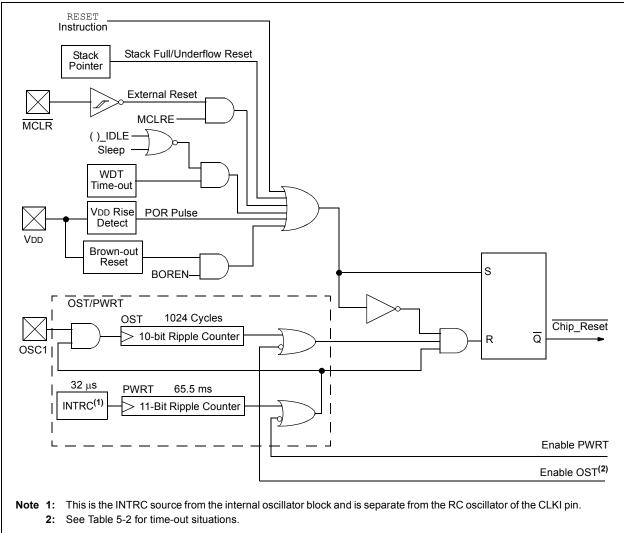

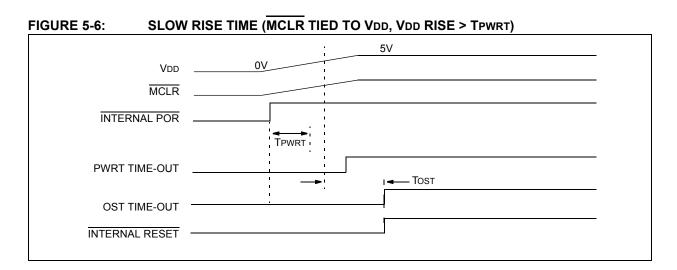

## 5.0 RESET

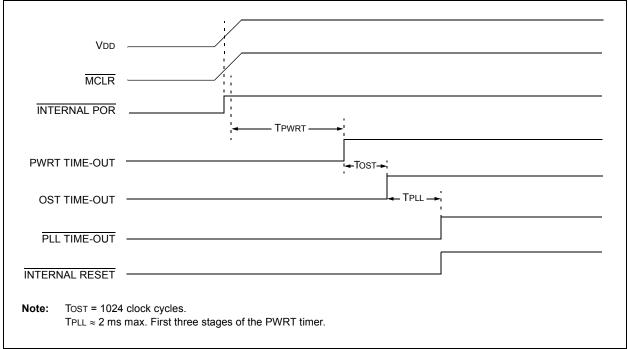

The PIC18F2221/2321/4221/4321 family devices differentiate between various kinds of Reset:

- a) Power-on Reset (POR)

- b) MCLR Reset during normal operation

- c) MCLR Reset during power-managed modes

- d) Watchdog Timer (WDT) Reset (during execution)

- e) Programmable Brown-out Reset (BOR)

- f) RESET Instruction

- g) Stack Full Reset

- h) Stack Underflow Reset

This section discusses Resets generated by MCLR, POR and BOR and covers the operation of the various start-up timers. Stack Reset events are covered in Section 6.1.2.4 "Stack Full and Underflow Resets". WDT Resets are covered in Section 24.2 "Watchdog Timer (WDT)". A simplified block diagram of the On-Chip Reset Circuit is shown in Figure 5-1.

## 5.1 RCON Register

Device Reset events are tracked through the RCON register (Register 5-1). The lower five bits of the register indicate that a specific Reset event has occurred. In most cases, these bits can only be cleared by the event and must be set by the application after the event. The state of these flag bits, taken together, can be read to indicate the type of Reset that just occurred. This is described in more detail in **Section 5.6 "Reset State of Registers"**.

The RCON register also has control bits for setting interrupt priority (IPEN) and software control of the BOR (SBOREN). Interrupt priority is discussed in Section 10.0 "Interrupts". BOR is covered in Section 5.4 "Brown-out Reset (BOR)".

| Register | Aŗ   | oplicabl | e Devic | es   | Power-on Reset,<br>Brown-out Reset | MCLR Resets,<br>WDT Reset,<br>RESET Instruction,<br>Stack Resets | Wake-up via WDT<br>or Interrupt |  |

|----------|------|----------|---------|------|------------------------------------|------------------------------------------------------------------|---------------------------------|--|

| TOSU     | 2221 | 2321     | 4221    | 4321 | 0 0000                             | 0 0000                                                           | 0 uuuu <b>(3)</b>               |  |

| TOSH     | 2221 | 2321     | 4221    | 4321 | 0000 0000                          | 0000 0000                                                        | uuuu uuuu <b>(3)</b>            |  |

| TOSL     | 2221 | 2321     | 4221    | 4321 | 0000 0000                          | 0000 0000                                                        | uuuu uuuu <b>(3)</b>            |  |

| STKPTR   | 2221 | 2321     | 4221    | 4321 | 00-0 0000                          | uu-0 0000                                                        | uu-u uuuu <b>(3)</b>            |  |

| PCLATU   | 2221 | 2321     | 4221    | 4321 | 00 0000                            | 00 0000                                                          | uu uuuu                         |  |

| PCLATH   | 2221 | 2321     | 4221    | 4321 | 0000 0000                          | 0000 0000                                                        | սսսս սսսս                       |  |

| PCL      | 2221 | 2321     | 4221    | 4321 | 0000 0000                          | 0000 0000                                                        | PC + 2 <sup>(2)</sup>           |  |

| TBLPTRU  | 2221 | 2321     | 4221    | 4321 | 00 0000                            | 00 0000                                                          | uu uuuu                         |  |

| TBLPTRH  | 2221 | 2321     | 4221    | 4321 | 0000 0000                          | 0000 0000                                                        | uuuu uuuu                       |  |

| TBLPTRL  | 2221 | 2321     | 4221    | 4321 | 0000 0000                          | 0000 0000                                                        | uuuu uuuu                       |  |

| TABLAT   | 2221 | 2321     | 4221    | 4321 | 0000 0000                          | 0000 0000                                                        | uuuu uuuu                       |  |

| PRODH    | 2221 | 2321     | 4221    | 4321 | XXXX XXXX                          | սսսս սսսս                                                        | uuuu uuuu                       |  |

| PRODL    | 2221 | 2321     | 4221    | 4321 | XXXX XXXX                          | uuuu uuuu                                                        | uuuu uuuu                       |  |

| INTCON   | 2221 | 2321     | 4221    | 4321 | 0000 000x                          | 0000 000u                                                        | uuuu uuuu <b>(1)</b>            |  |

| INTCON2  | 2221 | 2321     | 4221    | 4321 | 1111 -1-1                          | 1111 -1-1                                                        | uuuu -u-u <b>(1)</b>            |  |

| INTCON3  | 2221 | 2321     | 4221    | 4321 | 11-0 0-00                          | 11-0 0-00                                                        | uu-u u-uu <b>(1)</b>            |  |

| INDF0    | 2221 | 2321     | 4221    | 4321 | N/A                                | N/A                                                              | N/A                             |  |

| POSTINC0 | 2221 | 2321     | 4221    | 4321 | N/A                                | N/A                                                              | N/A                             |  |

| POSTDEC0 | 2221 | 2321     | 4221    | 4321 | N/A                                | N/A                                                              | N/A                             |  |

| PREINC0  | 2221 | 2321     | 4221    | 4321 | N/A                                | N/A                                                              | N/A                             |  |

| PLUSW0   | 2221 | 2321     | 4221    | 4321 | N/A                                | N/A                                                              | N/A                             |  |

| FSR0H    | 2221 | 2321     | 4221    | 4321 | 0000                               | 0000                                                             | uuuu                            |  |

| FSR0L    | 2221 | 2321     | 4221    | 4321 | XXXX XXXX                          | นนนน นนนน                                                        | սսսս սսսս                       |  |

| WREG     | 2221 | 2321     | 4221    | 4321 | XXXX XXXX                          | นนนน นนนน                                                        | սսսս սսսս                       |  |

| INDF1    | 2221 | 2321     | 4221    | 4321 | N/A                                | N/A                                                              | N/A                             |  |

| POSTINC1 | 2221 | 2321     | 4221    | 4321 | N/A                                | N/A                                                              | N/A                             |  |

| POSTDEC1 | 2221 | 2321     | 4221    | 4321 | N/A                                | N/A                                                              | N/A                             |  |

| PREINC1  | 2221 | 2321     | 4221    | 4321 | N/A                                | N/A                                                              | N/A                             |  |

| PLUSW1   | 2221 | 2321     | 4221    | 4321 | N/A                                | N/A                                                              | N/A                             |  |

#### TABLE 5-4: INITIALIZATION CONDITIONS FOR ALL REGISTERS

**Legend:** u = unchanged, x = unknown, - = unimplemented bit, read as '0', q = value depends on condition. Shaded cells indicate conditions do not apply for the designated device.

Note 1: One or more bits in the INTCONx or PIRx registers will be affected (to cause wake-up).

2: When the wake-up is due to an interrupt and the GIEL or GIEH bit is set, the PC is loaded with the interrupt vector (0008h or 0018h).

**3:** When the wake-up is due to an interrupt and the GIEL or GIEH bit is set, the TOSU, TOSH and TOSL are updated with the current value of the PC. The STKPTR is modified to point to the next location in the hardware stack.

4: See Table 5-3 for Reset value for specific condition.

**5:** Bits 6 and 7 of PORTA, LATA and TRISA are enabled, depending on the oscillator mode selected. When not enabled as PORTA pins, they are disabled and read '0'.

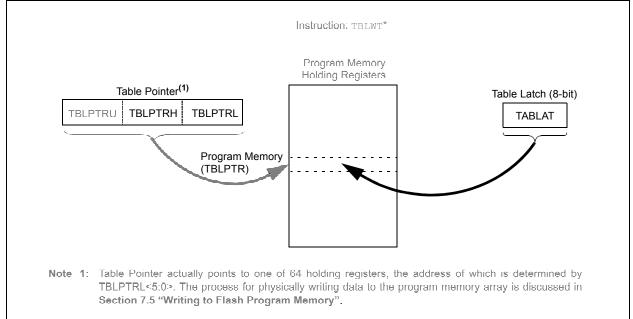

### FIGURE 7-2: TABLE WRITE OPERATION

## 7.2 Control Registers

Several control registers are used in conjunction with the  ${\tt TBLRD}$  and  ${\tt TBLWT}$  instructions. These include the:

- EECON1 register

- · EECON2 register

- TABLAT register

- TBLPTR registers

#### 7.2.1 EECON1 AND EECON2 REGISTERS

The EECON1 register (Register 7-1) is the control register for memory accesses. The EECON2 register is not a physical register; it is used exclusively in the memory write and erase sequences. Reading EECON2 will read all '0's.

The EEPGD control bit determines if the access will be a program or data EEPROM memory access. When clear, any subsequent operations will operate on the data EEPROM memory. When set, any subsequent operations will operate on the program memory.

The CFGS control bit determines if the access will be to the Configuration/Calibration registers or to program memory/data EEPROM memory. When set, subsequent operations will operate on Configuration registers regardless of EEPGD (see **Section 24.0 "Special Features of the CPU"**). When clear, memory selection access is determined by EEPGD. The FREE bit, when set, will allow a program memory erase operation. When FREE is set, the erase operation is initiated on the next WR command. When FREE is clear, only writes are enabled.

The WREN bit, when set, will allow a write operation. On power-up, the WREN bit is clear. The WRERR bit is set in hardware when the WR bit is set and cleared when the internal programming timer expires and the write operation is complete.

| Note: | During normal operation, the WRERR bit     |  |  |  |  |  |  |  |

|-------|--------------------------------------------|--|--|--|--|--|--|--|

|       | may read as '1'. This can indicate that a  |  |  |  |  |  |  |  |

|       | write operation was prematurely termi-     |  |  |  |  |  |  |  |

|       | nated by a Reset, or a write operation was |  |  |  |  |  |  |  |

|       | attempted improperly.                      |  |  |  |  |  |  |  |

The WR control bit initiates write operations. The bit cannot be cleared, only set, in software; it is cleared in hardware at the completion of the write operation.

| Note: | The EEIF interrupt flag bit (PIR2<4>) is set |

|-------|----------------------------------------------|

|       | when the write is complete. It must be       |

|       | cleared in software.                         |

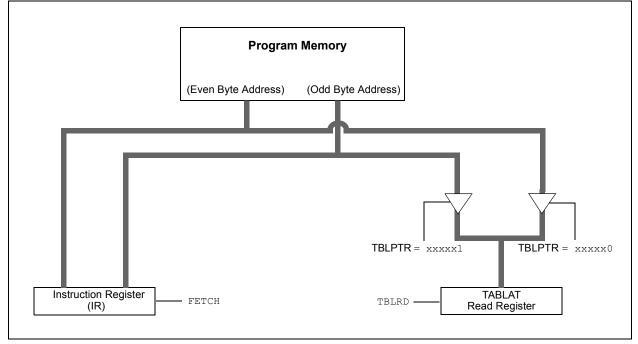

#### 7.3 Reading the Flash Program Memory

The TBLRD instruction is used to retrieve data from program memory and place it into data RAM. Table reads from program memory are performed one byte at a time.

TBLPTR points to a byte address in program space. Executing TBLRD places the byte pointed to into TABLAT. In addition, TBLPTR can be modified automatically for the next table read operation.

The internal program memory is typically organized by words. The Least Significant bit of the address selects between the high and low bytes of the word. Figure 7-4 shows the interface between the internal program memory and the TABLAT.

#### FIGURE 7-4: READS FROM FLASH PROGRAM MEMORY

#### EXAMPLE 7-1: READING A FLASH PROGRAM MEMORY WORD

|           | MOVLW<br>MOVWF<br>MOVLW<br>MOVWF | CODE_ADDR_UPPER<br>TBLPTRU<br>CODE_ADDR_HIGH<br>TBLPTRH |   | Load TBLPTR with the base<br>address of the word |

|-----------|----------------------------------|---------------------------------------------------------|---|--------------------------------------------------|

|           | MOVLW                            | CODE ADDR LOW                                           |   |                                                  |

|           | MOVWF                            | TBLPTRL                                                 |   |                                                  |

| READ_WORD |                                  |                                                         |   |                                                  |

|           | TBLRD*+                          |                                                         | ; | read into TABLAT and increment                   |

|           | MOVF                             | TABLAT, W                                               | ; | get data                                         |

|           | MOVWF                            | WORD_EVEN                                               |   |                                                  |

|           | TBLRD*+                          |                                                         | ; | read into TABLAT and increment                   |

|           | MOVF                             | TABLAT, W                                               | ; | get data                                         |

|           | MOVWF                            | WORD_ODD                                                |   |                                                  |

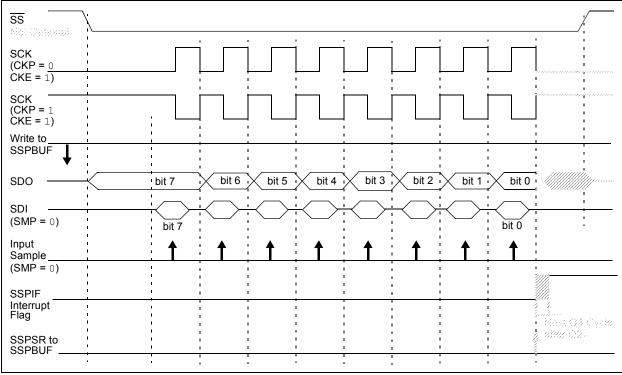

#### 18.3.6 SLAVE MODE

In Slave mode, the data is transmitted and received as the external clock pulses appear on SCK. When the last bit is latched, the SSPIF interrupt flag bit is set.

Before enabling the module in SPI Slave mode, the clock line must match the proper Idle state. The clock line can be observed by reading the SCK pin. The Idle state is determined by the CKP bit (SSPCON1<4>).

While in Slave mode, the external clock is supplied by the external clock source on the SCK pin. This external clock must meet the minimum high and low times as specified in the electrical specifications.

While in Sleep mode, the slave can transmit/receive data. When a byte is received, the device will wake-up from Sleep.

#### 18.3.7 SLAVE SELECT SYNCHRONIZATION

The  $\overline{SS}$  pin allows a Synchronous Slave mode. The SPI operation must be in Slave mode with the  $\overline{SS}$  pin control enabled (SSPCON1<3:0> = 04h). When the  $\overline{SS}$  pin is low, transmission and reception are enabled and the

SDO pin is driven. When the  $\overline{SS}$  pin goes high, the SDO pin is no longer driven, even if in the middle of a transmitted byte and becomes a floating output. External pull-up/pull-down resistors may be desirable depending on the application.

| Note 1: | When                                     | When the SPI interface is in Slave mode |        |               |         |  |  |  |  |  |  |

|---------|------------------------------------------|-----------------------------------------|--------|---------------|---------|--|--|--|--|--|--|

|         | with                                     | SS                                      | pin    | control       | enabled |  |  |  |  |  |  |

|         | (SSPCON1 < 3:0 > = 0100), the SPI module |                                         |        |               |         |  |  |  |  |  |  |

|         | will res                                 | et if the                               | SS pir | n is set to V | DD.     |  |  |  |  |  |  |

2: If the SPI interface is used in Slave mode with CKE set, then the SS pin control must be enabled.

When the SPI module resets, the bit counter is forced to '0'. This can be done by either forcing the  $\overline{SS}$  pin to a high level or clearing the SSPEN bit.

To emulate two-wire communication, the SDO pin can be connected to the SDI pin. When the SPI needs to operate as a receiver, the SDO pin can be configured as an input. This disables transmissions from the SDO. The SDI can always be left as an input (SDI function) since it cannot create a bus conflict.

#### FIGURE 18-4: SLAVE SYNCHRONIZATION WAVEFORM

| FIGURE 18-5:                                                      | SPI N                 | IODE W      | /AVEFO                                       | RM (SL                | AVE MC                | DE WIT      | H CKE :               | = 0)                                          |   |                                  |            |

|-------------------------------------------------------------------|-----------------------|-------------|----------------------------------------------|-----------------------|-----------------------|-------------|-----------------------|-----------------------------------------------|---|----------------------------------|------------|

| -<br>SS<br>Opäend                                                 | •<br>•<br>•           |             |                                              |                       |                       |             |                       |                                               |   |                                  | <br>       |

| 90X<br>(CRP = 0<br>(CRS = 0)                                      |                       |             |                                              |                       |                       |             |                       |                                               |   |                                  |            |

| 497°Z                                                             | :<br>4                |             | ·<br>·<br>·                                  | ·<br>·<br>·           |                       | ·<br>·      |                       | ·<br>:<br>: ······                            |   |                                  | 3<br>3<br> |

| (CR49 + 1<br>OKE + 0)                                             | :<br>:<br>:           |             |                                              |                       |                       |             |                       |                                               |   |                                  |            |

| Véla la<br>SSPSUF                                                 |                       | •           | 2<br>2<br>2<br>2                             | :<br>:<br>:<br>:      | e<br>Garana<br>E<br>E | •           | 2<br>2<br>2           | ·<br>                                         | ( |                                  | *<br>      |

| 9870                                                              |                       | K 158 V     | <br>X                                        | X 58.6                |                       | X68.3       | X 68.0                |                                               |   | <u>(3</u> 3-6)                   |            |

| 809<br>(9849 = 0)                                                 | ·<br>·<br>·<br>·<br>· |             |                                              | dijijijijiji          |                       |             |                       |                                               |   |                                  | *<br>1<br> |

| inguja<br>Samagoiae                                               | -<br>-<br>-<br>       |             | ,<br>, , , , , , , , , , , , , , , , , , ,   | . 49.                 |                       |             |                       |                                               |   | <i>a</i> .                       |            |

| (53492 == 0)<br>(5389299<br>===============<br>================== | :<br>:<br>:           |             | -<br>5<br>5<br>5<br>5                        | e<br>•<br>•<br>•<br>• | -<br>5<br>5<br>6<br>6 | :<br>:      | ·<br>5<br>5<br>5<br>5 | ,<br>,<br>;<br>;                              |   | Next ()                          |            |

| SSPSR 5<br>SSPSRF                                                 | ,<br>,<br>6           | •<br>•<br>• | )<br>)<br>////////////////////////////////// | :<br>:<br>            | t<br>t<br>5           | •<br>•<br>• | )<br>;<br>,           | :<br>:<br>· · · · · · · · · · · · · · · · · · |   | 2002 (22<br>2022 (22<br>2023 (22 |            |

### FIGURE 18-6: SPI MODE WAVEFORM (SLAVE MODE WITH CKE = 1)

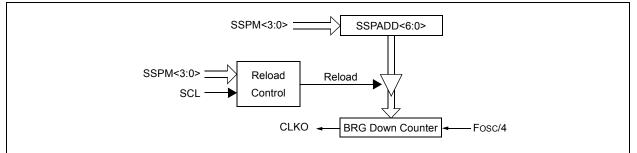

#### 18.4.7 BAUD RATE

In I<sup>2</sup>C Master mode, the Baud Rate Generator (BRG) reload value is placed in the lower 7 bits of the SSPADD register (Figure 18-19). When a write occurs to SSPBUF, the Baud Rate Generator will automatically begin counting. The BRG counts down to 0 and stops until another reload has taken place. The BRG count is decremented twice per instruction cycle (TcY) on the Q2 and Q4 clocks. In I<sup>2</sup>C Master mode, the BRG is reloaded automatically.

Once the given operation is complete (i.e., transmission of the last data bit is followed by ACK), the internal clock will automatically stop counting and the SCL pin will remain in its last state.

Table 18-3 demonstrates clock rates based on instruction cycles and the BRG value loaded into SSPADD.

#### FIGURE 18-19: BAUD RATE GENERATOR BLOCK DIAGRAM

#### TABLE 18-3: I<sup>2</sup>C<sup>™</sup> CLOCK RATE W/BRG

| Fosc   | Fcy    | Fcy * 2 | BRG Value | FscL<br>(2 Rollovers of BRG) |

|--------|--------|---------|-----------|------------------------------|

| 40 MHz | 10 MHz | 20 MHz  | 18h       | 400 kHz                      |

| 40 MHz | 10 MHz | 20 MHz  | 1Fh       | 312.5 kHz                    |

| 40 MHz | 10 MHz | 20 MHz  | 63h       | 100 kHz                      |

| 16 MHz | 4 MHz  | 8 MHz   | 09h       | 400 kHz                      |

| 16 MHz | 4 MHz  | 8 MHz   | 0Ch       | 308 kHz                      |

| 16 MHz | 4 MHz  | 8 MHz   | 27h       | 100 kHz                      |

| 4 MHz  | 1 MHz  | 2 MHz   | 02h       | 333 kHz                      |

| 4 MHz  | 1 MHz  | 2 MHz   | 09h       | 100 kHz                      |

| 4 MHz  | 1 MHz  | 2 MHz   | 00h       | 1 MHz                        |

| REGISTER 19-2: | RCSTA: R                  |                                                                                                                                                     | TATUS AN       |                |              | TER           |              |              |  |  |  |  |  |

|----------------|---------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------|----------------|----------------|--------------|---------------|--------------|--------------|--|--|--|--|--|

|                | R/W-0                     | R/W-0                                                                                                                                               | R/W-0          | R/W-0          | R/W-0        | R-0           | R-0          | R-x          |  |  |  |  |  |

|                | SPEN                      | RX9                                                                                                                                                 | SREN           | CREN           | ADDEN        | FERR          | OERR         | RX9D         |  |  |  |  |  |

|                | bit 7                     |                                                                                                                                                     |                |                |              |               |              | bit 0        |  |  |  |  |  |

| bit 7          |                           | ial Dart Enal                                                                                                                                       | bla bit        |                |              |               |              |              |  |  |  |  |  |

| bit 7          |                           | ial Port Enal                                                                                                                                       |                | DV/DT and      | TV/CK pipe   | an aprial pa  | rt nina)     |              |  |  |  |  |  |

|                |                           | <ul> <li>1 = Serial port enabled (configures RX/DT and TX/CK pins as serial port pins)</li> <li>0 = Serial port disabled (held in Reset)</li> </ul> |                |                |              |               |              |              |  |  |  |  |  |

| bit 6          | <b>RX9:</b> 9-bit         | X9: 9-bit Receive Enable bit                                                                                                                        |                |                |              |               |              |              |  |  |  |  |  |

|                |                           | <ul> <li>1 = Selects 9-bit reception</li> <li>0 = Selects 8-bit reception</li> </ul>                                                                |                |                |              |               |              |              |  |  |  |  |  |

| bit 5          | SREN: Sin                 | REN: Single Receive Enable bit                                                                                                                      |                |                |              |               |              |              |  |  |  |  |  |

|                |                           | Asynchronous mode:<br>Don't care.<br>Synchronous mode – Master:                                                                                     |                |                |              |               |              |              |  |  |  |  |  |

|                | Synchrono                 |                                                                                                                                                     |                |                |              |               |              |              |  |  |  |  |  |

|                |                           | 1 = Enables single receive                                                                                                                          |                |                |              |               |              |              |  |  |  |  |  |

|                |                           | es single rec                                                                                                                                       |                |                |              |               |              |              |  |  |  |  |  |

|                |                           | leared after                                                                                                                                        | -              | complete.      |              |               |              |              |  |  |  |  |  |

|                | Don't care.               | <u>us mode – S</u>                                                                                                                                  | <u>blave:</u>  |                |              |               |              |              |  |  |  |  |  |

| bit 4          |                           | ntinuous Re                                                                                                                                         | ceive Enable   | e bit          |              |               |              |              |  |  |  |  |  |

|                | Asynchron                 |                                                                                                                                                     |                |                |              |               |              |              |  |  |  |  |  |

|                | 1 = Enable                |                                                                                                                                                     |                |                |              |               |              |              |  |  |  |  |  |

|                | 0 = Disable               | es receiver                                                                                                                                         |                |                |              |               |              |              |  |  |  |  |  |

|                | Synchrono                 |                                                                                                                                                     |                |                | ODEN         |               |              |              |  |  |  |  |  |

|                |                           | s continuous<br>es continuou                                                                                                                        |                | til enable bit | CREN is cle  | eared (CREI   | N overrides  | SREN)        |  |  |  |  |  |

| bit 3          |                           | ddress Dete                                                                                                                                         |                | t              |              |               |              |              |  |  |  |  |  |

| bit o          |                           | ous mode 9-                                                                                                                                         |                |                |              |               |              |              |  |  |  |  |  |

|                |                           |                                                                                                                                                     |                |                | upt and load | s the receiv  | e buffer whe | en RSR<8>    |  |  |  |  |  |

|                | 0 = Disabl                | es address o                                                                                                                                        | detection, all | bytes are r    | eceived and  | ninth bit car | n be used as | s parity bit |  |  |  |  |  |

|                |                           | ous mode 9-                                                                                                                                         | bit (RX9 = c   | ) <u>):</u>    |              |               |              |              |  |  |  |  |  |

|                | Don't care.               |                                                                                                                                                     |                |                |              |               |              |              |  |  |  |  |  |

| bit 2          |                           | ming Error b                                                                                                                                        |                |                |              |               |              |              |  |  |  |  |  |

|                | 1 = Framin<br>0 = No fran |                                                                                                                                                     | be updated     | by reading     | RCREG regi   | ister and rec | eiving next  | valid byte)  |  |  |  |  |  |

| bit 1          | OERR: OV                  | errun Error b                                                                                                                                       | pit            |                |              |               |              |              |  |  |  |  |  |

|                |                           | n error (can                                                                                                                                        | be cleared b   | by clearing b  | oit CREN)    |               |              |              |  |  |  |  |  |

|                | 0 = No ove                |                                                                                                                                                     |                |                |              |               |              |              |  |  |  |  |  |

| bit 0          |                           | bit of Receiv                                                                                                                                       |                |                |              |               | <b>C</b>     | _            |  |  |  |  |  |

|                | I his can be              | e address/da                                                                                                                                        | ata bit or a p | arity bit and  | must be cal  | culated by u  | ser tirmware | 9.           |  |  |  |  |  |

|                | Legend:                   |                                                                                                                                                     |                |                |              |               |              |              |  |  |  |  |  |

|                | R = Reada                 | ble bit                                                                                                                                             | W = W          | /ritable bit   | U = Unin     | nplemented    | bit, read as | ʻ0'          |  |  |  |  |  |

|                | -n = Value                |                                                                                                                                                     | '1' = B        | it is set      |              | s cleared     | x = Bit is u |              |  |  |  |  |  |

|                |                           |                                                                                                                                                     | i – D          |                |              |               |              |              |  |  |  |  |  |

#### 19.4.2 EUSART SYNCHRONOUS SLAVE RECEPTION

The operation of the Synchronous Master and Slave modes is identical, except in the case of Sleep, or any Idle mode and bit SREN, which is a "don't care" in Slave mode.

If receive is enabled by setting the CREN bit prior to entering Sleep or any Idle mode, then a word may be received while in this low-power mode. Once the word is received, the RSR register will transfer the data to the RCREG register; if the RCIE enable bit is set, the interrupt generated will wake the chip from the lowpower mode. If the global interrupt is enabled, the program will branch to the interrupt vector. To set up a Synchronous Slave Reception:

- Enable the synchronous master serial port by setting bits, SYNC and SPEN, and clearing bit, CSRC.

- 2. If interrupts are desired, set enable bit RCIE.

- 3. If the signal from the CK pin is to be inverted, set the TXCKP bit.

- 4. If 9-bit reception is desired, set bit, RX9.

- 5. To enable reception, set enable bit, CREN.

- Flag bit, RCIF, will be set when reception is complete. An interrupt will be generated if enable bit, RCIE, was set.

- 7. Read the RCSTA register to get the 9th bit (if enabled) and determine if any error occurred during reception.

- 8. Read the 8-bit received data by reading the RCREG register.

- 9. If any error occurred, clear the error by clearing bit, CREN.

- 10. If using interrupts, ensure that the GIE and PEIE bits in the INTCON register (INTCON<7:6>) are set.

| Name    | Bit 7                | Bit 6        | Bit 5       | Bit 4        | Bit 3 | Bit 2  | Bit 1  | Bit 0  | Reset<br>Values<br>on page |

|---------|----------------------|--------------|-------------|--------------|-------|--------|--------|--------|----------------------------|

| INTCON  | GIE/GIEH             | PEIE/GIEL    | TMR0IE      | INT0IE       | RBIE  | TMR0IF | INT0IF | RBIF   | 55                         |

| PIR1    | PSPIF <sup>(1)</sup> | ADIF         | RCIF        | TXIF         | SSPIF | CCP1IF | TMR2IF | TMR1IF | 58                         |

| PIE1    | PSPIE <sup>(1)</sup> | ADIE         | RCIE        | TXIE         | SSPIE | CCP1IE | TMR2IE | TMR1IE | 58                         |

| IPR1    | PSPIP <sup>(1)</sup> | ADIP         | RCIP        | TXIP         | SSPIP | CCP1IP | TMR2IP | TMR1IP | 58                         |

| RCSTA   | SPEN                 | RX9          | SREN        | CREN         | ADDEN | FERR   | OERR   | RX9D   | 57                         |

| RCREG   | EUSART F             | Receive Regi | ster        |              |       |        |        |        | 57                         |

| TXSTA   | CSRC                 | TX9          | TXEN        | SYNC         | SENDB | BRGH   | TRMT   | TX9D   | 57                         |

| BAUDCON | ABDOVF               | RCIDL        | RXDTP       | TXCKP        | BRG16 | —      | WUE    | ABDEN  | 57                         |

| SPBRGH  | EUSART E             | aud Rate G   | enerator Re | gister High  | Byte  |        |        |        | 57                         |

| SPBRG   | EUSART E             | aud Rate G   | enerator Re | gister Low I | Byte  |        |        |        | 57                         |

#### TABLE 19-10: REGISTERS ASSOCIATED WITH SYNCHRONOUS SLAVE RECEPTION

Legend: — = unimplemented, read as '0'. Shaded cells are not used for synchronous slave reception.

Note 1: These bits are unimplemented on 28-pin devices and read as '0'.

### 23.6 Operation During Sleep

When enabled, the HLVD circuitry continues to operate during Sleep. If the device voltage crosses the trip point, the HLVDIF bit will be set and the device will wake-up from Sleep. Device execution will continue from the interrupt vector address if interrupts have been globally enabled.

#### 23.7 Effects of a Reset

A device Reset forces all registers to their Reset state. This forces the HLVD module to be turned off.

| Name    | Bit 7    | Bit 6     | Bit 5  | Bit 4  | Bit 3  | Bit 2  | Bit 1  | Bit 0  | Reset<br>Values<br>on Page |

|---------|----------|-----------|--------|--------|--------|--------|--------|--------|----------------------------|

| HLVDCON | VDIRMAG  |           | IRVST  | HLVDEN | HLVDL3 | HLVDL2 | HLVDL1 | HLVDL0 | 56                         |

| INTCON  | GIE/GIEH | PEIE/GIEL | TMR0IE | INT0IE | RBIE   | TMR0IF | INT0IF | RBIF   | 55                         |

| PIR2    | OSCFIF   | CMIF      | —      | EEIF   | BCLIF  | HLVDIF | TMR3IF | CCP2IF | 58                         |

| PIE2    | OSCFIE   | CMIE      | _      | EEIE   | BCLIE  | HLVDIE | TMR3IE | CCP2IE | 58                         |

| IPR2    | OSCFIP   | CMIP      |        | EEIP   | BCLIP  | HLVDIP | TMR3IP | CCP2IP | 58                         |

#### TABLE 23-1: REGISTERS ASSOCIATED WITH HIGH/LOW-VOLTAGE DETECT MODULE

Legend: — = unimplemented, read as '0'. Shaded cells are unused by the HLVD module.

#### TABLE 25-2: PIC18FXXXX INSTRUCTION SET

| Mnemo    | onic,                           | Description                              | Qualas     | 16-Bit Instruction Word |       |      |      | Status          | Nataa      |

|----------|---------------------------------|------------------------------------------|------------|-------------------------|-------|------|------|-----------------|------------|

| Opera    | nds                             | Description                              | Cycles     | MSb                     |       |      | LSb  | Affected        | Notes      |

| BYTE-ORI | ENTED (                         | OPERATIONS                               |            |                         |       |      |      |                 |            |

| ADDWF    | f, d, a                         | Add WREG and f                           | 1          | 0010                    | 01da0 | ffff | ffff | C, DC, Z, OV, N | 1, 2       |

| ADDWFC   | f, d, a                         | Add WREG and Carry bit to f              | 1          | 0010                    | 0da   | ffff | ffff | C, DC, Z, OV, N | 1, 2       |

| ANDWF    | f, d, a                         | AND WREG with f                          | 1          | 0001                    | 01da  | ffff | ffff | Z, N            | 1,2        |

| CLRF     | f, a                            | Clear f                                  | 1          | 0110                    | 101a  | ffff | ffff | Z               | 2          |

| COMF     | f, d, a                         | Complement f                             | 1          | 0001                    | 11da  | ffff | ffff | Z, N            | 1, 2       |

| CPFSEQ   | f, a                            | Compare f with WREG, Skip =              | 1 (2 or 3) | 0110                    | 001a  | ffff | ffff | None            | 4          |

| CPFSGT   | f, a                            | Compare f with WREG, Skip >              | 1 (2 or 3) | 0110                    | 010a  | ffff | ffff | None            | 4          |

| CPFSLT   | f, a                            | Compare f with WREG, Skip <              | 1 (2 or 3) | 0110                    | 000a  | ffff | ffff | None            | 1, 2       |

| DECF     | f, d, a                         | Decrement f                              | 1          | 0000                    | 01da  | ffff | ffff | C, DC, Z, OV, N | 1, 2, 3, 4 |

| DECFSZ   | f, d, a                         | Decrement f, Skip if 0                   | 1 (2 or 3) | 0010                    | 11da  | ffff | ffff | None            | 1, 2, 3, 4 |

| DCFSNZ   | f, d, a                         | Decrement f, Skip if Not 0               | 1 (2 or 3) | 0100                    | 11da  | ffff | ffff | None            | 1, 2       |

| INCF     | f, d, a                         | Increment f                              | 1          | 0010                    | 10da  | ffff | ffff | C, DC, Z, OV, N | 1, 2, 3, 4 |

| INCFSZ   | f, d, a                         | Increment f, Skip if 0                   | 1 (2 or 3) | 0011                    | 11da  | ffff | ffff | None            | 4          |

| INFSNZ   | f, d, a                         | Increment f, Skip if Not 0               | 1 (2 or 3) | 0100                    | 10da  | ffff | ffff | None            | 1, 2       |

| IORWF    | f, d, a                         | Inclusive OR WREG with f                 | 1          | 0001                    | 00da  | ffff | ffff | Z, N            | 1, 2       |

| MOVF     | f, d, a                         | Move f                                   | 1          | 0101                    | 00da  | ffff | ffff | Z, N            | 1          |

| MOVFF    | f <sub>s</sub> , f <sub>d</sub> | Move f <sub>s</sub> (source) to 1st Word | 2          | 1100                    | ffff  | ffff | ffff | None            |            |

|          |                                 | f <sub>d</sub> (destination) 2nd Word    |            | 1111                    | ffff  | ffff | ffff |                 |            |

| MOVWF    | f, a                            | Move WREG to f                           | 1          | 0110                    | 111a  | ffff | ffff | None            |            |

| MULWF    | f, a                            | Multiply WREG with f                     | 1          | 0000                    | 001a  | ffff | ffff | None            | 1, 2       |

| NEGF     | f, a                            | Negate f                                 | 1          | 0110                    | 110a  | ffff | ffff | C, DC, Z, OV, N |            |

| RLCF     | f, d, a                         | Rotate Left f through Carry              | 1          | 0011                    | 01da  | ffff | ffff | C, Z, N         | 1, 2       |

| RLNCF    | f, d, a                         | Rotate Left f (No Carry)                 | 1          | 0100                    | 01da  | ffff | ffff | Z, N            |            |

| RRCF     | f, d, a                         | Rotate Right f through Carry             | 1          | 0011                    | 00da  | ffff | ffff | C, Z, N         |            |

| RRNCF    | f, d, a                         | Rotate Right f (No Carry)                | 1          | 0100                    | 00da  | ffff | ffff | Z, N            |            |

| SETF     | f, a                            | Set f                                    | 1          | 0110                    | 100a  | ffff | ffff | None            | 1, 2       |

| SUBFWB   | f, d, a                         | Subtract f from WREG with<br>Borrow      | 1          | 0101                    | 01da  | ffff | ffff | C, DC, Z, OV, N |            |

| SUBWF    | f, d, a                         | Subtract WREG from f                     | 1          | 0101                    | 11da  | ffff | ffff | C, DC, Z, OV, N | 1, 2       |

| SUBWFB   | f, d, a                         | Subtract WREG from f with                | 1          | 0101                    | 10da  | ffff | ffff | C, DC, Z, OV, N |            |

|          | , . , .                         | Borrow                                   |            |                         |       |      |      | , _, , _ , .    |            |

| SWAPF    | f, d, a                         | Swap Nibbles in f                        | 1          | 0011                    | 10da  | ffff | ffff | None            | 4          |

| TSTFSZ   | f, a                            | Test f, Skip if 0                        | 1 (2 or 3) | 0110                    | 011a  | ffff | ffff | None            | 1, 2       |

| XORWF    | f, d, a                         | Exclusive OR WREG with f                 | 1          | 0001                    | 10da  | ffff | ffff | Z, N            | ,          |

**Note 1:** When a PORT register is modified as a function of itself (e.g., MOVF PORTB, 1, 0), the value used will be that value present on the pins themselves. For example, if the data latch is '1' for a pin configured as input and is driven low by an external device, the data will be written back with a '0'.

2: If this instruction is executed on the TMR0 register (and where applicable, 'd' = 1), the prescaler will be cleared if assigned.

3: If the Program Counter (PC) is modified or a conditional test is true, the instruction requires two cycles. The second cycle is executed as a NOP.

4: Some instructions are two-word instructions. The second word of these instructions will be executed as a NOP unless the first word of the instruction retrieves the information embedded in these 16 bits. This ensures that all program memory locations have a valid instruction.

| CLRF                                                | Clear f                                                                                                                         |                                |                       | CLRWDT                                                                                                       | Clear Wat                                                    | tchdog Time    | ər          |  |  |

|-----------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------|--------------------------------|-----------------------|--------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------|----------------|-------------|--|--|

| Syntax:                                             | CLRF f{,a                                                                                                                       | }                              |                       | Syntax:                                                                                                      | CLRWDT                                                       |                |             |  |  |

| Operands:                                           | $0 \leq f \leq 255$                                                                                                             | $0 \leq f \leq 255$            |                       |                                                                                                              | None                                                         | None           |             |  |  |

|                                                     | <b>a</b> ∈[0,1]                                                                                                                 |                                |                       | Operation:                                                                                                   | $000h \rightarrow Wl$                                        | ,              |             |  |  |

| Operation:                                          | $\begin{array}{l} 000h \rightarrow f, \\ 1 \rightarrow Z \end{array}$                                                           |                                |                       |                                                                                                              | $000h \rightarrow Wl$ $1 \rightarrow TO,$ $1 \rightarrow PD$ | DT postscaler, |             |  |  |

| Status Affected:                                    | Z                                                                                                                               |                                |                       | Status Affected:                                                                                             | $T \rightarrow PD$<br>TO, PD                                 |                |             |  |  |

| Encoding:                                           | 0110                                                                                                                            | 101a fff                       | ff ffff               |                                                                                                              |                                                              |                | 0.0.0.1.0.0 |  |  |

| Description:                                        |                                                                                                                                 | ontents of the                 | specified             | Encoding:                                                                                                    | 0000                                                         | 0000 00        |             |  |  |

|                                                     | register.<br>If 'a' is '0', the Access Bank is selected.<br>If 'a' is '1', the BSR is used to select the<br>GPR bank (default). |                                |                       | Description: CLRWDT instruction res<br>Watchdog Timer. It also<br>postscaler of the WDT.<br>and PD, are set. |                                                              |                | resets the  |  |  |

|                                                     |                                                                                                                                 | nd the extende                 |                       | Words:                                                                                                       | 1                                                            |                |             |  |  |

|                                                     |                                                                                                                                 | iteral Offset A                | tion operates         | Cycles:                                                                                                      | 1                                                            |                |             |  |  |

|                                                     |                                                                                                                                 | ever f ≤ 95 (5F                | 0                     | Q Cycle Activity                                                                                             |                                                              |                |             |  |  |

|                                                     |                                                                                                                                 | 2.3 "Byte-Ori<br>d Instruction |                       | Q1                                                                                                           | Q2                                                           | Q3             | Q4          |  |  |

|                                                     |                                                                                                                                 | et Mode" for                   |                       | Decode                                                                                                       | No                                                           | Process        | No          |  |  |

| Words:                                              | 1                                                                                                                               |                                |                       |                                                                                                              | operation                                                    | Data           | operation   |  |  |

| Cycles:                                             | 1                                                                                                                               |                                |                       | Example:                                                                                                     | CLRWDT                                                       |                |             |  |  |

| Q Cycle Activity:                                   |                                                                                                                                 |                                |                       | Before Inst                                                                                                  |                                                              |                |             |  |  |

| Q1                                                  | Q2                                                                                                                              | Q3                             | Q4                    |                                                                                                              | Counter =                                                    | ?              |             |  |  |

| Decode                                              | Read<br>register 'f'                                                                                                            | Process<br>Data                | Write<br>register 'f' |                                                                                                              | ction<br>Counter =<br>Postscaler =                           | 00h<br>0       |             |  |  |

| Example:                                            | CLRF                                                                                                                            | FLAG_REG,                      | 1                     | TO<br>PD                                                                                                     | =                                                            | 1<br>1         |             |  |  |

| Before Instru<br>FLAG_F<br>After Instruct<br>FLAG_F | REG = 5Ah                                                                                                                       |                                |                       |                                                                                                              |                                                              |                |             |  |  |

| DECFSZ                                                   | Decremer                                                                                                                                                                                                                                       | nt f, Skip if (                                                                                                                                                                  | D                                                                                                                                                                                                                                                | DCF   | SNZ                                                  |

|----------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------|------------------------------------------------------|

| Syntax:                                                  | DECFSZ f                                                                                                                                                                                                                                       | {,d {,a}}                                                                                                                                                                        |                                                                                                                                                                                                                                                  | Synt  | ax:                                                  |

| Operands:                                                | $0 \le f \le 255$<br>$d \in [0, 1]$<br>$a \in [0, 1]$                                                                                                                                                                                          |                                                                                                                                                                                  |                                                                                                                                                                                                                                                  | Oper  | ands:                                                |

| Operation:                                               | (f) – $1 \rightarrow de$ skip if result                                                                                                                                                                                                        |                                                                                                                                                                                  |                                                                                                                                                                                                                                                  | Oper  | ation:                                               |

| Status Affected:                                         | None                                                                                                                                                                                                                                           |                                                                                                                                                                                  |                                                                                                                                                                                                                                                  | Statu | is Affected:                                         |

| Encoding:                                                | 0010                                                                                                                                                                                                                                           | 11da ff:                                                                                                                                                                         | ff ffff                                                                                                                                                                                                                                          | Enco  | oding:                                               |

| Description:                                             | decremente<br>placed in W<br>placed back<br>If the result<br>which is alre<br>and a NOP is<br>it a two-cycl<br>If 'a' is '0', th<br>GPR bank (<br>If 'a' is '0' an<br>set is enable<br>in Indexed I<br>mode when<br>Section 25.<br>Bit-Oriente | le instruction.<br>The Access Bar<br>The BSR is use<br>default).<br>The the extend<br>ed, this instru-<br>Literal Offset $\lambda$<br>ever f $\leq$ 95 (5<br><b>2.3 "Byte-Or</b> | the result is<br>ne result is<br>(default).<br>t instruction,<br>is discarded<br>stead, making<br>nk is selected.<br>d to select the<br>ed instruction<br>ction operates<br>Addressing<br>Fh). See<br><b>:iented and</b><br><b>is in Indexed</b> | Desc  | pription:                                            |

| Words:                                                   | 1                                                                                                                                                                                                                                              |                                                                                                                                                                                  |                                                                                                                                                                                                                                                  |       |                                                      |

| Cycles:                                                  | 1(2)                                                                                                                                                                                                                                           |                                                                                                                                                                                  |                                                                                                                                                                                                                                                  | Word  | ds:                                                  |

| -,                                                       | Note: 3 cy                                                                                                                                                                                                                                     | cles if skip ar<br>2-word instru                                                                                                                                                 |                                                                                                                                                                                                                                                  | Cycle | es:                                                  |

| Q Cycle Activity:                                        |                                                                                                                                                                                                                                                |                                                                                                                                                                                  | <b>.</b>                                                                                                                                                                                                                                         | 0.0   | ycle Activity:                                       |

| Q1                                                       | Q2<br>Read                                                                                                                                                                                                                                     | Q3<br>Process                                                                                                                                                                    | Q4<br>Write to                                                                                                                                                                                                                                   | QU    | Q1                                                   |