Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

E·XFI

| Product Status             | Active                                                                      |

|----------------------------|-----------------------------------------------------------------------------|

| Core Processor             | PIC                                                                         |

| Core Size                  | 8-Bit                                                                       |

| Speed                      | 40MHz                                                                       |

| Connectivity               | I <sup>2</sup> C, SPI, UART/USART                                           |

| Peripherals                | Brown-out Detect/Reset, HLVD, POR, PWM, WDT                                 |

| Number of I/O              | 36                                                                          |

| Program Memory Size        | 4KB (2K x 16)                                                               |

| Program Memory Type        | FLASH                                                                       |

| EEPROM Size                | 256 x 8                                                                     |

| RAM Size                   | 512 x 8                                                                     |

| Voltage - Supply (Vcc/Vdd) | 2V ~ 5.5V                                                                   |

| Data Converters            | A/D 13x10b                                                                  |

| Oscillator Type            | Internal                                                                    |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                           |

| Mounting Type              | Surface Mount                                                               |

| Package / Case             | 44-VQFN Exposed Pad                                                         |

| Supplier Device Package    | 44-QFN (8x8)                                                                |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic18lf4221t-i-ml |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

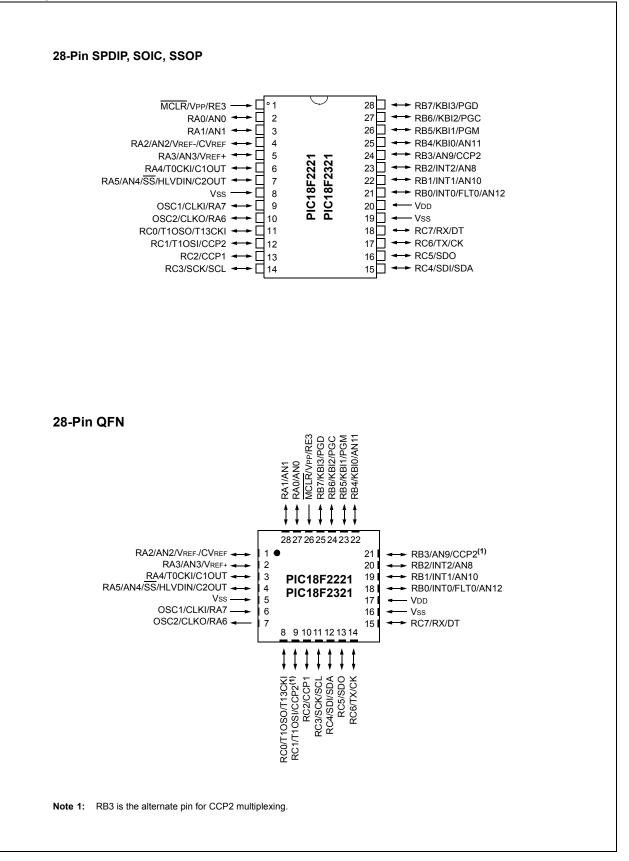

### **Pin Diagrams**

| Din Nama                                                     | Pi         | n Numl   | ber     | Pin Buffer      | Description                  |                                                                                                  |

|--------------------------------------------------------------|------------|----------|---------|-----------------|------------------------------|--------------------------------------------------------------------------------------------------|

| Pin Name                                                     | PDIP       | QFN      | TQFP    | Туре            | Туре                         | Description                                                                                      |

|                                                              |            |          |         |                 |                              | PORTC is a bidirectional I/O port.                                                               |

| RC0/T1OSO/T13CKI<br>RC0<br>T1OSO<br>T13CKI                   | 15         | 34       | 32      | I/O<br>O<br>I   | ST<br>—<br>ST                | Digital I/O.<br>Timer1 oscillator analog output.<br>Timer1/Timer3 external clock input.          |

| RC1/T1OSI/CCP2<br>RC1<br>T1OSI<br>CCP2 <sup>(1)</sup>        | 16         | 35       | 35      | I/O<br>I<br>I/O | ST<br>CMOS<br>ST             | Digital I/O.<br>Timer1 oscillator analog input.<br>Capture 2 input/Compare 2 output/PWM2 output. |

| RC2/CCP1/P1A<br>RC2<br>CCP1<br>P1A                           | 17         | 36       | 36      | I/O<br>I/O<br>O | ST<br>ST                     | Digital I/O.<br>Capture 1 input/Compare 1 output/PWM1 output.<br>Enhanced CCP1 output.           |

| RC3/SCK/SCL<br>RC3<br>SCK                                    | 18         | 37       | 37      | I/O<br>I/O      | ST<br>ST                     | Digital I/O.<br>Synchronous serial clock input/output for<br>SPI mode.                           |

| SCL                                                          |            |          |         | I/O             | l <sup>2</sup> C             | Synchronous serial clock input/output for I <sup>2</sup> C <sup>™</sup> mode.                    |

| RC4/SDI/SDA<br>RC4<br>SDI<br>SDA                             | 23         | 42       | 42      | I/O<br>I<br>I/O | ST<br>ST<br>I <sup>2</sup> C | Digital I/O.<br>SPI data in.<br>I <sup>2</sup> C data I/O.                                       |

| RC5/SDO<br>RC5<br>SDO                                        | 24         | 43       | 43      | I/O<br>O        | ST<br>—                      | Digital I/O.<br>SPI data out.                                                                    |

| RC6/TX/CK<br>RC6<br>TX<br>CK                                 | 25         | 44       | 44      | I/O<br>O<br>I/O | ST<br>—<br>ST                | Digital I/O.<br>EUSART asynchronous transmit.<br>EUSART synchronous clock (see related RX/DT)    |

| RC7/RX/DT<br>RC7<br>RX<br>DT                                 | 26         | 1        | 1       | I/O<br>I<br>I/O | ST<br>ST<br>ST               | Digital I/O.<br>EUSART asynchronous receive.<br>EUSART synchronous data (see related TX/CK).     |

| Legend: TTL = TTL of<br>ST = Schm<br>I <sup>2</sup> C = ST w | nitt Trigg | er input | with CN | 10S lev         | /els                         | CMOS = CMOS compatible input or output<br>I = Input P = Power<br>O = Output                      |

### TABLE 1-3: PIC18F4221/4321 PINOUT I/O DESCRIPTIONS (CONTINUED)

**Note 1:** Default assignment for CCP2 when Configuration bit, CCP2MX, is set.

2: Alternate assignment for CCP2 when Configuration bit, CCP2MX, is cleared.

| Pin Name                              | Pi     | n Numb | ber     | Pin Buffer            |           | Description                                                                           |

|---------------------------------------|--------|--------|---------|-----------------------|-----------|---------------------------------------------------------------------------------------|

| Pin Name                              | PDIP   | QFN    | TQFP    | Туре                  | Туре      | Description                                                                           |

|                                       |        |        |         |                       |           | PORTE is a bidirectional I/O port.                                                    |

| RE0/RD/AN5                            | 8      | 25     | 25      |                       |           |                                                                                       |

| RE0                                   |        |        |         | I/O                   | ST        | Digital I/O.                                                                          |

| RD                                    |        |        |         | I                     | TTL       | Read control for Parallel Slave Port                                                  |

|                                       |        |        |         |                       | Angles    | (see also $\overline{WR}$ and $\overline{CS}$ pins).                                  |

| AN5                                   |        |        |         | I                     | Analog    | Analog Input 5.                                                                       |

| RE1/WR/AN6                            | 9      | 26     | 26      |                       |           |                                                                                       |

| RE1                                   |        |        |         | I/O                   | ST        | Digital I/O.                                                                          |

| WR                                    |        |        |         | I                     | TTL       | Write control for Parallel Slave Port (see $\overline{CS}$ and $\overline{RD}$ pins). |

| AN6                                   |        |        |         | 1                     | Analog    | Analog Input 6.                                                                       |

| RE2/CS/AN7                            | 10     | 27     | 27      | •                     | / lineiog |                                                                                       |

| RE2/CS/AN7<br>RE2                     | 10     | 27     | 27      | I/O                   | ST        | Digital I/O.                                                                          |

|                                       |        |        |         | "U                    | TTL       | Chip Select control for Parallel Slave Port                                           |

|                                       |        |        |         | •                     |           | (see related $\overline{RD}$ and $\overline{WR}$ ).                                   |

| AN7                                   |        |        |         | Ι                     | Analog    | Analog Input 7.                                                                       |

| RE3                                   | _      | _      | _       | _                     |           | See MCLR/VPP/RE3 pin.                                                                 |

| Vss                                   | 12, 31 | 6, 30, | 6, 29   | Р                     |           | Ground reference for logic and I/O pins.                                              |

|                                       |        | 31     |         |                       |           |                                                                                       |

| Vdd                                   | 11, 32 |        | 7, 28   | Р                     |           | Positive supply for logic and I/O pins.                                               |

|                                       |        | 28, 29 |         |                       |           |                                                                                       |

| NC                                    | —      | 13     | 12, 13, | —                     | —         | No Connect.                                                                           |

|                                       |        |        | 33, 34  |                       |           |                                                                                       |

| Legend: TTL = TTL c                   |        |        |         |                       |           | CMOS = CMOS compatible input or output                                                |

| ST = Schm<br>I <sup>2</sup> C = ST wi |        |        |         | I = Input $P = Power$ |           |                                                                                       |

#### **TABLE 1-3**: PIC18F4221/4321 PINOUT I/O DESCRIPTIONS (CONTINUED)

$I^2C = ST$  with  $I^2C^{TM}$  or SMB levels

= Output 0 Note 1: Default assignment for CCP2 when Configuration bit, CCP2MX, is set.

2: Alternate assignment for CCP2 when Configuration bit, CCP2MX, is cleared.

# TABLE 3-2:CAPACITOR SELECTION FOR<br/>QUARTZ CRYSTALS

| Osc Type | Crystal<br>Freq                     | Typical Capacitor Values<br>Tested:       |                                           |  |  |  |  |

|----------|-------------------------------------|-------------------------------------------|-------------------------------------------|--|--|--|--|

|          | Fieq                                | C1                                        | C2                                        |  |  |  |  |

| LP       | 32 kHz                              | 22 pF                                     | 22 pF                                     |  |  |  |  |

| XT       | 1 MHz<br>4 MHz                      | 22 pF<br>22 pF                            | 22 pF<br>22 pF                            |  |  |  |  |

| HS       | 4 MHz<br>10 MHz<br>20 MHz<br>25 MHz | 22 pF<br>22 pF<br>22 pF<br>22 pF<br>22 pF | 22 pF<br>22 pF<br>22 pF<br>22 pF<br>22 pF |  |  |  |  |

### Capacitor values are for design guidance only.

Different capacitor values may be required to produce acceptable oscillator operation. The user should test the performance of the oscillator over the expected VDD and temperature range for the application. Refer to the following application notes for oscillator specific information:

- AN588, "PIC<sup>®</sup> Microcontroller Oscillator Design Guide"

- AN826, "Crystal Oscillator Basics and Crystal Selection for rfPIC<sup>®</sup> and PIC<sup>®</sup> Devices"

- AN849, "Basic PIC<sup>®</sup> Oscillator Design"

- AN943, "Practical PIC<sup>®</sup> Oscillator Analysis and Design"

- AN949, "Making Your Oscillator Work"

See the notes following this table for additional information.

- **Note 1:** Higher capacitance increases the stability of the oscillator but also increases the start-up time.

- When operating below 3V VDD, or when using certain ceramic resonators at any voltage, it may be necessary to use the HS mode or switch to a crystal oscillator.

- Since each resonator/crystal has its own characteristics, the user should consult the resonator/crystal manufacturer for appropriate values of external components.

- 4: Rs may be required to avoid overdriving crystals with low drive level specification.

- Always verify oscillator performance over the VDD and temperature range that is expected for the application.

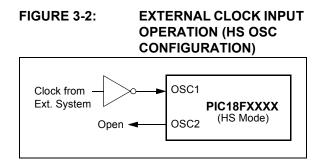

An external clock source may also be connected to the OSC1 pin in the HS mode, as shown in Figure 3-2. When operated in this mode, parameters D033 and D043 apply.

# 3.3 External Clock Input

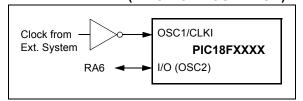

The EC and ECIO Oscillator modes require an external clock source to be connected to the OSC1 pin. There is no oscillator start-up time required after a Power-on Reset or after an exit from Sleep mode.

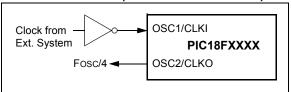

In the EC Oscillator mode, the oscillator frequency divided by 4 is available on the OSC2 pin. This signal may be used for test purposes or to synchronize other logic. Figure 3-3 shows the pin connections for the EC Oscillator mode.

# FIGURE 3-3:

#### EXTERNAL CLOCK INPUT OPERATION (EC CONFIGURATION)

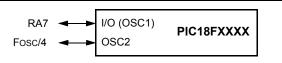

The ECIO Oscillator mode functions like the EC mode, except that the OSC2 pin becomes an additional general purpose I/O pin. The I/O pin becomes bit 6 of PORTA (RA6). Figure 3-4 shows the pin connections for the ECIO Oscillator mode. When operated in this mode, parameters D033A and D043A apply.

### EXTERNAL CLOCK INPUT OPERATION (ECIO CONFIGURATION)

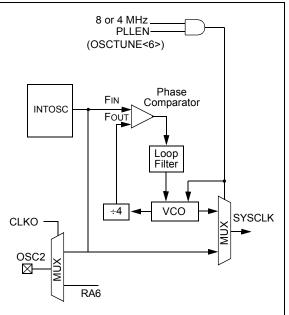

# 3.6 Internal Oscillator Block

The PIC18F2221/2321/4221/4321 family of devices includes an internal oscillator block which generates two different clock signals; either can be used as the microcontroller's clock source. This may eliminate the need for external oscillator circuits on the OSC1 and/or OSC2 pins.

The main output (INTOSC) is an 8 MHz clock source, which can be used to directly drive the device clock. It also drives a postscaler, which can provide a range of clock frequencies from 31 kHz to 4 MHz. The INTOSC output is enabled when a clock frequency from 125 kHz to 8 MHz is selected. The INTOSC output can also be enabled when 31 kHz is selected, depending on the INTSRC bit (OSCTUNE<7>).

The other clock source is the internal RC oscillator (INTRC), which provides a nominal 31 kHz output. INTRC is enabled if it is selected as the device clock source; it is also enabled automatically when any of the following are enabled:

- Power-up Timer

- · Fail-Safe Clock Monitor

- · Watchdog Timer

- Two-Speed Start-up

These features are discussed in greater detail in Section 24.0 "Special Features of the CPU".

The clock source frequency (INTOSC direct, INTRC direct or INTOSC postscaler) is selected by configuring the IRCF bits of the OSCCON register (page 37).

### 3.6.1 INTIO MODES

Using the internal oscillator as the clock source eliminates the need for up to two external oscillator pins, which can then be used for digital I/O. Two distinct configurations are available:

- In INTIO1 mode, the OSC2 pin outputs Fosc/4, while OSC1 functions as RA7 (see Figure 3-8) for digital input and output.

- In INTIO2 mode, OSC1 functions as RA7 and OSC2 functions as RA6 (see Figure 3-9), both for digital input and output.

### FIGURE 3-8: INTIO1 OSCILLATOR MODE

| FIGURE 3-9: | INTIO2 OSCILLATOR MODE |

|-------------|------------------------|

|             |                        |

| RA7 🛶 🕨 | I/O (OSC1) | PIC18FXXXX |  |

|---------|------------|------------|--|

| RA6 🔶   | I/O (OSC2) |            |  |

### 3.6.2 INTOSC OUTPUT FREQUENCY

The internal oscillator block is calibrated at the factory to produce an INTOSC output frequency of 8 MHz.

The INTRC oscillator operates independently of the INTOSC source. Any changes in INTOSC across voltage and temperature are not necessarily reflected by changes in INTRC or vice versa.

### 3.6.3 OSCTUNE REGISTER

The INTOSC output has been calibrated at the factory but can be adjusted in the user's application. This is done by writing to TUN<4:0> (OSCTUNE<4:0>) in the OSCTUNE register (Register 3-1).

When the OSCTUNE register is modified, the INTOSC frequency will begin shifting to the new frequency. Code execution continues during this shift. There is no indication that the shift has occurred. The INTRC is not affected by OSCTUNE.

The OSCTUNE register also implements the INTSRC (OSCTUNE<7>) and PLLEN (OSCTUNE<6>) bits, which control certain features of the internal oscillator block. The INTSRC bit allows users to select which internal oscillator provides the clock source when the 31 kHz frequency option is selected. This is covered in greater detail in **Section 3.7.1** "Oscillator Control **Register**".

The PLLEN bit controls the operation of the Phase Locked Loop (PLL) in Internal Oscillator modes (see Figure 3-10).

### FIGURE 3-10: INTOSC AND PLL BLOCK DIAGRAM

# 8.5 Operation During Code-Protect

Data EEPROM memory has its own code-protect bits in Configuration Words. External read and write operations are disabled if code protection is enabled.

The microcontroller itself can both read and write to the internal data EEPROM, regardless of the state of the code-protect Configuration bit. Refer to Section 24.0 "Special Features of the CPU" for additional information.

# 8.6 Protection Against Spurious Write

To protect against spurious EEPROM writes, various mechanisms have been implemented. On power-up, the WREN bit is cleared. In addition, writes to the EEPROM are blocked during the Power-up Timer period (TPWRT, parameter 33).

The write initiate sequence and the WREN bit together help prevent an accidental write during Brown-out Reset, power glitch or software malfunction.

### 8.7 Using the Data EEPROM

The data EEPROM is a high-endurance, byte addressable array that has been optimized for the storage of frequently changing data. Such data is typically updated at least one time within the number of writes defined by specification, D124. If any location storing data is not written at least this often, the data EEPROM array must be refreshed. For this reason, values that change infrequently, or not at all, should be stored in Flash program memory.

A simple data EEPROM refresh routine is shown in Example 8-3.

**Note:** If data EEPROM is only used to store constants and/or data that changes often, an array refresh is likely not required. See specification, D124.

| EXAMPLE 8-3: | DATA EEPROM REFRESH ROUTINE |

|--------------|-----------------------------|

|--------------|-----------------------------|

|      |        | DATA EEL KG   |                              |

|------|--------|---------------|------------------------------|

|      | CLRF   | EEADR         | ; Start at address 0         |

|      | BCF    | EECON1, CFGS  | ; Set for memory             |

|      | BCF    | EECON1, EEPGD | ; Set for Data EEPROM        |

|      | BCF    | INTCON, GIE   | ; Disable interrupts         |

|      | BSF    | EECON1, WREN  | ; Enable writes              |

| LOOP |        |               | ; Loop to refresh array      |

|      | BSF    | EECON1, RD    | ; Read current address       |

|      | MOVLW  | 55h           | ;                            |

|      | MOVWF  | EECON2        | ; Write 55h                  |

|      | MOVLW  | 0AAh          | ;                            |

|      | MOVWF  | EECON2        | ; Write OAAh                 |

|      | BSF    | EECON1, WR    | ; Set WR bit to begin write  |

|      | BTFSC  | EECON1, WR    | ; Wait for write to complete |

|      | BRA    | \$-2          |                              |

|      | INCFSZ | EEADR, F      | ; Increment address          |

|      | BRA    | LOOP          | ; Not zero, do it again      |

|      | BCF    | EECON1, WREN  | ; Disable writes             |

|      | BSF    | INTCON, GIE   | ; Enable interrupts          |

| 1    |        |               |                              |

| TABLE 11-7:  | PORTD I  | 0 301           |     |             |                                                                                                                                                         |

|--------------|----------|-----------------|-----|-------------|---------------------------------------------------------------------------------------------------------------------------------------------------------|

| Pin          | Function | TRIS<br>Setting | I/O | I/O<br>Type | Description                                                                                                                                             |

| RD0/PSP0     | RD0      | 0               | 0   | DIG         | LATD<0> data output.                                                                                                                                    |

|              |          | 1               | -   | ST          | PORTD<0> data input.                                                                                                                                    |

|              | PSP0     | х               | 0   | DIG         | PSP read data output (LATD<0>); takes priority over port data.                                                                                          |

|              |          | x               | Ι   | TTL         | PSP write data input.                                                                                                                                   |

| RD1/PSP1     | RD1      | 0               | 0   | DIG         | LATD<1> data output.                                                                                                                                    |

|              |          | 1               | Ι   | ST          | PORTD<1> data input.                                                                                                                                    |

|              | PSP1     | x               | 0   | DIG         | PSP read data output (LATD<1>); takes priority over port data.                                                                                          |

|              |          | x               | Ι   | TTL         | PSP write data input.                                                                                                                                   |

| RD2/PSP2     | RD2      | 0               | 0   | DIG         | LATD<2> data output.                                                                                                                                    |

|              |          | 1               | Ι   | ST          | PORTD<2> data input.                                                                                                                                    |

|              | PSP2     | х               | 0   | DIG         | PSP read data output (LATD<2>); takes priority over port data.                                                                                          |

|              |          | х               | Ι   | TTL         | PSP write data input.                                                                                                                                   |

| RD3/PSP3     | RD3      | 0               | 0   | DIG         | LATD<3> data output.                                                                                                                                    |

|              |          | 1               | I   | ST          | PORTD<3> data input.                                                                                                                                    |

|              | PSP3     | х               | 0   | DIG         | PSP read data output (LATD<3>); takes priority over port data.                                                                                          |

|              |          | x               | Ι   | TTL         | PSP write data input.                                                                                                                                   |

| RD4/PSP4     | RD4      | 0               | 0   | DIG         | LATD<4> data output.                                                                                                                                    |

|              |          | 1               | Ι   | ST          | PORTD<4> data input.                                                                                                                                    |

|              | PSP4     | х               | 0   | DIG         | PSP read data output (LATD<4>); takes priority over port data.                                                                                          |

|              |          | х               | I   | TTL         | PSP write data input.                                                                                                                                   |

| RD5/PSP5/P1B | RD5      | 0               | 0   | DIG         | LATD<5> data output.                                                                                                                                    |

|              |          | 1               | Ι   | ST          | PORTD<5> data input.                                                                                                                                    |

|              | PSP5     | х               | 0   | DIG         | PSP read data output (LATD<5>); takes priority over port data.                                                                                          |

|              |          | х               | Ι   | TTL         | PSP write data input.                                                                                                                                   |

|              | P1B      | 0               | 0   | DIG         | ECCP1 Enhanced PWM output, Channel B; takes priority over port and<br>PSP data. May be configured for tri-state during Enhanced PWM<br>shutdown events. |

| RD6/PSP6/P1C | RD6      | 0               | 0   | DIG         | LATD<6> data output.                                                                                                                                    |

|              |          | 1               | Ι   | ST          | PORTD<6> data input.                                                                                                                                    |

|              | PSP6     | х               | 0   | DIG         | PSP read data output (LATD<6>); takes priority over port data.                                                                                          |

|              |          | x               | Ι   | TTL         | PSP write data input.                                                                                                                                   |

|              | P1C      | 0               | 0   | DIG         | ECCP1 Enhanced PWM output, channel C; takes priority over port and PSP data. May be configured for tri-state during Enhanced PWM shutdown events.       |

| RD7/PSP7/P1D | RD7      | 0               | 0   | DIG         | LATD<7> data output.                                                                                                                                    |

|              |          | 1               |     | ST          | PORTD<7> data input.                                                                                                                                    |

|              | PSP7     | х               | 0   | DIG         | PSP read data output (LATD<7>); takes priority over port data.                                                                                          |

|              |          | x               | Ι   | TTL         | PSP write data input.                                                                                                                                   |

|              | P1D      | 0               | 0   | DIG         | ECCP1 Enhanced PWM output, Channel D; takes priority over port<br>and PSP data. May be configured for tri-state during Enhanced PWM<br>shutdown events. |

# TABLE 11-7: PORTD I/O SUMMARY

**Legend:** DIG = Digital level output; TTL = TTL input buffer; ST = Schmitt Trigger input buffer; x = Don't care (TRIS bit does not affect port direction or is overridden for this option).

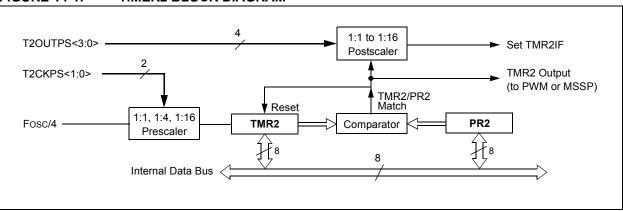

# 14.2 Timer2 Interrupt

Timer2 can also generate an optional device interrupt. The Timer2 output signal (TMR2 to PR2 match) provides the input for the 4-bit output counter/postscaler. This counter generates the TMR2 match interrupt flag which is latched in TMR2IF (PIR1<1>). The interrupt is enabled by setting the TMR2 Match Interrupt Enable bit, TMR2IE (PIE1<1>).

A range of 16 postscale options (from 1:1 through 1:16 inclusive) can be selected with the postscaler control bits, T2OUTPS<3:0> (T2CON<6:3>).

# 14.3 Timer2 Output

The unscaled output of TMR2 is available primarily to the CCP modules, where it is used as a time base for operations in PWM mode.

Timer2 can be optionally used as the shift clock source for the MSSP module operating in SPI mode. Additional information is provided in Section 18.0 "Master Synchronous Serial Port (MSSP) Module".

# FIGURE 14-1: TIMER2 BLOCK DIAGRAM

### TABLE 14-1: REGISTERS ASSOCIATED WITH TIMER2 AS A TIMER/COUNTER

| Name   | Bit 7                | Bit 6       | Bit 5    | Bit 4         | Bit 3    | Bit 2  | Bit 1   | Bit 0   | Reset<br>Values<br>on page |

|--------|----------------------|-------------|----------|---------------|----------|--------|---------|---------|----------------------------|

| INTCON | GIE/GIEH             | PEIE/GIEL   | TMR0IE   | <b>INTOIE</b> | RBIE     | TMR0IF | INT0IF  | RBIF    | 55                         |

| PIR1   | PSPIF <sup>(1)</sup> | ADIF        | RCIF     | TXIF          | SSPIF    | CCP1IF | TMR2IF  | TMR1IF  | 58                         |

| PIE1   | PSPIE <sup>(1)</sup> | ADIE        | RCIE     | TXIE          | SSPIE    | CCP1IE | TMR2IE  | TMR1IE  | 58                         |

| IPR1   | PSPIP <sup>(1)</sup> | ADIP        | RCIP     | TXIP          | SSPIP    | CCP1IP | TMR2IP  | TMR1IP  | 58                         |

| TMR2   | Timer2 Reg           | jister      |          |               |          |        |         |         | 56                         |

| T2CON  |                      | T2OUTPS3    | T2OUTPS2 | T2OUTPS1      | T2OUTPS0 | TMR2ON | T2CKPS1 | T2CKPS0 | 56                         |

| PR2    | Timer2 Peri          | od Register |          |               |          |        |         |         | 56                         |

Legend: — = unimplemented, read as '0'. Shaded cells are not used by the Timer2 module.

Note 1: These bits are unimplemented on 28-pin devices and read as '0'.

| FIGURE 18-5:                                                      | SPI N                 | IODE W      | /AVEFO                                       | RM (SL                | AVE MC                | DE WIT      | H CKE :               | = 0)                                          |   |                                  |            |

|-------------------------------------------------------------------|-----------------------|-------------|----------------------------------------------|-----------------------|-----------------------|-------------|-----------------------|-----------------------------------------------|---|----------------------------------|------------|

| -<br>SS<br>Opäend                                                 | •<br>•<br>•           |             |                                              |                       |                       |             |                       |                                               |   |                                  | <br>       |

| 90X<br>(CRP = 0<br>(CRS = 0)                                      |                       |             |                                              |                       |                       |             |                       |                                               |   |                                  |            |

| 497°Z                                                             | :<br>4                |             | ·<br>·<br>·                                  | ·<br>·<br>·           |                       | ·<br>·      |                       | ·<br>:<br>: ······                            |   |                                  | 3<br>3<br> |

| (CR49 + 1<br>0763 + 0)                                            | :<br>:<br>:           |             |                                              |                       |                       |             |                       |                                               |   |                                  |            |

| Véla la<br>SSPSUF                                                 |                       | •           | 2<br>2<br>2<br>2                             | :<br>:<br>:<br>:      | e<br>Garana<br>E<br>E | •           | 2<br>2<br>2           | ·<br>                                         | ( |                                  | *<br>      |

| 9870                                                              |                       | K 158 V     | <br>X                                        | X 58.6                |                       | X68.3       | X 68.0                |                                               |   | <u>(3</u> 3-6)                   |            |

| 809<br>(9849 = 0)                                                 | ·<br>·<br>·<br>·<br>· |             |                                              | dijijijijiji          |                       |             |                       |                                               |   |                                  | *<br>1<br> |

| inguja<br>Samagoiae                                               | -<br>-<br>-<br>       |             | ,<br>, , , , , , , , , , , , , , , , , , ,   | . 49.                 |                       |             |                       |                                               |   | <i>a</i> .                       |            |

| (53492 == 0)<br>(5389299<br>===============<br>================== | :<br>:<br>:           |             | -<br>5<br>5<br>5<br>5                        | e<br>•<br>•<br>•<br>• | -<br>5<br>5<br>6<br>6 | :<br>:      | ·<br>5<br>5<br>5<br>5 | ,<br>,<br>;<br>;                              |   | Next ()                          |            |

| SSPSR 5<br>SSPSRF                                                 | ,<br>,<br>6           | •<br>•<br>• | )<br>)<br>////////////////////////////////// | :<br>:<br>            | t<br>t<br>5           | •<br>•<br>• | )<br>;<br>,           | :<br>:<br>· · · · · · · · · · · · · · · · · · |   | 2002 (22<br>2022 (22<br>2023 (22 |            |

# FIGURE 18-6: SPI MODE WAVEFORM (SLAVE MODE WITH CKE = 1)

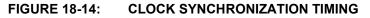

# 18.4.4.5 Clock Synchronization and the CKP bit

When the CKP bit is cleared, the SCL output is forced to '0'. However, clearing the CKP bit will not assert the SCL output low until the SCL output is already sampled low. Therefore, the CKP bit will not assert the SCL line until an external  $I^2C$  master device has

already asserted the SCL line. The SCL output will remain low until the CKP bit is set and all other devices on the  $I^2$ C bus have deasserted SCL. This ensures that a write to the CKP bit will not violate the minimum high time requirement for SCL (see Figure 18-14).

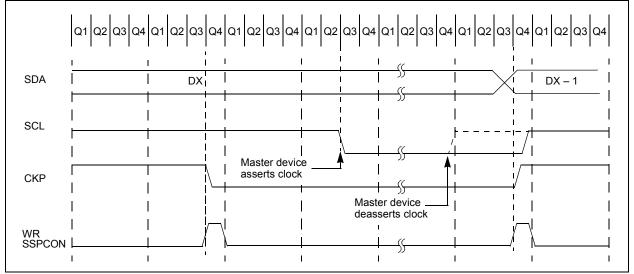

### 18.4.6 MASTER MODE

Master mode is enabled by setting and clearing the appropriate SSPM bits in SSPCON1 and by setting the SSPEN bit. In Master mode, the SCL and SDA lines are manipulated by the MSSP hardware.

Master mode of operation is supported by interrupt generation on the detection of the Start and Stop conditions. The Stop (P) and Start (S) bits are cleared from a Reset or when the MSSP module is disabled. Control of the  $I^2C$  bus may be taken when the P bit is set, or the bus is Idle, with both the S and P bits clear.

In Firmware Controlled Master mode, user code conducts all  $I^2C$  bus operations based on Start and Stop bit conditions.

Once Master mode is enabled, the user has six options.

- 1. Assert a Start condition on SDA and SCL.

- 2. Assert a Repeated Start condition on SDA and SCL.

- 3. Write to the SSPBUF register initiating transmission of data/address.

- 4. Configure the I<sup>2</sup>C port to receive data.

- 5. Generate an Acknowledge condition at the end of a received byte of data.

- 6. Generate a Stop condition on SDA and SCL.

Note: The MSSP module, when configured in I<sup>2</sup>C Master mode, does not allow queueing of events. For instance, the user is not allowed to initiate a Start condition and immediately write the SSPBUF register to initiate transmission before the Start condition is complete. In this case, the SSPBUF will not be written to and the WCOL bit will be set, indicating that a write to the SSPBUF did not occur.

The following events will cause the MSSP Interrupt Flag bit, SSPIF, to be set (MSSP interrupt, if enabled):

- · Start condition

- Stop condition

- · Data transfer byte transmitted/received

- Acknowledge transmit

- Repeated Start

# 18.4.10 I<sup>2</sup>C MASTER MODE TRANSMISSION

Transmission of a data byte, a 7-bit address or the other half of a 10-bit address is accomplished by simply writing a value to the SSPBUF register. This action will set the Buffer Full flag bit, BF and allow the Baud Rate Generator to begin counting and start the next transmission. Each bit of address/data will be shifted out onto the SDA pin after the falling edge of SCL is asserted (see data hold time specification parameter 106). SCL is held low for one Baud Rate Generator rollover count (TBRG). Data should be valid before SCL is released high (see data setup time specification parameter 107). When the SCL pin is released high, it is held that way for TBRG. The data on the SDA pin must remain stable for that duration and some hold time after the next falling edge of SCL. After the eighth bit is shifted out (the falling edge of the eighth clock), the BF flag is cleared and the master releases SDA. This allows the slave device being addressed to respond with an  $\overline{ACK}$  bit during the ninth bit time if an address match occurred, or if data was received properly. The status of ACK is written into the ACKDT bit on the falling edge of the ninth clock. If the master receives an Acknowledge, the Acknowledge Status bit, ACKSTAT, is cleared. If not, the bit is set. After the ninth clock, the SSPIF bit is set and the master clock (Baud Rate Generator) is suspended until the next data byte is loaded into the SSPBUF, leaving SCL low and SDA unchanged (Figure 18-23).

After the write to the SSPBUF, each bit of the address will be shifted out on the falling edge of SCL until all seven address bits and the R/W bit are completed. On the falling edge of the eighth clock, the master will deassert the SDA pin, allowing the slave to respond with an Acknowledge. On the falling edge of the ninth clock, the master will sample the SDA pin to see if the address was recognized by a slave. The status of the ACK bit is loaded into the ACKSTAT status bit (SSPCON2<6>). Following the falling edge of the ninth clock transmission of the address, the SSPIF is set, the BF flag is cleared and the Baud Rate Generator is turned off until another write to the SSPBUF takes place, holding SCL low and allowing SDA to float.

### 18.4.10.1 BF Status Flag

In Transmit mode, the BF bit (SSPSTAT<0>) is set when the CPU writes to SSPBUF and is cleared when all 8 bits are shifted out.

### 18.4.10.2 WCOL Status Flag

If the user writes the SSPBUF when a transmit is already in progress (i.e., SSPSR is still shifting out a data byte), the WCOL flag is set and the contents of the buffer are unchanged (the write doesn't occur) after 2 TcY after the SSPBUF write. If SSPBUF is rewritten within 2 TcY, the WCOL bit is set and SSPBUF is updated. This may result in a corrupted transfer. The user should verify that the WCOL flag is clear after each write to SSPBUF to ensure the transfer is correct.

### 18.4.10.3 ACKSTAT Status Flag

In Transmit mode, the ACKSTAT bit (SSPCON2<6>) is cleared when the slave has sent an Acknowledge  $(\overline{ACK} = 0)$  and is set when the slave does not Acknowledge  $(\overline{ACK} = 1)$ . A slave sends an Acknowledge when it has recognized its address (including a general call), or when the slave has properly received its data.

# 18.4.11 I<sup>2</sup>C MASTER MODE RECEPTION

Master mode reception is enabled by programming the Receive Enable bit, RCEN (SSPCON2<3>).

Note: The MSSP module must be in an Idle state before the RCEN bit is set or the RCEN bit will be disregarded.

The Baud Rate Generator begins counting and on each rollover, the state of the SCL pin changes (high-to-low/ low-to-high) and data is shifted into the SSPSR. After the falling edge of the eighth clock, the receive enable flag is automatically cleared, the contents of the SSPSR are loaded into the SSPBUF, the BF flag bit is set, the SSPIF flag bit is set and the Baud Rate Generator is suspended from counting, holding SCL low. The MSSP is now in Idle state awaiting the next command. When the buffer is read by the CPU, the BF flag bit is automatically cleared. The user can then send an Acknowledge bit at the end of reception by setting the Acknowledge Sequence Enable bit, ACKEN (SSPCON2<4>).

### 18.4.11.1 BF Status Flag

In receive operation, the BF bit is set when an address or data byte is loaded into SSPBUF from SSPSR. It is cleared when the SSPBUF register is read.

### 18.4.11.2 SSPOV Status Flag

In receive operation, the SSPOV bit is set when 8 bits are received into the SSPSR and the BF flag bit is already set from a previous reception.

### 18.4.11.3 WCOL Status Flag

If the user writes the SSPBUF when a receive is already in progress (i.e., SSPSR is still shifting in a data byte), the WCOL bit is set and the contents of the buffer are unchanged (the write doesn't occur).

<sup>© 2009</sup> Microchip Technology Inc.

|              |                       | SYNC = 0, BRGH = 0, BRG16 = 1 |                             |                       |            |                             |                       |            |                             |                       |            |                             |  |  |  |  |

|--------------|-----------------------|-------------------------------|-----------------------------|-----------------------|------------|-----------------------------|-----------------------|------------|-----------------------------|-----------------------|------------|-----------------------------|--|--|--|--|

| BAUD<br>RATE | Fosc = 40.000 MHz     |                               |                             | Fosc = 20.000 MHz     |            |                             | Fosc = 10.000 MHz     |            |                             | Fosc = 8.000 MHz      |            |                             |  |  |  |  |

| (K)          | Actual<br>Rate<br>(K) | %<br>Error                    | SPBRG<br>value<br>(decimal) | Actual<br>Rate<br>(K) | %<br>Error | SPBRG<br>value<br>(decimal) | Actual<br>Rate<br>(K) | %<br>Error | SPBRG<br>value<br>(decimal) | Actual<br>Rate<br>(K) | %<br>Error | SPBRG<br>value<br>(decimal) |  |  |  |  |

| 0.3          | 0.300                 | 0.00                          | 8332                        | 0.300                 | 0.02       | 4165                        | 0.300                 | 0.02       | 2082                        | 0.300                 | -0.04      | 1665                        |  |  |  |  |

| 1.2          | 1.200                 | 0.02                          | 2082                        | 1.200                 | -0.03      | 1041                        | 1.200                 | -0.03      | 520                         | 1.201                 | -0.16      | 415                         |  |  |  |  |

| 2.4          | 2.402                 | 0.06                          | 1040                        | 2.399                 | -0.03      | 520                         | 2.404                 | 0.16       | 259                         | 2.403                 | -0.16      | 207                         |  |  |  |  |

| 9.6          | 9.615                 | 0.16                          | 259                         | 9.615                 | 0.16       | 129                         | 9.615                 | 0.16       | 64                          | 9.615                 | -0.16      | 51                          |  |  |  |  |

| 19.2         | 19.231                | 0.16                          | 129                         | 19.231                | 0.16       | 64                          | 19.531                | 1.73       | 31                          | 19.230                | -0.16      | 25                          |  |  |  |  |

| 57.6         | 58.140                | 0.94                          | 42                          | 56.818                | -1.36      | 21                          | 56.818                | -1.36      | 10                          | 55.555                | 3.55       | 8                           |  |  |  |  |

| 115.2        | 113.636               | -1.36                         | 21                          | 113.636               | -1.36      | 10                          | 125.000               | 8.51       | 4                           | —                     | _          | _                           |  |  |  |  |

| TABLE 19-3: | <b>BAUD RATES FOR ASYNCHRONOUS MODES (</b> | CONTINUED) |  |

|-------------|--------------------------------------------|------------|--|

|             |                                            |            |  |

|             | SYNC = 0, BRGH = 0, BRG16 = 1 |                            |     |                       |            |                             |                       |            |                             |

|-------------|-------------------------------|----------------------------|-----|-----------------------|------------|-----------------------------|-----------------------|------------|-----------------------------|

| BAUD        | Fose                          | Fosc = 4.000 MHz           |     |                       | c = 2.000  | MHz                         | Fosc = 1.000 MHz      |            |                             |

| RATE<br>(K) | Actual<br>Rate<br>(K)         | % SPBRG<br>Error (decimal) |     | Actual<br>Rate<br>(K) | %<br>Error | SPBRG<br>value<br>(decimal) | Actual<br>Rate<br>(K) | %<br>Error | SPBRG<br>value<br>(decimal) |

| 0.3         | 0.300                         | 0.04                       | 832 | 0.300                 | -0.16      | 415                         | 0.300                 | -0.16      | 207                         |

| 1.2         | 1.202                         | 0.16                       | 207 | 1.201                 | -0.16      | 103                         | 1.201                 | -0.16      | 51                          |

| 2.4         | 2.404                         | 0.16                       | 103 | 2.403                 | -0.16      | 51                          | 2.403                 | -0.16      | 25                          |

| 9.6         | 9.615                         | 0.16                       | 25  | 9.615                 | -0.16      | 12                          | —                     | _          | _                           |

| 19.2        | 19.231                        | 0.16                       | 12  | —                     | _          | _                           | —                     | _          | _                           |

| 57.6        | 62.500                        | 8.51                       | 3   | —                     | _          | _                           | —                     | _          | _                           |

| 115.2       | 125.000                       | 8.51                       | 1   | —                     | _          | —                           | —                     | _          | _                           |

|              | SYNC = 0, BRGH = 1, BRG16 = 1 or SYNC = 1, BRG16 = 1 |            |                             |                       |            |                             |                       |            |                             |                       |            |                             |

|--------------|------------------------------------------------------|------------|-----------------------------|-----------------------|------------|-----------------------------|-----------------------|------------|-----------------------------|-----------------------|------------|-----------------------------|

| BAUD<br>RATE | Fosc = 40.000 MHz                                    |            | Fosc                        | = 20.000              | ) MHz      | Fosc = 10.000 MHz           |                       |            | Fosc = 8.000 MHz            |                       |            |                             |

| (K)          | Actual<br>Rate<br>(K)                                | %<br>Error | SPBRG<br>value<br>(decimal) | Actual<br>Rate<br>(K) | %<br>Error | SPBRG<br>value<br>(decimal) | Actual<br>Rate<br>(K) | %<br>Error | SPBRG<br>value<br>(decimal) | Actual<br>Rate<br>(K) | %<br>Error | SPBRG<br>value<br>(decimal) |

| 0.3          | 0.300                                                | 0.00       | 33332                       | 0.300                 | 0.00       | 16665                       | 0.300                 | 0.00       | 8332                        | 0.300                 | -0.01      | 6665                        |

| 1.2          | 1.200                                                | 0.00       | 8332                        | 1.200                 | 0.02       | 4165                        | 1.200                 | 0.02       | 2082                        | 1.200                 | -0.04      | 1665                        |

| 2.4          | 2.400                                                | 0.02       | 4165                        | 2.400                 | 0.02       | 2082                        | 2.402                 | 0.06       | 1040                        | 2.400                 | -0.04      | 832                         |

| 9.6          | 9.606                                                | 0.06       | 1040                        | 9.596                 | -0.03      | 520                         | 9.615                 | 0.16       | 259                         | 9.615                 | -0.16      | 207                         |

| 19.2         | 19.193                                               | -0.03      | 520                         | 19.231                | 0.16       | 259                         | 19.231                | 0.16       | 129                         | 19.230                | -0.16      | 103                         |

| 57.6         | 57.803                                               | 0.35       | 172                         | 57.471                | -0.22      | 86                          | 58.140                | 0.94       | 42                          | 57.142                | 0.79       | 34                          |

| 115.2        | 114.943                                              | -0.22      | 86                          | 116.279               | 0.94       | 42                          | 113.636               | -1.36      | 21                          | 117.647               | -2.12      | 16                          |

|       | SYNC = 0, BRGH = 1, BRG16 = 1 or SYNC = 1, BRG16 = 1 |            |                             |                                          |           |                       |                  |                             |     |

|-------|------------------------------------------------------|------------|-----------------------------|------------------------------------------|-----------|-----------------------|------------------|-----------------------------|-----|

| BAUD  | Fosc = 4.000 MHz                                     |            |                             | Fos                                      | c = 2.000 | MHz                   | Fosc = 1.000 MHz |                             |     |

| (K)   | Actual<br>Rate<br>(K)                                | %<br>Error | SPBRG<br>value<br>(decimal) | Actual % SPBRG /<br>Rate Error (decimal) |           | Actual<br>Rate<br>(K) | %<br>Error       | SPBRG<br>value<br>(decimal) |     |

| 0.3   | 0.300                                                | 0.01       | 3332                        | 0.300                                    | -0.04     | 1665                  | 0.300            | -0.04                       | 832 |

| 1.2   | 1.200                                                | 0.04       | 832                         | 1.201                                    | -0.16     | 415                   | 1.201            | -0.16                       | 207 |

| 2.4   | 2.404                                                | 0.16       | 415                         | 2.403                                    | -0.16     | 207                   | 2.403            | -0.16                       | 103 |

| 9.6   | 9.615                                                | 0.16       | 103                         | 9.615                                    | -0.16     | 51                    | 9.615            | -0.16                       | 25  |

| 19.2  | 19.231                                               | 0.16       | 51                          | 19.230                                   | -0.16     | 25                    | 19.230           | -0.16                       | 12  |

| 57.6  | 58.824                                               | 2.12       | 16                          | 55.555                                   | 3.55      | 8                     | —                | _                           | —   |

| 115.2 | 111.111                                              | -3.55      | 8                           | —                                        | _         | _                     | _                | _                           | —   |

# 20.2 Selecting and Configuring Acquisition Time

The ADCON2 register allows the user to select an acquisition time that occurs each time the GO/DONE bit is set. It also gives users the option to use an automatically determined acquisition time.

Acquisition time may be set with the ACQT<2:0> bits (ADCON2<5:3>), which provides a range of 2 to 20 TAD. When the GO/DONE bit is set, the A/D module continues to sample the input for the selected acquisition time, then automatically begins a conversion. Since the acquisition time is programmed, there may be no need to wait for an acquisition time between selecting a channel and setting the GO/DONE bit.

Manual acquisition is selected when ACQT<2:0> = 000. When the GO/DONE bit is set, sampling is stopped and a conversion begins. The user is responsible for ensuring the required acquisition time has passed between selecting the desired input channel and setting the GO/DONE bit. This option is also the default Reset state of the ACQT<2:0> bits and is compatible with devices that do not offer programmable acquisition times.

In either case, when the conversion is completed, the GO/DONE bit is cleared, the ADIF flag is set and the A/D begins sampling the currently selected channel again. If an acquisition time is programmed, there is nothing to indicate if the acquisition time has ended or if the conversion has begun.

# 20.3 Selecting the A/D Conversion Clock

The A/D conversion time per bit is defined as TAD. The A/D conversion requires 11 TAD per 10-bit conversion. The source of the A/D conversion clock is software selectable. There are seven possible options for TAD:

- 2 Tosc

- 4 Tosc

- 8 Tosc

- 16 Tosc

- 32 Tosc

- 64 Tosc

- Internal RC Oscillator

For correct A/D conversions, the A/D conversion clock (TAD) must be as short as possible, but greater than the minimum TAD (see parameter 130 for more information).

Table 20-1 shows the resultant TAD times derived from the device operating frequencies and the A/D clock source selected.

| AD Clock Sc       | ource (TAD)         | Maximum Device Frequency |                                 |  |  |  |

|-------------------|---------------------|--------------------------|---------------------------------|--|--|--|

| Operation         | Operation ADCS<2:0> |                          | PIC18LF2X21/4X21 <sup>(4)</sup> |  |  |  |

| 2 Tosc            | 000                 | 2.86 MHz                 | 1.43 kHz                        |  |  |  |

| 4 Tosc            | 100                 | 5.71 MHz                 | 2.86 MHz                        |  |  |  |

| 8 Tosc            | 001                 | 11.43 MHz                | 5.72 MHz                        |  |  |  |

| 16 Tosc           | 101                 | 22.86 MHz                | 11.43 MHz                       |  |  |  |

| 32 Tosc           | 010                 | 40.0 MHz                 | 22.86 MHz                       |  |  |  |

| 64 Tosc           | 110                 | 40.0 MHz                 | 22.86 MHz                       |  |  |  |

| RC <sup>(3)</sup> | x11                 | 1.00 MHz <sup>(1)</sup>  | 1.00 MHz <sup>(2)</sup>         |  |  |  |

### TABLE 20-1: TAD VS. DEVICE OPERATING FREQUENCIES

**Note 1:** The RC source has a typical TAD time of  $1.2 \ \mu$ s.

**2:** The RC source has a typical TAD time of 2.5  $\mu$ s.

- **3:** For device frequencies above 1 MHz, the device must be in Sleep for the entire conversion or the A/D accuracy may be out of specification.

- 4: Low-power (PIC18LFXXXX) devices only.

| REGISTER 24-1: | CONFIG1                                                                                       | H: CONFIG                                                                                                                                               | URATION                                                                                                             | REGISTER    | R 1 HIGH (E                                                | BYTE ADD   | RESS 3000      | 01h)    |

|----------------|-----------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------|-------------|------------------------------------------------------------|------------|----------------|---------|

|                | R/P-0                                                                                         | R/P-0                                                                                                                                                   | U-0                                                                                                                 | U-0         | R/P-0                                                      | R/P-1      | R/P-1          | R/P-1   |

|                | IESO                                                                                          | FCMEN                                                                                                                                                   | _                                                                                                                   | _           | FOSC3                                                      | FOSC2      | FOSC1          | FOSC0   |

|                | bit 7                                                                                         |                                                                                                                                                         |                                                                                                                     |             |                                                            |            |                | bit 0   |

| bit 7          | 1 = Oscillat<br>0 = Oscillat                                                                  | or Switchov<br>or Switchov                                                                                                                              | er mode ena<br>er mode dis                                                                                          | abled       | it                                                         |            |                |         |

| bit 6          | 1 = Fail-Sa                                                                                   | fe Clock Mo                                                                                                                                             | ck Monitor E<br>nitor enable<br>nitor disable                                                                       | d           |                                                            |            |                |         |

| bit 5-4        | Unimplem                                                                                      | ented: Read                                                                                                                                             | <b>d as</b> '0'                                                                                                     |             |                                                            |            |                |         |

| bit 3-0        |                                                                                               |                                                                                                                                                         | Selection b                                                                                                         |             |                                                            |            |                |         |

|                | 101x = Exi<br>1001 = Inte<br>1000 = Inte<br>0111 = Exi<br>0110 = HS<br>0101 = EC<br>0100 = EC | ternal RC os<br>ernal oscilla<br>ernal oscilla<br>ternal RC os<br>oscillator, p<br>oscillator, c<br>ternal RC os<br>oscillator oscillator<br>oscillator | scillator, CLH<br>tor block, CL<br>tor block, po<br>scillator, port<br>PLL enabled<br>port function<br>CLKO functio |             | on RA6<br>on RA6, po<br>n RA6 and I<br>RA6<br>juency = 4 x | RA7        | n RA7          |         |

|                | Legend:                                                                                       |                                                                                                                                                         |                                                                                                                     |             |                                                            |            |                |         |

|                | R = Readal                                                                                    | ole bit                                                                                                                                                 | P = Progra                                                                                                          | ammable bit | U = Unin                                                   | nplemented | bit, read as ' | 0'      |

|                | -n = Value v                                                                                  | when device                                                                                                                                             | e is unprogra                                                                                                       | mmed        | u = Unch                                                   | anged from | programme      | d state |

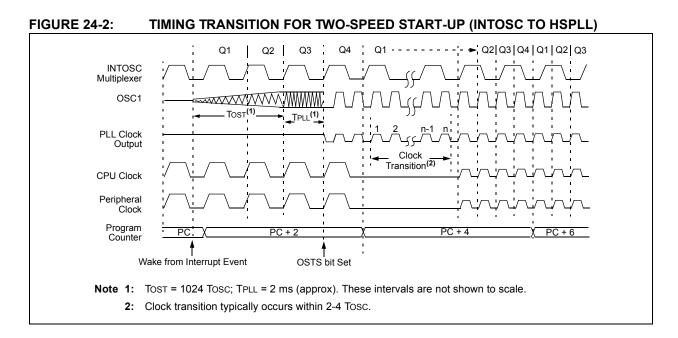

# 24.3 Two-Speed Start-up

The Two-Speed Start-up feature helps to minimize the latency period from oscillator start-up to code execution by allowing the microcontroller to use the INTOSC oscillator as a clock source until the primary clock source is available. It is enabled by setting the IESO Configuration bit.

Two-Speed Start-up should be enabled only if the primary oscillator mode is LP, XT, HS or HSPLL (crystal-based modes). Other sources do not require an OST start-up delay; for these, Two-Speed Start-up should be disabled.

When enabled, Resets and wake-ups from Sleep mode cause the device to configure itself to run from the internal oscillator block as the clock source, following the time-out of the Power-up Timer after a Power-on Reset is enabled. This allows almost immediate code execution while the primary oscillator starts and the OST is running. Once the OST times out, the device automatically switches to PRI\_RUN mode.

To use a higher clock speed on wake-up, the INTOSC or postscaler clock sources can be selected to provide a higher clock speed by setting bits, IRCF<2:0>, immediately after Reset. For wake-ups from Sleep, the INTOSC or postscaler clock sources can be selected by setting the IRCF<2:0> bits prior to entering Sleep mode.

In all other power-managed modes, Two-Speed Startup is not used. The device will be clocked by the currently selected clock source until the primary clock source becomes available. The setting of the IESO bit is ignored.

### 24.3.1 SPECIAL CONSIDERATIONS FOR USING TWO-SPEED START-UP

While using the INTOSC oscillator in Two-Speed Startup, the device still obeys the normal command sequences for entering power-managed modes, including multiple SLEEP instructions (refer to **Section 4.1.4 "Multiple Sleep Commands"**). In practice, this means that user code can change the SCS<1:0> bit settings or issue SLEEP instructions before the OST times out. This would allow an application to briefly wake-up, perform routine "housekeeping" tasks and return to Sleep before the device starts to operate from the primary oscillator.

User code can also check if the primary clock source is currently providing the device clocking by checking the status of the OSTS bit (OSCCON<3>). If the bit is set, the primary oscillator is providing the clock. Otherwise, the internal oscillator block is providing the clock during wake-up from Reset or Sleep mode.

| NEGF              | Negate f                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

|-------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Syntax:           | NEGF f {,a}                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

| Operands:         | $0 \le f \le 255$<br>$a \in [0, 1]$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

| Operation:        | $(\overline{f}) + 1 \rightarrow f$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

| Status Affected:  | N, OV, C, DC, Z                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

| Encoding:         | 0110 110a ffff ffff                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

| Description:      | Location 'f' is negated using two's<br>complement. The result is placed in the<br>data memory location 'f'.<br>If 'a' is '0', the Access Bank is selected.<br>If 'a' is '1', the BSR is used to select the<br>GPR bank (default).<br>If 'a' is '0' and the extended instruction<br>set is enabled, this instruction operates<br>in Indexed Literal Offset Addressing<br>mode whenever $f \le 95$ (5Fh). See<br>Section 25.2.3 "Byte-Oriented and<br>Bit-Oriented Instructions in Indexed<br>Literal Offset Mode" for details. |

| Words:            | 1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

| Cycles:           | 1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

| Q Cycle Activity: |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

| NOF   | )              | No Opera   | ation     |      |    |          |

|-------|----------------|------------|-----------|------|----|----------|

| Synta | ax:            | NOP        |           |      |    |          |

| Oper  | ands:          | None       |           |      |    |          |

| Oper  | ation:         | No operati | on        |      |    |          |

| Statu | s Affected:    | None       |           |      |    |          |

| Enco  | ding:          | 0000       | 0000 0000 |      | 00 | 0000     |

|       |                | 1111       | XXXX      | XXX  | xx | XXXX     |

| Desc  | ription:       | No operati | on.       |      |    |          |

| Word  | ls:            | 1          |           |      |    |          |

| Cycle | es:            | 1          |           |      |    |          |

| QC    | ycle Activity: |            |           |      |    |          |

|       | Q1             | Q2         | Q         | 3    |    | Q4       |

|       | Decode         | No         | No        | )    |    | No       |

|       |                | operation  | opera     | tion | op | peration |

Example:

None.

| Q1     | Q2           | Q3      | Q4           |

|--------|--------------|---------|--------------|

| Decode | Read         | Process | Write        |

|        | register 'f' | Data    | register 'f' |

Example: NEGF REG, 1

> Before Instruction REG = 0011 1010 [3Ah] After Instruction REG = 1100 0110 [C6h]

© 2009 Microchip Technology Inc.

# 27.3 DC Characteristics: PIC18F2221/2321/4221/4321 (Industrial) PIC18LF2221/2321/4221/4321 (Industrial)

| DC CHA       | DC CHARACTERISTICS |                                                     |                    | perature -40 | )°C ≤ T/   | (unless otherwise stated)<br>$A \le +85^{\circ}C$ for industrial<br>$A \le +125^{\circ}C$ for extended |

|--------------|--------------------|-----------------------------------------------------|--------------------|--------------|------------|--------------------------------------------------------------------------------------------------------|

| Param<br>No. | Symbol             | Characteristic                                      | Min                | Мах          | Conditions |                                                                                                        |

|              | VIL                | Input Low Voltage                                   |                    |              |            |                                                                                                        |