Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

#### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Product Status             | Active                                                                     |

|----------------------------|----------------------------------------------------------------------------|

| Core Processor             | PIC                                                                        |

| Core Size                  | 8-Bit                                                                      |

| Speed                      | 40MHz                                                                      |

| Connectivity               | I <sup>2</sup> C, SPI, UART/USART                                          |

| Peripherals                | Brown-out Detect/Reset, HLVD, POR, PWM, WDT                                |

| Number of I/O              | 36                                                                         |

| Program Memory Size        | 8KB (4K x 16)                                                              |

| Program Memory Type        | FLASH                                                                      |

| EEPROM Size                | 256 x 8                                                                    |

| RAM Size                   | 512 x 8                                                                    |

| Voltage - Supply (Vcc/Vdd) | 2V ~ 5.5V                                                                  |

| Data Converters            | A/D 13x10b                                                                 |

| Oscillator Type            | Internal                                                                   |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                          |

| Mounting Type              | Surface Mount                                                              |

| Package / Case             | 44-VQFN Exposed Pad                                                        |

| Supplier Device Package    | 44-QFN (8x8)                                                               |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic18lf4321-i-ml |

|                            |                                                                            |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

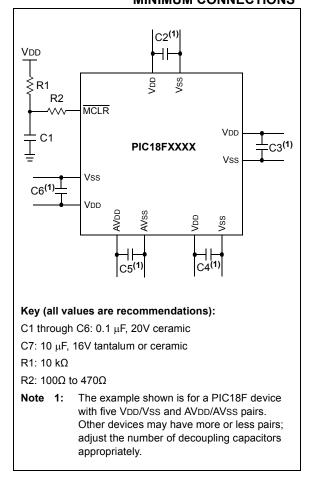

# 2.0 GUIDELINES FOR GETTING STARTED WITH PIC18F MICROCONTROLLERS

# 2.1 Basic Connection Requirements

Getting started with the PIC18F2221/2321/4221/4321 family family of 8-bit microcontrollers requires attention to a minimal set of device pin connections before proceeding with development.

The following pins must always be connected:

- All VDD and Vss pins (see Section 2.2 "Power Supply Pins")

- All AVDD and AVss pins, regardless of whether or not the analog device features are used (see Section 2.2 "Power Supply Pins")

- MCLR pin

(see Section 2.3 "Master Clear (MCLR) Pin")

These pins must also be connected if they are being used in the end application:

- PGC/PGD pins used for In-Circuit Serial Programming<sup>™</sup> (ICSP<sup>™</sup>) and debugging purposes (see Section 2.4 "ICSP Pins")

- OSCI and OSCO pins when an external oscillator source is used

(see Section 2.5 "External Oscillator Pins")

Additionally, the following pins may be required:

• VREF+/VREF- pins used when external voltage reference for analog modules is implemented

| Note: | The AVDD and AVSS pins must always be   |

|-------|-----------------------------------------|

|       | connected, regardless of whether any of |

|       | the analog modules are being used.      |

The minimum mandatory connections are shown in Figure 2-1.

## FIGURE 2-1: RECOMMENDED MINIMUM CONNECTIONS

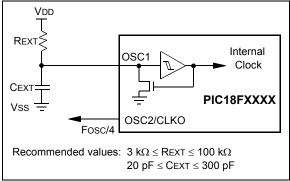

# 3.4 RC Oscillator

For timing insensitive applications, the RC and RCIO Oscillator modes offer additional cost savings. The actual oscillator frequency is a function of several factors:

- supply voltage

- values of the external resistor (REXT) and capacitor (CEXT)

- · operating temperature

Given the same device, operating voltage, temperature and component values, there will also be unit-to-unit frequency variations. These are due to factors such as:

- normal manufacturing variation

- difference in lead frame capacitance between package types (especially for low CEXT values)

- variations within the tolerance of limits of  $\ensuremath{\mathsf{REXT}}$  and  $\ensuremath{\mathsf{CEXT}}$

In the RC Oscillator mode, the oscillator frequency divided by 4 is available on the OSC2 pin. This signal may be used for test purposes or to synchronize other logic. Figure 3-5 shows how the R/C combination is connected.

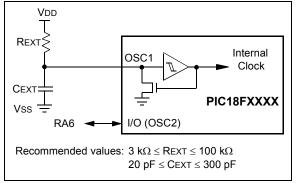

The RCIO Oscillator mode (Figure 3-6) functions like the RC mode, except that the OSC2 pin becomes an additional general purpose I/O pin. The I/O pin becomes bit 6 of PORTA (RA6).

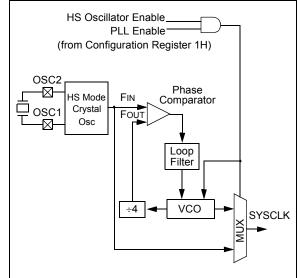

# 3.5 PLL Frequency Multiplier

A Phase Locked Loop (PLL) circuit is provided as an option for users who wish to use a lower frequency oscillator circuit or to clock the device up to its highest rated frequency from a crystal oscillator. This may be useful for customers who are concerned with EMI due to high-frequency crystals or users who require higher clock speeds from an internal oscillator.

### 3.5.1 HSPLL OSCILLATOR MODE

The HSPLL mode makes use of the HS mode oscillator for frequencies up to 10 MHz. A PLL then multiplies the oscillator output frequency by 4 to produce an internal clock frequency up to 40 MHz. The PLLEN bit is not available when this mode is configured as the primary clock source.

The PLL is only available to the crystal oscillator when the FOSC<3:0> Configuration bits are programmed for HSPLL mode (= 0110).

## 3.5.2 PLL AND INTOSC

The PLL is also available to the internal oscillator block when the internal oscillator block is configured as the primary clock source. In this configuration, the PLL is enabled in software and generates a clock output of up to 32 MHz. The operation of INTOSC with the PLL is described in **Section 3.6.4 "PLL in INTOSC Modes"**.

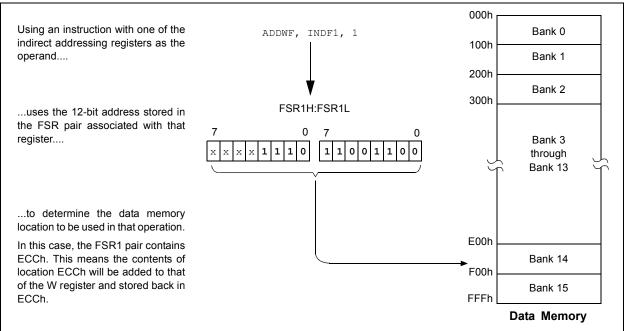

# 6.4.3.1 FSR Registers and the INDF Operand

At the core of indirect addressing are three sets of registers: FSR0, FSR1 and FSR2. Each represents a pair of 8-bit registers, FSRnH and FSRnL. The four upper bits of the FSRnH register are not used so each FSR pair holds a 12-bit value. This represents a value that can address the entire range of the data memory in a linear fashion. The FSR register pairs, then, serve as pointers to data memory locations.

Indirect addressing is accomplished with a set of Indirect File Operands, INDF0 through INDF2. These can be thought of as "virtual" registers: they are mapped in the SFR space but are not physically implemented. Reading or writing to a particular INDF register actually accesses its corresponding FSR register pair. A read from INDF1, for example, reads the data at the address indicated by FSR1H:FSR1L. Instructions that use the INDF registers as operands actually use the contents of their corresponding FSR as a pointer to the instruction's target. The INDF operand is just a convenient way of using the pointer.

Because indirect addressing uses a full 12-bit address, data RAM banking is not necessary. Thus, the current contents of the BSR and the Access RAM bit have no effect on determining the target address.

### 6.4.3.2 FSR Registers and POSTINC, POSTDEC, PREINC and PLUSW

In addition to the INDF operand, each FSR register pair also has four additional indirect operands. Like INDF, these are "virtual" registers that cannot be indirectly read or written to. Accessing these registers actually accesses the associated FSR register pair, but also performs a specific action on its stored value. They are:

- POSTDEC: accesses the FSR value, then automatically decrements it by 1 afterwards

- POSTINC: accesses the FSR value, then automatically increments it by 1 afterwards

- PREINC: increments the FSR value by 1, then uses it in the operation

- PLUSW: adds the signed value of the W register (range of -127 to 128) to that of the FSR and uses the new value in the operation.

In this context, accessing an INDF register uses the value in the FSR registers without changing them. Similarly, accessing a PLUSW register gives the FSR value offset by that in the W register; neither value is actually changed in the operation. Accessing the other virtual registers changes the value of the FSR registers.

Operations on the FSRs with POSTDEC, POSTINC and PREINC affect the entire register pair; that is, rollovers of the FSRnL register from FFh to 00h carry over to the FSRnH register. On the other hand, results of these operations do not change the value of any flags in the STATUS register (e.g., Z, N, OV, etc.).

## FIGURE 6-7: INDIRECT ADDRESSING

# 7.0 FLASH PROGRAM MEMORY

The Flash program memory is readable, writable and erasable during normal operation over the entire VDD range.

A read from program memory is executed on one byte at a time. A write to program memory is executed on blocks of 8 bytes at a time. Program memory is erased in blocks of 64 bytes at a time. A bulk erase operation may not be issued from user code.

Writing or erasing program memory will cease instruction fetches until the operation is complete. The program memory cannot be accessed during the write or erase, therefore, code cannot execute. An internal programming timer terminates program memory writes and erases.

A value written to program memory does not need to be a valid instruction. Executing a program memory location that forms an invalid instruction results in a NOP.

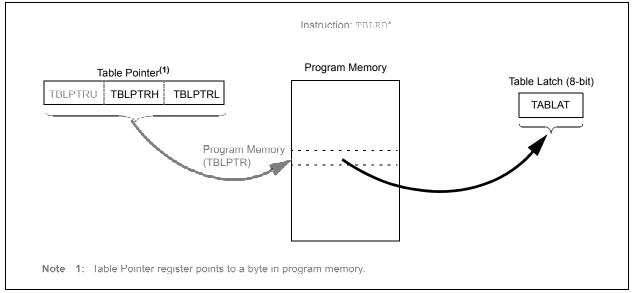

## 7.1 Table Reads and Table Writes

In order to read and write program memory, there are two operations that allow the processor to move bytes between the program memory space and the data RAM:

- Table Read (TBLRD)

- Table Write (TBLWT)

The program memory space is 16 bits wide, while the data RAM space is 8 bits wide. Table reads and table writes move data between these two memory spaces through an 8-bit register (TABLAT).

Table read operations retrieve data from program memory and place it into the data RAM space. Figure 7-1 shows the operation of a table read with program memory and data RAM.

Table write operations store data from the data memory space into holding registers in program memory. The procedure to write the contents of the holding registers into program memory is detailed in **Section 7.5 "Writing to Flash Program Memory"**. Figure 7-2 shows the operation of a table write with program memory and data RAM.

Table operations work with byte entities. A table block containing data, rather than program instructions, is not required to be word-aligned. Therefore, a table block can start and end at any byte address. If a table write is being used to write executable code into program memory, program instructions will need to be word-aligned.

FIGURE 7-1: TABLE READ OPERATION

NOTES:

## 11.2 PORTB, TRISB and LATB Registers

PORTB is an 8-bit wide, bidirectional port. The corresponding Data Direction register is TRISB. Setting a TRISB bit (= 1) will make the corresponding PORTB pin an input (i.e., put the corresponding output driver in a High-Impedance mode). Clearing a TRISB bit (= 0) will make the corresponding PORTB pin an output (i.e., put the contents of the output latch on the selected pin).

The Data Latch register (LATB) is also memory mapped. Read-modify-write operations on the LATB register read and write the latched output value for PORTB.

| CLRF  | PORTB  | ; Initialize PORTB by     |

|-------|--------|---------------------------|

|       |        | ; clearing output         |

|       |        | ; data latches            |

| CLRF  | LATB   | ; Alternate method        |

|       |        | ; to clear output         |

|       |        | ; data latches            |

| MOVLW | OFh    | ; Set RB<4:0> as          |

| MOVWF | ADCON1 | ; digital I/O pins        |

|       |        | ; (required if config bit |

|       |        | ; PBADEN is set)          |

| MOVLW | OCFh   | ; Value used to           |

|       |        | ; initialize data         |

|       |        | ; direction               |

| MOVWF | TRISB  | ; Set RB<3:0> as inputs   |

|       |        | ; RB<5:4> as outputs      |

|       |        | ; RB<7:6> as inputs       |

|       |        |                           |

Each of the PORTB pins has a weak internal pull-up. A single control bit can turn <u>on all</u> the pull-ups. This is performed by clearing bit, RBPU (INTCON2<7>). The weak pull-up is automatically turned off when the port pin is configured as an output. The pull-ups are disabled on a Power-on Reset.

| Note: | On a Power-on Reset, RB<4:0> are<br>configured as analog inputs by default and<br>read as '0'; RB<7:5> are configured as<br>digital inputs. |

|-------|---------------------------------------------------------------------------------------------------------------------------------------------|

|       | By clearing the Configuration bit,<br>PBADEN, RB<4:0> will alternatively be<br>configured as digital inputs on POR.                         |

Four of the PORTB pins (RB<7:4>) have an interrupton-change feature. Only pins configured as inputs can cause this interrupt to occur (i.e., any RB<7:4> pin configured as an output is excluded from the interrupton-change comparison). The input pins (of RB<7:4>) are compared with the old value latched on the last read of PORTB. The "mismatch" outputs of RB<7:4> are ORed together to generate the RB Port Change Interrupt with Flag bit, RBIF (INTCON<0>).

This interrupt can wake the device from Sleep mode or any of the Idle modes. The user, in the Interrupt Service Routine, can clear the interrupt in the following manner:

- a) Any read or write of PORTB (except with the MOVFF (ANY), PORTB instruction).

- b) 1 Tcy.

- c) Clear flag bit, RBIF.

A mismatch condition will continue to set flag bit, RBIF. Reading PORTB and waiting 1 Tcy will end the mismatch condition and allow flag bit, RBIF, to be cleared. Also, if the port pin returns to its original state, the mismatch condition will be cleared.

The interrupt-on-change feature is recommended for wake-up on key depression operation and operations where PORTB is only used for the interrupt-on-change feature. Polling of PORTB is not recommended while using the interrupt-on-change feature.

RB3 can be configured by the Configuration bit, CCP2MX, as the alternate peripheral pin for the CCP2 module (CCP2MX = 0).

NOTES:

# 13.0 TIMER1 MODULE

The Timer1 timer/counter module incorporates these features:

- Software selectable operation as a 16-bit timer or counter

- Readable and writable 8-bit registers (TMR1H and TMR1L)

- Selectable clock source (internal or external) with device clock or Timer1 oscillator internal options

- Interrupt-on-overflow

- Reset on CCP Special Event Trigger

- Device clock status flag (T1RUN)

A simplified block diagram of the Timer1 module is shown in Figure 13-1. A block diagram of the module's operation in Read/Write mode is shown in Figure 13-2.

The module incorporates its own low-power oscillator to provide an additional clocking option. The Timer1 oscillator can also be used as a low-power clock source for the microcontroller in power-managed operation.

Timer1 can also be used to provide Real-Time Clock (RTC) functionality to applications with only a minimal addition of external components and code overhead.

Timer1 is controlled through the T1CON Control register (Register 13-1). It also contains the Timer1 Oscillator Enable bit (T1OSCEN). Timer1 can be enabled or disabled by setting or clearing control bit, TMR1ON (T1CON<0>).

| STER 13-1: | T1CON: TIMER1 CONTROL REGISTER |                                                                                                                                                                  |                |                                |                 |                 |                |        |  |  |  |  |  |

|------------|--------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------|--------------------------------|-----------------|-----------------|----------------|--------|--|--|--|--|--|

|            | R/W-0                          | R-0                                                                                                                                                              | R/W-0          | R/W-0                          | R/W-0           | R/W-0           | R/W-0          | R/W-0  |  |  |  |  |  |

|            | RD16                           | T1RUN                                                                                                                                                            | T1CKPS1        | T1CKPS0                        | T1OSCEN         | T1SYNC          | TMR1CS         | TMR10N |  |  |  |  |  |

|            | bit 7                          |                                                                                                                                                                  |                |                                |                 |                 |                | bit 0  |  |  |  |  |  |

| bit 7      | <b>RD16:</b> 16                | -Bit Read/V                                                                                                                                                      | Vrite Mode E   | nable bit                      |                 |                 |                |        |  |  |  |  |  |

|            |                                | <ul> <li>1 = Enables register read/write of TImer1 in one 16-bit operation</li> <li>0 = Enables register read/write of Timer1 in two 8-bit operations</li> </ul> |                |                                |                 |                 |                |        |  |  |  |  |  |

| bit 6      | T1RUN: T                       | imer1 Syst                                                                                                                                                       | em Clock Sta   | atus bit                       |                 |                 |                |        |  |  |  |  |  |

|            |                                |                                                                                                                                                                  |                | Timer1 oscilla<br>another sour |                 |                 |                |        |  |  |  |  |  |

| bit 5-4    | T1CKPS<                        | : <b>1:0&gt;:</b> Time                                                                                                                                           | er1 Input Cloc | k Prescale S                   | elect bits      |                 |                |        |  |  |  |  |  |

|            |                                | Prescale va                                                                                                                                                      |                |                                |                 |                 |                |        |  |  |  |  |  |

|            |                                | Prescale va<br>Prescale va                                                                                                                                       |                |                                |                 |                 |                |        |  |  |  |  |  |

|            |                                | Prescale va                                                                                                                                                      |                |                                |                 |                 |                |        |  |  |  |  |  |

| bit 3      | T1OSCE                         | <b>1:</b> Timer1 C                                                                                                                                               | Scillator Ena  | ble bit                        |                 |                 |                |        |  |  |  |  |  |

|            | -                              | 1 oscillator                                                                                                                                                     |                |                                |                 |                 |                |        |  |  |  |  |  |

|            | • • • • • • •                  | 1 oscillator                                                                                                                                                     |                | ck resistor ar                 | e turned off to | o eliminate     | nower drain    |        |  |  |  |  |  |

| bit 2      |                                |                                                                                                                                                                  |                |                                | onization Sele  |                 |                |        |  |  |  |  |  |

|            |                                | R1CS = 1:                                                                                                                                                        |                |                                |                 |                 |                |        |  |  |  |  |  |

|            |                                | •                                                                                                                                                                | ze external c  | •                              |                 |                 |                |        |  |  |  |  |  |

|            | •                              |                                                                                                                                                                  | ernal clock in | put                            |                 |                 |                |        |  |  |  |  |  |

|            |                                | <u>R1CS = 0:</u><br>ianored Ti                                                                                                                                   | mer1 uses th   | e internal clo                 | ck when TMF     | <b>R1CS =</b> 0 |                |        |  |  |  |  |  |

| bit 1      |                                | 0                                                                                                                                                                | ock Source S   |                                |                 |                 |                |        |  |  |  |  |  |

|            |                                |                                                                                                                                                                  |                |                                | KI (on the ris  | sing edge)      |                |        |  |  |  |  |  |

|            |                                | nal clock (F                                                                                                                                                     |                |                                |                 |                 |                |        |  |  |  |  |  |

| bit 0      | TMR1ON: Timer1 On bit          |                                                                                                                                                                  |                |                                |                 |                 |                |        |  |  |  |  |  |

|            | 1 = Enab<br>0 = Stops          | les Timer1<br>Timer1                                                                                                                                             |                |                                |                 |                 |                |        |  |  |  |  |  |

|            | Legend:                        |                                                                                                                                                                  |                |                                |                 |                 |                |        |  |  |  |  |  |

|            | R = Read                       | able bit                                                                                                                                                         | VV = V         | Vritable bit                   | U = Unim        | plemented b     | oit, read as ' | 0'     |  |  |  |  |  |

|            | -n = Value                     | e at POR                                                                                                                                                         | '1' = E        | Bit is set                     | '0' = Bit is    | cleared         | x = Bit is u   | nknown |  |  |  |  |  |

|            |                                |                                                                                                                                                                  |                |                                |                 |                 |                |        |  |  |  |  |  |

## REGISTER 13-1: T1CON: TIMER1 CONTROL REGISTER

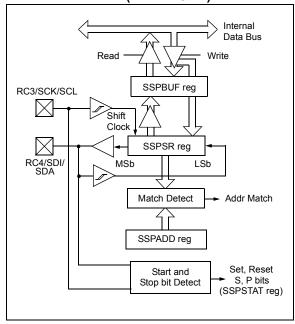

# 18.4 I<sup>2</sup>C Mode

The MSSP module in  $I^2C$  mode fully implements all master and slave functions (including general call support) and provides interrupts on Start and Stop bits in hardware to determine a free bus (multi-master function). The MSSP module implements the standard mode specifications, as well as 7-bit and 10-bit addressing.

Two pins are used for data transfer:

- Serial clock (SCL) RC3/SCK/SCL

- Serial data (SDA) RC4/SDI/SDA

The user must configure these pins as inputs or outputs through the TRISC<4:3> bits.

#### FIGURE 18-7: MSSP BLOCK DIAGRAM (I<sup>2</sup>C™ MODE)

# 18.4.1 REGISTERS

The MSSP module has six registers for  $\mathsf{I}^2\mathsf{C}$  operation. These are:

- MSSP Control Register 1 (SSPCON1)

- MSSP Control Register 2 (SSPCON2)

- MSSP Status Register (SSPSTAT)

- Serial Receive/Transmit Buffer Register (SSPBUF)

- MSSP Shift Register (SSPSR) Not directly accessible

- MSSP Address Register (SSPADD)

SSPCON1, SSPCON2 and SSPSTAT are the control and status registers in  $I^2C$  mode operation. The SSPCON1 and SSPCON2 registers are readable and writable. The lower 6 bits of the SSPSTAT are read-only. The upper two bits of the SSPSTAT are read/write.

SSPSR is the shift register used for shifting data in or out. SSPBUF is the buffer register to which data bytes are written to or read from.

SSPADD register holds the slave device address when the MSSP is configured in I<sup>2</sup>C Slave mode. When the MSSP is configured in Master mode, the lower seven bits of SSPADD act as the Baud Rate Generator reload value.

In receive operations, SSPSR and SSPBUF together create a double-buffered receiver. When SSPSR receives a complete byte, it is transferred to SSPBUF and the SSPIF interrupt is set.

During transmission, the SSPBUF is not doublebuffered. A write to SSPBUF will write to both SSPBUF and SSPSR.

### **REGISTER 18-4:** SSPCON1: MSSP CONTROL REGISTER 1 ( $I^2C^{TM}$ MODE)

| R/W-0 |

|-------|-------|-------|-------|-------|-------|-------|-------|

| WCOL  | SSPOV | SSPEN | CKP   | SSPM3 | SSPM2 | SSPM1 | SSPM0 |

| bit 7 |       |       |       |       |       |       | bit 0 |

#### bit 7 WCOL: Write Collision Detect bit

In Master Transmit mode:

- 1 = A write to the SSPBUF register was attempted while the I<sup>2</sup>C<sup>™</sup> conditions were not valid for a transmission to be started (must be cleared in software)

- 0 = No collision

In Slave Transmit mode:

- 1 = The SSPBUF register is written while it is still transmitting the previous word (must be cleared in software)

- 0 = No collision

In Receive mode (Master or Slave modes):

This is a "don't care" bit.

#### bit 6 SSPOV: Receive Overflow Indicator bit

#### In Receive mode:

- 1 = A byte is received while the SSPBUF register is still holding the previous byte (must be cleared in software)

- 0 = No overflow

#### In Transmit mode:

This is a "don't care" bit in Transmit mode.

#### bit 5 SSPEN: Master Synchronous Serial Port Enable bit

- 1 = Enables the serial port and configures the SDA and SCL pins as the serial port pins

- 0 = Disables serial port and configures these pins as I/O port pins

Note: When enabled, the SDA and SCL pins must be properly configured as inputs.

bit 4 **CKP:** SCK Release Control bit

In Slave mode:

- 1 = Release clock

- 0 = Holds clock low (clock stretch), used to ensure data setup time

In Master mode:

Unused in this mode.

#### bit 3-0 SSPM<3:0>: Master Synchronous Serial Port Mode Select bits

1111 =  $I^2C$  Slave mode, 10-bit address with Start and Stop bit interrupts enabled

- $1110 = I^2C$  Slave mode, 7-bit address with Start and Stop bit interrupts enabled

- $1011 = I^2C$  Firmware Controlled Master mode (slave Idle)

- $1000 = I^2C$  Master mode, clock = Fosc/(4 \* (SSPADD + 1))

- 0111 =  $I^2C$  Slave mode, 10-bit address

- 0110 =  $I^2C$  Slave mode, 7-bit address

Bit combinations not specifically listed here are either reserved or implemented in SPI mode only.

# Legend:

| Logona.           |                  |                      |                    |

|-------------------|------------------|----------------------|--------------------|

| R = Readable bit  | W = Writable bit | U = Unimplemented I  | bit, read as '0'   |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared | x = Bit is unknown |

# 18.4.10 I<sup>2</sup>C MASTER MODE TRANSMISSION

Transmission of a data byte, a 7-bit address or the other half of a 10-bit address is accomplished by simply writing a value to the SSPBUF register. This action will set the Buffer Full flag bit, BF and allow the Baud Rate Generator to begin counting and start the next transmission. Each bit of address/data will be shifted out onto the SDA pin after the falling edge of SCL is asserted (see data hold time specification parameter 106). SCL is held low for one Baud Rate Generator rollover count (TBRG). Data should be valid before SCL is released high (see data setup time specification parameter 107). When the SCL pin is released high, it is held that way for TBRG. The data on the SDA pin must remain stable for that duration and some hold time after the next falling edge of SCL. After the eighth bit is shifted out (the falling edge of the eighth clock), the BF flag is cleared and the master releases SDA. This allows the slave device being addressed to respond with an  $\overline{ACK}$  bit during the ninth bit time if an address match occurred, or if data was received properly. The status of ACK is written into the ACKDT bit on the falling edge of the ninth clock. If the master receives an Acknowledge, the Acknowledge Status bit, ACKSTAT, is cleared. If not, the bit is set. After the ninth clock, the SSPIF bit is set and the master clock (Baud Rate Generator) is suspended until the next data byte is loaded into the SSPBUF, leaving SCL low and SDA unchanged (Figure 18-23).

After the write to the SSPBUF, each bit of the address will be shifted out on the falling edge of SCL until all seven address bits and the R/W bit are completed. On the falling edge of the eighth clock, the master will deassert the SDA pin, allowing the slave to respond with an Acknowledge. On the falling edge of the ninth clock, the master will sample the SDA pin to see if the address was recognized by a slave. The status of the ACK bit is loaded into the ACKSTAT status bit (SSPCON2<6>). Following the falling edge of the ninth clock transmission of the address, the SSPIF is set, the BF flag is cleared and the Baud Rate Generator is turned off until another write to the SSPBUF takes place, holding SCL low and allowing SDA to float.

### 18.4.10.1 BF Status Flag

In Transmit mode, the BF bit (SSPSTAT<0>) is set when the CPU writes to SSPBUF and is cleared when all 8 bits are shifted out.

### 18.4.10.2 WCOL Status Flag

If the user writes the SSPBUF when a transmit is already in progress (i.e., SSPSR is still shifting out a data byte), the WCOL flag is set and the contents of the buffer are unchanged (the write doesn't occur) after 2 TcY after the SSPBUF write. If SSPBUF is rewritten within 2 TcY, the WCOL bit is set and SSPBUF is updated. This may result in a corrupted transfer. The user should verify that the WCOL flag is clear after each write to SSPBUF to ensure the transfer is correct.

### 18.4.10.3 ACKSTAT Status Flag

In Transmit mode, the ACKSTAT bit (SSPCON2<6>) is cleared when the slave has sent an Acknowledge  $(\overline{ACK} = 0)$  and is set when the slave does not Acknowledge  $(\overline{ACK} = 1)$ . A slave sends an Acknowledge when it has recognized its address (including a general call), or when the slave has properly received its data.

## 18.4.11 I<sup>2</sup>C MASTER MODE RECEPTION

Master mode reception is enabled by programming the Receive Enable bit, RCEN (SSPCON2<3>).

Note: The MSSP module must be in an Idle state before the RCEN bit is set or the RCEN bit will be disregarded.

The Baud Rate Generator begins counting and on each rollover, the state of the SCL pin changes (high-to-low/ low-to-high) and data is shifted into the SSPSR. After the falling edge of the eighth clock, the receive enable flag is automatically cleared, the contents of the SSPSR are loaded into the SSPBUF, the BF flag bit is set, the SSPIF flag bit is set and the Baud Rate Generator is suspended from counting, holding SCL low. The MSSP is now in Idle state awaiting the next command. When the buffer is read by the CPU, the BF flag bit is automatically cleared. The user can then send an Acknowledge bit at the end of reception by setting the Acknowledge Sequence Enable bit, ACKEN (SSPCON2<4>).

#### 18.4.11.1 BF Status Flag

In receive operation, the BF bit is set when an address or data byte is loaded into SSPBUF from SSPSR. It is cleared when the SSPBUF register is read.

#### 18.4.11.2 SSPOV Status Flag

In receive operation, the SSPOV bit is set when 8 bits are received into the SSPSR and the BF flag bit is already set from a previous reception.

#### 18.4.11.3 WCOL Status Flag

If the user writes the SSPBUF when a receive is already in progress (i.e., SSPSR is still shifting in a data byte), the WCOL bit is set and the contents of the buffer are unchanged (the write doesn't occur).

<sup>© 2009</sup> Microchip Technology Inc.

|             |                       |            |                             |                       | SYNC       | = 0, BRGH                   | I = 0, BRG            | <b>316 =</b> 0 |                             |                       |            |                             |

|-------------|-----------------------|------------|-----------------------------|-----------------------|------------|-----------------------------|-----------------------|----------------|-----------------------------|-----------------------|------------|-----------------------------|

| BAUD        | Fosc = 40.000 MHz     |            |                             | Fosc = 20.000 MHz     |            |                             | Fosc = 10.000 MHz     |                |                             | Fosc = 8.000 MHz      |            |                             |

| RATE<br>(K) | Actual<br>Rate<br>(K) | %<br>Error | SPBRG<br>value<br>(decimal) | Actual<br>Rate<br>(K) | %<br>Error | SPBRG<br>value<br>(decimal) | Actual<br>Rate<br>(K) | %<br>Error     | SPBRG<br>value<br>(decimal) | Actual<br>Rate<br>(K) | %<br>Error | SPBRG<br>value<br>(decimal) |

| 0.3         | _                     |            |                             |                       |            |                             | _                     |                | _                           |                       |            |                             |

| 1.2         | —                     | —          | —                           | 1.221                 | 1.73       | 255                         | 1.202                 | 0.16           | 129                         | 1.201                 | -0.16      | 103                         |

| 2.4         | 2.441                 | 1.73       | 255                         | 2.404                 | 0.16       | 129                         | 2.404                 | 0.16           | 64                          | 2.403                 | -0.16      | 51                          |

| 9.6         | 9.615                 | 0.16       | 64                          | 9.766                 | 1.73       | 31                          | 9.766                 | 1.73           | 15                          | 9.615                 | -0.16      | 12                          |

| 19.2        | 19.531                | 1.73       | 31                          | 19.531                | 1.73       | 15                          | 19.531                | 1.73           | 7                           | _                     | _          | _                           |

| 57.6        | 56.818                | -1.36      | 10                          | 62.500                | 8.51       | 4                           | 52.083                | -9.58          | 2                           | _                     | _          | _                           |

| 115.2       | 125.000               | 8.51       | 4                           | 104.167               | -9.58      | 2                           | 78.125                | -32.18         | 1                           | _                     | _          | _                           |

#### TABLE 19-3: BAUD RATES FOR ASYNCHRONOUS MODES

|              |                       | SYNC = 0, BRGH = 0, BRG16 = 0 |                             |                       |            |                             |                       |            |                             |  |  |  |  |  |

|--------------|-----------------------|-------------------------------|-----------------------------|-----------------------|------------|-----------------------------|-----------------------|------------|-----------------------------|--|--|--|--|--|

| BAUD<br>RATE | Fos                   | c = 4.000                     | MHz                         | Fos                   | c = 2.000  | MHz                         | Fosc = 1.000 MHz      |            |                             |  |  |  |  |  |

| (K)          | Actual<br>Rate<br>(K) | %<br>Error                    | SPBRG<br>value<br>(decimal) | Actual<br>Rate<br>(K) | %<br>Error | SPBRG<br>value<br>(decimal) | Actual<br>Rate<br>(K) | %<br>Error | SPBRG<br>value<br>(decimal) |  |  |  |  |  |

| 0.3          | 0.300                 | 0.16                          | 207                         | 0.300                 | -0.16      | 103                         | 0.300                 | -0.16      | 51                          |  |  |  |  |  |

| 1.2          | 1.202                 | 0.16                          | 51                          | 1.201                 | -0.16      | 25                          | 1.201                 | -0.16      | 12                          |  |  |  |  |  |

| 2.4          | 2.404                 | 0.16                          | 25                          | 2.403                 | -0.16      | 12                          | _                     | _          | _                           |  |  |  |  |  |

| 9.6          | 8.929                 | -6.99                         | 6                           | —                     | _          | _                           | _                     | _          | _                           |  |  |  |  |  |

| 19.2         | 20.833                | 8.51                          | 2                           | —                     | _          | _                           | _                     | _          | _                           |  |  |  |  |  |

| 57.6         | 62.500                | 8.51                          | 0                           | —                     | _          | _                           | —                     | _          | _                           |  |  |  |  |  |

| 115.2        | 62.500                | -45.75                        | 0                           | _                     | —          | —                           | _                     | _          |                             |  |  |  |  |  |

|             | SYNC = 0, BRGH = 1, BRG16 = 0 |                                                                           |     |                       |            |                             |                       |            |                             |                  |       |     |  |

|-------------|-------------------------------|---------------------------------------------------------------------------|-----|-----------------------|------------|-----------------------------|-----------------------|------------|-----------------------------|------------------|-------|-----|--|

| BAUD        | Fosc = 40.000 MHz             |                                                                           |     | Fosc = 20.000 MHz     |            |                             | Fosc = 10.000 MHz     |            |                             | Fosc = 8.000 MHz |       |     |  |

| RATE<br>(K) | Actual<br>Rate<br>(K)         | SPBRG Actual SPBRG<br>value Rate % value<br>(decimal) (K) Error (decimal) |     | Actual<br>Rate<br>(K) | %<br>Error | SPBRG<br>value<br>(decimal) | Actual<br>Rate<br>(K) | %<br>Error | SPBRG<br>value<br>(decimal) |                  |       |     |  |

| 0.3         | _                             |                                                                           | _   | —                     | _          | _                           |                       |            | _                           |                  | _     | _   |  |

| 1.2         | —                             | _                                                                         | _   | —                     | _          | _                           | —                     | _          | _                           | —                | _     | —   |  |

| 2.4         | —                             | _                                                                         | _   | —                     | _          | _                           | 2.441                 | 1.73       | 255                         | 2.403            | -0.16 | 207 |  |

| 9.6         | 9.766                         | 1.73                                                                      | 255 | 9.615                 | 0.16       | 129                         | 9.615                 | 0.16       | 64                          | 9.615            | -0.16 | 51  |  |

| 19.2        | 19.231                        | 0.16                                                                      | 129 | 19.231                | 0.16       | 64                          | 19.531                | 1.73       | 31                          | 19.230           | -0.16 | 25  |  |

| 57.6        | 58.140                        | 0.94                                                                      | 42  | 56.818                | -1.36      | 21                          | 56.818                | -1.36      | 10                          | 55.555           | 3.55  | 8   |  |

| 115.2       | 113.636                       | -1.36                                                                     | 21  | 113.636               | -1.36      | 10                          | 125.000               | 8.51       | 4                           | —                | _     | _   |  |

|              |                       | SYNC = 0, BRGH = 1, BRG16 = 0 |                             |                       |            |                             |                       |            |                             |  |  |  |  |

|--------------|-----------------------|-------------------------------|-----------------------------|-----------------------|------------|-----------------------------|-----------------------|------------|-----------------------------|--|--|--|--|

| BAUD<br>RATE | Foso                  | = 4.000                       | MHz                         | Fos                   | c = 2.000  | MHz                         | Fosc = 1.000 MHz      |            |                             |  |  |  |  |

| (K)          | Actual<br>Rate<br>(K) | %<br>Error                    | SPBRG<br>value<br>(decimal) | Actual<br>Rate<br>(K) | %<br>Error | SPBRG<br>value<br>(decimal) | Actual<br>Rate<br>(K) | %<br>Error | SPBRG<br>value<br>(decimal) |  |  |  |  |

| 0.3          | _                     |                               | _                           |                       |            | _                           | 0.300                 | -0.16      | 207                         |  |  |  |  |

| 1.2          | 1.202                 | 0.16                          | 207                         | 1.201                 | -0.16      | 103                         | 1.201                 | -0.16      | 51                          |  |  |  |  |

| 2.4          | 2.404                 | 0.16                          | 103                         | 2.403                 | -0.16      | 51                          | 2.403                 | -0.16      | 25                          |  |  |  |  |

| 9.6          | 9.615                 | 0.16                          | 25                          | 9.615                 | -0.16      | 12                          | _                     | _          | _                           |  |  |  |  |

| 19.2         | 19.231                | 0.16                          | 12                          | _                     | _          | _                           | _                     | _          | _                           |  |  |  |  |

| 57.6         | 62.500                | 8.51                          | 3                           | —                     | _          | _                           | —                     | _          | _                           |  |  |  |  |

| 115.2        | 125.000               | 8.51                          | 1                           |                       | _          | —                           | _                     | _          | _                           |  |  |  |  |

© 2009 Microchip Technology Inc.

| RLN         | ICF                                              | Rotate Le                                                                                                                                                                                     | eft f (No Car                                                                                                                                                                              | ry)                                                                                                                                                                                  |

|-------------|--------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Synt        | ax:                                              | RLNCF                                                                                                                                                                                         | f {,d {,a}}                                                                                                                                                                                |                                                                                                                                                                                      |

| Oper        | rands:                                           | $0 \le f \le 255$<br>$d \in [0, 1]$<br>$a \in [0, 1]$                                                                                                                                         |                                                                                                                                                                                            |                                                                                                                                                                                      |

| Oper        | ration:                                          | $(f \le n >) \rightarrow de$<br>$(f \le 7 >) \rightarrow de$                                                                                                                                  | est <n +="" 1="">,<br/>est&lt;0&gt;</n>                                                                                                                                                    |                                                                                                                                                                                      |

| Statu       | is Affected:                                     | N, Z                                                                                                                                                                                          |                                                                                                                                                                                            |                                                                                                                                                                                      |

| Enco        | oding:                                           | 0100                                                                                                                                                                                          | 01da ff                                                                                                                                                                                    | ff ffff                                                                                                                                                                              |

|             | pription:                                        | one bit to th<br>is placed in<br>stored back<br>If 'a' is '0', th<br>If 'a' is '1', th<br>GPR bank<br>If 'a' is '0' a<br>set is enabl<br>in Indexed<br>mode wher<br>Section 25<br>Bit-Oriente | W. If 'd' is '1'<br>is in register 'f'<br>he Access Ba<br>he BSR is use<br>(default).<br>Ind the extend<br>ed, this instru<br>Literal Offset<br>hever $f \le 95$ (5<br><b>.2.3 "Byte-O</b> | '0', the result is<br>(default).<br>nk is selected.<br>d to select the<br>led instruction<br>ction operates<br>Addressing<br>JFh). See<br>riented and<br>ns in Indexed<br>d details. |

| Word        | ds:                                              | 1                                                                                                                                                                                             |                                                                                                                                                                                            |                                                                                                                                                                                      |

| Cycle       | es:                                              | 1                                                                                                                                                                                             |                                                                                                                                                                                            |                                                                                                                                                                                      |

| QC          | ycle Activity:                                   |                                                                                                                                                                                               |                                                                                                                                                                                            |                                                                                                                                                                                      |

|             | Q1                                               | Q2                                                                                                                                                                                            | Q3                                                                                                                                                                                         | Q4                                                                                                                                                                                   |

|             | Decode                                           | Read<br>register 'f'                                                                                                                                                                          | Process<br>Data                                                                                                                                                                            | Write to destination                                                                                                                                                                 |

| <u>Exar</u> | nple:                                            | RLNCF                                                                                                                                                                                         | REG, 1,                                                                                                                                                                                    | 0                                                                                                                                                                                    |

|             | Before Instruc<br>REG<br>After Instructio<br>REG | = 1010 1                                                                                                                                                                                      | 011                                                                                                                                                                                        |                                                                                                                                                                                      |

|             | REG                                              | - 0101 0                                                                                                                                                                                      | 111                                                                                                                                                                                        |                                                                                                                                                                                      |

| RRC   | F                 | R                                                             | otate R                                                                                                                                                                                       | ight f th                                                                                                                                                                           | nroug                                                                                                                          | h Carry                                                                                                                                                                                    |

|-------|-------------------|---------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Synta | ax:               | R                                                             | RCF f                                                                                                                                                                                         | {,d {,a}}                                                                                                                                                                           |                                                                                                                                |                                                                                                                                                                                            |

| Oper  | ands:             | 0                                                             | ≤ f ≤ 255                                                                                                                                                                                     | 5                                                                                                                                                                                   |                                                                                                                                |                                                                                                                                                                                            |

|       |                   |                                                               | ∈ [0,1]                                                                                                                                                                                       |                                                                                                                                                                                     |                                                                                                                                |                                                                                                                                                                                            |

|       |                   | а                                                             | ∈[0,1]                                                                                                                                                                                        |                                                                                                                                                                                     |                                                                                                                                |                                                                                                                                                                                            |

| Oper  | ation:            | (f                                                            | $<$ n>) $\rightarrow$ (<br>$<$ 0>) $\rightarrow$ (<br>C) $\rightarrow$ des                                                                                                                    |                                                                                                                                                                                     | 1>,                                                                                                                            |                                                                                                                                                                                            |

| Statu | s Affected:       | С                                                             | , N, Z                                                                                                                                                                                        |                                                                                                                                                                                     |                                                                                                                                |                                                                                                                                                                                            |

| Enco  | dina:             | Г                                                             | 0011                                                                                                                                                                                          | 00da                                                                                                                                                                                | fft                                                                                                                            | f ffff                                                                                                                                                                                     |

|       | ription:          |                                                               |                                                                                                                                                                                               |                                                                                                                                                                                     |                                                                                                                                | ' are rotated                                                                                                                                                                              |

|       |                   | or<br>fla<br>If<br>If<br>If<br>G<br>If<br>So<br>If<br>So<br>B | he bit to f<br>ag. If 'd' is<br>'d' is '1',<br>agister 'f'<br>'a' is '0',<br>'a' is '0',<br>'a' is '1',<br>PR bank<br>'a' is '0'<br>et is enal<br>Indexed<br>ode whe<br>ection 2<br>it-Orient | the right<br>s '0', the<br>the resu<br>(default)<br>the Acce<br>the BSR<br>c (default)<br>and the e<br>oled, this<br>L Literal C<br>never f ≤<br>5.2.3 "B<br>ted Instri<br>fset Mod | through<br>result is<br>lt is pla<br>ess Bar<br>is use<br>).<br>extende<br>instruc<br>Offset A<br>595 (5F<br>yte-Ori<br>uction | n the Carry<br>s placed in W.<br>iced back in<br>hk is selected.<br>d to select the<br>ed instruction<br>ction operates<br>iddressing<br>Th). See<br>ented and<br>s in Indexed<br>details. |

| Word  | ls:               | 1                                                             |                                                                                                                                                                                               |                                                                                                                                                                                     |                                                                                                                                |                                                                                                                                                                                            |

| Cycle | es:               | 1                                                             |                                                                                                                                                                                               |                                                                                                                                                                                     |                                                                                                                                |                                                                                                                                                                                            |

| QC    | ycle Activity:    |                                                               |                                                                                                                                                                                               |                                                                                                                                                                                     |                                                                                                                                |                                                                                                                                                                                            |

|       | Q1                |                                                               | Q2                                                                                                                                                                                            | Q                                                                                                                                                                                   | 3                                                                                                                              | Q4                                                                                                                                                                                         |

|       | Decode            |                                                               | Read<br>gister 'f'                                                                                                                                                                            | Proc<br>Da                                                                                                                                                                          |                                                                                                                                | Write to destination                                                                                                                                                                       |

|       |                   |                                                               | 0                                                                                                                                                                                             |                                                                                                                                                                                     |                                                                                                                                |                                                                                                                                                                                            |

| Exan  | nple:             | R                                                             | RCF                                                                                                                                                                                           | REG,                                                                                                                                                                                | 0, (                                                                                                                           | )                                                                                                                                                                                          |

|       | Before Instruc    | tion                                                          |                                                                                                                                                                                               |                                                                                                                                                                                     |                                                                                                                                |                                                                                                                                                                                            |

|       | REG<br>C          | =<br>=                                                        | 1110<br><b>0</b>                                                                                                                                                                              | 0110                                                                                                                                                                                |                                                                                                                                |                                                                                                                                                                                            |

|       | After Instruction | n                                                             |                                                                                                                                                                                               |                                                                                                                                                                                     |                                                                                                                                |                                                                                                                                                                                            |

|       | REG               | =                                                             | 1110                                                                                                                                                                                          | 0110                                                                                                                                                                                |                                                                                                                                |                                                                                                                                                                                            |

|       | W                 | =                                                             | 0111                                                                                                                                                                                          | 0011                                                                                                                                                                                |                                                                                                                                |                                                                                                                                                                                            |

|       | С                 | =                                                             | 0                                                                                                                                                                                             |                                                                                                                                                                                     |                                                                                                                                |                                                                                                                                                                                            |

| SUBLW                                                        | 5           | Subtract                     | W from                   | n Lite  | ral |           |  |  |

|--------------------------------------------------------------|-------------|------------------------------|--------------------------|---------|-----|-----------|--|--|

| Syntax:                                                      | 9           | SUBLW k                      |                          |         |     |           |  |  |

| Operands:                                                    | C           | $0 \le k \le 255$            |                          |         |     |           |  |  |

| Operation:                                                   | k           | $i - (W) \rightarrow$        | W                        |         |     |           |  |  |

| Status Affected:                                             | ١           | I, OV, C,                    | DC, Z                    |         |     |           |  |  |

| Encoding:                                                    | Γ           | 0000                         | 1000                     | kkk     | k   | kkkk      |  |  |