Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

### Details

E·XFI

| Product Status             | Active                                                                     |

|----------------------------|----------------------------------------------------------------------------|

| Core Processor             | PIC                                                                        |

| Core Size                  | 8-Bit                                                                      |

| Speed                      | 40MHz                                                                      |

| Connectivity               | I <sup>2</sup> C, SPI, UART/USART                                          |

| Peripherals                | Brown-out Detect/Reset, HLVD, POR, PWM, WDT                                |

| Number of I/O              | 36                                                                         |

| Program Memory Size        | 8KB (4K × 16)                                                              |

| Program Memory Type        | FLASH                                                                      |

| EEPROM Size                | 256 x 8                                                                    |

| RAM Size                   | 512 x 8                                                                    |

| Voltage - Supply (Vcc/Vdd) | 2V ~ 5.5V                                                                  |

| Data Converters            | A/D 13x10b                                                                 |

| Oscillator Type            | Internal                                                                   |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                          |

| Mounting Type              | Surface Mount                                                              |

| Package / Case             | 44-TQFP                                                                    |

| Supplier Device Package    | 44-TQFP (10x10)                                                            |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic18lf4321-i-pt |

|                            |                                                                            |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

| Pin Name                                                                                                                                                                                                          | Pin Number |     |      | Pin Bu | Buffer | Description                                                                                                                                |  |  |  |

|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------|-----|------|--------|--------|--------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|

|                                                                                                                                                                                                                   | PDIP       | QFN | TQFP | Туре   | Туре   | Description                                                                                                                                |  |  |  |

| MCLR/VPP/RE3<br>MCLR                                                                                                                                                                                              | 1          | 18  | 18   | I      | ST     | Master Clear (input) or programming voltage (input).<br>Master Clear (Reset) input. This pin is an active-low<br>Reset to the device.      |  |  |  |

| Vpp                                                                                                                                                                                                               |            |     |      | Р      |        | Programming voltage input.                                                                                                                 |  |  |  |

| RE3                                                                                                                                                                                                               |            |     |      | Ι      | ST     | Digital input.                                                                                                                             |  |  |  |

| OSC1/CLKI/RA7<br>OSC1                                                                                                                                                                                             | 13         | 32  | 30   | I      | Analog | ST buffer when configured in RC mode;                                                                                                      |  |  |  |

| CLKI                                                                                                                                                                                                              |            |     |      | Ι      | Analog | analog otherwise.<br>External clock source input. Always associated with<br>pin function OSC1. (See related OSC1/CLKI,<br>OSC2/CLKO pins.) |  |  |  |

| RA7                                                                                                                                                                                                               |            |     |      | I/O    | TTL    | General purpose I/O pin.                                                                                                                   |  |  |  |

| OSC2/CLKO/RA6<br>OSC2                                                                                                                                                                                             | 14         | 33  | 31   | 0      | _      | Oscillator crystal or clock output.<br>Oscillator crystal output. Connects to crystal<br>or resonator in Crystal Oscillator mode.          |  |  |  |

| CLKO                                                                                                                                                                                                              |            |     |      | 0      | —      | In RC, EC and INTIO modes, OSC2 pin outputs<br>CLKO which has one-fourth the frequency of OSC1                                             |  |  |  |

| RA6                                                                                                                                                                                                               |            |     |      | I/O    | TTL    | and denotes the instruction cycle rate.<br>General purpose I/O pin.                                                                        |  |  |  |

| Legend:TTL = TTL compatible inputTTL = TTL compatible inputCMOS = CMOS compatible input or outputST = Schmitt Trigger input with CMOS levelsI= InputP = Power $I^2C$ = ST with $I^2C^{TM}$ or SMB levelsO= Output |            |     |      |        |        |                                                                                                                                            |  |  |  |

### TABLE 1-3: PIC18F4221/4321 PINOUT I/O DESCRIPTIONS

Note 1: Default assignment for CCP2 when Configuration bit, CCP2MX, is set.

2: Alternate assignment for CCP2 when Configuration bit, CCP2MX, is cleared.

### 3.8 Effects of Power-Managed Modes on the Various Clock Sources

When PRI\_IDLE mode is selected, the designated primary oscillator continues to run without interruption. For all other power-managed modes, the oscillator using the OSC1 pin is disabled. The OSC1 pin (and OSC2 pin in Crystal Oscillator modes) will stop oscillating.

In secondary clock modes (SEC\_RUN and SEC\_IDLE), the Timer1 oscillator is operating and providing the device clock. The Timer1 oscillator may also run in all power-managed modes if required to clock Timer1 or Timer3.

In internal oscillator modes (RC\_RUN and RC\_IDLE), the internal oscillator block provides the device clock source. The 31 kHz INTRC output can be used directly to provide the clock and may be enabled to support various special features, regardless of the powermanaged mode (see Section 24.2 "Watchdog Timer (WDT)", Section 24.3 "Two-Speed Start-up" and Section 24.4 "Fail-Safe Clock Monitor" for more information). The INTOSC output at 8 MHz may be used directly to clock the device or may be divided down by the postscaler. The INTOSC output is disabled if the clock is provided directly from the INTRC output. The INTOSC output is also enabled for Two-Speed Start-up at 1 MHz after a Reset.

If the Sleep mode is selected, all clock sources are stopped. Since all the transistor switching currents have been stopped, Sleep mode achieves the lowest current consumption of the device (only leakage currents).

Enabling any on-chip feature that will operate during Sleep will increase the current consumed during Sleep. The INTRC is required to support WDT operation. The Timer1 oscillator may be operating to support a Real-Time Clock. Other features may be operating that do not require a device clock source (i.e., MSSP slave, PSP, INTx pins and others). Peripherals that may add significant current consumption are listed in **Section 27.2 "DC Characteristics".**

### 3.9 Power-up Delays

Power-up delays are controlled by two or three timers, so that no external Reset circuitry is required for most applications. The delays ensure that the device is kept in Reset until the device power supply is stable under normal circumstances and the primary clock is operating and stable. For additional information on power-up delays, see **Section 5.5 "Device Reset Timers"**.

The first timer is the Power-up Timer (PWRT) which provides a fixed delay on power-up (parameter 33, Table 27-10). It is enabled by clearing (= 0) the PWRTEN Configuration bit (CONFIG2L<0>).

### 3.9.1 DELAYS FOR POWER-UP AND RETURN TO PRIMARY CLOCK

The second timer is the Oscillator Start-up Timer (OST), intended to delay execution until the crystal oscillator is stable (LP, XT and HS modes). The OST does this by counting 1024 oscillator cycles before allowing the oscillator to clock the device.

When the HSPLL Oscillator mode is selected, a third timer delays execution for an additional 2 ms following the HS mode OST delay, so the PLL can lock to the incoming clock frequency. At the end of these delays, the OSTS bit (OSCCON<3>) is set.

There is a delay of interval TCSD (parameter 38, Table 27-10), once execution is allowed to start, when the controller becomes ready to execute instructions. This delay runs concurrently with any other delays. This may be the only delay that occurs when any of the EC, RC or INTIO modes are used as the primary clock source.

| OSC Mode      | OSC1 Pin                                              | OSC2 Pin                                              |

|---------------|-------------------------------------------------------|-------------------------------------------------------|

| RC, INTIO1    | Floating, external resistor pulls high                | At logic low (clock/4 output)                         |

| RCIO          | Floating, external resistor pulls high                | Configured as PORTA, bit 6                            |

| INTIO2        | Configured as PORTA, bit 7                            | Configured as PORTA, bit 6                            |

| ECIO          | Floating, driven by external clock                    | Configured as PORTA, bit 6                            |

| EC            | Floating, driven by external clock                    | At logic low (clock/4 output)                         |

| LP, XT and HS | Feedback inverter disabled at quiescent voltage level | Feedback inverter disabled at quiescent voltage level |

TABLE 3-3:OSC1 AND OSC2 PIN STATES IN SLEEP MODE

**Note:** See Table 5-2 in **Section 5.0 "Reset"** for time-outs due to Sleep and MCLR Reset.

### 4.4.1 PRI\_IDLE MODE

This mode is unique among the three low-power Idle modes, in that it does not disable the primary device clock. For timing sensitive applications, this allows for the fastest resumption of device operation with its more accurate primary clock source, since the clock source does not have to "warm-up" or transition from another oscillator.

PRI\_IDLE mode is entered from PRI\_RUN mode by setting the IDLEN bit and executing a SLEEP instruction. If the device is in another Run mode, set IDLEN first, then clear the SCS bits and execute SLEEP. Although the CPU is disabled, the peripherals continue to be clocked from the primary clock source specified by the FOSC<3:0> Configuration bits. The OSTS bit remains set (see Figure 4-7).

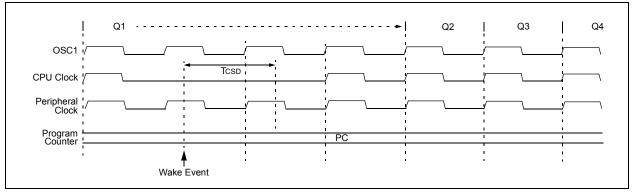

When a wake event occurs, the CPU is clocked from the primary clock source. A delay of interval TCSD (parameter 38, Table 27-10) is required between the wake event and when code execution starts. This is required to allow the CPU to become ready to execute instructions. After the wake-up, the OSTS bit remains set. The IDLEN and SCS bits are not affected by the wake-up (see Figure 4-8).

### 4.4.2 SEC\_IDLE MODE

In SEC\_IDLE mode, the CPU is disabled but the peripherals continue to be clocked from the Timer1 oscillator. This mode is entered from SEC\_RUN by setting the IDLEN bit and executing a SLEEP instruction. If the device is in another Run mode, set the IDLEN bit first, then set the SCS<1:0> bits to '01' and execute SLEEP. When the clock source is switched to the Timer1 oscillator, the primary oscillator is shut down, the OSTS bit is cleared and the T1RUN bit is set.

When a wake event occurs, the peripherals continue to be clocked from the Timer1 oscillator. After an interval of TCSD following the wake event, the CPU begins executing code being clocked by the Timer1 oscillator. The IDLEN and SCS bits are not affected by the wake-up; the Timer1 oscillator continues to run (see Figure 4-8).

Note: The Timer1 oscillator should already be running prior to entering SEC\_IDLE mode. If the T1OSCEN bit is not set when writing the SCS<1:0> bits, entry to SEC\_IDLE mode will not occur. If the Timer1 oscillator is enabled but not yet running, peripheral clocks will be delayed until the oscillator has started. In such situations, initial oscillator operation is far from stable and unpredictable operation may result.

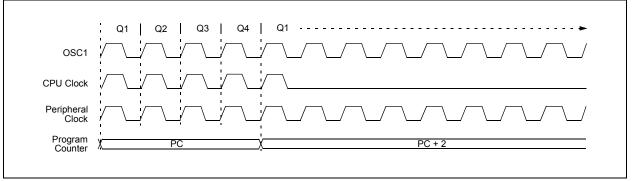

### FIGURE 4-7: TRANSITION TIMING FOR ENTRY TO IDLE MODE

### FIGURE 4-8: TRANSITION TIMING FOR WAKE FROM IDLE TO RUN MODE

### 6.1.1 PROGRAM COUNTER

The Program Counter (PC) specifies the address of the instruction to fetch for execution. The PC is 21 bits wide and is contained in three separate 8-bit registers. The low byte, known as the PCL register, is both readable and writable. The high byte, or PCH register, contains the PC<15:8> bits; it is not directly readable or writable. Updates to the PCH register are performed through the PCLATH register. The upper byte is called PCU. This register contains the PC<20:16> bits; it is also not directly readable or writable. Updates to the PCH register. Updates to the PCU register are performed through the PCLATH register contains the PC<20:16> bits; it is also not directly readable or writable. Updates to the PCU register are performed through the PCLATU register.

The contents of PCLATH and PCLATU are transferred to the program counter by any operation that writes PCL. Similarly, the upper two bytes of the program counter are transferred to PCLATH and PCLATU by an operation that reads PCL. This is useful for computed offsets to the PC (see **Section 6.1.4.1 "Computed GOTO"**).

The PC addresses bytes in the program memory. To prevent the PC from becoming misaligned with word instructions, the Least Significant bit of PCL is fixed to a value of '0'. The PC increments by 2 to address sequential instructions in the program memory.

The CALL, RCALL, GOTO and program branch instructions write to the program counter directly. For these instructions, the contents of PCLATH and PCLATU are not transferred to the program counter.

### 6.1.2 RETURN ADDRESS STACK

The return address stack allows any combination of up to 31 program calls and interrupts to occur. The PC is pushed onto the stack when a CALL or RCALL instruction is executed or an interrupt is Acknowledged. The PC value is pulled off the stack on a RETURN, RETLW or a RETFIE instruction. PCLATU and PCLATH are not affected by any of the RETURN or CALL instructions.

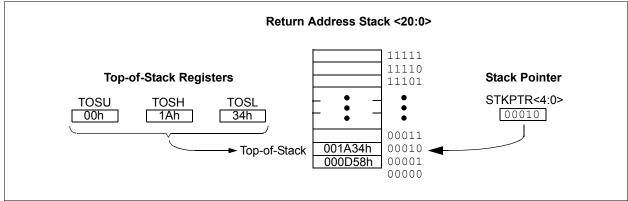

The stack operates as a 31-word by 21-bit RAM and a 5-bit Stack Pointer, STKPTR. The stack space is not part of either program or data space. The Stack Pointer is readable and writable and the address on the top of the stack is readable and writable through the Top-of-Stack Special Function Registers. Data can also be pushed to, or popped from the stack, using these registers.

A CALL type instruction causes a push onto the stack; the Stack Pointer is first incremented and the location pointed to by the Stack Pointer is written with the contents of the PC (already pointing to the instruction following the CALL). A RETURN type instruction causes a pop from the stack; the contents of the location pointed to by the STKPTR are transferred to the PC and then the Stack Pointer is decremented.

The Stack Pointer is initialized to '00000' after all Resets. There is no RAM associated with the location corresponding to a Stack Pointer value of '00000'; this is only a Reset value. Status bits indicate if the stack is full or has overflowed or has underflowed.

### 6.1.2.1 Top-of-Stack Access

Only the top of the return address stack (TOS) is readable and writable. A set of three registers, TOSU:TOSH:TOSL, hold the contents of the stack location pointed to by the STKPTR register (Figure 6-2). This allows users to implement a software stack if necessary. After a CALL, RCALL or interrupt, the software can read the pushed value by reading the TOSU:TOSH:TOSL registers. These values can be placed on a user-defined software stack. At return time, the software can return these values to TOSU:TOSH:TOSL and do a return.

The user must disable the global interrupt enable bits while accessing the stack to prevent inadvertent stack corruption.

### FIGURE 6-2: RETURN ADDRESS STACK AND ASSOCIATED REGISTERS

### 8.5 Operation During Code-Protect

Data EEPROM memory has its own code-protect bits in Configuration Words. External read and write operations are disabled if code protection is enabled.

The microcontroller itself can both read and write to the internal data EEPROM, regardless of the state of the code-protect Configuration bit. Refer to Section 24.0 "Special Features of the CPU" for additional information.

### 8.6 Protection Against Spurious Write

To protect against spurious EEPROM writes, various mechanisms have been implemented. On power-up, the WREN bit is cleared. In addition, writes to the EEPROM are blocked during the Power-up Timer period (TPWRT, parameter 33).

The write initiate sequence and the WREN bit together help prevent an accidental write during Brown-out Reset, power glitch or software malfunction.

### 8.7 Using the Data EEPROM

The data EEPROM is a high-endurance, byte addressable array that has been optimized for the storage of frequently changing data. Such data is typically updated at least one time within the number of writes defined by specification, D124. If any location storing data is not written at least this often, the data EEPROM array must be refreshed. For this reason, values that change infrequently, or not at all, should be stored in Flash program memory.

A simple data EEPROM refresh routine is shown in Example 8-3.

**Note:** If data EEPROM is only used to store constants and/or data that changes often, an array refresh is likely not required. See specification, D124.

| EXAMPLE 8-3: | DATA EEPROM REFRESH ROUTINE |

|--------------|-----------------------------|

|--------------|-----------------------------|

|      |        | DATA EEL KG   |                              |

|------|--------|---------------|------------------------------|

|      | CLRF   | EEADR         | ; Start at address 0         |

|      | BCF    | EECON1, CFGS  | ; Set for memory             |

|      | BCF    | EECON1, EEPGD | ; Set for Data EEPROM        |

|      | BCF    | INTCON, GIE   | ; Disable interrupts         |

|      | BSF    | EECON1, WREN  | ; Enable writes              |

| LOOP |        |               | ; Loop to refresh array      |

|      | BSF    | EECON1, RD    | ; Read current address       |

|      | MOVLW  | 55h           | ;                            |

|      | MOVWF  | EECON2        | ; Write 55h                  |

|      | MOVLW  | 0AAh          | ;                            |

|      | MOVWF  | EECON2        | ; Write OAAh                 |

|      | BSF    | EECON1, WR    | ; Set WR bit to begin write  |

|      | BTFSC  | EECON1, WR    | ; Wait for write to complete |

|      | BRA    | \$-2          |                              |

|      | INCFSZ | EEADR, F      | ; Increment address          |

|      | BRA    | LOOP          | ; Not zero, do it again      |

|      | BCF    | EECON1, WREN  | ; Disable writes             |

|      | BSF    | INTCON, GIE   | ; Enable interrupts          |

| 1    |        |               |                              |

| Pin                                                               | Function | TRIS<br>Setting                                             | I/O                                                                                                                                                               | I/O<br>Type | Description                                                                                                          |

|-------------------------------------------------------------------|----------|-------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------|----------------------------------------------------------------------------------------------------------------------|

| RA0/AN0                                                           | RA0      | 0                                                           | 0                                                                                                                                                                 | DIG         | LATA<0> data output; not affected by analog input.                                                                   |

|                                                                   |          | 1                                                           | I                                                                                                                                                                 | TTL         | PORTA<0> data input; disabled when analog input enabled.                                                             |

|                                                                   | AN0      | 1                                                           | Ι                                                                                                                                                                 | ANA         | A/D Input Channel 0 and Comparator C1- input. Default input configuration on POR; does not affect digital output.    |

| RA1/AN1                                                           | RA1      | 0                                                           | O         DIG         LATA<1> data output; not affected by analog input.           I         TTL         PORTA<1> data input; disabled when analog input enabled. |             |                                                                                                                      |

|                                                                   |          | 1                                                           |                                                                                                                                                                   | TTL         | PORTA<1> data input; disabled when analog input enabled.                                                             |

|                                                                   | AN1      | 1                                                           | -                                                                                                                                                                 | ANA         | A/D Input Channel 1 and Comparator C2- input. Default input<br>configuration on POR; does not affect digital output. |

| RA2/AN2/<br>Vref-/CVref                                           | RA2      | 0                                                           | 0                                                                                                                                                                 | DIG         | LATA<2> data output; not affected by analog input. Disabled when CVREF output enabled.                               |

|                                                                   |          | 1                                                           | Ι                                                                                                                                                                 | TTL         | PORTA<2> data input. Disabled when analog functions enabled;<br>disabled when CVREF output enabled.                  |

|                                                                   | AN2      | 1                                                           | Ι                                                                                                                                                                 | ANA         | A/D Input Channel 2 and Comparator C2+ input. Default input<br>configuration on POR; not affected by analog output.  |

|                                                                   | VREF-    | 1                                                           | Ι                                                                                                                                                                 | ANA         | A/D and comparator voltage reference low input.                                                                      |

|                                                                   | CVREF    | х                                                           | 0                                                                                                                                                                 | ANA         | Comparator voltage reference output. Enabling this feature disables digital I/O.                                     |

| RA3/AN3/VREF+                                                     | RA3      | 0                                                           | 0                                                                                                                                                                 | DIG         | LATA<3> data output; not affected by analog input.                                                                   |

|                                                                   |          | 1                                                           | Ι                                                                                                                                                                 | TTL         | PORTA<3> data input; disabled when analog input enabled.                                                             |

|                                                                   | AN3      | 1                                                           | Ι                                                                                                                                                                 | ANA         | A/D Input Channel 3 and Comparator C1+ input. Default input<br>configuration on POR.                                 |

|                                                                   | VREF+    | 1                                                           | Ι                                                                                                                                                                 | ANA         | A/D and comparator voltage reference high input.                                                                     |

| RA4/T0CKI/C1OUT                                                   | RA4      | 0                                                           | 0                                                                                                                                                                 | DIG         | LATA<4> data output.                                                                                                 |

|                                                                   |          | 1                                                           |                                                                                                                                                                   | ST          | PORTA<4> data input; default configuration on POR.                                                                   |

|                                                                   | TOCKI    | 1                                                           | -                                                                                                                                                                 | ST          | Timer0 clock input.                                                                                                  |

|                                                                   | C10UT    | 0                                                           | 0                                                                                                                                                                 | DIG         | Comparator 1 output; takes priority over port data.                                                                  |

| RA5/AN4/SS/                                                       | RA5      | 0                                                           | 0                                                                                                                                                                 | DIG         | LATA<5> data output; not affected by analog input.                                                                   |

| HLVDIN/C2OUT                                                      |          | 1                                                           | Ι                                                                                                                                                                 | TTL         | PORTA<5> data input; disabled when analog input enabled.                                                             |

|                                                                   | AN4      | 1                                                           | Ι                                                                                                                                                                 | ANA         | A/D Input Channel 4. Default configuration on POR.                                                                   |

|                                                                   | SS       | 1                                                           | Ι                                                                                                                                                                 | TTL         | Slave Select input for MSSP (MSSP module).                                                                           |

|                                                                   | HLVDIN   | 1                                                           | Ι                                                                                                                                                                 | ANA         | High/Low-Voltage Detect external trip point input.                                                                   |

|                                                                   | C2OUT    | 0                                                           | 0                                                                                                                                                                 | DIG         | Comparator 2 output; takes priority over port data.                                                                  |

| OSC2/CLKO/RA6                                                     | RA6      | 0                                                           | 0                                                                                                                                                                 | DIG         | LATA<6> data output. Enabled in RCIO, INTIO2 and ECIO modes only.                                                    |

|                                                                   |          | 1                                                           | Ι                                                                                                                                                                 | TTL         | PORTA<6> data input. Enabled in RCIO, INTIO2 and ECIO modes only.                                                    |

|                                                                   | OSC2     | x                                                           | 0                                                                                                                                                                 | ANA         | Main oscillator feedback output connection (XT, HS and LP modes).                                                    |

|                                                                   | CLKO     | x                                                           | 0                                                                                                                                                                 | DIG         | System cycle clock output (Fosc/4) in RC, INTIO1 and EC Oscillator modes.                                            |

| OSC1/CLKI/RA7 RA7 0 O DIG LATA<7> data output. Disabled in extern |          | LATA<7> data output. Disabled in external oscillator modes. |                                                                                                                                                                   |             |                                                                                                                      |

|                                                                   |          | 1                                                           | Ι                                                                                                                                                                 | TTL         | PORTA<7> data input. Disabled in external oscillator modes.                                                          |

|                                                                   | OSC1     | х                                                           | Ι                                                                                                                                                                 | ANA         | Main oscillator input connection.                                                                                    |

|                                                                   | CLKI     | х                                                           | Ι                                                                                                                                                                 | ANA         | Main clock input connection.                                                                                         |

### TABLE 11-1: PORTA I/O SUMMARY

Legend: DIG = Digital level output; TTL = TTL input buffer; ST = Schmitt Trigger input buffer; ANA = Analog level input/output; x = Don't care (TRIS bit does not affect port direction or is overridden for this option).

| TABLE 11-4: | SUMMARY OF REGISTERS ASSOCIATED WITH PORTB |

|-------------|--------------------------------------------|

|-------------|--------------------------------------------|

| Name    | Bit 7                                        | Bit 6                                                    | Bit 5    | Bit 4  | Bit 3  | Bit 2  | Bit 1  | Bit 0  | Reset<br>Values<br>on page |  |

|---------|----------------------------------------------|----------------------------------------------------------|----------|--------|--------|--------|--------|--------|----------------------------|--|

| PORTB   | RB7                                          | RB6                                                      | RB5      | RB4    | RB3    | RB2    | RB1    | RB0    | 58                         |  |

| LATB    | PORTB Dat                                    | PORTB Data Latch Register (Read and Write to Data Latch) |          |        |        |        |        |        |                            |  |

| TRISB   | PORTB Dat                                    | a Direction R                                            | Register |        |        |        |        |        | 58                         |  |

| INTCON  | GIE/GIEH                                     | PEIE/GIEL                                                | TMR0IE   | INT0IE | RBIE   | TMR0IF | INT0IF | RBIF   | 55                         |  |

| INTCON2 | RBPU INTEDGO INTEDG1 INTEDG2 — TMR0IP — RBIP |                                                          |          |        |        |        |        |        | 55                         |  |

| INTCON3 | INT2IP                                       | INT1IP                                                   | _        | INT2IE | INT1IE | _      | INT2IF | INT1IF | 55                         |  |

| ADCON1  |                                              | _                                                        | VCFG1    | VCFG0  | PCFG3  | PCFG2  | PCFG1  | PCFG0  | 57                         |  |

**Legend:** — = unimplemented, read as '0'. Shaded cells are not used by PORTB.

### 11.5 PORTE, TRISE and LATE Registers

Depending on the particular PIC18F2221/2321/4221/ 4321 family device selected, PORTE is implemented in two different ways.

For 40/44-pin devices, PORTE is a 4-bit wide port. Three pins (RE0/RD/AN5, RE1/WR/AN6 and RE2/CS/ AN7) are individually configurable as inputs or outputs. These pins have Schmitt Trigger input buffers. When selected as analog inputs, these pins will read as '0'.

The corresponding Data Direction register is TRISE. Setting a TRISE bit (= 1) will make the corresponding PORTE pin an input (i.e., put the corresponding output driver in a High-Impedance mode). Clearing a TRISE bit (= 0) will make the corresponding PORTE pin an output (i.e., put the contents of the output latch on the selected pin).

TRISE controls the direction of the RE pins, even when they are being used as analog inputs. The user must make sure to keep the pins configured as inputs when using them as analog inputs.

| Note: | On  | а    | Power-on    | Reset,   | RE<2:0> | are |

|-------|-----|------|-------------|----------|---------|-----|

|       | con | figu | red as anal | og input | 5.      |     |

The upper four bits of the TRISE register also control the operation of the Parallel Slave Port. Their operation is explained in Register 11-1.

The Data Latch register (LATE) is also memory mapped. Read-modify-write operations on the LATE register, read and write the latched output value for PORTE.

The fourth pin of PORTE ( $\overline{\text{MCLR}}/\text{VPP}/\text{RE3}$ ) is an input only pin. Its operation is controlled by the MCLRE Configuration bit. When selected as a port pin (MCLRE = 0), it functions as a digital input only pin; as such, it does not have TRIS or LAT bits associated with its operation. Otherwise, it functions as the device's Master Clear input. In either configuration, RE3 also functions as the programming voltage input during programming.

| Note: | On a Power-on Reset, RE3 is enabled as |  |  |  |  |  |  |  |  |  |

|-------|----------------------------------------|--|--|--|--|--|--|--|--|--|

|       | a digital input only if Master Clear   |  |  |  |  |  |  |  |  |  |

|       | functionality is disabled.             |  |  |  |  |  |  |  |  |  |

### EXAMPLE 11-5: INITIALIZING PORTE

|       | -      |   |                                     |

|-------|--------|---|-------------------------------------|

| CLRF  | PORTE  |   | Initialize PORTE by clearing output |

|       |        | ; | data latches                        |

| CLRF  | LATE   | ; | Alternate method                    |

|       |        | ; | to clear output                     |

|       |        | ; | data latches                        |

| MOVLW | OFh    | ; | Configure A/D                       |

| MOVWF | ADCON1 | ; | for digital inputs                  |

| MOVLW | 03h    | ; | Value used to                       |

|       |        | ; | initialize data                     |

|       |        | ; | direction                           |

| MOVWF | TRISE  | ; | Set RE<0> as inputs                 |

|       |        | ; | RE<1> as outputs                    |

|       |        | ; | RE<2> as inputs                     |

|       |        |   |                                     |

### 11.5.1 PORTE IN 28-PIN DEVICES

For 28-pin devices, PORTE is only available when Master Clear functionality is disabled (MCLRE = 0). In these cases, PORTE is a single bit, input only port comprised of RE3 only. The pin operates as previously described.

| REGISTER 17-3: | ECCP1AS                                                                                                                                                                                               |                                                                           |                                               | JRE/COMP     | PARE/PW     | M AUTO-  | SHUTDOW               | N                     |

|----------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------|-----------------------------------------------|--------------|-------------|----------|-----------------------|-----------------------|

|                | R/W-0                                                                                                                                                                                                 | R/W-0                                                                     | R/W-0                                         | R/W-0        | R/W-0       | R/W-0    | R/W-0                 | R/W-0                 |

|                | ECCPASE                                                                                                                                                                                               | ECCPAS2                                                                   | ECCPAS1                                       | ECCPAS0      | PSSAC1      | PSSAC0   | PSSBD1 <sup>(1)</sup> | PSSBD0 <sup>(1)</sup> |

|                | bit 7                                                                                                                                                                                                 |                                                                           |                                               |              |             |          |                       | bit 0                 |

| bit 7          | ECCPASE:                                                                                                                                                                                              | ECCP Auto                                                                 | -Shutdown                                     | Event Status | bit         |          |                       |                       |

|                | 1 = A shuto<br>0 = ECCP                                                                                                                                                                               |                                                                           |                                               | d; ECCP out  | puts are in | shutdown | state                 |                       |

| bit 6-4        | ECCPAS<2                                                                                                                                                                                              | :0>: ECCP                                                                 | Auto-Shutdo                                   | own Source   | Select bits |          |                       |                       |

|                | 111 = FLT0<br>110 = FLT0<br>101 = FLT0<br>011 = Eithe<br>010 = Com<br>001 = Com<br>000 = Auto                                                                                                         | or Compara<br>or Comparate<br>r Comparate<br>parator 2 ou<br>parator 1 ou | ator 2<br>ator 1<br>or 1 or 2<br>tput<br>tput | mparator 2   |             |          |                       |                       |

| bit 3-2        | <ul> <li>1x = Pins A and C are tri-state (40/44-pin devices);<br/>PWM output is tri-state (28-pin devices)</li> <li>01 = Drive Pins A and C to '1'</li> <li>00 = Drive Pins A and C to '0'</li> </ul> |                                                                           |                                               |              |             |          |                       |                       |

| bit 1-0        |                                                                                                                                                                                                       |                                                                           |                                               |              |             |          |                       |                       |

| Legend:           |                  |                      |                    |

|-------------------|------------------|----------------------|--------------------|

| R = Readable bit  | W = Writable bit | U = Unimplemented    | bit, read as '0'   |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared | x = Bit is unknown |

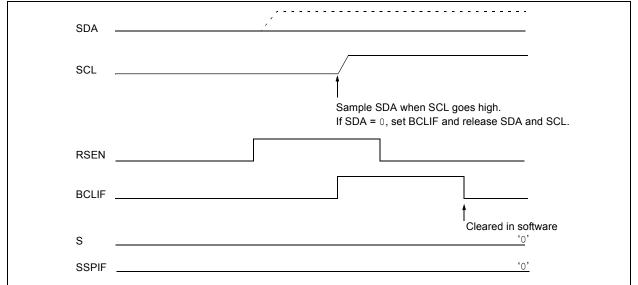

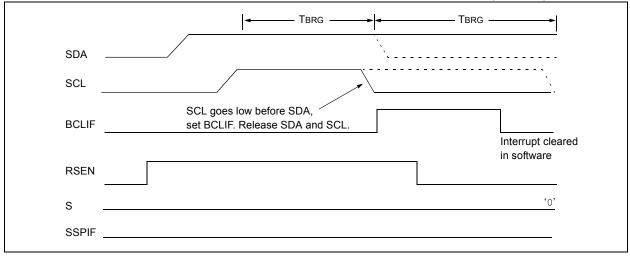

### 18.4.17.2 Bus Collision During a Repeated Start Condition

During a Repeated Start condition, a bus collision occurs if:

- a) A low level is sampled on SDA when SCL goes from low level to high level.

- b) SCL goes low before SDA is asserted low, indicating that another master is attempting to transmit a data '1'.

When the user deasserts SDA and the pin is allowed to float high, the BRG is loaded with SSPADD<6:0> and counts down to 0. The SCL pin is then deasserted and when sampled high, the SDA pin is sampled.

If SDA is low, a bus collision has occurred (i.e., another master is attempting to transmit a data '0', Figure 18-31). If SDA is sampled high, the BRG is reloaded and begins counting. If SDA goes from high-to-low before the BRG times out, no bus collision occurs because no two masters can assert SDA at exactly the same time.

If SCL goes from high-to-low before the BRG times out and SDA has not already been asserted, a bus collision occurs. In this case, another master is attempting to transmit a data '1' during the Repeated Start condition, see Figure 18-32.

If, at the end of the BRG time-out, both SCL and SDA are still high, the SDA pin is driven low and the BRG is reloaded and begins counting. At the end of the count, regardless of the status of the SCL pin, the SCL pin is driven low and the Repeated Start condition is complete.

### FIGURE 18-31: BUS COLLISION DURING A REPEATED START CONDITION (CASE 1)

### FIGURE 18-32: BUS COLLISION DURING REPEATED START CONDITION (CASE 2)

# PIC18F2221/2321/4221/4321 FAMILY

|                         |             | ·                     |                                                                                       |                       |

|-------------------------|-------------|-----------------------|---------------------------------------------------------------------------------------|-----------------------|

| BRG Value               | XXXXh       | 0000h                 | <u> </u>                                                                              | 001Ch                 |

| RX pin                  |             | Start                 | -Edge #1 -Edge #2 -Edge #3 Edge #4<br>Bit 0 Bit 1 Bit 2 Bit 3 Bit 4 Bit 5 Bit 6 Bit 7 | – Edge #5<br>Stop Bit |

| BRG Clock               |             |                       |                                                                                       |                       |

| ABDEN bit               | Set by User |                       |                                                                                       | Auto-Cleared          |

| RCIF bit<br>(Interrupt) |             | 1<br>1<br>1<br>1      |                                                                                       |                       |

| Read<br>RCREG           |             | ,<br>,<br>,<br>,<br>, |                                                                                       |                       |

| SPBRG                   |             | ı                     | XXXXh                                                                                 | 1Ch                   |

| SPBRGH                  |             |                       | XXXXh                                                                                 | 00h                   |

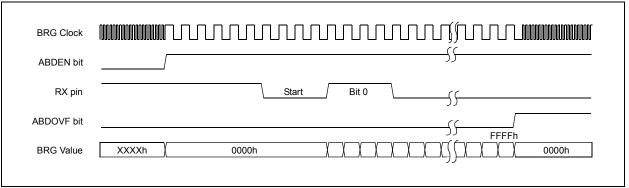

### FIGURE 19-2: BRG OVERFLOW SEQUENCE

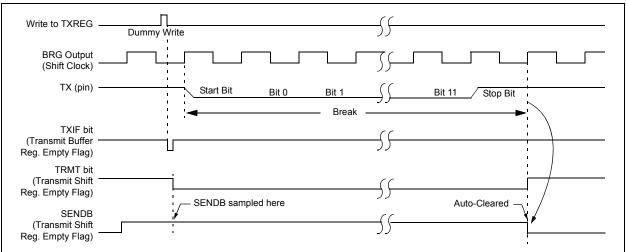

### 19.2.5 BREAK CHARACTER SEQUENCE

The EUSART module has the capability of sending the special Break character sequences that are required by the LIN/J2602 bus standard. The Break character transmit consists of a Start bit, followed by twelve '0' bits and a Stop bit. The Frame Break character is sent whenever the SENDB and TXEN bits (TXSTA<3> and TXSTA<5>) are set while the Transmit Shift register is loaded with data. Note that the value of data written to TXREG will be ignored and all '0's will be transmitted.

The SENDB bit is automatically reset by hardware after the corresponding Stop bit is sent. This allows the user to preload the transmit FIFO with the next transmit byte following the Break character (typically, the Sync character in the LIN/J2602 specification).

Note that the data value written to the TXREG for the Break character is ignored. The write simply serves the purpose of initiating the proper sequence.

The TRMT bit indicates when the transmit operation is active or Idle, just as it does during normal transmission. See Figure 19-10 for the timing of the Break character sequence.

### 19.2.5.1 Break and Sync Transmit Sequence

The following sequence will send a message frame header made up of a Break, followed by an Auto-Baud Sync byte. This sequence is typical of a LIN/J2602 bus master.

- 1. Configure the EUSART for the desired mode.

- 2. Set the TXEN and SENDB bits to set up the Break character.

- 3. Load the TXREG with a dummy character to initiate transmission (the value is ignored).

- 4. Write '55h' to TXREG to load the Sync character into the transmit FIFO buffer.

- 5. After the Break has been sent, the SENDB bit is reset by hardware. The Sync character now transmits in the preconfigured mode.

When the TXREG becomes empty, as indicated by the TXIF, the next data byte can be written to TXREG.

### 19.2.6 RECEIVING A BREAK CHARACTER

The Enhanced USART module can receive a Break character in two ways.

The first method forces configuration of the baud rate at a frequency of 9/13 the typical speed. This allows for the Stop bit transition to be at the correct sampling location (13 bits for Break versus Start bit and 8 data bits for typical data).

The second method uses the auto-wake-up feature described in **Section 19.2.4 "Auto-Wake-up on Sync Break Character"**. By enabling this feature, the EUSART will sample the next two transitions on RX/DT, cause an RCIF interrupt and receive the next data byte followed by another interrupt.

Note that following a Break character, the user will typically want to enable the Auto-Baud Rate Detect feature. For both methods, the user can set the ABD bit once the TXIF interrupt is observed.

### FIGURE 19-10: SEND BREAK CHARACTER SEQUENCE

### 21.0 COMPARATOR MODULE

The analog comparator module contains two comparators that can be configured in a variety of ways. The inputs can be selected from the analog inputs multiplexed with pins RA0 through RA5, as well as the on-chip voltage reference (see Section 22.0 "Comparator Voltage Reference Module"). The digital outputs (normal or inverted) are available at the pin level and can also be read through the control register.

The CMCON register (Register 21-1) selects the comparator input and output configuration. Block diagrams of the various comparator configurations are shown in Figure 21-1.

### REGISTER 21-1: CMCON: COMPARATOR CONTROL REGISTER

| R-0   | R-0   | R/W-0 | R/W-0 | R/W-0 | R/W-1 | R/W-1 | R/W-1 |

|-------|-------|-------|-------|-------|-------|-------|-------|

| C2OUT | C10UT | C2INV | C1INV | CIS   | CM2   | CM1   | CM0   |

| bit 7 |       |       |       |       |       |       | bit 0 |

bit 7 C2OUT: Comparator 2 Output bit When C2INV = 0: 1 = C2 VIN+ > C2 VIN-0 = C2 VIN + < C2 VIN -When C2INV = 1: 1 = C2 VIN + < C2 VIN -0 = C2 VIN+ > C2 VINbit 6 C1OUT: Comparator 1 Output bit When C1INV = 0: 1 = C1 VIN+ > C1 VIN-0 = C1 VIN + < C1 VIN -When C1INV = 1: 1 = C1 VIN + < C1 VIN -0 = C1 VIN + > C1 VIN bit 5 C2INV: Comparator 2 Output Inversion bit 1 = C2 output inverted 0 = C2 output not inverted bit 4 C1INV: Comparator 1 Output Inversion bit 1 = C1 output inverted 0 = C1 output not inverted bit 3 CIS: Comparator Input Switch bit When CM<2:0> = 110: 1 = C1 VIN- connects to RA3/AN3/VREF+ C2 VIN- connects to RA2/AN2/VREF-/CVREF 0 = C1 VIN- connects to RA0/AN0 C2 VIN- connects to RA1/AN1 bit 2-0 CM<2:0>: Comparator Mode bits Figure 21-1 shows the Comparator modes and the CM<2:0> bit settings. I agand

| Legenu.           |                  |                      |                    |

|-------------------|------------------|----------------------|--------------------|

| R = Readable bit  | W = Writable bit | U = Unimplemented    | bit, read as '0'   |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared | x = Bit is unknown |

## PIC18F2221/2321/4221/4321 FAMILY

NOTES:

### 27.2 DC Characteristics: Power-Down and Supply Current PIC18F2221/2321/4221/4321 (Industrial) PIC18LF2221/2321/4221/4321 (Industrial) (Continued)

| PIC18LF2<br>(Indus | 221/2321/4221/4321<br>trial)          |      |     | rating C<br>perature |           | ess otherwise state $A \le +85^{\circ}C$ for indust                                         |                                           |

|--------------------|---------------------------------------|------|-----|----------------------|-----------|---------------------------------------------------------------------------------------------|-------------------------------------------|

|                    | 21/2321/4221/4321<br>trial, Extended) |      |     | rating C<br>perature | -40°C ≤ T | ess otherwise state<br>$A \le +85^{\circ}C$ for indus<br>$A \le +125^{\circ}C$ for extended | strial                                    |

| Param<br>No.       | Device                                | Тур  | Max | Units                |           | Conditio                                                                                    | ns                                        |

|                    | Supply Current (IDD) <sup>(2)</sup>   |      |     |                      |           |                                                                                             |                                           |

|                    | PIC18LF2X21/4X21                      | 51   | 75  | μA                   | -40°C     |                                                                                             |                                           |

|                    |                                       | 54   | 75  | μA                   | +25°C     | VDD = 2.0V                                                                                  |                                           |

|                    |                                       | 60   | 75  | μA                   | +85°C     |                                                                                             |                                           |

|                    | PIC18LF2X21/4X21                      | 83   | 123 | μA                   | -40°C     |                                                                                             |                                           |

|                    |                                       | 88   | 123 | μΑ                   | +25°C     | VDD = 3.0V                                                                                  | Fosc = 1 MHz                              |

|                    |                                       | 93   | 123 | μΑ                   | +85°C     |                                                                                             | ( <b>PRI_IDLE</b> mode,<br>EC oscillator) |

|                    | All Devices                           | 180  | 260 | μA                   | -40°C     |                                                                                             |                                           |

|                    |                                       | 180  | 260 | μA                   | +25°C     | VDD = 5.0V                                                                                  |                                           |

|                    |                                       | 180  | 260 | μA                   | +85°C     | VDD - 5.0V                                                                                  |                                           |

|                    | Extended Devices Only                 | 190  | 260 | μA                   | +125°C    |                                                                                             |                                           |

|                    | PIC18LF2X21/4X21                      | 210  | 290 | μA                   | -40°C     |                                                                                             |                                           |

|                    |                                       | 220  | 290 | μA                   | +25°C     | VDD = 2.0V                                                                                  |                                           |

|                    |                                       | 230  | 290 | μA                   | +85°C     |                                                                                             |                                           |

|                    | PIC18LF2X21/4X21                      | 350  | 480 | μA                   | -40°C     |                                                                                             |                                           |

|                    |                                       | 360  | 480 | μA                   | +25°C     | VDD = 3.0V                                                                                  | Fosc = 4 MHz<br>( <b>PRI IDLE</b> mode,   |

|                    |                                       | 370  | 480 | μA                   | +85°C     |                                                                                             | EC oscillator)                            |

|                    | All Devices                           | 0.69 | 1   | mA                   | -40°C     |                                                                                             | ,                                         |

|                    |                                       | 0.70 | 1   | mA                   | +25°C     | VDD = 5.0V                                                                                  |                                           |

|                    |                                       | 0.72 | 1   | mA                   | +85°C     | VDD - 5.0V                                                                                  |                                           |

|                    | Extended Devices Only                 | 0.74 | 1   | mA                   | +125°C    |                                                                                             |                                           |

|                    | Extended Devices Only                 | 3.7  | 4.0 | mA                   | +125°C    | VDD = 4.2V                                                                                  | Fosc = 25 MHz                             |

|                    |                                       | 4.6  | 5.0 | mA                   | +125°C    | VDD = 5.0V                                                                                  | ( <b>PRI_IDLE</b> mode,<br>EC oscillator) |

|                    | All Devices                           | 6.0  | 7.3 | mA                   | -40°C     |                                                                                             |                                           |

|                    |                                       | 6.2  | 7.3 | mA                   | +25°C     | VDD = 4.2V                                                                                  |                                           |

|                    |                                       | 6.6  | 7.3 | mA                   | +85°C     |                                                                                             | Fosc = 40 MHz<br>( <b>PRI_IDLE</b> mode,  |

|                    | All Devices                           | 6.8  | 9.2 | mA                   | -40°C     |                                                                                             | EC oscillator)                            |

|                    |                                       | 7.0  | 9.2 | mA                   | +25°C     | VDD = 5.0V                                                                                  |                                           |

|                    |                                       | 7.1  | 9.2 | mA                   | +85°C     |                                                                                             |                                           |

Legend: Shading of rows is to assist in readability of the table.

**Note 1:** The power-down current in Sleep mode does not depend on the oscillator type. Power-down current is measured with the part in Sleep mode, with all I/O pins in high-impedance state and tied to VDD or Vss, and all features that add delta current disabled (such as WDT, Timer1 Oscillator, BOR, etc.).

- 2: The supply current is mainly a function of operating voltage, frequency and mode. Other factors, such as I/O pin loading and switching rate, oscillator type and circuit, internal code execution pattern and temperature, also have an impact on the current consumption.

- The test conditions for all IDD measurements in active operation mode are:

- OSC1 = external square wave, from rail-to-rail; all I/O pins tri-stated, pulled to VDD or VSS;

- MCLR = VDD; WDT enabled/disabled as specified.

- **3:** Low-power, Timer1 oscillator is selected unless otherwise indicated, where LPT1OSC (CONFIG3H<2>) = 1.

- **4:** BOR and HLVD enable internal band gap reference. With both modules enabled, current consumption will be less than the sum of both specifications.

- 5: When operation below -10°C is expected, use T1OSC High-Power mode, where LPT1OSC (CONFIG3H<2>) = 0.

### 27.3 DC Characteristics: PIC18F2221/2321/4221/4321 (Industrial) PIC18LF2221/2321/4221/4321 (Industrial) (Continued)

| DC CH4       | ARACTEI | RISTICS                                    |           | perature -4 | $0^{\circ}C \le T$ | (unless otherwise stated)<br>$A \le +85^{\circ}C$ for industrial<br>$A \le +125^{\circ}C$ for extended |

|--------------|---------|--------------------------------------------|-----------|-------------|--------------------|--------------------------------------------------------------------------------------------------------|

| Param<br>No. | Symbol  | Characteristic                             | Min       | Max         | Units              | Conditions                                                                                             |

|              | IPU     | Weak Pull-up Current                       |           |             |                    |                                                                                                        |

| D070         | IPURB   | PORTB Weak Pull-up Current                 | 50        | 400         | μA                 | VDD = 5V, VPIN = VSS                                                                                   |

|              | Vol     | Output Low Voltage                         |           |             |                    |                                                                                                        |

| D080         |         | I/O Ports                                  | _         | 0.6         | V                  | IOL = 8.5 mA, VDD = 4.5V,<br>-40°C to +85°C                                                            |

| D083         |         | OSC2/CLKO<br>(RC, RCIO, EC, ECIO modes)    | _         | 0.6         | V                  | Io∟ = 1.6 mA, VDD = 4.5V,<br>-40°C to +85°C                                                            |

|              | Vон     | Output High Voltage <sup>(3)</sup>         |           |             |                    |                                                                                                        |

| D090         |         | I/O Ports                                  | Vdd - 0.7 | —           | V                  | IOH = -3.0 mA, VDD = 4.5V,<br>-40°C to +85°C                                                           |

| D092         |         | OSC2/CLKO<br>(RC, RCIO, EC, ECIO modes)    | Vdd - 0.7 | —           | V                  | IOH = -1.3 mA, VDD = 4.5V,<br>-40°С to +85°С                                                           |

|              |         | Capacitive Loading Specs<br>on Output Pins |           |             |                    |                                                                                                        |

| D100         | COSC2   | OSC2 Pin                                   | —         | 15          | pF                 | In XT, HS and LP modes<br>when external clock is used<br>to drive OSC1                                 |

| D101         | Сю      | All I/O Pins and OSC2<br>(in RC mode)      | _         | 50          | pF                 | Maximum that allows the<br>AC Timing Specifications to<br>be met                                       |

| D102         | Св      | SCL, SDA                                   | —         | 400         | pF                 | Maximum bus capacitance<br>permitted by I <sup>2</sup> C™<br>Specification                             |

**Note 1:** In RC oscillator configuration, the OSC1/CLKI pin is a Schmitt Trigger input. It is not recommended that the  $PIC^{\mathbb{R}}$  device be driven with an external clock while in RC mode.

2: The leakage current on the MCLR pin is strongly dependent on the applied voltage level. The specified levels represent normal operating conditions. Higher leakage current may be measured at different input voltages.

**3:** Negative current is defined as current sourced by the pin.

### 27.4.2 TIMING CONDITIONS

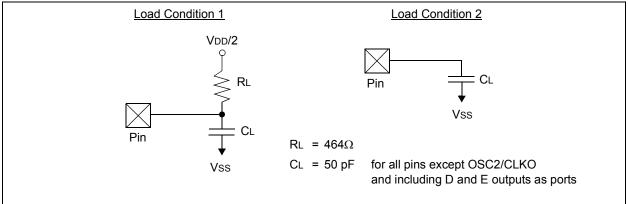

The temperature and voltages specified in Table 27-5 apply to all timing specifications unless otherwise noted. Figure 27-5 specifies the load conditions for the timing specifications.

Note: Because of space limitations, the generic terms "PIC18FXXXX" and "PIC18LFXXXX" are used throughout this section to refer to the PIC18F2221/2321/4221/4321 and PIC18LF2221/2321/4221/4321 families of devices specifically and only those devices.

### TABLE 27-5: TEMPERATURE AND VOLTAGE SPECIFICATIONS – AC

|                    | Standard Operating Conditions (unless otherwise stated)                     |  |

|--------------------|-----------------------------------------------------------------------------|--|

|                    | Operating temperature $-40^{\circ}C \le TA \le +85^{\circ}C$ for industrial |  |

| AC CHARACTERISTICS | $-40^{\circ}C \le TA \le +125^{\circ}C$ for extended                        |  |

| AC CHARACTERISTICS | Operating voltage VDD range as described in DC spec Section 27.1 and        |  |

|                    | Section 27.3.                                                               |  |

|                    | LF parts operate for industrial temperatures only.                          |  |

### FIGURE 27-5: LOAD CONDITIONS FOR DEVICE TIMING SPECIFICATIONS

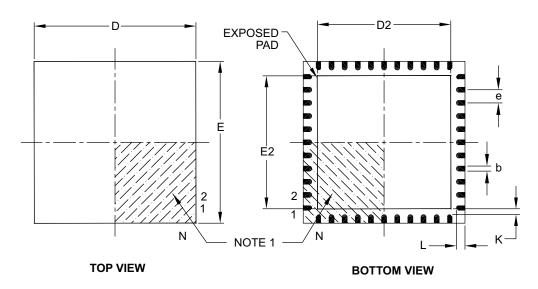

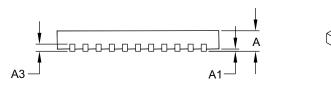

### 44-Lead Plastic Quad Flat, No Lead Package (ML) – 8x8 mm Body [QFN]

**Note:** For the most current package drawings, please see the Microchip Packaging Specification located at http://www.microchip.com/packaging

|                        | Units            |      | MILLIMETERS | 3    |

|------------------------|------------------|------|-------------|------|

|                        | Dimension Limits | MIN  | NOM         | MAX  |

| Number of Pins         | N                |      | 44          |      |

| Pitch                  | e                |      | 0.65 BSC    |      |

| Overall Height         | A                | 0.80 | 0.90        | 1.00 |

| Standoff               | A1               | 0.00 | 0.02        | 0.05 |

| Contact Thickness      | A3               |      | 0.20 REF    |      |

| Overall Width          | E                |      | 8.00 BSC    |      |

| Exposed Pad Width      | E2               | 6.30 | 6.45        | 6.80 |

| Overall Length         | D                |      | 8.00 BSC    |      |

| Exposed Pad Length     | D2               | 6.30 | 6.45        | 6.80 |

| Contact Width          | b                | 0.25 | 0.30        | 0.38 |

| Contact Length         | L                | 0.30 | 0.40        | 0.50 |

| Contact-to-Exposed Pad | К                | 0.20 | -           | -    |

Notes:

1. Pin 1 visual index feature may vary, but must be located within the hatched area.

2. Package is saw singulated.

3. Dimensioning and tolerancing per ASME Y14.5M.

BSC: Basic Dimension. Theoretically exact value shown without tolerances.

REF: Reference Dimension, usually without tolerance, for information purposes only.

Microchip Technology Drawing C04-103B

| RA2/AN2/VREF-/CVREF                                                                                    |                                        |

|--------------------------------------------------------------------------------------------------------|----------------------------------------|

| RA3/AN3/VREF+                                                                                          |                                        |

| RA4/T0CKI/C1OUT                                                                                        | 15, 19                                 |

| RA5/AN4/SS/HLVDIN/C2OUT                                                                                | 15, 19                                 |

| RB0/INT0/FLT0/AN12                                                                                     | 16, 20                                 |

| RB1/INT1/AN10                                                                                          | 16, 20                                 |

| RB2/INT2/AN8                                                                                           | 16, 20                                 |

| RB3/AN9/CCP2                                                                                           | 16, 20                                 |

| RB4/KBI0/AN11                                                                                          | 16, 20                                 |

| RB5/KBI1/PGM                                                                                           | 16, 20                                 |

| RB6/KBI2/PGC                                                                                           | 16, 20                                 |

| RB7/KBI3/PGD                                                                                           |                                        |

| RC0/T10S0/T13CKI                                                                                       | 17, 21                                 |

| RC1/T1OSI/CCP2                                                                                         | 17. 21                                 |

| RC2/CCP1                                                                                               |                                        |

| RC2/CCP1/P1A                                                                                           |                                        |

| RC3/SCK/SCL                                                                                            |                                        |

| RC4/SDI/SDA                                                                                            | ,                                      |

| RC5/SDO                                                                                                | -                                      |

| RC6/TX/CK                                                                                              | ,                                      |

| RC7/RX/DT                                                                                              | ,                                      |

| RD0/PSP0                                                                                               | ,                                      |

| RD1/PSP1                                                                                               |                                        |

|                                                                                                        |                                        |

| RD2/PSP2                                                                                               |                                        |

| RD3/PSP3                                                                                               |                                        |