Welcome to **E-XFL.COM**

What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded - Microcontrollers</u>"

| Details                    |                                                                                     |

|----------------------------|-------------------------------------------------------------------------------------|

| Product Status             | Obsolete                                                                            |

| Core Processor             | F <sup>2</sup> MC-16LX                                                              |

| Core Size                  | 16-Bit                                                                              |

| Speed                      | 16MHz                                                                               |

| Connectivity               | UART/USART                                                                          |

| Peripherals                | POR, WDT                                                                            |

| Number of I/O              | 51                                                                                  |

| Program Memory Size        | 32KB (32K x 8)                                                                      |

| Program Memory Type        | Mask ROM                                                                            |

| EEPROM Size                | -                                                                                   |

| RAM Size                   | 1K x 8                                                                              |

| Voltage - Supply (Vcc/Vdd) | 4.5V ~ 5.5V                                                                         |

| Data Converters            | A/D 8x8/10b                                                                         |

| Oscillator Type            | External                                                                            |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                                   |

| Mounting Type              | Surface Mount                                                                       |

| Package / Case             | 64-LQFP                                                                             |

| Supplier Device Package    | 64-LQFP (12x12)                                                                     |

| Purchase URL               | https://www.e-xfl.com/product-detail/infineon-technologies/mb90561apfm-gs-313-bnde1 |

#### (Continued)

- Instruction set

- Bit, byte, word, and long word data types

- 23 different addressing modes

- Enhanced calculation precision using a 32-bit accumulator

- Enhanced signed multiplication and division instructions and RETI instruction

- Instruction set designed for high level language (C) and multi-tasking

- · Uses a system stack pointer

- Symmetric instruction set and barrel shift instructions

- Program patch function (2 address pointers) .

- 4-byte instruction queue

- Interrupt function

- · Priority levels are programmable

- · 32 interrupts

- Data transfer function

- Extended intelligent I/O service function : Up to 16 channels

- Low-power consumption modes

- Sleep mode (CPU operating clock stops.)

- Timebase timer mode (Only oscillation clock and timebase timer continue to operate.)

- Stop mode (Oscillation clock stops.)

- CPU intermittent operation mode (The CPU operates intermittently at the specified interval.)

- Package

- LQFP-64P (FTP-64P-M23: 0.65 mm pin pitch)

- QFP-64P (FTP-64P-M06: 1.00 mm pin pitch)

- SH-DIP (DIP-64P-M01 : 1.778 mm pin pitch)

- Process : CMOS technology

### **■ PERIPHERAL FUNCTIONS (RESOURCES)**

I/O ports: 51 ports (max.)

Timebase timer: 1 channel

Watchdog timer: 1 channel

16-bit reload timer: 2 channels

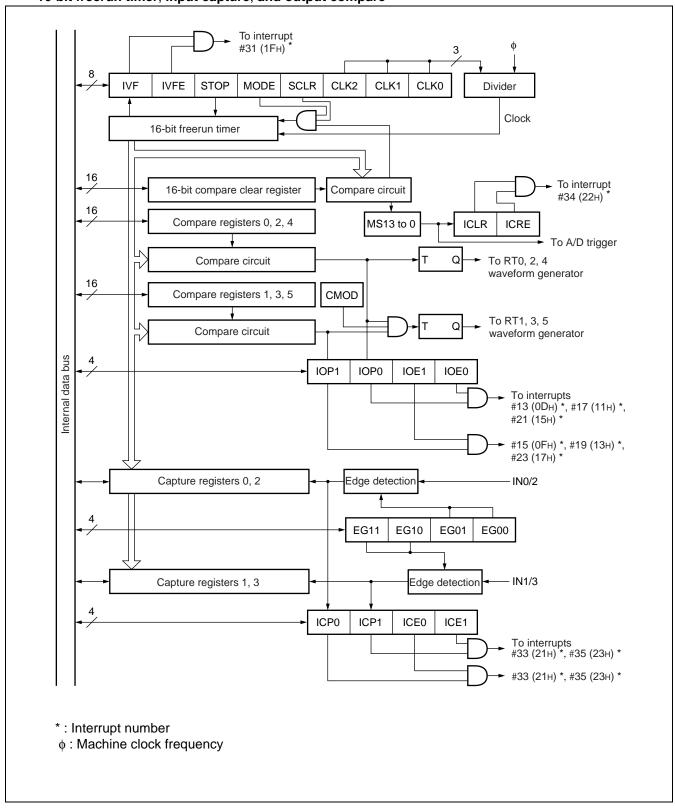

• Multi-function timer

• 16-bit free-run timer: 1 channel

• Output compare : 6 channels

Can output an interrupt request when a match occurs between the count in the 16-bit freerun timer and the value set in the compare register.

• Input capture: 4 channels

On detecting an active edge on the input signal from an external input pin, copies the count value of the 16bit freerun timer to the input capture data register and generates an interrupt request.

- 8/16-bit PPG timer (8-bit × 6 channels or 16-bit × 3 channels) The period and duty of the output pulse can be set by the program.

- Waveform generator (8-bit timer: 3 channels)

- UART : 2 channels

- Full-duplex, double-buffered (8-bit)

- Can be set to asynchronous or clock synchronous serial transfer (I/O expansion serial) operation

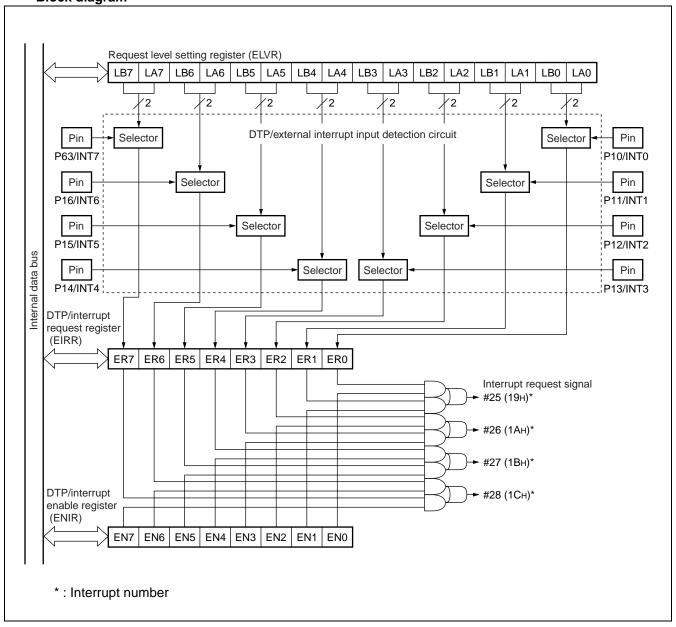

- DTP/external interrupt circuit (8 channels)

- External interrupts can activate the extended intelligent I/O service.

- Generates interrupts in response to external interrupt inputs.

## ■ I/O CIRCUITS

| Туре | Circuit                                        | Remarks                                                                                                                                                                                                                                                                     |

|------|------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| А    | X1  Nch Pch Pch Nch Nch Standby control signal | Oscillation circuit     Internal oscillation feedback     resistor (R <sub>f</sub> )                                                                                                                                                                                        |

| В    | CMOS hysteresis input                          | CMOS hysteresis input                                                                                                                                                                                                                                                       |

| С    |                                                | CMOS hysteresis I/O pin with pull-up control CMOS output CMOS hysteresis input (with input cutoff function in standby mode) Internal pull-up resistor (Rp)  Note > The pull-up resistor is active when the port is set as an input.                                         |

| D    |                                                | CMOS hysteresis I/O pin CMOS output CMOS hysteresis input (with input cutoff function in standby mode)  Notes > The I/O port output and internal resource output share the same output buffer.  The I/O port input and internal resource input share the same input buffer. |

## ■ I/O MAP

| Address                  | Abbreviat-<br>ed Register<br>Name | Register name                                | Read/<br>Write | Resource Name            | Initial Value                |

|--------------------------|-----------------------------------|----------------------------------------------|----------------|--------------------------|------------------------------|

| 000000н                  | PDR0                              | Port 0 data register                         | R/W            | Port 0                   | XXXXXXXXB                    |

| 000001н                  | PDR1                              | Port 1 data register                         | R/W            | Port 1                   | XXXXXXXX                     |

| 000002н                  | PDR2                              | Port 2 data register                         | R/W            | Port 2                   | XXXXXXXX                     |

| 000003н                  | PDR3                              | Port 3 data register                         | R/W            | Port 3                   | XXXXXXXXB                    |

| 000004н                  | PDR4                              | Port 4 data register                         | R/W            | Port 4                   | XXXXXXXXB                    |

| 000005н                  | PDR5                              | Port 5 data register                         | R/W            | Port 5                   | XXXXXXXXB                    |

| 000006н                  | PDR6                              | Port 6 data register                         | R/W            | Port 6                   | XXXXXXXXB                    |

| 000007н<br>to<br>00000Fн |                                   | Access prol                                  | nibited        |                          |                              |

| 000010н                  | DDR0                              | Port 0 direction register                    | R/W            | Port 0                   | 0 0 0 0 0 0 0 0 В            |

| 000011н                  | DDR1                              | Port 1 direction register                    | R/W            | Port 1                   | 0 0 0 0 0 0 0 0 В            |

| 000012н                  | DDR2                              | Port 2 direction register                    | R/W            | Port 2                   | 0 0 0 0 0 0 0 0 В            |

| 000013н                  | DDR3                              | Port 3 direction register                    | R/W            | Port 3                   | 0 0 0 0 0 0 0 0 В            |

| 000014н                  | DDR4                              | Port 4 direction register                    | R/W            | Port 4                   | X 0 0 0 0 0 0 0 <sub>B</sub> |

| 000015н                  | DDR5                              | Port 5 direction register                    | R/W            | Port 5                   | 0 0 0 0 0 0 0 0 В            |

| 000016н                  | DDR6                              | Port 6 direction register                    | R/W            | Port 6                   | XXXX 0 0 0 0 <sub>B</sub>    |

| 000017н                  | ADER                              | Analog input enable register                 | R/W            | Port 5,<br>A/D converter | 11111111                     |

| 000018н<br>to<br>00001Fн |                                   | Access prol                                  | nibited        |                          |                              |

| 000020н                  | SMR0                              | Mode register ch0                            | R/W            |                          | 0 0 0 0 0 X 0 0 <sub>B</sub> |

| 000021н                  | SCR0                              | Control register ch0                         | W, R/W         |                          | 0 0 0 0 0 1 0 0в             |

| 000022н                  | SIDR0                             | Input data register ch0                      | R              | UART0                    | XXXXXXXX                     |

| 000022H                  | SODR0                             | Output data register ch0                     | W              |                          |                              |

| 000023н                  | SSR0                              | Status register ch0                          | R, R/W         |                          | 0 0 0 0 1 0 0 0в             |

| 000024н                  | SMR1                              | Mode register ch1                            | R/W            |                          | 0 0 0 0 0 X 0 0 <sub>B</sub> |

| 000025н                  | SCR1                              | Control register ch1                         | W, R/W         |                          | 0 0 0 0 0 1 0 0в             |

| 000026                   | SIDR1                             | Input data register ch1                      | R              | UART1                    | VVVVVV-                      |

| 000026н                  | SODR1                             | Output data register ch1                     | W              |                          | XXXXXXXXB                    |

| 000027н                  | SSR1                              | Status register ch1                          | R, R/W         |                          | 00001000в                    |

| 000028н                  |                                   | Access prol                                  | nibited        |                          | •                            |

| 000029н                  | CDCR0                             | Communication prescaler control register ch0 | R/W            | Communication prescaler  | 0 XXX 0 0 0 0 <sub>B</sub>   |

| Address                  | Abbreviat-<br>ed Register<br>Name | Register name                           | Read/<br>Write | Resource Name        | Initial Value               |

|--------------------------|-----------------------------------|-----------------------------------------|----------------|----------------------|-----------------------------|

| 00004Дн                  | PPGC5                             | PPG control register ch5 (upper)        | R/W            | 0/40 hit DDO time an | 0000001в                    |

| 00004Ен                  | PCS45                             | PPG clock control register ch4, ch5     | R/W            | 8/16-bit PPG timer   | 0 0 0 0 0 0 XXB             |

| 00004Fн                  |                                   | Access prohi                            | bited          | 1                    | I.                          |

| 000050н                  | TMRR0                             | 8-bit reload register ch0               | R/W            |                      | XXXXXXXX                    |

| 000051н                  | DTCR0                             | 8-bit timer control register ch0        | R/W            |                      | 00000000                    |

| 000052н                  | TMRR1                             | 8-bit reload register ch1               | R/W            |                      | XXXXXXXX                    |

| 000053н                  | DTCR1                             | 8-bit timer control register ch1        | R/W            | Waveform generator   | 0 0 0 0 0 0 0 0в            |

| 000054н                  | TMRR2                             | 8-bit reload register ch2               | R/W            | generator            | XXXXXXXX                    |

| 000055н                  | DTCR2                             | 8-bit timer control register ch2        | R/W            |                      | 00000000                    |

| 000056н                  | SIGCR                             | Waveform control register               | R/W            |                      | 0 0 0 0 0 0 0 0в            |

| 000057н                  |                                   | Access prohi                            | bited          |                      |                             |

| 000058н                  | CPCLR                             | Compare clear register (lower)          | R/W            |                      | XXXXXXXXB                   |

| 000059н                  | CPCLR                             | Compare clear register (upper)          | R/W            | †                    | XXXXXXXXB                   |

| 00005Ан                  | TCDT                              | Timer data register (lower)             | R/W            | 16-bit freerun       | 0 0 0 0 0 0 0 0в            |

| 00005Вн                  | TODI                              | Timer data register (upper)             | R/W            | timer                | 0 0 0 0 0 0 0 0в            |

| 00005Сн                  | TCCS                              | Timer control/status register (lower)   | R/W            |                      | 0 0 0 0 0 0 0 0 В           |

| 00005Дн                  | 1003                              | Timer control/status register (upper)   | R/W            | ]                    | 0 XX 0 0 0 0 0 <sub>B</sub> |

| 00005Ен                  |                                   | Access probi                            | hitad          |                      |                             |

| 00005Fн                  |                                   | Access prohi                            | biteu          |                      |                             |

| 000060н                  | IPCP0                             | Input capture data register ch0 (lower) | R              |                      | XXXXXXXX                    |

| 000061н                  | IFCFU                             | Input capture data register ch0 (upper) | R              |                      | XXXXXXXXB                   |

| 000062н                  | IPCP1                             | Input capture data register ch1 (lower) | R              |                      | XXXXXXXX                    |

| 000063н                  | IFCFI                             | Input capture data register ch1 (upper) | R              |                      | XXXXXXXXB                   |

| 000064н                  | IPCP2                             | Input capture data register ch2 (lower) | R              | Input capture        | XXXXXXXX                    |

| 000065н                  | IFCF2                             | Input capture data register ch2 (upper) | R              | ]                    | XXXXXXXXB                   |

| 000066н                  | IPCP3                             | Input capture data register ch3 (lower) | R              |                      | XXXXXXXX                    |

| 000067н                  | IFCF3                             | Input capture data register ch3 (upper) | R              |                      | XXXXXXXX                    |

| 000068н                  | ICS01                             | Input capture control register 01       | R/W            | <u> </u>             | 0 0 0 0 0 0 0 0 0в          |

| 000069н                  |                                   | Access prohi                            | bited          |                      |                             |

| 00006Ан                  | ICS23                             | Input capture control register 23       | R/W            | Input capture        | 00000000                    |

| 00006Вн<br>to<br>00006Ен | Access prohibited                 |                                         |                |                      |                             |

| Address | Abbreviat-<br>ed Register<br>Name | Register name                             | Read/<br>Write | Resource Name                        | Initial Value               |

|---------|-----------------------------------|-------------------------------------------|----------------|--------------------------------------|-----------------------------|

| 00006Fн | ROMM                              | ROM mirror function selection register    | W              | ROM mirror function selection module | XXXXXXX 1 <sub>B</sub>      |

| 000070н | OCCP0                             | Compare register ch0 (lower)              | R/W            |                                      | XXXXXXXXB                   |

| 000071н | OCCFU                             | Compare register ch0 (upper)              | R/W            |                                      | XXXXXXXX                    |

| 000072н | OCCP1                             | Compare register ch1 (lower)              | R/W            |                                      | XXXXXXXXB                   |

| 000073н | OCCPT                             | Compare register ch1 (upper)              | R/W            | 1                                    | XXXXXXXXB                   |

| 000074н | 00000                             | Compare register ch2 (lower)              | R/W            |                                      | XXXXXXXXB                   |

| 000075н | OCCP2                             | Compare register ch2 (upper)              | R/W            | †                                    | XXXXXXXXB                   |

| 000076н | 00000                             | Compare register ch3 (lower)              | R/W            |                                      | XXXXXXXX                    |

| 000077н | OCCP3                             | Compare register ch3 (upper)              | R/W            | †                                    | XXXXXXXXB                   |

| 000078н | 00004                             | Compare register ch4 (lower)              | R/W            | 0.4                                  | XXXXXXXX                    |

| 000079н | OCCP4                             | Compare register ch4 (upper)              | R/W            | Output compare                       | XXXXXXXX                    |

| 00007Ан | 00005                             | Compare register ch5 (lower)              | R/W            |                                      | XXXXXXXX                    |

| 00007Вн | OCCP5                             | Compare register ch5 (upper)              | R/W            |                                      | XXXXXXXX                    |

| 00007Сн | OCS0                              | Compare control register ch0 (lower)      | R/W            |                                      | 0 0 0 0 XX 0 Ов             |

| 00007Dн | OCS1                              | Compare control register ch1 (upper)      | R/W            |                                      | XXX 0 0 0 0 0 <sub>B</sub>  |

| 00007Ен | OCS2                              | Compare control register ch2 (lower)      | R/W            |                                      | 0 0 0 0 XX 0 0 <sub>B</sub> |

| 00007Fн | OCS3                              | Compare control register ch3 (upper)      | R/W            |                                      | XXX 0 0 0 0 0 <sub>B</sub>  |

| 000080н | OCS4                              | Compare control register ch4 (lower)      | R/W            |                                      | 0 0 0 0 XX 0 0 <sub>B</sub> |

| 000081н | OCS5                              | Compare control register ch5 (upper)      | R/W            |                                      | XXX 0 0 0 0 0 <sub>B</sub>  |

| 000082н | TMCSR0:L                          | Timer control status register ch0 (lower) | R/W            |                                      | 00000000                    |

| 000083н | TMCSR0:H                          | Timer control status register ch0 (upper) | R/W            |                                      | XXXX 0 0 0 0 <sub>B</sub>   |

| 000004  | TMR0                              | 16-bit timer register ch0 (lower)         | R              |                                      | XXXXXXXX                    |

| 000084н | TMRLR0                            | 16-bit reload register ch0 (lower)        | W              |                                      | XXXXXXXX                    |

| 000005  | TMR0                              | 16-bit timer register ch0 (upper)         | R              |                                      | XXXXXXXX                    |

| 000085н | TMRHR0                            | 16-bit reload register ch0 (upper)        | W              | 40 1.7                               | XXXXXXXX                    |

| 000086н | TMCSR1:L                          | Timer control status register ch1 (lower) | R/W            | 16-bit reload timer                  | 00000000                    |

| 000087н | TMCSR1:H                          | Timer control status register ch1 (upper) | R/W            |                                      | XXXX 0 0 0 0 <sub>B</sub>   |

| 000000  | TMR1                              | 16-bit timer register ch1 (lower)         | R              | 1                                    | XXXXXXXXB                   |

| 000088н | TMRLR1                            | 16-bit reload register ch1 (lower)        | W              | 1                                    | XXXXXXXXB                   |

| 000000  | TMR1                              | 16-bit timer register ch1 (upper)         | R              | 1                                    | XXXXXXXXB                   |

| 000089н | TMRHR1                            | 16-bit reload register ch1 (upper)        | W              | 1                                    | XXXXXXXX                    |

| Address                  | Abbreviat-<br>ed Register<br>Name | Register name                                   | Read/<br>Write | Resource Name           | Initial Value               |  |  |

|--------------------------|-----------------------------------|-------------------------------------------------|----------------|-------------------------|-----------------------------|--|--|

| 0000В6н                  | ICR06                             | Interrupt control register 06 (for writing)     | W, R/W         |                         | ХХХХ 0 1 1 1в               |  |  |

| ООООВОН                  | ICKUU                             | Interrupt control register 06 (for reading)     | R, R/W         |                         | XX 0 0 0 1 1 1 <sub>B</sub> |  |  |

| 0000В7н                  | ICR07                             | Interrupt control register 07 (for writing)     | W, R/W         |                         | XXXX 0 1 1 1 <sub>B</sub>   |  |  |

| 0000Б7н                  | ICKU1                             | Interrupt control register 07 (for reading)     | R, R/W         |                         | XX 0 0 0 1 1 1 <sub>B</sub> |  |  |

| 0000В8н                  | ICR08                             | Interrupt control register 08 (for writing)     | W, R/W         |                         | XXXX 0 1 1 1 <sub>B</sub>   |  |  |

| ООООВОН                  | ICKUO                             | Interrupt control register 08 (for reading)     | R, R/W         |                         | XX 0 0 0 1 1 1 <sub>B</sub> |  |  |

| 0000В9н                  | ICR09                             | Interrupt control register 09 (for writing)     | W, R/W         |                         | XXXX 0 1 1 1 <sub>B</sub>   |  |  |

| ООООБЭН                  | ICKUS                             | Interrupt control register 09 (for reading)     | R, R/W         |                         | XX 0 0 0 1 1 1 <sub>B</sub> |  |  |

| 0000ВАн                  | ICR10                             | Interrupt control register 10 (for writing)     | W, R/W         |                         | XXXX 0 1 1 1 <sub>B</sub>   |  |  |

| ООООБАН                  | ICKIU                             | Interrupt control register 10 (for reading)     | R, R/W         | Interrupte              | ХХ 0 0 0 1 1 1в             |  |  |

| 0000ВВн                  | ICR11                             | Interrupt control register 11 (for writing)     | W, R/W         | Interrupts              | XXXX 0 1 1 1 <sub>B</sub>   |  |  |

| ООООБЬН                  | ICKII                             | Interrupt control register 11 (for reading)     | R, R/W         |                         | XX 0 0 0 1 1 1 <sub>B</sub> |  |  |

| 0000ВСн                  | ICR12                             | Interrupt control register 12 (for writing)     | W, R/W         |                         | XXXX 0 1 1 1 <sub>B</sub>   |  |  |

| ООООВСН                  | ICKIZ                             | Interrupt control register 12 (for reading)     | R, R/W         |                         | ХХ 0 0 0 1 1 1в             |  |  |

| 0000ВДн                  | ICR13                             | Interrupt control register 13 (for writing)     | W, R/W         |                         | XXXX 0 1 1 1 <sub>B</sub>   |  |  |

| ООООБОН                  |                                   | Interrupt control register 13 (for reading)     | R, R/W         |                         | ХХ 0 0 0 1 1 1в             |  |  |

| 0000ВЕн                  | ICR14                             | Interrupt control register 14 (for writing)     | W, R/W         |                         | XXXX 0 1 1 1 <sub>B</sub>   |  |  |

| ООООВЕН                  | 101(14                            | Interrupt control register 14 (for reading)     | R, R/W         |                         | ХХ 0 0 0 1 1 1в             |  |  |

| 0000ВFн                  | ICR15                             | Interrupt control register 15 (for writing)     | W, R/W         |                         | XXXX 0 1 1 1 <sub>B</sub>   |  |  |

| ООООБГН                  | ICKIS                             | Interrupt control register 15 (for reading)     | R, R/W         |                         | ХХ 0 0 0 1 1 1в             |  |  |

| 0000C0н<br>to<br>0000FFн |                                   | Unused ar                                       | ea             |                         |                             |  |  |

| 000100н<br>to<br>#н      |                                   | RAM area                                        |                |                         |                             |  |  |

| #н<br>to<br>001FEFн      |                                   | Reserved area                                   |                |                         |                             |  |  |

| 001FF0н                  |                                   | Program address detection register ch0 (lower)  | R/W            |                         | XXXXXXXX                    |  |  |

| 001FF1н                  | PADR0                             | Program address detection register ch0 (middle) | R/W            | Address match detection | XXXXXXXXB                   |  |  |

| 001FF2н                  |                                   | Program address detection register ch0 (lower)  | R/W            |                         | XXXXXXXX                    |  |  |

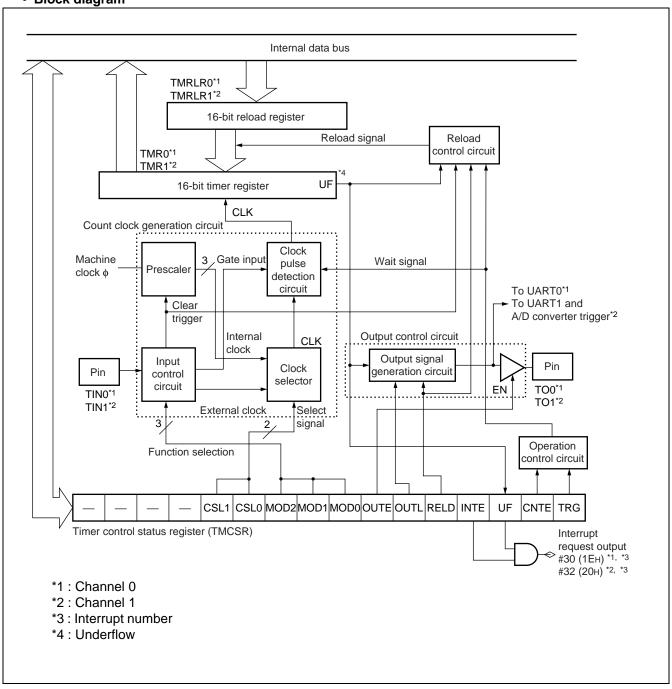

### 4. 16-Bit Reload Timers 0 and 1 (With Event Count Function)

- The 16-bit reload timers have the following functions.

- The count clock can be selected from three internal clocks or the external event clock.

- An interrupt to the CPU can be generated when an underflow occurs on 16-bit reload timer 0 or 1. This interrupt allows the timers to be used as interval timers.

- Two different operation modes can be selected when an underflow occurs on 16-bit reload timer 0 or 1: oneshot mode in which timer operation halts when an underflow occurs or reload mode in which the value in the reload register is loaded into the timer and counting continues.

- Extended intelligent I/O service (EI2OS) is supported.

- The MB90560/565 series contains two 16-bit reload timer channels.

#### • 16-bit reload timer operation modes

| Count Clock           | Start Trigger    | Operation When an<br>Underflow Occurs |

|-----------------------|------------------|---------------------------------------|

|                       | Software trigger | One-shot mode                         |

| Internal clock        | Software trigger | Reload mode                           |

| Internal Clock        | External trigger | One-shot mode                         |

|                       |                  | Reload mode                           |

| Event count mode      | Software trigger | One-shot mode                         |

| (external clock mode) | Software trigger | Reload mode                           |

### • Interval times for the 16-bit reload timers

| Count Clock Count Clock Period Example of Inte |                 | Example of Interval Times |

|------------------------------------------------|-----------------|---------------------------|

|                                                | 2¹/φ (0.125 μs) | 0.125 μs to 8.192 ms      |

| Internal clock                                 | 2³/φ (0.5 μs)   | 0.5 μs to 32.768 ms       |

|                                                | 25/φ (2.0 μs)   | 2.0 μs to 131.1 ms        |

| Event count mode                               | 2³/φ or longer  | 0.5 μs or longer          |

Note: The values enclosed in () and the example of interval times is for a machine clock frequency of 16 MHz. \$\phi\$ is the machine clock frequency value for the calculation.

Remarks: 16-bit reload timer 0 can be used to generate the baud rate for UART0.

16-bit reload timer 1 can be used to generate the baud rate for UART1 and activation trigger for the A/D converter.

### • Block diagram

• An interrupt can be generated when an active edge is detected on the external signal (ICS01, ICS23 : ICE0 = "1", ICE1 = "1", ICE2 = "1", ICE3 = "1") .

#### • 8/16-bit PPG timer (8-bit : 6 channels, 16-bit : 3 channels)

The 8/16-bit PPG timer consists of an 8-bit down counter (PCNT), PPG control registers (PPGC0 to PPGC 5), PPG clock control registers (PCS01, PCS23, PCS45), and PPG reload registers (PRLL0 to PRLL5, PRLH0 to PRLH5).

When used as an 8/16-bit reload timer, the PPG operates as an event timer. The PPG can also be used to output pulses with specified frequency and duty ratio.

- 8-bit PPG mode

- Each channel operates as an independent 8-bit PPG.

- 8-bit prescaler + 8-bit PPG mode ch0 (ch2, ch4) operates as an 8-bit prescaler and ch1 (ch3, ch5) operates as a variable frequency PPG by counting up on the borrow output from ch0 (ch2, ch4) .

- 16-bit PPG mode ch0 (ch2, ch4) and ch1 (ch3, ch5) operate together as a 16-bit PPG.

- PPG operation

Outputs pulses with the specified frequency and duty ratio (ratio of "H" level period and "L" level period), and can also be used as a D/A converter when combined with an external circuit.

#### Waveform generator

The waveform generator consists of an 8-bit timer, 8-bit timer control registers (DTCR0 to DTCR2), 8-bit reload registers (TMRR0 to TMRR2), and waveform control register (SIGCR).

The waveform generator can generate a DC chopper output or non-overlapping three-phase waveform output for inverter control using the realtime outputs (RT0 to RT5) and 8/16-bit PPG timer.

- A non-overlapping waveform can be generated by using the 8-bit timer as a deadtime timer and adding a nonoverlap time delay to the PPG timer pulse output. (Deadtime timer function)

- A non-overlapping waveform can be generated by using the 8-bit timer as a deadtime timer and adding a non-overlap time delay to the realtime outputs (RT1, RT3, RT5). (Deadtime timer function)

- A GATE signal can be generated when a match occurs between the count from the 16-bit freerun timer and compare register in the output compare (OCCP0 to OCCP5) (rising edge on realtime output (RT)) to control the PPG timer operation. (GATE function)

- Can control the RTO0 to RTO5 pin outputs using the DTTI pin input.

By making the DTTI pin input clockless, the pins can be controlled externally even when the oscillation clock is halted. (The level for each pin can be set by the program.) However, the I/O ports (P30 to P35) must have been set beforehand as outputs and the output values set in the port 3 data register (PDR3).

- Block diagram

- 16-bit freerun timer, input capture, and output compare

#### (2) Structure of the DTP/external interrupt circuit

The DTP/external interrupt circuit consists of the following four blocks:

- DTP/interrupt detection circuit

- DTP/interrupt request register (EIRR)

- DTP/interrupt enable register (ENIR)

- Request level setting register (ELVR)

· Block diagram

#### 9. 8/10-Bit A/D Converter

- Overview of the 8/10-bit A/D converter

- The 8/10-bit A/D converter uses RC successive approximation to convert analog input voltages to an 8-bit or 10-bit digital value.

- The input signals can be selected from the eight analog input pin channels.

### • 8/10-bit A/D converter functions

|                                                                                                                                                              | o, io all / ve delitration initiation                                                                                                                                                                             |  |  |  |  |  |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|--|

| A/D conversion time is 6.13 $\mu$ s (for a 16 MHz machine clock, including san time) . The minimum sampling time is 2.0 $\mu$ s (for a 16 MHz machine clock) |                                                                                                                                                                                                                   |  |  |  |  |  |

| Conversion method                                                                                                                                            | RC successive approximation with sample & hold circuit                                                                                                                                                            |  |  |  |  |  |

| Resolution                                                                                                                                                   | 8-bit or 10-bit, selectable                                                                                                                                                                                       |  |  |  |  |  |

| Analog input pins                                                                                                                                            | Eight analog input pin channels are available. The input pin can be selected by the program.                                                                                                                      |  |  |  |  |  |

| Interrupts                                                                                                                                                   | An interrupt request can be generated and EI <sup>2</sup> OS invoked when A/D conversion completes. The conversion data protection function operates when A/D conversion is performed with the interrupt enabled. |  |  |  |  |  |

| A/D conversion start trigger                                                                                                                                 | The conversion start trigger can be set from the following options: software, output of 16-bit reload timer 1 (rising edge), or zero detection edge from 16-bit freerun timer.                                    |  |  |  |  |  |

| El <sup>2</sup> OS support                                                                                                                                   | Supported by the extended intelligent I/O service (EI <sup>2</sup> OS) .                                                                                                                                          |  |  |  |  |  |

### • 8/10-bit A/D converter conversion modes

| Conversion Mode                                                | Single Conversion Mode Operation                                                                            | Scan Conversion Mode Operation                                                                                                          |

|----------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------|

| Single-shot conversion mode 1<br>Single-shot conversion mode 2 | Performs one conversion for the specified channel (1 channel) then halts.                                   | Sequentially performs one conversion for multiple channels (up to 8 channels can be set), then halts.                                   |

| Continuous conversion mode                                     | Performs repeated conversions for the specified channel (1 channel).                                        | Performs repeated conversions for the specified channels (up to 8 channels can be set) .                                                |

| Incremental conversion mode                                    | Performs one conversion for the specified channel (1 channel) then halts and waits for the next activation. | Sequentially performs one conversion for multiple channels (up to 8 channels can be set), then halts and waits for the next activation. |

### • 8/10-bit A/D converter interrupts and El<sup>2</sup>OS

| Interrupt No. | Interrupt Control Register |         | Vector Table Address |                     | El <sup>2</sup> OS  |       |

|---------------|----------------------------|---------|----------------------|---------------------|---------------------|-------|

| interrupt No. | Register Name              | Address | Lower                | Upper               | Bank                | LI-OS |

| #11 (0Вн)     | ICR00                      | 0000В0н | FFFFD0 <sub>H</sub>  | FFFFD1 <sub>H</sub> | FFFFD2 <sub>H</sub> | 0     |

○ : Available

### 13. 1 Mbit Flash Memory

- This section describes the flash memory on the MB90F568 and does not apply to evaluation and mask ROM versions.

- The flash memory is located in banks FE to FF in the CPU memory map.

### • Flash memory functions

|                            | Function                                                                                                                                                                                                                                                                    |  |  |  |

|----------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|

| Memory size                | • 1 Mbit (128 KBytes)                                                                                                                                                                                                                                                       |  |  |  |

| Memory configuration       | • 128 KWords × 8 bits or 64 KWords × 16 bits                                                                                                                                                                                                                                |  |  |  |

| Sector configuration       | 16 KBytes + 8 KBytes + 8 KBytes + 32 KBytes + 64 KBytes                                                                                                                                                                                                                     |  |  |  |

| Sector protect function    | Selectable for each sector                                                                                                                                                                                                                                                  |  |  |  |

| Programming algorithm      | <ul> <li>Automatic programming algorithm (Embedded Algorithm : Equivalent to<br/>MBM29F400TA)</li> </ul>                                                                                                                                                                    |  |  |  |

| Operation commands         | <ul> <li>Compatible with JEDEC standard commands</li> <li>Includes an erase pause and restart function</li> <li>Write/erase completion detection by data polling or toggle bit</li> <li>Erasing by sector available (sectors can be combined in any combination)</li> </ul> |  |  |  |

| No. of write/erase cycles  | Min. 10,000 guaranteed                                                                                                                                                                                                                                                      |  |  |  |

| Memory write/erase method  | <ul> <li>Can be written and erased using a parallel writer</li> <li>Can be written and erased using a dedicated serial writer</li> <li>Can be written and erased by the program</li> </ul>                                                                                  |  |  |  |

| Interrupts                 | Write and erase completion interrupts                                                                                                                                                                                                                                       |  |  |  |

| El <sup>2</sup> OS support | Not supported by the extended intelligent I/O service (EI <sup>2</sup> OS) .                                                                                                                                                                                                |  |  |  |

### • Sector configuration of flash memory

| Flash memory   | CPU address | Writer address* |  |  |

|----------------|-------------|-----------------|--|--|

| 212 (214 )     | FE0000н     | 60000н          |  |  |

| SA0 (64 Kbyte) | FEFFFH      | 6FFFFH          |  |  |

| SA1 (32 Kbyte) | FF0000H     | 70000н          |  |  |

| SAT (32 Rbyte) | FF7FFFH     | 77FFFH          |  |  |

| SA2 (8 Kbyte)  | FF8000H     | 78000н          |  |  |

| SAZ (6 Kbyte)  | FF9FFFH     | 79FFFн          |  |  |

| CA2 (9 Khyto)  | FFA000H     | 7А000н          |  |  |

| SA3 (8 Kbyte)  | FFBFFFH     | 7BFFFH          |  |  |

| SA4 (16 Kbyte) | FFC000H     | 7С000н          |  |  |

|                | FEFFFFH     | 7FFFFH          |  |  |

<sup>\*:</sup> The writer address is the address to be used instead of the CPU address when writing data from a parallel flash memory writer. Use the writer address when programming or erasing with a general-purpose parallel writer.

## 6. Flash Memory Erase and Programming Performance

| Parameter                            | Condition                             | Value   |     |       | Units  | Remarks                                |  |

|--------------------------------------|---------------------------------------|---------|-----|-------|--------|----------------------------------------|--|

|                                      |                                       | Min     | Тур | Max   | Ullits | Kelilaiks                              |  |

| Sector erase time                    |                                       | _       | 1   | 15    | s      | Excludes 00H programming prior erasure |  |

| Chip erase time                      | $T_A = +25  ^{\circ}C$<br>Vcc = 5.0 V | _       | 5   | _     | s      | Excludes 00H programming prior erasure |  |

| Word (16 bit width) programming time |                                       | _       | 16  | 3,600 | μs     | Excludes system-level overhead         |  |

| Erase/Program cycle                  | _                                     | 10,000  |     | _     | cycle  |                                        |  |

| Data holding time                    | _                                     | 100,000 |     | _     | h      |                                        |  |

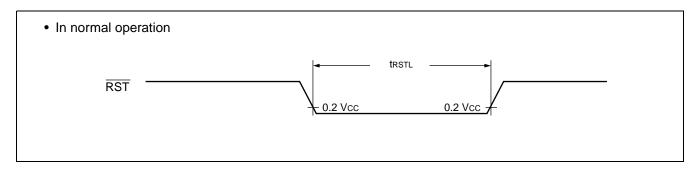

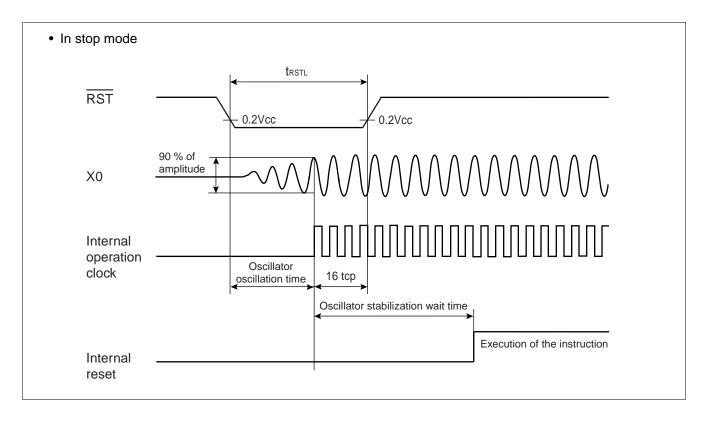

### (2) Reset

$$(T_A = -40 \, ^{\circ}\text{C} \text{ to } +85 \, ^{\circ}\text{C}, \, \text{Vcc} = 2.7 \, \text{V} \, \text{ to } 3.6 \, \text{V}, \, \text{Vss} = \text{AVss} = 0.0 \, \text{V})$$

| Parameter        | Symbol | Pin Name    | Condition | Value                                 | Unit | Remarks |                     |

|------------------|--------|-------------|-----------|---------------------------------------|------|---------|---------------------|

| Farameter        | Symbol | riii Naiile | Condition | Min.                                  | Max. | Oilit   | Nemarks             |

| Reset input time | toor   | rstl RST    |           | 16 tcp —                              |      | ns      | In normal operation |

|                  | IKSIL  |             |           | Oscillator oscillation time* + 16 tcp |      | ms      | In stop<br>mode     |

<sup>\*:</sup> Oscillator oscillation time is the time to reach 90% amplitude. For a crystal oscillator, this is a few to several dozen ms; for a ceramic oscillator, this is several hundred µs to a few ms, and for an external clock this is 0 ms.

### (4) UART0 and UART1

(T<sub>A</sub> = -40 °C to +85 °C, Vcc = 2.7 V to 3.6 V, Vss = AVss = 0.0 V)

| Parameter                                      | Symbol        | Pin Name                 | Condition                                     | Value |      | Unit  | Remarks |

|------------------------------------------------|---------------|--------------------------|-----------------------------------------------|-------|------|-------|---------|

| Faranteter                                     | Syllibol      | Fili Naille              | Condition                                     | Min.  | Max. | Oilit | Kemarks |

| Serial clock cycle time                        | <b>t</b> scyc | SCK0, SCK1               |                                               | 8 tcp |      | ns    |         |

| $SCK \downarrow \to SOT$ delay time            | tsLOV         | SCK0, SCK1<br>SOT0, SOT1 | Internal shift clock<br>mode, output pin      | -80   | 80   | ns    |         |

| Valid SIN → SCK $\uparrow$                     | <b>t</b> ıvsh | SCK0, SCK1<br>SIN0, SIN1 | load is  CL = 80 pF + 1 TTL                   | 100   | _    | ns    |         |

| $SCK \uparrow \rightarrow valid SIN hold time$ | <b>t</b> sнıx | SCK0, SCK1<br>SIN0, SIN1 |                                               | 60    | _    | ns    |         |

| Serial clock "H" pulse width                   | <b>t</b> shsl | SCK0, SCK1               |                                               | 4 tcp |      | ns    |         |

| Serial clock "L" pulse width                   | <b>t</b> slsh | SCK0, SCK1               |                                               | 4 tcp |      | ns    |         |

| $SCK \downarrow \to SOT$ delay time            | tslov         | SCK0, SCK1<br>SOT0, SOT1 | mode, output pin                              |       | 150  | ns    |         |

| Valid SIN $\rightarrow$ SCK ↑                  | <b>t</b> ıvsh | SCK0, SCK1<br>SIN0, SIN1 | load is $C_L = 80 \text{ pF} + 1 \text{ TTL}$ | 60    |      | ns    |         |

| $SCK \uparrow \rightarrow valid SIN hold time$ | <b>t</b> sнıx | SCK0, SCK1<br>SIN0, SIN1 |                                               | 60    |      | ns    |         |

Notes: • These are the AC ratings for CLK synchronous mode.

- CV is the load capacitor connected to the pin for testing.

- tcp is the machine cycle period (unit = ns)

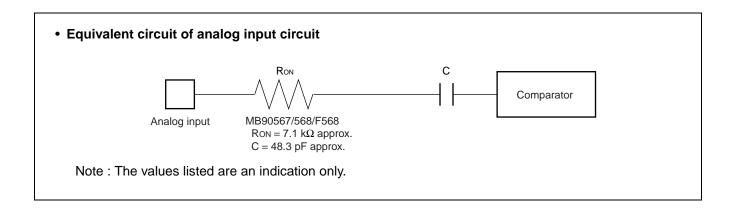

#### 5. Electrical Characteristics for the A/D Converter

$\begin{array}{l} (MB90567/568/F568: T_{A} = -40 \ ^{\circ}C \ to \ +85 \ ^{\circ}C, \ 2.7 \ V \leq AVR, \ Vcc = AVcc = 2.7 \ V \ \ to \ 3.6 \ V, \ Vss = AVss = 0.0 \ V) \\ (MB90V560: T_{A} = +25 \ ^{\circ}C, \ 3.0 \ V \leq AVR, \ Vcc = AVcc = 3.0 \ V \ \ to \ 3.6 \ V, \ Vss = AVss = 0.0 \ V) \\ \end{array}$

| Parameter                     | Symbol           | Pin Name   |                  | Value            |                  | Unit | Remarks            |  |

|-------------------------------|------------------|------------|------------------|------------------|------------------|------|--------------------|--|

| Parameter                     | Symbol           | rin Name   | Min.             | Тур.             | Max.             | Unit |                    |  |

| Resolution                    | _                | _          | _                | _                | 10               | bit  |                    |  |

| Total error                   | _                |            | _                | _                | ±3.0             | LSB  |                    |  |

| Non-linearity error           | _                |            | _                | _                | ±2.5             | LSB  |                    |  |

| Differential linearity error  | _                | _          | _                | _                | ±1.9             | LSB  |                    |  |

| Zero transition voltage       | Vот              | AN0 to AN7 | AVss<br>-1.5 LSB | AVss<br>+0.5 LSB | AVss<br>+2.5 LSB | V    | 1 LSB = (AVR-AVss/ |  |

| Full-scale transition voltage | V <sub>FST</sub> | AN0 to AN7 | AVR<br>-3.5 LSB  | AVR<br>-1.5 LSB  | AVR<br>+0.5 LSB  | V    | 1024               |  |

| Conversion time               | _                | _          | _                | 66 tcp           | _                | ns   |                    |  |

| Sampling time                 | _                |            | _                | 32 tcp           | _                | ns   |                    |  |

| Analog port input current     | lain             | AN0 to AN7 | _                | _                | 10               | μΑ   |                    |  |

| Analog input voltage          | Vain             | AN0 to AN7 | 0                |                  | AVR              | V    |                    |  |

| Reference voltage             | _                | AVR        | 2.7              | _                | AVcc             | V    |                    |  |

| Power supply current          | lΑ               | AVcc       | _                | 1                | 5                | mA   |                    |  |

| Power supply current          | Іан              | AVcc       | _                | _                | 5                | μΑ   | *                  |  |

| Reference voltage             | IR               | AVR        | _                | 100              | 200              | μΑ   |                    |  |

| supply current                | I <sub>RH</sub>  | AVR        |                  |                  | 5                | μΑ   | *                  |  |

| Variation between channels    | _                | AN0 to AN7 | _                | _                | 4                | LSB  |                    |  |

<sup>\*:</sup> Current when A/D converter is not used and CPU is in stop mode (Vcc = AVcc = AVR = 3.3 V)

Notes: • The L reference voltage is fixed to AVss. The relative error increases as AVR becomes smaller.

• Ensure that the output impedance of the external circuit connected to the analog input meets the following condition :

Output impedance of MB90F568 external circuit  $\leq$  14 k $\Omega$  (Sampling Time = 4  $\mu$ s)

Output impedance of MB90567/568 external circuit  $\,\leq 7~k\Omega$  (Sampling Time = 4  $\mu s)$

• If the output impedance of the external circuit is too high, the analog voltage sampling time may be too short.

## **FUJITSU MICROELECTRONICS LIMITED**

7-1, Nishishinjuku 2-chome, Shinjuku Dai-Ichi Seimei Bldg., Shinjuku-ku, Tokyo 163-0722, JAPAN

Tel: +81-3-5322-3347 Fax: +81-3-5322-3387

http://jp.fujitsu.com/fml/en/

For further information please contact:

#### North and South America

FUJITSU MICROELECTRONICS AMERICA, INC. 1250 E. Arques Avenue, M/S 333 Sunnyvale, CA 94085-5401, U.S.A. Tel: +1-408-737-5600 Fax: +1-408-737-5999 http://www.fma.fujitsu.com/

#### **Europe**

FUJITSU MICROELECTRONICS EUROPE GmbH Pittlerstrasse 47, 63225 Langen, F. R. GERMANY Tel: +49-6103-690-0 Fax: +49-6103-690-122 http://emea.fujitsu.com/microelectronics/

#### Korea

FUJITSU MICROELECTRONICS KOREA LTD. 1002 Daechi-Dong, 206 KOSMO TOWER, Kangnam-Gu, Seoul 135-280, KOREA Tel: +82-2-3484-7100 Fax: +82-2-3484-7111 http://www.fmk.fujitsu.com/

#### **Asia Pacific**

FUJITSU MICROELECTRONICS ASIA PTE LTD.

151 Lorong Chuan, #05-08 New Tech Park,

Singapore 556741, SINGAPORE

Tel: +65-6281-0770 Fax: +65-6281-0220

http://www.fujitsu.com/sg/services/micro/semiconductor/

FUJITSU MICROELECTRONICS SHANGHAI CO., LTD. No.222 Yan An Road(E), Rm.3102, Bund Center, Shanghai 200002, P. R. CHINA Tel: +86-21-6335-1560 Fax: +86-21-6335-1605 http://cn.fujitsu.com/fmc/

FUJITSU MICROELECTRONICS PACIFIC ASIA LTD.

11 Canton Road, 10/F., World Commerce Centre,

Tsimshatsui, Kowloon, HONG KONG

Tel: +852-2377-0226 Fax: +852-2376-3269

http://cn.fujitsu.com/fmc/tw

#### All Rights Reserved.

The contents of this document are subject to change without notice.

Customers are advised to consult with sales representatives before ordering.

The information, such as descriptions of function and application circuit examples, in this document are presented solely for the purpose of reference to show examples of operations and uses of FUJITSU MICROELECTRONICS device; FUJITSU MICROELECTRONICS does not warrant proper operation of the device with respect to use based on such information. When you develop equipment incorporating the device based on such information, you must assume any responsibility arising out of such use of the information.

FUJITSU MICROELECTRONICS assumes no liability for any damages whatsoever arising out of the use of the information.

Any information in this document, including descriptions of function and schematic diagrams, shall not be construed as license of the use or exercise of any intellectual property right, such as patent right or copyright, or any other right of FUJITSU MICROELECTRONICS or any third party or does FUJITSU MICROELECTRONICS warrant non-infringement of any third-party's intellectual property right or other right by using such information. FUJITSU MICROELECTRONICS assumes no liability for any infringement of the intellectual property rights or other rights of third parties which would result from the use of information contained herein.

The products described in this document are designed, developed and manufactured as contemplated for general use, including without limitation, ordinary industrial use, general office use, personal use, and household use, but are not designed, developed and manufactured as contemplated (1) for use accompanying fatal risks or dangers that, unless extremely high safety is secured, could have a serious effect to the public, and could lead directly to death, personal injury, severe physical damage or other loss (i.e., nuclear reaction control in nuclear facility, aircraft flight control, air traffic control, mass transport control, medical life support system, missile launch control in weapon system), or (2) for use requiring extremely high reliability (i.e., submersible repeater and artificial satellite).

Please note that FUJITSU MICROELECTRONICS will not be liable against you and/or any third party for any claims or damages arising in connection with above-mentioned uses of the products.

Any semiconductor devices have an inherent chance of failure. You must protect against injury, damage or loss from such failures by incorporating safety design measures into your facility and equipment such as redundancy, fire protection, and prevention of over-current levels and other abnormal operating conditions.

Exportation/release of any products described in this document may require necessary procedures in accordance with the regulations of the Foreign Exchange and Foreign Trade Control Law of Japan and/or US export control laws.

The company names and brand names herein are the trademarks or registered trademarks of their respective owners.