#### Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

E·XF

| Product Status             | Active                                                                     |

|----------------------------|----------------------------------------------------------------------------|

| Core Processor             | ARM® Cortex®-M0+                                                           |

| Core Size                  | 32-Bit Single-Core                                                         |

| Speed                      | 48MHz                                                                      |

| Connectivity               | I <sup>2</sup> C, SCI, SPI, UART/USART, USB                                |

| Peripherals                | Brown-out Detect/Reset, DMA, I <sup>2</sup> S, POR, PWM, WDT               |

| Number of I/O              | 38                                                                         |

| Program Memory Size        | 64KB (64K x 8)                                                             |

| Program Memory Type        | FLASH                                                                      |

| EEPROM Size                | -                                                                          |

| RAM Size                   | 8K x 8                                                                     |

| Voltage - Supply (Vcc/Vdd) | 2.7V ~ 3.63V                                                               |

| Data Converters            | A/D 14x12b; D/A 1x10b                                                      |

| Oscillator Type            | Internal                                                                   |

| Operating Temperature      | -40°C ~ 105°C (TA)                                                         |

| Mounting Type              | Surface Mount                                                              |

| Package / Case             | 48-TQFP                                                                    |

| Supplier Device Package    | 48-TQFP (7x7)                                                              |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/atsamda1g16b-abt |

|                            |                                                                            |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

### 17.6.5.2 Run in Standby Mode

In standby mode, the GCLK can continuously output the generator output to GCLK\_IO.

When set, the GCLK can continuously output the generator output to GCLK\_IO.

Refer to Generic Clock Output on I/O Pins for details.

### 17.6.6 Synchronization

Due to asynchronicity between the main clock domain and the peripheral clock domains, some registers need to be synchronized when written or read.

When executing an operation that requires synchronization, the Synchronization Busy bit in the Status register (STATUS.SYNCBUSY) will be set immediately, and cleared when synchronization is complete.

If an operation that requires synchronization is executed while STATUS.SYNCBUSY=1, the bus will be stalled. All operations will complete successfully, but the CPU will be stalled and interrupts will be pending as long as the bus is stalled.

The following registers are synchronized when written:

- Generic Clock Generator Control register (GENCTRL)

- Generic Clock Generator Division register (GENDIV)

- Control register (CTRL)

Required write-synchronization is denoted by the "Write-Synchronized" property in the register description.

### Related Links

Register Synchronization

### 17.7 Register Summary

### Table 17-2. Register Summary

| Offset | Name     | Bit   |          |       |          |          |        |     |       |       |

|--------|----------|-------|----------|-------|----------|----------|--------|-----|-------|-------|

|        |          | Pos.  |          |       |          |          |        |     |       |       |

| 0x0    | CTRL     | 7:0   |          |       |          |          |        |     |       | SWRST |

| 0x1    | STATUS   | 7:0   | SYNCBUSY |       |          |          |        |     |       |       |

| 0x2    | CLKCTRL  | 7:0   |          |       | ID[      | 5:0]     |        |     |       |       |

| 0x3    | GLACIAL  | 15:8  | WRTLOCK  | CLKEN | GEN[3:0] |          |        |     |       |       |

| 0x4    |          | 7:0   |          |       |          | ID[3:0]  |        |     |       |       |

| 0x5    | GENCTRL  | 15:8  |          |       |          | SRC[4:0] |        |     |       |       |

| 0x6    | GENCIRE  | 23:16 |          |       | RUNSTDBY | DIVSEL   | OE     | OOV | IDC   | GENEN |

| 0x7    |          | 31:24 |          |       |          |          |        |     |       |       |

| 0x8    |          | 7:0   |          |       |          |          |        | ID[ | [3:0] |       |

| 0x9    | - GENDIV | 15:8  |          |       | DIV[7:0] |          |        |     |       |       |

| 0xA    |          | 23:16 |          |       |          | DIV      | [15:8] |     |       |       |

| 0xB    |          | 31:24 |          |       |          |          |        |     |       |       |

| Value | Description                            |

|-------|----------------------------------------|

| 0     | The APBC clock for the TC3 is stopped. |

| 1     | The APBC clock for the TC3 is enabled. |

### Bit 10 – TCC2: TCC2 APB Clock Enable

| Value | Description                             |

|-------|-----------------------------------------|

| 0     | The APBC clock for the TCC2 is stopped. |

| 1     | The APBC clock for the TCC2 is enabled. |

### Bit 9 – TCC1: TCC1 APB Clock Enable

| Value | Description                             |

|-------|-----------------------------------------|

| 0     | The APBC clock for the TCC1 is stopped. |

| 1     | The APBC clock for the TCC1 is enabled. |

### Bit 8 – TCC0: TCC0 APB Clock Enable

| Value | Description                             |

|-------|-----------------------------------------|

| 0     | The APBC clock for the TCC0 is stopped. |

| 1     | The APBC clock for the TCC0 is enabled. |

### Bit 7 – SERCOM5: SERCOM5 APB Clock Enable

| Value | Description                                |

|-------|--------------------------------------------|

| 0     | The APBC clock for the SERCOM5 is stopped. |

| 1     | The APBC clock for the SERCOM5 is enabled. |

### Bit 6 – SERCOM4: SERCOM4 APB Clock Enable

| Value | Description                                |

|-------|--------------------------------------------|

| 0     | The APBC clock for the SERCOM4 is stopped. |

| 1     | The APBC clock for the SERCOM4 is enabled. |

### Bit 5 – SERCOM3: SERCOM3 APB Clock Enable

| Value | Description                                |

|-------|--------------------------------------------|

| 0     | The APBC clock for the SERCOM3 is stopped. |

| 1     | The APBC clock for the SERCOM3 is enabled. |

### Bit 4 – SERCOM2: SERCOM2 APB Clock Enable

| Value | Description                                |

|-------|--------------------------------------------|

| 0     | The APBC clock for the SERCOM2 is stopped. |

| 1     | The APBC clock for the SERCOM2 is enabled. |

### Bit 3 – SERCOM1: SERCOM1 APB Clock Enable

| Value | Description                                |

|-------|--------------------------------------------|

| 0     | The APBC clock for the SERCOM1 is stopped. |

| 1     | The APBC clock for the SERCOM1 is enabled. |

### Bit 2 – SERCOM0: SERCOM0 APB Clock Enable

# SAM DA1

| Offset | Name        | Bit Pos.       |          |            |          |         |                |         |             |        |  |

|--------|-------------|----------------|----------|------------|----------|---------|----------------|---------|-------------|--------|--|

|        |             |                |          |            |          |         |                |         |             |        |  |

| 0x27   |             |                |          |            |          |         |                |         |             |        |  |

| 0x28   |             | 7:0            |          |            |          | FIN     | E[7:0]         |         |             |        |  |

| 0x29   |             | 15:8           |          |            | COAR     | SE[5:0] |                |         | FINE        | [9:8]  |  |

| 0x2A   | DFLLVAL     | 23:16          |          |            |          | DIFI    | =[7:0]         |         |             |        |  |

| 0x2B   |             | 31:24          |          | DIFF[15:8] |          |         |                |         |             |        |  |

| 0x2C   |             | 7:0            |          |            |          | MUI     | _[7:0]         |         |             |        |  |

| 0x2D   |             | 15:8           |          |            |          | MUL     | [15:8]         |         |             |        |  |

| 0x2E   | DFLLMUL     | 23:16          |          | FSTEP[7:0] |          |         |                |         |             |        |  |

| 0x2F   |             | 31:24          |          |            | CSTE     | P[5:0]  |                |         | FSTE        | P[9:8] |  |

| 0x30   | DFLLSYNC    | 7:0            | READREQ  |            |          |         |                |         |             |        |  |

| 0x31   |             |                |          |            |          |         |                |         |             |        |  |

|        | Reserved    |                |          |            |          |         |                |         |             |        |  |

| 0x33   |             |                |          |            |          |         |                |         |             |        |  |

| 0x34   |             | 7:0            |          | RUNSTDBY   |          | ACTIO   | ON[1:0]        | HYST    | ENABLE      |        |  |

| 0x35   | BOD33       | 15:8           |          | PSE        | L[3:0]   |         |                |         | CEN         | MODE   |  |

| 0x36   | 60033       | 23:16          |          |            |          |         | LEVI           | EL[5:0] |             |        |  |

| 0x37   |             | 31:24          |          |            |          |         |                |         |             |        |  |

| 0x38   |             |                |          |            |          |         |                |         |             |        |  |

|        | Reserved    |                |          |            |          |         |                |         |             |        |  |

| 0x3B   |             |                |          |            |          |         |                |         |             |        |  |

| 0x3C   | VREG        | 7:0            |          | RUNSTDBY   |          |         |                |         |             |        |  |

| 0x3D   |             | 15:8           |          |            | FORCELDO |         |                |         |             |        |  |

| 0x3E   |             |                |          |            |          |         |                |         |             |        |  |

|        | Reserved    |                |          |            |          |         |                |         |             |        |  |

| 0x3F   |             |                |          |            |          |         |                |         |             |        |  |

| 0x40   |             | 7:0            |          |            |          |         |                | BGOUTEN | TSEN        |        |  |

| 0x41   | VREF        | 15:8           |          |            |          |         |                |         |             |        |  |

| 0x42   |             | 23:16          |          |            |          | CALI    | B[7:0]         |         |             |        |  |

| 0x43   |             | 31:24          |          |            |          |         |                |         | CALIB[10:8] |        |  |

| 0x44   | DPLLCTRLA   | 7:0            | ONDEMAND | RUNSTDBY   |          |         |                |         | ENABLE      |        |  |

| 0x45   | <b>D</b>    |                |          |            |          |         |                |         |             |        |  |

|        | Reserved    |                |          |            |          |         |                |         |             |        |  |

| 0x47   |             | 7.0            |          |            |          | 1.05    | 0[7:0]         |         |             |        |  |

| 0x48   |             | 7:0            |          |            |          | LDF     | R[7:0]         |         | [11.0]      |        |  |

| 0x49   | DPLLRATIO   | 15:8           |          |            |          |         |                |         |             |        |  |

| 0x4A   | _           | 23:16<br>31:24 |          |            |          |         |                | LDRFR   | AC[3:0]     |        |  |

| 0x4B   |             |                |          |            | DEEO     | LK[4.0] |                |         |             | D[4.0] |  |

| 0x4C   |             | 7:0            |          |            | REFC     | LK[1:0] | WUF            | LPEN    | FILTE       | R[1:0] |  |

| 0x4D   | - DPLLCTRLB | 15:8           |          |            |          | LBYPASS | ([7:0]         |         | LTIME[2:0]  |        |  |

| 0x4E   |             | 23:16          |          |            |          | DIV     | <b>'</b> [7:0] |         |             |        |  |

| 0x4F   |             | 31:24          |          |            |          |         |                |         | DIV[10:8]   |        |  |

| 0x50   | DPLLSTATUS  | 7:0            |          |            |          |         | DIV            | ENABLE  | CLKRDY      | LOCK   |  |

### Bit 11 – B33SRDY: BOD33 Synchronization Ready Interrupt Enable

Writing a zero to this bit has no effect.

Writing a one to this bit will set the BOD33 Synchronization Ready Interrupt Enable bit, which enables the BOD33 Synchronization Ready interrupt.

| Value | Description                                                                            |  |  |  |  |

|-------|----------------------------------------------------------------------------------------|--|--|--|--|

| 0     | The BOD33 Synchronization Ready interrupt is disabled.                                 |  |  |  |  |

| 1     | The BOD33 Synchronization Ready interrupt is enabled, and an interrupt request will be |  |  |  |  |

|       | generated when the BOD33 Synchronization Ready Interrupt flag is set.                  |  |  |  |  |

### Bit 10 – BOD33DET: BOD33 Detection Interrupt Enable

Writing a zero to this bit has no effect.

Writing a one to this bit will set the BOD33 Detection Interrupt Enable bit, which enables the BOD33 Detection interrupt.

| Value | Description                                                                                                                          |

|-------|--------------------------------------------------------------------------------------------------------------------------------------|

| 0     | The BOD33 Detection interrupt is disabled.                                                                                           |

| 1     | The BOD33 Detection interrupt is enabled, and an interrupt request will be generated when the BOD33 Detection Interrupt flag is set. |

### Bit 9 – BOD33RDY: BOD33 Ready Interrupt Enable

Writing a zero to this bit has no effect.

Writing a one to this bit will set the BOD33 Ready Interrupt Enable bit, which enables the BOD33 Ready interrupt.

| Value | Description                                                                                                                  |

|-------|------------------------------------------------------------------------------------------------------------------------------|

| 0     | The BOD33 Ready interrupt is disabled.                                                                                       |

| 1     | The BOD33 Ready interrupt is enabled, and an interrupt request will be generated when the BOD33 Ready Interrupt flag is set. |

### Bit 8 – DFLLRCS: DFLL Reference Clock Stopped Interrupt Enable

Writing a zero to this bit has no effect.

Writing a one to this bit will set the DFLL Reference Clock Stopped Interrupt Enable bit, which enables the DFLL Reference Clock Stopped interrupt.

| Value | Description                                                                                                                                                    |

|-------|----------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 0     | The DFLL Reference Clock Stopped interrupt is disabled.                                                                                                        |

| 1     | The DFLL Reference Clock Stopped interrupt is enabled, and an interrupt request will be generated when the DFLL Reference Clock Stopped Interrupt flag is set. |

### Bit 7 – DFLLLCKC: DFLL Lock Coarse Interrupt Enable

Writing a zero to this bit has no effect.

Writing a one to this bit will set the DFLL Lock Coarse Interrupt Enable bit, which enables the DFLL Lock Coarse interrupt.

| Value | Description                                                                                                                            |

|-------|----------------------------------------------------------------------------------------------------------------------------------------|

| 0     | The DFLL Lock Coarse interrupt is disabled.                                                                                            |

| 1     | The DFLL Lock Coarse interrupt is enabled, and an interrupt request will be generated when the DFLL Lock Coarse Interrupt flag is set. |

# SAM DA1

| Offset           | Name       | Bit Pos. |                 |         |        |         |           |         |            |        |  |

|------------------|------------|----------|-----------------|---------|--------|---------|-----------|---------|------------|--------|--|

| 0x30             |            | 7:0      |                 |         |        |         | LVLEXx    | LVLEXx  | LVLEXx     | LVLEXx |  |

| 0x31             |            | 15:8     | ABUSY           |         |        |         |           | ID[4:0] |            |        |  |

| 0x32             | ACTIVE     | 23:16    |                 |         |        | BTCN    | IT[7:0]   |         |            |        |  |

| 0x33             |            | 31:24    |                 |         |        | BTCN    | T[15:8]   |         |            |        |  |

| 0x34             |            | 7:0      | BASEADDR[7:0]   |         |        |         |           |         |            |        |  |

| 0x35             |            | 15:8     | BASEADDR[15:8]  |         |        |         |           |         |            |        |  |

| 0x36             | BASEADDR   | 23:16    | BASEADDR[23:16] |         |        |         |           |         |            |        |  |

| 0x37             |            | 31:24    |                 |         |        | BASEADI | DR[31:24] |         |            |        |  |

| 0x38             |            | 7:0      |                 |         |        | WRBAD   | DR[7:0]   |         |            |        |  |

| 0x39             | WRBADDR    | 15:8     | WRBADDR[15:8]   |         |        |         |           |         |            |        |  |

| 0x3A             | WRBADDR    | 23:16    | WRBADDR[23:16]  |         |        |         |           |         |            |        |  |

| 0x3B             |            | 31:24    |                 |         |        | WRBADI  | DR[31:24] |         |            |        |  |

| 0x3C<br><br>0x3E | Reserved   |          |                 |         |        |         |           |         |            |        |  |

| 0x3F             | CHID       | 7:0      |                 |         |        |         |           | ID[     | 3:0]       |        |  |

| 0x40             | CHCTRLA    | 7:0      |                 |         |        |         |           |         | ENABLE     | SWRST  |  |

| 0x41<br><br>0x43 | Reserved   |          |                 |         |        |         |           |         |            |        |  |

| 0x44             |            | 7:0      |                 | LV      | L[1:0] | EVOE    | EVIE      |         | EVACT[2:0] |        |  |

| 0x45             | CHCTRLB    | 15:8     |                 |         |        |         | TRIGS     | RC[5:0] | -          |        |  |

| 0x46             | CHCTREB    | 23:16    | TRIGA           | CT[1:0] |        |         |           |         |            |        |  |

| 0x47             |            | 31:24    |                 |         |        |         |           |         | CME        | 0[1:0] |  |

| 0x48             |            |          |                 |         |        |         |           |         |            |        |  |

|                  | Reserved   |          |                 |         |        |         |           |         |            |        |  |

| 0x4B             |            |          |                 |         |        |         |           |         |            |        |  |

| 0x4C             | CHINTENCLR | 7:0      |                 |         |        |         |           | SUSP    | TCMPL      | TERR   |  |

| 0x4D             | CHINTENSET | 7:0      |                 |         |        |         |           | SUSP    | TCMPL      | TERR   |  |

| 0x4E             | CHINTFLAG  | 7:0      |                 |         |        |         |           | SUSP    | TCMPL      | TERR   |  |

| 0x4F             | CHSTATUS   | 7:0      |                 |         |        |         |           | FERR    | BUSY       | PEND   |  |

### 22.8 Register Description

Registers can be 8, 16, or 32 bits wide. Atomic 8-, 16- and 32-bit accesses are supported. In addition, the 8-bit quarters and 16-bit halves of a 32-bit register, and the 8-bit halves of a 16-bit register can be accessed directly.

Some registers are optionally write-protected by the Peripheral Access Controller (PAC). Optional PAC write-protection is denoted by the "PAC Write-Protection" property in each individual register description. For details, refer to Register Access Protection.

Some registers are enable-protected, meaning they can only be written when the peripheral is disabled. Enable-protection is denoted by the "Enable-Protected" property in each individual register description.

### 22.8.1 Control

### 24.4 Signal Description

Not applicable.

### 24.5 **Product Dependencies**

In order to use this module, other parts of the system must be configured correctly, as described below.

### 24.5.1 Power Management

The NVMCTRL will continue to operate in any sleep mode where the selected source clock is running. The NVMCTRL interrupts can be used to wake up the device from sleep modes.

The Power Manager will automatically put the NVM block into a low-power state when entering sleep mode. This is based on the Control B register (CTRLB) SLEEPPRM bit setting. Refer to the CTRLB.SLEEPPRM register description for more details.

### **Related Links**

PM – Power Manager

### 24.5.2 Clocks

Two synchronous clocks are used by the NVMCTRL. One is provided by the AHB bus (CLK\_NVMCTRL\_AHB) and the other is provided by the APB bus (CLK\_NVMCTRL\_APB). For higher system frequencies, a programmable number of wait states can be used to optimize performance. When changing the AHB bus frequency, the user must ensure that the NVM Controller is configured with the proper number of wait states. Refer to the Electrical Characteristics for the exact number of wait states to be used for a particular frequency range.

### **Related Links**

**Electrical Characteristics**

### 24.5.3 Interrupts

The NVM Controller interrupt request line is connected to the interrupt controller. Using the NVMCTRL interrupt requires the interrupt controller to be programmed first.

### 24.5.4 Debug Operation

When an external debugger forces the CPU into debug mode, the peripheral continues normal operation.

Access to the NVM block can be protected by the security bit. In this case, the NVM block will not be accessible. See the section on the NVMCTRL Security Bit for details.

### 24.5.5 Register Access Protection

All registers with write-access are optionally write-protected by the Peripheral Access Controller (PAC), except the following registers:

- Interrupt Flag Status and Clear register (INTFLAG)

- Status register (STATUS)

Optional write-protection by the Peripheral Access Controller (PAC) is denoted by the "PAC Write-Protection" property in each individual register description.

### **Related Links**

PAC - Peripheral Access Controller

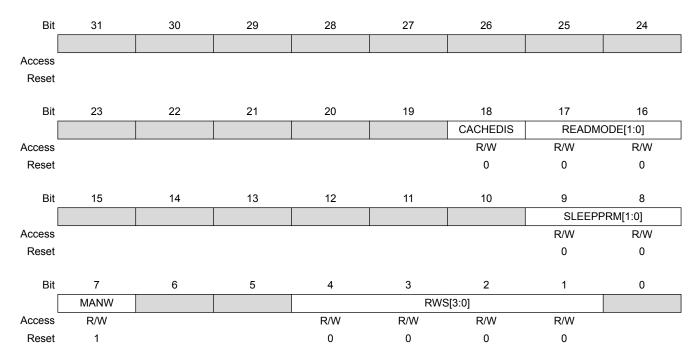

Name:CTRLBOffset:0x04 [ID-00000b2c]Reset:0x00000080Property:PAC Write-Protection

### Bit 18 – CACHEDIS: Cache Disable

This bit is used to disable the cache.

| Value | Description           |

|-------|-----------------------|

| 0     | The cache is enabled  |

| 1     | The cache is disabled |

### Bits 17:16 - READMODE[1:0]: NVMCTRL Read Mode

| Value | Name            | Description                                                                                                                                                                                                                                            |

|-------|-----------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 0x0   | NO_MISS_PENALTY | The NVM Controller (cache system) does not insert wait states on a cache miss. Gives the best system performance.                                                                                                                                      |

| 0x1   | LOW_POWER       | Reduces power consumption of the cache system, but inserts a wait<br>state each time there is a cache miss. This mode may not be relevant<br>if CPU performance is required, as the application will be stalled and<br>may lead to increased run time. |

| 0x2   | DETERMINISTIC   | The cache system ensures that a cache hit or miss takes the same<br>amount of time, determined by the number of programmed Flash wait<br>states. This mode can be used for real-time applications that require<br>deterministic execution timings.     |

| 0x3   | Reserved        |                                                                                                                                                                                                                                                        |

### Bits 9:8 – SLEEPPRM[1:0]: Power Reduction Mode during Sleep

Indicates the Power Reduction Mode during sleep.

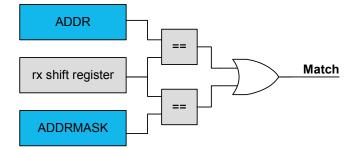

### Figure 27-5. Two Unique Addresses

### Address Range

The range of addresses between and including ADDR.ADDR and ADDR.ADDRMASK will cause a match. ADDR.ADDR and ADDR.ADDRMASK can be set to any two addresses, with ADDR.ADDR acting as the upper limit and ADDR.ADDRMASK acting as the lower limit.

### Figure 27-6. Address Range

### 27.6.4 DMA Operation

Not applicable.

### 27.6.5 Interrupts

Interrupt sources are mode-specific. See the respective SERCOM mode chapters for details.

Each interrupt source has its own interrupt flag.

The interrupt flag in the Interrupt Flag Status and Clear register (INTFLAG) will be set when the interrupt condition is met.

Each interrupt can be individually enabled by writing '1' to the corresponding bit in the Interrupt Enable Set register (INTENSET), and disabled by writing '1' to the corresponding bit in the Interrupt Enable Clear register (INTENCLR).

An interrupt request is generated when the interrupt flag is set and the corresponding interrupt is enabled. The interrupt request remains active until either the interrupt flag is cleared, the interrupt is disabled, or the SERCOM is reset. For details on clearing interrupt flags, refer to the INTFLAG register description.

The SERCOM has one common interrupt request line for all the interrupt sources. The value of INTFLAG indicates which interrupt condition occurred. The user must read the INTFLAG register to determine which interrupt condition is present.

### Note:

Note that interrupts must be globally enabled for interrupt requests.

### **Related Links**

Nested Vector Interrupt Controller

### 27.6.6 Events

Not applicable.

### 27.6.7 Sleep Mode Operation

The peripheral can operate in any sleep mode where the selected serial clock is running. This clock can be external or generated by the internal baud-rate generator.

#### **Transaction Diagram Symbols** Bus Driver Special Bus Conditions Master driving bus S START condition Sr Slave driving bus repeated START condition Ρ STOP condition Either Master or Slave driving bus Data Package Direction Acknowledge R Master Read Acknowledge (ACK) Α '1' '0' Ā $\overline{\mathbf{W}}$ Master Write Not Acknowledge (NACK)

### 30.6.2 Basic Operation

'0'

### 30.6.2.1 Initialization

The following registers are enable-protected, meaning they can be written only when the I<sup>2</sup>C interface is disabled (CTRLA.ENABLE is '0'):

'1'

- Control A register (CTRLA), except Enable (CTRLA.ENABLE) and Software Reset (CTRLA.SWRST) bits

- Control B register (CTRLB), except Acknowledge Action (CTRLB.ACKACT) and Command (CTRLB.CMD) bits

- Baud register (BAUD)

- Address register (ADDR) in slave operation.

When the I<sup>2</sup>C is enabled or is being enabled (CTRLA.ENABLE=1), writing to these registers will be discarded. If the I<sup>2</sup>C is being disabled, writing to these registers will be completed after the disabling.

Enable-protection is denoted by the "Enable-Protection" property in the register description.

Before the  $I^2C$  is enabled it must be configured as outlined by the following steps:

- 1. Select I<sup>2</sup>C Master or Slave mode by writing 0x4 or 0x5 to the Operating Mode bits in the CTRLA register (CTRLA.MODE).

- 2. If desired, select the SDA Hold Time value in the CTRLA register (CTRLA.SDAHOLD).

- 3. If desired, enable smart operation by setting the Smart Mode Enable bit in the CTRLB register (CTRLB.SMEN).

- 4. If desired, enable SCL low time-out by setting the SCL Low Time-Out bit in the Control A register (CTRLA.LOWTOUT).

- 5. In Master mode:

- 5.1. Select the inactive bus time-out in the Inactive Time-Out bit group in the CTRLA register (CTRLA.INACTOUT).

- 5.2. Write the Baud Rate register (BAUD) to generate the desired baud rate.

In Slave mode:

## 31. I2S - Inter-IC Sound Controller

### 31.1 Overview

The Inter-IC Sound Controller (I<sup>2</sup>S) provides bidirectional, synchronous and digital audio link with external audio devices.

This controller is compliant with the Inter-IC Sound (I<sup>2</sup>S) bus specification. It supports TDM interface with external multi-slot audio codecs. It also supports PDM interface with external MEMS microphones.

The I<sup>2</sup>S consists of two Clock Units and two Serializers, that can be enabled separately, to provide Master, Slave, or controller modes, and operate as Receiver or Transmitter.

The pins associated with  $I^2S$  peripheral are SDm, FSn, SCKn, and MCKn pins, where n=[0,1] denotes the of clock unit and m=[0,1] is the Serializers instance.

FSn is referred to as Word Select in standard I<sup>2</sup>S mode operation and as Frame Sync in TDM mode. Peripheral DMAC channels, separate for each Serializer, allow a continuous high bitrate data transfer without processor intervention to the following:

- Audio CODECs in Master, Slave, or Controller mode

- Stereo DAC or ADC through dedicated I<sup>2</sup>S serial interface

- Multi-slot or multiple stereo DACs or ADCs, using the TDM format

- Mono or stereo MEMS microphones, using the PDM interface

- 1-channel burst transfer with non-periodic Frame Sync

Each Serializer supports using either a single DMAC channel for all data channels, or two separate DMAC channels for different data channels.

The I<sup>2</sup>S supports 8- and 16-bit compact stereo format. This helps in reducing the required DMA bandwidth by transferring the left and right samples within the same data word.

Usually, an external audio codec or digital signal processor (DSP) requires a clock which is a multiple of the sampling frequency *fs* (eg.  $384 \times fs$ ). The l<sup>2</sup>S peripheral in Master Mode and Controller mode is capable of outputting an output clock ranging from  $16 \times fs$  to  $1024 \times fs$  on the Master Clock pin (MCKn).

### 31.2 Features

- Compliant with Inter-IC Sound (I<sup>2</sup>S) bus specification

- 2 independent Serializers configurable as receiver or as transmitter

- Supported data formats:

- 32-, 24-, 20-, 18-, 16-, and 8-bit mono or stereo format

- 16- and 8-bit compact stereo format, with left and right samples packed in the same word to reduce data transfers

- Supported data frame formats:

- 2-channel I<sup>2</sup>S with Word Select

- 1- to 8-slot Time Division Multiplexed (TDM) with Frame Sync and individually enabled slots

- 1- or 2-channel Pulse Density Modulation (PDM) reception for MEMS microphones

- 1-channel burst transfer with non-periodic Frame Sync

- 2 independent Clock Units handling either the same clock or separate clocks for the Serializers:

### Bits 1,0 – RXRDYx : Receive Ready x Interrupt Enable [x=1..0]

Writing a '0' to this bit has no effect.

Writing a '1' to this bit will set the Receive Ready Interrupt Enable bit, which enables the Receive Ready interrupt.

| Value | Description                              |

|-------|------------------------------------------|

| 0     | The Receive Ready interrupt is disabled. |

| 1     | The Receive Ready interrupt is enabled.  |

### 31.9.5 Interrupt Flag Status and Clear

| Name:       | INTFLAG            |  |  |  |  |  |

|-------------|--------------------|--|--|--|--|--|

| Offset:     | 0x14 [ID-000019dd] |  |  |  |  |  |

| Reset:      | 0x0000             |  |  |  |  |  |

| Property: - |                    |  |  |  |  |  |

| 15 | 14      | 13    | 12                                                                                              | 11                                     | 10                                           | 9                                                   | 8                                                                                    |

|----|---------|-------|-------------------------------------------------------------------------------------------------|----------------------------------------|----------------------------------------------|-----------------------------------------------------|--------------------------------------------------------------------------------------|

|    |         | TXURx | TXURx                                                                                           |                                        |                                              | TXRDYx                                              | TXRDYx                                                                               |

|    |         | R/W   | R/W                                                                                             |                                        |                                              | R/W                                                 | R/W                                                                                  |

|    |         | 0     | 0                                                                                               |                                        |                                              | 0                                                   | 0                                                                                    |

|    |         |       |                                                                                                 |                                        |                                              |                                                     |                                                                                      |

| 7  | 6       | 5     | 4                                                                                               | 3                                      | 2                                            | 1                                                   | 0                                                                                    |

|    |         | RXORx | RXORx                                                                                           |                                        |                                              | RXRDYx                                              | RXRDYx                                                                               |

|    |         | R/W   | R/W                                                                                             |                                        |                                              | R/W                                                 | R/W                                                                                  |

|    |         | 0     | 0                                                                                               |                                        |                                              | 0                                                   | 0                                                                                    |

|    | 15<br>7 |       | TXURx           R/W           0           7         6           S           RXORx           R/W | TXURxTXURxR/WR/W007654RXORxRXORxR/WR/W | TXURxTXURxR/WR/W0076543RXORxRXORxRXORxR/WR/W | TXURxTXURxTXURxR/WR/W00765432RXORxRXORxRXORxLR/WR/W | TXURxTXURxTXRDYxR/WR/WR/W00076543217654321765432176788887777888777778887788888788888 |

### Bits 13,12 – TXURx : Transmit Underrun x [x=1..0]

This flag is cleared by writing a '1' to it.

This flag is set when a Transmit Underrun condition occurs in Sequencer x, and will generate an interrupt request if INTENCLR/SET.TXURx is set to '1'.

Writing a '0' to this bit has no effect.

Writing a '1' to this bit will clear the Transmit Underrun x interrupt flag.

### Bits 9,8 – TXRDYx : Transmit Ready x [x=1..0]

This flag is cleared by writing to DATAx register or writing a '1' to it.

This flag is set when Sequencer x is ready to accept a new data word to be transmitted, and will generate an interrupt request if INTENCLR/SET.TXRDYx is set to '1'.

Writing a '0' to this bit has no effect.

Writing a '1' to this bit will clear the Transmit Ready x interrupt flag.

### Bits 4,5 – RXORx : Receive Overrun x [x=1..0]

This flag is cleared by writing a '1' to it.

This flag is set when a Receive Overrun condition occurs in Sequencer x, and will generate an interrupt request if INTENCLR/SET.RXORx is set to '1'.

Writing a '0' to this bit has no effect.

Writing a '1' to this bit will clear the Receive Overrun x interrupt flag.

- Input events:

- Two input events for counter

- One input event for each channel

- Output events:

- Three output events (Count, Re-Trigger and Overflow) available for counter

- One Compare Match/Input Capture event output for each channel

- Interrupts:

- Overflow and Re-Trigger interrupt

- Compare Match/Input Capture interrupt

- Interrupt on fault detection

- Can be used with DMA and can trigger DMA transactions

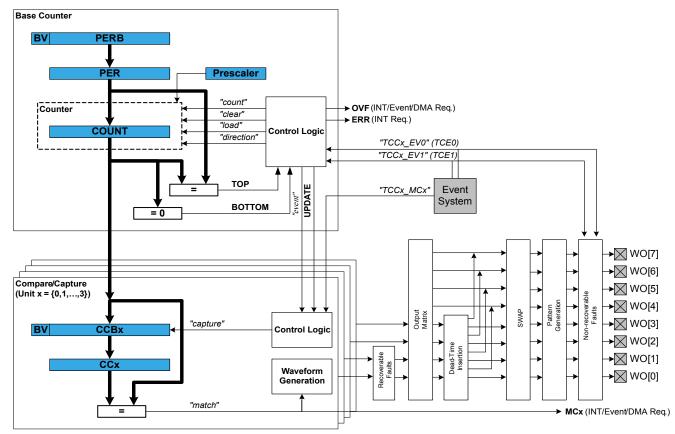

### 33.3 Block Diagram

### Figure 33-1. Timer/Counter for Control Applications - Block Diagram

## 33.4 Signal Description

| Pin Name   | Туре           | Description                       |

|------------|----------------|-----------------------------------|

| TCCx/WO[0] | Digital output | Compare channel 0 waveform output |

| TCCx/WO[1] | Digital output | Compare channel 1 waveform output |

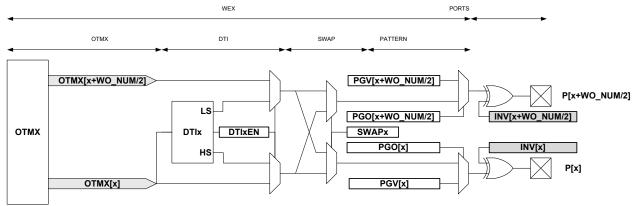

### Figure 33-31. Waveform Extension Stage Details

**The output matrix (OTMX)** unit distributes compare channels, according to the selectable configurations in Table 33-4.

| Table 33-4 | Output Matrix C | Channel Pin | Routing | Configuration |

|------------|-----------------|-------------|---------|---------------|

|------------|-----------------|-------------|---------|---------------|

| Value |     | OTMX[x] |     |     |     |     |     |     |

|-------|-----|---------|-----|-----|-----|-----|-----|-----|

| 0x0   | CC3 | CC2     | CC1 | CC0 | CC3 | CC2 | CC1 | CC0 |

| 0x1   | CC1 | CC0     | CC1 | CC0 | CC1 | CC0 | CC1 | CC0 |

| 0x2   | CC0 | CC0     | CC0 | CC0 | CC0 | CC0 | CC0 | CC0 |

| 0x3   | CC1 | CC1     | CC1 | CC1 | CC1 | CC1 | CC1 | CC0 |

Notes on Table 33-4:

- Configuration 0x0 is the default configuration. The channel location is the default one, and channels are distributed on outputs modulo the number of channels. Channel 0 is routed to the Output matrix output OTMX[0], and Channel 1 to OTMX[1]. If there are more outputs than channels, then channel 0 is duplicated to the Output matrix output OTMX[CC\_NUM], channel 1 to OTMX[CC\_NUM+1] and so on.

- Configuration 0x1 distributes the channels on output modulo half the number of channels. This

assigns twice the number of output locations to the lower channels than the default configuration.

This can be used, for example, to control the four transistors of a full bridge using only two compare

channels.

Using pattern generation, some of these four outputs can be overwritten by a constant level, enabling flexible drive of a full bridge in all quadrant configurations.

- Configuration 0x2 distributes compare channel 0 (CC0) to all port pins. With pattern generation, this

configuration can control a stepper motor.

- Configuration 0x3 distributes the compare channel CC0 to the first output, and the channel CC1 to all other outputs. Together with pattern generation and the fault extension, this configuration can control up to seven LED strings, with a boost stage.

| Value | ОТМХ[3] | ОТМХ[2] | ОТМХ[1] | ОТМХ[0] |

|-------|---------|---------|---------|---------|

| 0x0   | CC3     | CC2     | CC1     | CC0     |

| 0x1   | CC1     | CC0     | CC1     | CC0     |

### Table 33-5. Example: four compare channels on four outputs

### 33.6.4.2 Interrupts

The TCC has the following interrupt sources:

- Overflow/Underflow (OVF)

- Retrigger (TRG)

- Count (CNT) refer also to description of EVCTRL.CNTSEL.

- Capture Overflow Error (ERR)

- Debug Fault State (DFS)

- Recoverable Faults (FAULTn)

- Non-recoverable Faults (FAULTx)

- Compare Match or Capture Channels (MCx)

These interrupts are asynchronous wake-up sources. See Sleep Mode Entry and Exit Table in PM/Sleep Mode Controller section for details.

Each interrupt source has an interrupt flag associated with it. The interrupt flag in the Interrupt Flag Status and Clear (INTFLAG) register is set when the interrupt condition occurs. Each interrupt can be individually enabled by writing a '1' to the corresponding bit in the Interrupt Enable Set (INTENSET) register, and disabled by writing a '1' to the corresponding bit in the Interrupt Enable Clear (INTENCLR) register. An interrupt request is generated when the interrupt flag is set and the corresponding interrupt is enabled. The interrupt request remains active until the interrupt flag is cleared, the interrupt is disabled, or the TCC is reset. See INTFLAG for details on how to clear interrupt flags. The TCC has one common interrupt request line for all the interrupt sources. The user must read the INTFLAG register to determine which interrupt condition is present.

Note: Interrupts must be globally enabled for interrupt requests to be generated. Refer to *Nested Vector Interrupt Controller* for details.

### **Related Links**

Nested Vector Interrupt Controller Sleep Mode Controller IDLE Mode STANDBY Mode

### 33.6.4.3 Events

The TCC can generate the following output events:

- Overflow/Underflow (OVF)

- Trigger (TRG)

- Counter (CNT) For further details, refer to EVCTRL.CNTSEL description.

- Compare Match or Capture on compare/capture channels: MCx

Writing a '1' ('0') to an Event Output bit in the Event Control Register (EVCTRL.xxEO) enables (disables) the corresponding output event. Refer also to *EVSYS – Event System*.

The TCC can take the following actions on a channel input event (MCx):

- Capture event

- Generate a recoverable or non-recoverable fault

The TCC can take the following actions on counter Event 1 (TCCx EV1):

- Counter re-trigger

- Counter direction control

- Stop the counter

### Bit 1 – DTGLIN: Data Toggle IN Sequence

Writing a zero to the bit EPSTATUSCLR.DTGLINCLR will clear this bit.

Writing a one to the bit EPSTATUSSET.DTGLINSET will set this bit.

| Val | lue | Description                                                       |

|-----|-----|-------------------------------------------------------------------|

| 0   |     | The PID of the next expected IN transaction will be zero: data 0. |

| 1   |     | The PID of the next expected IN transaction will be one: data 1.  |

### Bit 0 – DTGLOUT: Data Toggle OUT Sequence

Writing a zero to the bit EPSTATUSCLR.DTGLOUTCLR will clear this bit.

Writing a one to the bit EPSTATUSSET.DTGLOUTSET will set this bit.

| Va | lue | Description                                                        |

|----|-----|--------------------------------------------------------------------|

| 0  |     | The PID of the next expected OUT transaction will be zero: data 0. |

| 1  |     | The PID of the next expected OUR transaction will be one: data 1.  |

### 34.8.3.5 Device EndPoint Interrupt Flag n

| Name:     | EPINTFLAGn                       |

|-----------|----------------------------------|

| Offset:   | 0x107 + (n x 0x20) [ID-0000306e] |

| Reset:    | 0x00                             |

| Property: | -                                |

| Bit    | 7 | 6 | 5     | 4     | 3 | 2      | 1 | 0     |   |

|--------|---|---|-------|-------|---|--------|---|-------|---|

|        |   |   | STALL | RXSTP |   | TRFAIL |   | TRCPT | 1 |

| Access |   |   | R/W   | R/W   |   | R/W    |   | R/W   |   |

| Reset  |   |   | 2     | 0     |   | 2      |   | 2     |   |

### Bit 5 – STALL: Transmit Stall x Interrupt Flag

This flag is cleared by writing a one to the flag.

This flag is set when a Transmit Stall occurs and will generate an interrupt if EPINTENCLR/SET.STALL is one.

EPINTFLAG.STALL is set for a single bank OUT endpoint or double bank IN/OUT endpoint when current bank is "0".

Writing a zero to this bit has no effect.

Writing a one to this bit clears the STALL Interrupt Flag.

### Bit 4 – RXSTP: Received Setup Interrupt Flag

This flag is cleared by writing a one to the flag.

This flag is set when a Received Setup occurs and will generate an interrupt if EPINTENCLR/SET.RXSTP is one.

Writing a zero to this bit has no effect.

Writing a one to this bit clears the RXSTP Interrupt Flag.

### Bit 2 – TRFAIL: Transfer Fail x Interrupt Flag

This flag is cleared by writing a one to the flag.

© 2017 Microchip Technology Inc.

| Bit    | 7 | 6 | 5     | 4     | 3    | 2      | 1 | 0     |

|--------|---|---|-------|-------|------|--------|---|-------|

|        |   |   | STALL | TXSTP | PERR | TRFAIL |   | TRCPT |

| Access |   |   | R/W   | R/W   | R/W  | R/W    |   | R/W   |

| Reset  |   |   | 0     | 0     | 0    | 0      |   | 2     |

### Bit 5 – STALL: Stall Interrupt Enable

Writing a zero to this bit has no effect.

Writing a one to this bit will enable the Stall interrupt.

| Value | Description                      |

|-------|----------------------------------|

| 0     | The Stall interrupt is disabled. |

| 1     | The Stall interrupt is enabled.  |

### Bit 4 – TXSTP: Transmitted Setup Interrupt Enable

Writing a zero to this bit has no effect.

Writing a one to this bit will enable the Transmitted Setup interrupt.

| Value | Description                                  |

|-------|----------------------------------------------|

| 0     | The Transmitted Setup interrupt is disabled. |

| 1     | The Transmitted Setup interrupt is enabled.  |

### Bit 3 – PERR: Pipe Error Interrupt Enable

Writing a zero to this bit has no effect.

Writing a one to this bit will enable the Pipe Error interrupt.

| Value | Description                           |

|-------|---------------------------------------|

| 0     | The Pipe Error interrupt is disabled. |

| 1     | The Pipe Error interrupt is enabled.  |

### Bit 2 – TRFAIL: Transfer Fail Interrupt Enable

Writing a zero to this bit has no effect.

Writing a one to this bit will enable the Transfer Fail interrupt.

| Value | Description                              |

|-------|------------------------------------------|

| 0     | The Transfer Fail interrupt is disabled. |

| 1     | The Transfer Fail interrupt is enabled.  |

### Bit 0 – TRCPT: Transfer Complete x interrupt Enable

Writing a zero to this bit has no effect.

Writing a one to this bit will enable the Transfer Complete interrupt Enable bit x.

0.2.7 Host Registers - Pipe RAM

| Value | Description                                    |

|-------|------------------------------------------------|

| 0     | The Transfer Complete x interrupt is disabled. |

| 1     | The Transfer Complete x interrupt is enabled.  |

| Bit    | 15  | 14   | 13          | 12  | 11          | 10  | 9   | 8   |  |  |  |

|--------|-----|------|-------------|-----|-------------|-----|-----|-----|--|--|--|

|        |     | PERM | AX[3:0]     |     | PEPNUM[3:0] |     |     |     |  |  |  |

| Access | R/W | R/W  | R/W         | R/W | R/W         | R/W | R/W | R/W |  |  |  |

| Reset  | 0   | 0    | 0           | х   | 0           | 0   | 0   | x   |  |  |  |

|        |     |      |             |     |             |     |     |     |  |  |  |

| Bit    | 7   | 6    | 5           | 4   | 3           | 2   | 1   | 0   |  |  |  |

|        |     |      | PDADDR[6:0] |     |             |     |     |     |  |  |  |

| Access |     | R/W  | R/W         | R/W | R/W         | R/W | R/W | R/W |  |  |  |

| Reset  |     | 0    | 0           | 0   | 0           | 0   | 0   | x   |  |  |  |

### Bits 15:12 – PERMAX[3:0]: Pipe Error Max Number

These bits define the maximum number of error for this Pipe before freezing the pipe automatically.

#### Bits 11:8 – PEPNUM[3:0]: Pipe EndPoint Number

These bits define the number of endpoint for this Pipe.

### Bits 6:0 – PDADDR[6:0]: Pipe Device Address

These bits define the Device Address for this pipe.

### 34.8.7.7 Host Status Pipe

Name: STATUS\_PIPE

Offset: 0x0E & 0x1E [ID-0000306e]

Reset: 0xxxxxxxx

Property: PAC Write-Protection, Write-Synchronized, Read-Synchronized

| Bit    | 15  | 14         | 13  | 12      | 11     | 10    | 9       | 8      |

|--------|-----|------------|-----|---------|--------|-------|---------|--------|

|        |     |            |     |         |        |       |         |        |

| Access |     |            |     |         |        |       |         |        |

| Reset  |     |            |     |         |        |       |         |        |

|        |     |            |     |         |        |       |         |        |

| Bit    | 7   | 6          | 5   | 4       | 3      | 2     | 1       | 0      |

|        |     | ERCNT[2:0] |     | CRC16ER | TOUTER | PIDER | DAPIDER | DTGLER |

| Access | R/W | R/W        | R/W | R/W     | R/W    | R/W   | R/W     | R/W    |

| Reset  | 0   | 0          | х   | x       | х      | х     | х       | x      |

#### Bits 7:5 – ERCNT[2:0]: Pipe Error Counter

These bits define the number of errors detected on the pipe.

### Bit 4 – CRC16ER: CRC16 ERROR

This bit defines the CRC16 Error Status.

This bit is set when a CRC 16 error has been detected during a IN transactions.

| Value | Description                       |

|-------|-----------------------------------|

| 0     | No CRC 16 Error detected.         |

| 1     | A CRC 16 error has been detected. |

### Bit 3 – TOUTER: TIME OUT ERROR

This bit defines the Time Out Error Status.

This bit is set when a Time Out error has been detected during a USB transaction.

### Bit 0 – ENABLE: Enable

Writing a zero to this bit disables comparator n. Writing a one to this bit enables comparator n.

Due to synchronization, there is delay from updating the register until the comparator is enabled/disabled. The value written to COMPCTRLn.ENABLE will read back immediately after being written. SYNCBUSY.COMPCTRLn is set. SYNCBUSY.COMPCTRLn is cleared when the peripheral is enabled/ disabled.

Writing a one to COMPCTRLn.ENABLE will prevent further changes to the other bits in COMPCTRLn. These bits remain protected until COMPCTRLn.ENABLE is written to zero and the write is synchronized.

### 36.8.12 Scaler n

Name:SCALEROffset:0x20 + n\*0x01 [n=0..1]Reset:0x00Property:PAC Write-Protection

| Bit    | 7 | 6 | 5   | 4   | 3    | 2          | 1   | 0   |  |  |  |  |

|--------|---|---|-----|-----|------|------------|-----|-----|--|--|--|--|

|        |   |   |     |     | VALU | VALUE[5:0] |     |     |  |  |  |  |

| Access |   |   | R/W | R/W | R/W  | R/W        | R/W | R/W |  |  |  |  |

| Reset  |   |   | 0   | 0   | 0    | 0          | 0   | 0   |  |  |  |  |

### Bits 5:0 - VALUE[5:0]: Scaler Value

These bits define the scaling factor for channel n of the  $V_{DD}$  voltage scaler. The output voltage,  $V_{SCALE}$ , is:

$$V_{\text{SCALE}} = \frac{V_{\text{DD}} \cdot (\text{VALUE}+1)}{64}$$

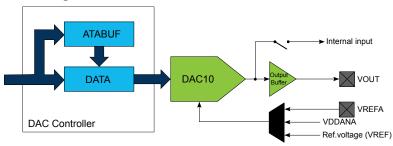

# 37. DAC – Digital-to-Analog Converter

### 37.1 Overview

The Digital-to-Analog Converter (DAC) converts a digital value to a voltage. The DAC has one channel with 10-bit resolution, and it is capable of converting up to 350,000 samples per second (350ksps).

### 37.2 Features

- DAC with 10-bit resolution

- Up to 350ksps conversion rate

- Multiple trigger sources

- High-drive capabilities

- Output can be used as input to the Analog Comparator (AC)

- DMA support

### 37.3 Block Diagram

Figure 37-1. DAC Block Diagram

### 37.4 Signal Description

| Signal Name | Туре          | Description        |

|-------------|---------------|--------------------|

| VOUT        | Analog output | DAC output         |

| VREFA       | Analog input  | External reference |

### **Related Links**

I/O Multiplexing and Considerations

### 37.5 **Product Dependencies**

In order to use this peripheral, other parts of the system must be configured correctly, as described below.

### 37.5.1 I/O Lines

Using the DAC Controller's I/O lines requires the I/O pins to be configured using the port configuration (PORT).

| Name                | Description           | Mode                      | VDD=1.8V |      |      | VDD=3.3V |      |      | Units |

|---------------------|-----------------------|---------------------------|----------|------|------|----------|------|------|-------|

|                     |                       |                           | Min.     | Тур. | Max. | Min.     | Тур. | Max. |       |

| t <sub>S_SDOH</sub> | Data output hold time | Slave transmitter         | 29.1     |      |      | 18.9     |      |      | ns    |

| t <sub>PDM2LS</sub> | Data input setup time | Master mode PDM2<br>Left  | 35.5     |      |      | 25.3     |      |      | ns    |

| t <sub>PDM2LH</sub> | Data input hold time  | Master mode PDM2<br>Left  | -8.2     |      |      | -8.2     |      |      | ns    |

| t <sub>PDM2RS</sub> | Data input setup time | Master mode PDM2<br>Right | 30.6     |      |      | 21.1     |      |      | ns    |

| t <sub>PDM2RH</sub> | Data input hold time  | Master mode PDM2<br>Right | -7       |      |      | -7       |      |      | ns    |

- 1. All timing characteristics given for 15pF capacitive load.

- 2. These values are based on simulations and not covered by test limits in production.

- 3. See I/O Pin Characteristics.