Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

-XF

| Product Status             | Active                                                                     |

|----------------------------|----------------------------------------------------------------------------|

| Core Processor             | ARM® Cortex®-M0+                                                           |

| Core Size                  | 32-Bit Single-Core                                                         |

| Speed                      | 48MHz                                                                      |

| Connectivity               | I <sup>2</sup> C, SCI, SPI, UART/USART, USB                                |

| Peripherals                | Brown-out Detect/Reset, DMA, I <sup>2</sup> S, POR, PWM, WDT               |

| Number of I/O              | 38                                                                         |

| Program Memory Size        | 64KB (64K x 8)                                                             |

| Program Memory Type        | FLASH                                                                      |

| EEPROM Size                | -                                                                          |

| RAM Size                   | 8K x 8                                                                     |

| Voltage - Supply (Vcc/Vdd) | 2.7V ~ 3.63V                                                               |

| Data Converters            | A/D 14x12b; D/A 1x10b                                                      |

| Oscillator Type            | Internal                                                                   |

| Operating Temperature      | -40°C ~ 105°C (TA)                                                         |

| Mounting Type              | Surface Mount                                                              |

| Package / Case             | 48-VFQFN Exposed Pad                                                       |

| Supplier Device Package    | 48-QFN (7x7)                                                               |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/atsamda1g16b-mbt |

|                            |                                                                            |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

# **Table of Contents**

| Intr | oduction                                                                                                                                                                                                                   | 1              |

|------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------|

| Fea  | atures                                                                                                                                                                                                                     | 1              |

| 1.   | Description                                                                                                                                                                                                                | 11             |

| 2.   | Configuration Summary                                                                                                                                                                                                      | 12             |

| 3.   | Ordering Information.         3.1. Device Variant A.         3.2. Device Variant B.         3.3. Device Identification.                                                                                                    | 14<br>15       |

| 4.   | Block Diagram                                                                                                                                                                                                              | 18             |

| 5.   | Pinout                                                                                                                                                                                                                     | 20<br>21       |

| 6.   | Signal Descriptions List                                                                                                                                                                                                   | 23             |

| 7.   | <ul><li>I/O Multiplexing and Considerations.</li><li>7.1. Multiplexed Signals.</li><li>7.2. Other Functions.</li></ul>                                                                                                     | 25             |

| 8.   | Power Supply and Start-Up Considerations.         8.1.       Power Domain Overview.         8.2.       Power Supply Considerations.         8.3.       Power-Up.         8.4.       Power-On Reset and Brown-Out Detector. | 30<br>30<br>32 |

| 9.   | Product Mapping                                                                                                                                                                                                            | 34             |

| 10.  | Automotive Quality Grade                                                                                                                                                                                                   | 35             |

| 11.  | Data Retention                                                                                                                                                                                                             | 36             |

| 12.  | Memories.         12.1. Embedded Memories.         12.2. Physical Memory Map.         12.3. NVM Calibration and Auxiliary Space.                                                                                           | 37<br>37       |

| 13.  | Processor And Architecture.         13.1. Cortex M0+ Processor.         13.2. Nested Vector Interrupt Controller.         13.3. Micro Trace Buffer.                                                                        | 41<br>42       |

| 23.5.                                                                                                                                                                     | Product Dependencies                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |                                                                                         |

|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------|

|                                                                                                                                                                           | Functional Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |                                                                                         |

| 23.7.                                                                                                                                                                     | Register Summary                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 317                                                                                     |

| 23.8.                                                                                                                                                                     | Register Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | 318                                                                                     |

|                                                                                                                                                                           |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |                                                                                         |

| 24. NVN                                                                                                                                                                   | ICTRL – Non-Volatile Memory Controller                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 327                                                                                     |

| 24.1.                                                                                                                                                                     | Overview                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | 327                                                                                     |

| 24.2.                                                                                                                                                                     | Features                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | 327                                                                                     |

| 24.3.                                                                                                                                                                     | Block Diagram                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |                                                                                         |

| 24.4.                                                                                                                                                                     | Signal Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | 328                                                                                     |

| 24.5.                                                                                                                                                                     | Product Dependencies                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | 328                                                                                     |

| 24.6.                                                                                                                                                                     | Functional Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |                                                                                         |

|                                                                                                                                                                           | Register Summary                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |                                                                                         |

| 24.8.                                                                                                                                                                     | Register Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |                                                                                         |

| 25. POF                                                                                                                                                                   | RT - I/O Pin Controller                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |                                                                                         |

|                                                                                                                                                                           | Overview                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |                                                                                         |

|                                                                                                                                                                           | Features                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |                                                                                         |

|                                                                                                                                                                           | Block Diagram                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |                                                                                         |

|                                                                                                                                                                           | Signal Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |                                                                                         |

|                                                                                                                                                                           | Product Dependencies                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |                                                                                         |

|                                                                                                                                                                           | Functional Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |                                                                                         |

|                                                                                                                                                                           | Register Summary                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |                                                                                         |

|                                                                                                                                                                           | Register Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |                                                                                         |

|                                                                                                                                                                           |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |                                                                                         |

| 26. EVS                                                                                                                                                                   | SYS – Event System                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | 372                                                                                     |

|                                                                                                                                                                           | SYS – Event System                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |                                                                                         |

| 26.1.                                                                                                                                                                     | Overview                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |                                                                                         |

| 26.1.<br>26.2.                                                                                                                                                            | Overview<br>Features                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |                                                                                         |

| 26.1.<br>26.2.<br>26.3.                                                                                                                                                   | Overview<br>Features<br>Block Diagram                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |                                                                                         |

| 26.1.<br>26.2.<br>26.3.<br>26.4.                                                                                                                                          | Overview.<br>Features<br>Block Diagram.<br>Signal Description.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |                                                                                         |

| 26.1.<br>26.2.<br>26.3.<br>26.4.<br>26.5.                                                                                                                                 | Overview<br>Features<br>Block Diagram<br>Signal Description<br>Product Dependencies                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |                                                                                         |

| 26.1.<br>26.2.<br>26.3.<br>26.4.<br>26.5.<br>26.5.                                                                                                                        | Overview<br>Features<br>Block Diagram<br>Signal Description<br>Product Dependencies<br>Functional Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | 372<br>372<br>372<br>373<br>373<br>373<br>373                                           |

| 26.1.<br>26.2.<br>26.3.<br>26.4.<br>26.5.<br>26.6.<br>26.7.                                                                                                               | Overview<br>Features<br>Block Diagram<br>Signal Description<br>Product Dependencies                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |                                                                                         |

| 26.1.<br>26.2.<br>26.3.<br>26.4.<br>26.5.<br>26.6.<br>26.6.<br>26.7.<br>26.8.                                                                                             | Overview<br>Features<br>Block Diagram<br>Signal Description<br>Product Dependencies<br>Functional Description<br>Register Summary<br>Register Description.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |                                                                                         |

| 26.1.<br>26.2.<br>26.3.<br>26.4.<br>26.5.<br>26.6.<br>26.7.<br>26.8.<br>27. SEF                                                                                           | Overview<br>Features<br>Block Diagram<br>Signal Description<br>Product Dependencies<br>Functional Description<br>Register Summary<br>Register Description<br>Register Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 372<br>372<br>372<br>373<br>373<br>373<br>374<br>374<br>379<br>379<br>379               |

| 26.1.<br>26.2.<br>26.3.<br>26.4.<br>26.5.<br>26.6.<br>26.7.<br>26.8.<br>27. SEF<br>27.1.                                                                                  | Overview<br>Features<br>Block Diagram<br>Signal Description<br>Product Dependencies<br>Functional Description<br>Register Summary<br>Register Description<br>Register Description<br>Register Description<br>Register Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |                                                                                         |

| 26.1.<br>26.2.<br>26.3.<br>26.4.<br>26.5.<br>26.6.<br>26.7.<br>26.8.<br>27. SEF<br>27.1.<br>27.1.<br>27.2.                                                                | Overview<br>Features<br>Block Diagram<br>Signal Description<br>Product Dependencies.<br>Functional Description<br>Register Summary<br>Register Description.<br>Register Description.<br>Register Description.<br>Register Description.<br>Register Description.<br>Register Summary<br>Register Description.<br>Register Description.<br>Register Description.<br>Register Description.<br>Register Description.<br>Register Description.<br>Register Description.<br>Register Description.<br>Register Description.<br>Register Description.                                                                                                                                                                                                 | 372<br>372<br>372<br>373<br>373<br>373<br>374<br>379<br>379<br>379<br>379<br>391<br>391 |

| 26.1.<br>26.2.<br>26.3.<br>26.4.<br>26.5.<br>26.6.<br>26.7.<br>26.8.<br>27. SEF<br>27.1.<br>27.2.<br>27.3.                                                                | Overview.         Features.         Block Diagram.         Signal Description.         Product Dependencies.         Functional Description.         Register Summary.         Register Description.         RCOM – Serial Communication Interface.         Overview.         Features.         Block Diagram.                                                                                                                                                                                                                                                                                                                                                                                                                                |                                                                                         |

| 26.1.<br>26.2.<br>26.3.<br>26.4.<br>26.5.<br>26.6.<br>26.7.<br>26.8.<br>27. SEF<br>27.1.<br>27.2.<br>27.3.<br>27.4.                                                       | Overview.         Features.         Block Diagram.         Signal Description.         Product Dependencies.         Functional Description.         Register Summary.         Register Description.         RCOM – Serial Communication Interface.         Overview.         Features.         Block Diagram.         Signal Description.                                                                                                                                                                                                                                                                                                                                                                                                    |                                                                                         |

| 26.1.<br>26.2.<br>26.3.<br>26.4.<br>26.5.<br>26.6.<br>26.7.<br>26.8.<br>27. SEF<br>27.1.<br>27.2.<br>27.3.<br>27.4.<br>27.5.                                              | Overview.         Features.         Block Diagram.         Signal Description.         Product Dependencies.         Functional Description.         Register Summary.         Register Description.         RCOM – Serial Communication Interface.         Overview.         Features.         Block Diagram.         Signal Description.         Product Dependencies.                                                                                                                                                                                                                                                                                                                                                                      |                                                                                         |

| 26.1.<br>26.2.<br>26.3.<br>26.4.<br>26.5.<br>26.6.<br>26.7.<br>26.8.<br><b>27. SEF</b><br>27.1.<br>27.2.<br>27.3.<br>27.4.<br>27.5.<br>27.6.                              | Overview.         Features.         Block Diagram.         Signal Description.         Product Dependencies.         Functional Description.         Register Summary.         Register Description.         RCOM – Serial Communication Interface.         Overview.         Features.         Block Diagram.         Signal Description.         Product Dependencies.         Functional Description.                                                                                                                                                                                                                                                                                                                                      |                                                                                         |

| 26.1.<br>26.2.<br>26.3.<br>26.4.<br>26.5.<br>26.6.<br>26.7.<br>26.8.<br>27. SEF<br>27.1.<br>27.2.<br>27.3.<br>27.4.<br>27.5.<br>27.6.<br>28. SEF                          | Overview                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |                                                                                         |

| 26.1.<br>26.2.<br>26.3.<br>26.4.<br>26.5.<br>26.6.<br>26.7.<br>26.8.<br>27. SEF<br>27.1.<br>27.3.<br>27.4.<br>27.3.<br>27.4.<br>27.5.<br>27.6.<br>28. SEF<br>and          | Overview.         Features.         Block Diagram.         Signal Description.         Product Dependencies.         Functional Description.         Register Summary.         Register Description.         RCOM – Serial Communication Interface.         Overview.         Features.         Block Diagram.         Signal Description.         Product Dependencies.         Functional Communication Interface.         Overview.         Features.         Block Diagram.         Signal Description.         Product Dependencies.         Functional Description.         Product Dependencies.         Functional Description.         RCOM USART – SERCOM Universal Synchronous and Asynchronous         Transmitter.               |                                                                                         |

| 26.1.<br>26.2.<br>26.3.<br>26.4.<br>26.5.<br>26.6.<br>26.7.<br>26.8.<br>27. SEF<br>27.1.<br>27.2.<br>27.3.<br>27.4.<br>27.5.<br>27.6.<br>28. SEF<br>and<br>28.1.          | Overview.         Features.         Block Diagram.         Signal Description.         Product Dependencies.         Functional Description.         Register Summary.         Register Description.         Register Description.         Register Description.         Register Description.         Register Description.         Redister Description.         Register Description.         Redister Description.         Preduct Dependencies.         Block Diagram.         Signal Description.         Product Dependencies.         Functional Description.         Product Dependencies.         Functional Description.         RCOM USART – SERCOM Universal Synchronous and Asynchronous         Transmitter.         Overview. |                                                                                         |

| 26.1.<br>26.2.<br>26.3.<br>26.4.<br>26.5.<br>26.6.<br>26.7.<br>26.8.<br>27. SEF<br>27.1.<br>27.2.<br>27.3.<br>27.4.<br>27.5.<br>27.6.<br>28. SEF<br>and<br>28.1.<br>28.2. | Overview.         Features.         Block Diagram.         Signal Description.         Product Dependencies.         Functional Description.         Register Summary.         Register Description.         RCOM – Serial Communication Interface.         Overview.         Features.         Block Diagram.         Signal Description.         Product Dependencies.         Functional Communication Interface.         Overview.         Features.         Block Diagram.         Signal Description.         Product Dependencies.         Functional Description.         Product Dependencies.         Functional Description.         RCOM USART – SERCOM Universal Synchronous and Asynchronous         Transmitter.               |                                                                                         |

Name:

WPCLR

Offset:

0x00 [ID-00000a18]

Reset:

0x00800000

Property:

| Bit    | 31  | 30  | 29  | 28  | 27  | 26   | 25    | 24   |

|--------|-----|-----|-----|-----|-----|------|-------|------|

|        |     |     |     |     |     |      |       |      |

| Access |     |     |     |     |     |      |       |      |

| Reset  |     |     |     |     |     |      |       |      |

|        |     |     |     |     |     |      |       |      |

| Bit    | 23  | 22  | 21  | 20  | 19  | 18   | 17    | 16   |

|        |     |     |     | 12S | PTC | DAC  | AC    | ADC  |

| Access |     |     |     | R/W | R/W | R/W  | R/W   | R/W  |

| Reset  |     |     |     | 0   | 0   | 0    | 0     | 0    |

|        |     |     |     |     |     |      |       |      |

| Bit    | 15  | 14  | 13  | 12  | 11  | 10   | 9     | 8    |

|        | TC7 | TC4 | TC5 | TC4 | TC3 | TCC2 | TCC1  | TCC0 |

| Access | R/W | R/W | R/W | R/W | R/W | R/W  | R/W   | R/W  |

| Reset  | 0   | 0   | 0   | 0   | 0   | 0    | 0     | 0    |

|        |     |     |     |     |     |      |       |      |

| Bit    | 7   | 6   | 5   | 4   | 3   | 2    | 1     | 0    |

|        |     |     |     |     |     |      | EVSYS |      |

| Access |     |     |     |     |     |      | R/W   |      |

| Reset  |     |     |     |     |     |      | 0     |      |

## Bit 20 – I2S

Writing a zero to these bits has no effect.

Writing a one to these bits will clear the Write Protect bit for the corresponding peripherals.

| Value | Description                   |

|-------|-------------------------------|

| 0     | Write-protection is disabled. |

| 1     | Write-protection is enabled.  |

## Bit 19 – PTC

Writing a zero to these bits has no effect.

Writing a one to these bits will clear the Write Protect bit for the corresponding peripherals.

| Value | Description                   |

|-------|-------------------------------|

| 0     | Write-protection is disabled. |

| 1     | Write-protection is enabled.  |

## Bit 18 – DAC:

Writing a zero to these bits has no effect.

Writing a one to these bits will clear the Write Protect bit for the corresponding peripherals.

| Value | Description                   |

|-------|-------------------------------|

| 0     | Write-protection is disabled. |

| 1     | Write-protection is enabled.  |

#### Table 18-4. Sleep Mode Overview

| Sleep   |       | AHB   | APB   | Oscillators  |            |                  |                  | Main  | Regulator | RAM       |

|---------|-------|-------|-------|--------------|------------|------------------|------------------|-------|-----------|-----------|

| Mode    | Clock | Clock | Clock | ONDEMAND = 0 |            | ONDEMAND = 1     |                  | Clock | Mode      | Mode      |

|         |       |       |       | RUNSTDBY=0   | RUNSTDBY=1 | RUNSTDBY=0       | RUNSTDBY=1       |       |           |           |

| Idle 0  | Stop  | Run   | Run   | Run          | Run        | Run if requested | Run if requested | Run   | Normal    | Normal    |

| Idle 1  | Stop  | Stop  | Run   | Run          | Run        | Run if requested | Run if requested | Run   | Normal    | Normal    |

| Idle 2  | Stop  | Stop  | Stop  | Run          | Run        | Run if requested | Run if requested | Run   | Normal    | Normal    |

| Standby | Stop  | Stop  | Stop  | Stop         | Run        | Stop             | Run if requested | Stop  | Low power | Low power |

#### IDLE Mode

The IDLE modes allow power optimization with the fastest wake-up time.

The CPU is stopped. To further reduce power consumption, the user can disable the clocking of modules and clock sources by configuring the SLEEP.IDLE bit group. The module will be halted regardless of the bit settings of the mask registers in the Power Manager (PM.AHBMASK, PM.APBxMASK).

Regulator operates in normal mode.

- Entering IDLE mode: The IDLE mode is entered by executing the WFI instruction. Additionally, if

the SLEEPONEXIT bit in the ARM Cortex System Control register (SCR) is set, the IDLE mode will

also be entered when the CPU exits the lowest priority ISR. This mechanism can be useful for

applications that only require the processor to run when an interrupt occurs. Before entering the

IDLE mode, the user must configure the IDLE mode configuration bit group and must write a zero

to the SCR.SLEEPDEEP bit.

- Exiting IDLE mode: The processor wakes the system up when it detects the occurrence of any interrupt that is not masked in the NVIC Controller with sufficient priority to cause exception entry. The system goes back to the ACTIVE mode. The CPU and affected modules are restarted.

#### STANDBY Mode

The STANDBY mode allows achieving very low power consumption.

In this mode, all clocks are stopped except those which are kept running if requested by a running module or have the ONDEMAND bit set to zero. For example, the RTC can operate in STANDBY mode. In this case, its Generic Clock clock source will also be enabled.

The regulator and the RAM operate in low-power mode.

A SLEEPONEXIT feature is also available.

- Entering STANDBY mode: This mode is entered by executing the WFI instruction with the SCR.SLEEPDEEP bit of the CPU is written to 1.

- Exiting STANDBY mode: Any peripheral able to generate an asynchronous interrupt can wake up the system. For example, a module running on a Generic clock can trigger an interrupt. When the enabled asynchronous wake-up event occurs and the system is woken up, the device will either execute the interrupt service routine or continue the normal program execution according to the Priority Mask Register (PRIMASK) configuration of the CPU.

#### 18.6.3 SleepWalking

SleepWalking is the capability for a device to temporarily wak-eup clocks for peripheral to perform a task without waking-up the CPU in STANDBY sleep mode. At the end of the sleepwalking task, the device can either be waken-up by an interrupt (from a peripheral involved in SleepWalking) or enter again into STANDBY sleep mode.

| Value | Description                                                                                    |

|-------|------------------------------------------------------------------------------------------------|

| 0     | The oscillator is always on, if enabled.                                                       |

| 1     | The oscillator is enabled when a peripheral is requesting the oscillator to be used as a clock |

|       | source. The oscillator is disabled if no peripheral is requesting the clock source.            |

#### Bit 6 – RUNSTDBY: Run in Standby

This bit controls how the XOSC behaves during standby sleep mode:

| Value | Description                                                                                                                                                                                                                                        |

|-------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 0     | The oscillator is disabled in standby sleep mode.                                                                                                                                                                                                  |

| 1     | The oscillator is not stopped in standby sleep mode. If XOSC.ONDEMAND is one, the clock source will be running when a peripheral is requesting the clock. If XOSC.ONDEMAND is zero, the clock source will always be running in standby sleep mode. |

#### Bit 2 – XTALEN: Crystal Oscillator Enable

This bit controls the connections between the I/O pads and the external clock or crystal oscillator:

| Value | Description                                                               |

|-------|---------------------------------------------------------------------------|

| 0     | External clock connected on XIN. XOUT can be used as general-purpose I/O. |

| 1     | Crystal connected to XIN/XOUT.                                            |

#### Bit 1 – ENABLE: Oscillator Enable

|   | /alue | Description                 |

|---|-------|-----------------------------|

| ( | )     | The oscillator is disabled. |

| • | 1     | The oscillator is enabled.  |

#### 19.8.6 32kHz External Crystal Oscillator (XOSC32K) Control

| Name:            | XOSC32K            |

|------------------|--------------------|

| Offset:          | 0x14 [ID-00003d5d] |

| Reset:           | 0x0080             |

| <b>Property:</b> | Write-Protected    |

| Bit    | 15       | 14       | 13     | 12      | 11    | 10     | 9            | 8   |

|--------|----------|----------|--------|---------|-------|--------|--------------|-----|

|        |          |          |        | WRTLOCK |       |        | STARTUP[2:0] |     |

| Access |          |          |        | R/W     |       | R/W    | R/W          | R/W |

| Reset  |          |          |        | 0       |       | 0      | 0            | 0   |

|        |          |          |        |         |       |        |              |     |

| Bit    | 7        | 6        | 5      | 4       | 3     | 2      | 1            | 0   |

|        | ONDEMAND | RUNSTDBY | AAMPEN |         | EN32K | XTALEN | ENABLE       |     |

| Access | R/W      | R/W      | R/W    |         | R/W   | R/W    | R/W          |     |

| Reset  | 1        | 0        | 0      |         | 0     | 0      | 0            |     |

## Bit 12 – WRTLOCK: Write Lock

This bit locks the XOSC32K register for future writes to fix the XOSC32K configuration.

| Value | Description                              |

|-------|------------------------------------------|

| 0     | The XOSC32K configuration is not locked. |

| 1     | The XOSC32K configuration is locked.     |

#### Bits 10:8 - STARTUP[2:0]: Oscillator Start-Up Time

These bits select the start-up time for the oscillator.

The OSCULP32K oscillator is used to clock the start-up counter.

Table 19-6. Start-Up Time for 32kHz External Crystal Oscillator

| STARTUP[2:0] | Number of OSCULP32K<br>Clock Cycles | Number of XOSC32K<br>Clock Cycles | Approximate Equivalent<br>Time<br>(OSCULP = 32kHz) <sup>(1)(2)(3)</sup> |

|--------------|-------------------------------------|-----------------------------------|-------------------------------------------------------------------------|

| 0x0          | 1                                   | 3                                 | 122µs                                                                   |

| 0x1          | 32                                  | 3                                 | 1068µs                                                                  |

| 0x2          | 2048                                | 3                                 | 62592µs                                                                 |

| 0x3          | 4096                                | 3                                 | 125092µs                                                                |

| 0x4          | 16384                               | 3                                 | 500092µs                                                                |

| 0x5          | 32768                               | 3                                 | 1000092µs                                                               |

| 0x6          | 65536                               | 3                                 | 2000092µs                                                               |

| 0x7          | 131072                              | 3                                 | 4000092µs                                                               |

Notes: 1. Number of cycles for the start-up counter.

2. Number of cycles for the synchronization delay, before PCLKSR.XOSC32KRDY is set.

3. Start-up time is n OSCULP32K cycles + 3 XOSC32K cycles.

## Bit 7 – ONDEMAND: On Demand Control

The On Demand operation mode allows an oscillator to be enabled or disabled depending on peripheral clock requests.

In On Demand operation mode, i.e., if the ONDEMAND bit has been previously written to one, the oscillator will only be running when requested by a peripheral. If there is no peripheral requesting the oscillator s clock source, the oscillator will be in a disabled state.

If On Demand is disabled the oscillator will always be running when enabled.

In standby sleep mode, the On Demand operation is still active if the XOSC32K.RUNSTDBY bit is one. If XOSC32K.RUNSTDBY is zero, the oscillator is disabled.

| Value | Description                                                                                                                                                                        |

|-------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 0     | The oscillator is always on, if enabled.                                                                                                                                           |

| 1     | The oscillator is enabled when a peripheral is requesting the oscillator to be used as a clock source. The oscillator is disabled if no peripheral is requesting the clock source. |

## Bit 6 – RUNSTDBY: Run in Standby

This bit controls how the XOSC32K behaves during standby sleep mode:

| Value | Description                                                                                                                                                     |

|-------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 0     | The oscillator is disabled in standby sleep mode.                                                                                                               |

| 1     | The oscillator is not stopped in standby sleep mode. If XOSC32K.ONDEMAND is one, the clock source will be running when a peripheral is requesting the clock. If |

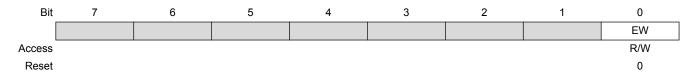

| Bit    | 7 | 6 | 5 | 4 | 3 | 2 | 1 | 0   |

|--------|---|---|---|---|---|---|---|-----|

|        |   |   |   |   |   |   |   | EW  |

| Access |   |   |   |   |   |   |   | R/W |

| Reset  |   |   |   |   |   |   |   | 0   |

#### Bit 0 – EW: Early Warning Interrupt Enable

Writing a zero to this bit has no effect.

Writing a one to this bit disables the Early Warning interrupt.

| Value | Description                              |

|-------|------------------------------------------|

| 0     | The Early Warning interrupt is disabled. |

| 1     | The Early Warning interrupt is enabled.  |

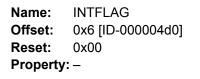

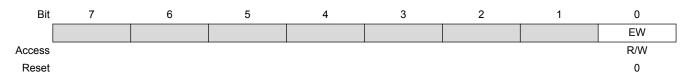

## 20.8.5 Interrupt Enable Set

Name:INTENSETOffset:0x5 [ID-000004d0]Reset:0x00Property:Write-Protected

#### **Bit 0 – EW: Early Warning Interrupt Enable**

Writing a zero to this bit has no effect.

Writing a one to this bit enables the Early Warning interrupt.

| Value | Description                              |

|-------|------------------------------------------|

| 0     | The Early Warning interrupt is disabled. |

| 1     | The Early Warning interrupt is enabled.  |

#### 20.8.6 Interrupt Flag Status and Clear

## Bit 0 – EW: Early Warning

This flag is set when an Early Warning interrupt occurs, as defined by the EWOFFSET bit group in EWCTRL.

- 2. Clock representation must be selected by writing the Clock Representation bit in the Control register (CTRL.CLKREP)

- 3. Prescaler value must be selected by writing the Prescaler bit group in the Control register (CTRL.PRESCALER)

The RTC prescaler divides the source clock for the RTC counter.

**Note:** In Clock/Calendar mode, the prescaler must be configured to provide a 1Hz clock to the counter for correct operation.

The frequency of the RTC clock (CLK\_RTC\_CNT) is given by the following formula:

$f_{\text{CLK\_RTC\_CNT}} = \frac{f_{\text{GCLK\_RTC}}}{2^{\text{PRESCALER}}}$

The frequency of the generic clock, GCLK\_RTC, is given by  $f_{GCLK_RTC}$ , and  $f_{CLK_RTC_CNT}$  is the frequency of the internal prescaled RTC clock, CLK\_RTC\_CNT.

## 21.6.2.2 Enabling, Disabling and Resetting

The RTC is enabled by setting the Enable bit in the Control register (CTRL.ENABLE=1). The RTC is disabled by writing CTRL.ENABLE=0.

The RTC is reset by setting the Software Reset bit in the Control register (CTRL.SWRST=1). All registers in the RTC, except DEBUG, will be reset to their initial state, and the RTC will be disabled. The RTC must be disabled before resetting it.

## 21.6.3 Operating Modes

The RTC counter supports three RTC operating modes: 32-bit Counter, 16-bit Counter and Clock/ Calendar. The operating mode is selected by writing to the Operating Mode bit group in the Control register (CTRL.MODE).

## 21.6.3.1 32-Bit Counter (Mode 0)

When the RTC Operating Mode bits in the Control register are zero (CTRL.MODE=00), the counter operates in 32-bit Counter mode. The block diagram of this mode is shown in Figure 21-1. When the RTC is enabled, the counter will increment on every 0-to-1 transition of CLK\_RTC\_CNT. The counter will increment until it reaches the top value of 0xFFFFFFF, and then wrap to 0x00000000. This sets the Overflow Interrupt flag in the Interrupt Flag Status and Clear register (INTFLAG.OVF).

The RTC counter value can be read from or written to the Counter Value register (COUNT) in 32-bit format.

The counter value is continuously compared with the 32-bit Compare register (COMP0). When a compare match occurs, the Compare 0interrupt flag in the Interrupt Flag Status and Clear register (INTFLAG.CMP0) is set on the next 0-to-1 transition of CLK\_RTC\_CNT.

If the Clear on Match bit in the Control register (CTRL.MATCHCLR) is '1', the counter is cleared on the next counter cycle when a compare match with COMP0 occurs. This allows the RTC to generate periodic interrupts or events with longer periods than are possible with the prescaler events. Note that when CTRL.MATCHCLR is '1', INTFLAG.CMP0 and INTFLAG.OVF will both be set simultaneously on a compare match with COMP0.

## 21.6.3.2 16-Bit Counter (Mode 1)

When the RTC Operating Mode bits in the Control register (CTRL.MODE) are 1, the counter operates in 16-bit Counter mode as shown in Figure 21-2. When the RTC is enabled, the counter will increment on every 0-to-1 transition of CLK\_RTC\_CNT. In 16-bit Counter mode, the 16-bit Period register (PER) holds the maximum value of the counter. The counter will increment until it reaches the PER value, and then

An AHB clock (CLK\_DMAC\_AHB) is required to clock the DMAC. This clock must be configured and enabled in the power manager before using the DMAC, and the default state of CLK\_DMAC\_AHB can be found in *Peripheral Clock Masking*.

This bus clock (CLK\_DMAC\_APB) is always synchronous to the module clock (CLK\_DMAC\_AHB), but can be divided by a prescaler and may run even when the module clock is turned off.

#### **Related Links**

Peripheral Clock Masking

#### 22.5.4 DMA

Not applicable.

#### 22.5.5 Interrupts

The interrupt request line is connected to the interrupt controller. Using the DMAC interrupt requires the interrupt controller to be configured first.

#### **Related Links**

Nested Vector Interrupt Controller

### 22.5.6 Events

The events are connected to the event system.

#### **Related Links**

EVSYS - Event System

#### 22.5.7 Debug Operation

When the CPU is halted in debug mode the DMAC will halt normal operation. The DMAC can be forced to continue operation during debugging. Refer to DBGCTRL for details.

#### 22.5.8 Register Access Protection

All registers with write-access can be write-protected optionally by the Peripheral Access Controller (PAC), except for the following registers:

- Interrupt Pending register (INTPEND)

- Channel ID register (CHID)

- Channel Interrupt Flag Status and Clear register (CHINTFLAG)

Optional write-protection by the Peripheral Access Controller (PAC) is denoted by the "PAC Write-Protection" property in each individual register description.

PAC write-protection does not apply to accesses through an external debugger.

## **Related Links**

PAC - Peripheral Access Controller

#### 22.5.9 Analog Connections

Not applicable.

## 22.6 Functional Description

## 22.6.1 Principle of Operation

The DMAC consists of a DMA module and a CRC module.

| Bit    | 31    | 30 | 29 | 28   | 27      | 26      | 25     | 24     |

|--------|-------|----|----|------|---------|---------|--------|--------|

|        |       |    |    | BTCN | T[15:8] |         |        |        |

| Access | R     | R  | R  | R    | R       | R       | R      | R      |

| Reset  | 0     | 0  | 0  | 0    | 0       | 0       | 0      | 0      |

|        |       |    |    |      |         |         |        |        |

| Bit    | 23    | 22 | 21 | 20   | 19      | 18      | 17     | 16     |

|        |       |    |    | BTCN | IT[7:0] |         |        |        |

| Access | R     | R  | R  | R    | R       | R       | R      | R      |

| Reset  | 0     | 0  | 0  | 0    | 0       | 0       | 0      | 0      |

|        |       |    |    |      |         |         |        |        |

| Bit    | 15    | 14 | 13 | 12   | 11      | 10      | 9      | 8      |

|        | ABUSY |    |    |      |         | ID[4:0] |        |        |

| Access | R     |    |    | R    | R       | R       | R      | R      |

| Reset  | 0     |    |    | 0    | 0       | 0       | 0      | 0      |

|        |       |    |    |      |         |         |        |        |

| Bit    | 7     | 6  | 5  | 4    | 3       | 2       | 1      | 0      |

|        |       |    |    |      | LVLEXx  | LVLEXx  | LVLEXx | LVLEXx |

| Access |       |    |    |      | R       | R       | R      | R      |

| Reset  |       |    |    |      | 0       | 0       | 0      | 0      |

#### Bits 31:16 – BTCNT[15:0]: Active Channel Block Transfer Count

These bits hold the 16-bit block transfer count of the ongoing transfer. This value is stored in the active channel and written back in the corresponding Write-Back channel memory location when the arbiter grants a new channel access. The value is valid only when the active channel active busy flag (ABUSY) is set.

#### Bit 15 – ABUSY: Active Channel Busy

This bit is cleared when the active transfer count is written back in the write-back memory section.

This bit is set when the next descriptor transfer count is read from the write-back memory section.

#### Bits 12:8 – ID[4:0]: Active Channel ID

These bits hold the channel index currently stored in the active channel registers. The value is updated each time the arbiter grants a new channel transfer access request.

#### Bits 3,2,1,0 – LVLEXx: Level x Channel Trigger Request Executing [x=3..0]

This bit is set when a level-x channel trigger request is executing or pending.

This bit is cleared when no request is pending or being executed.

#### 22.8.15 Descriptor Memory Section Base Address

Name:BASEADDROffset:0x34 [ID-00001ece]Reset:0x00000000Property:PAC Write-Protection, Enable-Protected

| Value | Description                      |

|-------|----------------------------------|

| 0     | Hardware SS control is disabled. |

| 1     | Hardware SS control is enabled.  |

#### Bit 9 – SSDE: Slave Select Low Detect Enable

This bit enables wake up when the slave select  $(\overline{SS})$  pin transitions from high to low.

| Value | Description                  |

|-------|------------------------------|

| 0     | SS low detector is disabled. |

| 1     | SS low detector is enabled.  |

#### Bit 6 – PLOADEN: Slave Data Preload Enable

Setting this bit will enable preloading of the slave shift register when there is no transfer in progress. If the SS line is high when DATA is written, it will be transferred immediately to the shift register.

#### Bits 2:0 – CHSIZE[2:0]: Character Size

| CHSIZE[2:0] | Name | Description |

|-------------|------|-------------|

| 0x0         | 8BIT | 8 bits      |

| 0x1         | 9BIT | 9 bits      |

| 0x2-0x7     | -    | Reserved    |

#### 29.8.3 Baud Rate

Name:BAUDOffset:0x0C [ID-00000e74]Reset:0x00Property:PAC Write-Protection, Enable-Protected

| Bit    | 7   | 6   | 5   | 4    | 3      | 2   | 1   | 0   |

|--------|-----|-----|-----|------|--------|-----|-----|-----|

|        |     |     |     | BAUI | D[7:0] |     |     |     |

| Access | R/W | R/W | R/W | R/W  | R/W    | R/W | R/W | R/W |

| Reset  | 0   | 0   | 0   | 0    | 0      | 0   | 0   | 0   |

#### Bits 7:0 – BAUD[7:0]: Baud Register

These bits control the clock generation, as described in the SERCOM Clock Generation – Baud-Rate Generator.

#### 29.8.4 Interrupt Enable Clear

Name:INTENCLROffset:0x14 [ID-00000e74]Reset:0x00Property:PAC Write-Protection

In Controller mode, only the Clock generation unit needs to be configured by writing to the CTRLA and CLKCTRLn registers, where parameters such as clock division factors, Number of slots, Slot size, Frame Sync signal, clock enable are selected.

## MCKn Clock Frequency

When the I<sup>2</sup>S is in Master mode, writing a '1' to CLKCTRLn.MCKEN will output GCLK\_I2S\_n as Master Clock to the MCKn pin. The Master Clock to MCKn pin can be divided by writing to CLKCTRLn.MCKSEL and CLKCTRLn.MCKOUTOUT. The Master Clock (MCKn) frequency is GCLK\_I2S\_n frequency divided by (MCLKOUTDIV+1).

$$f(MCKn) = \frac{f(GCLK_{I2S_n})}{(MCKOUTDIV+1)}$$

## SCKn Clock Frequency