Welcome to E-XFL.COM

#### Embedded - System On Chip (SoC): The Heart of Modern Embedded Systems

**Embedded - System On Chip (SoC)** refers to an integrated circuit that consolidates all the essential components of a computer system into a single chip. This includes a microprocessor, memory, and other peripherals, all packed into one compact and efficient package. SoCs are designed to provide a complete computing solution, optimizing both space and power consumption, making them ideal for a wide range of embedded applications.

#### What are **Embedded - System On Chip (SoC)**?

**System On Chip (SoC)** integrates multiple functions of a computer or electronic system onto a single chip. Unlike traditional multi-chip solutions. SoCs combine a central

#### Details

| Product Status          | Obsolete                                                        |

|-------------------------|-----------------------------------------------------------------|

| Architecture            | MCU, FPGA                                                       |

| Core Processor          | ARM® Cortex®-M3                                                 |

| Flash Size              | 128KB                                                           |

| RAM Size                | 16KB                                                            |

| Peripherals             | DMA, POR, WDT                                                   |

| Connectivity            | EBI/EMI, I <sup>2</sup> C, SPI, UART/USART                      |

| Speed                   | 100MHz                                                          |

| Primary Attributes      | ProASIC®3 FPGA, 60K Gates, 1536D-Flip-Flops                     |

| Operating Temperature   | 0°C ~ 85°C (TJ)                                                 |

| Package / Case          | 288-TFBGA, CSPBGA                                               |

| Supplier Device Package | 288-CSP (11x11)                                                 |

| Purchase URL            | https://www.e-xfl.com/product-detail/microsemi/a2f060m3e-1cs288 |

|                         |                                                                 |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

# 🌜 Microsemi.

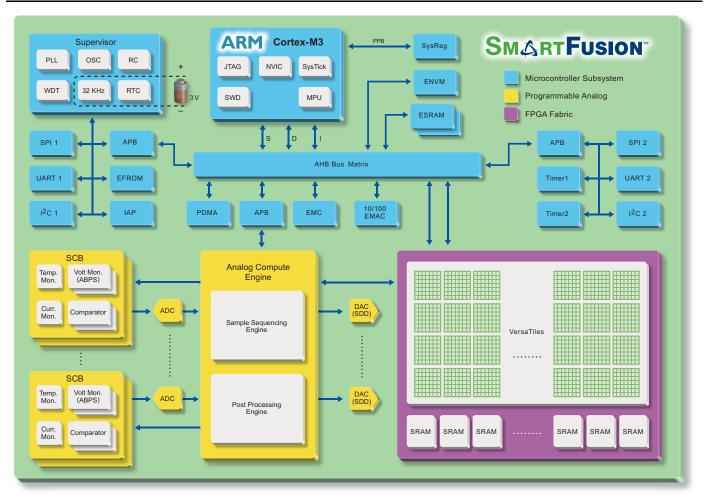

SmartFusion Customizable System-on-Chip (cSoC)

# SmartFusion cSoC Block Diagram

## Legend:

SDD – Sigma-delta DAC SCB – Signal conditioning block PDMA – Peripheral DMA IAP – In-application programming ABPS – Active bipolar prescaler WDT – Watchdog Timer

SWD – Serial Wire Debug

SmartFusion DC and Switching Characteristics

# **Power Consumption of Various Internal Resources**

Table 2-14 • Different Components Contributing to Dynamic Power Consumption in SmartFusion cSoCs

|           |                                                                           | Power Supp                  |         |            |          |           |          |

|-----------|---------------------------------------------------------------------------|-----------------------------|---------|------------|----------|-----------|----------|

| Parameter | Definition                                                                | Name                        | Domain  | A2F060     | A2F200   | A2F500    | Units    |

| PAC1      | Clock contribution of a Global Rib                                        | VCC                         | 1.5 V   | 3.39       | 3.40     | 5.05      | µW/MHz   |

| PAC2      | Clock contribution of a Global Spine                                      | VCC                         | 1.5 V   | 1.14       | 1.83     | 2.50      | µW/MHz   |

| PAC3      | Clock contribution of a VersaTile row                                     | VCC                         | 1.5 V   | 1.15       | 1.15     | 1.15      | µW/MHz   |

| PAC4      | Clock contribution of a VersaTile used as a sequential module             | VCC                         | 1.5 V   | 0.12       | 0.12     | 0.12      | µW/MHz   |

| PAC5      | First contribution of a VersaTile used as a sequential module             | VCC                         | 1.5 V   | 0.07       | 0.07     | 0.07      | µW/MHz   |

| PAC6      | Second contribution of a VersaTile used as a sequential module            | VCC                         | 1.5 V   | 0.29       | 0.29     | 0.29      | µW/MHz   |

| PAC7      | Contribution of a VersaTile used as<br>a combinatorial module             | VCC                         | 1.5 V   | 0.29       | 0.29     | 0.29      | µW/MHz   |

| PAC8      | Average contribution of a routing net                                     | VCC                         | 1.5 V   | 1.04       | 0.79     | 0.79      | µW/MHz   |

| PAC9      | Contribution of an I/O input pin (standard dependent)                     | VCCxxxxIOBx/VCC             | See Tab | ole 2-10 a | age 2-11 |           |          |

| PAC10     | Contribution of an I/O output pin (standard dependent)                    | VCCxxxxIOBx/VCC             | See Tab | ole 2-12 a | nd Table | 2-13 on p | age 2-11 |

| PAC11     | Average contribution of a RAM block during a read operation               | VCC                         | 1.5 V   | 25.00      |          |           | µW/MHz   |

| PAC12     | Average contribution of a RAM block during a write operation              | VCC                         | 1.5 V   |            | 30.00    |           |          |

| PAC13     | Dynamic Contribution for PLL                                              | VCC                         | 1.5 V   |            | 2.60     |           | µW/MHz   |

| PAC15     | Contribution of NVM block during a read operation (F < 33MHz)             | VCC                         | 1.5 V   |            | 358.00   |           | µW/MHz   |

| PAC16     | 1st contribution of NVM block during<br>a read operation (F > 33MHz)      | VCC                         | 1.5 V   |            | 12.88    |           | mW       |

| PAC17     | 2nd contribution of NVM block<br>during a read operation (F > 33MHz)      | VCC                         | 1.5 V   |            | 4.80     |           | µW/MHz   |

| PAC18     | Main Crystal Oscillator contribution                                      | VCCMAINXTAL                 | 3.3 V   |            | 1.98     |           | mW       |

| PAC19a    | RC Oscillator contribution                                                | VCCRCOSC                    | 3.3 V   |            | 3.30     |           | mW       |

| PAC19b    | RC Oscillator contribution                                                | VCC                         | 1.5 V   |            | 3.00     |           | mW       |

| PAC20a    | Analog Block Dynamic Power<br>Contribution of the ADC                     | VCC33ADCx                   | 3.3 V   |            | 8.25     |           | mW       |

| PAC20b    | Analog Block Dynamic Power<br>Contribution of the ADC                     | VCC15ADCx                   | 1.5 V   |            | 3.00     |           | mW       |

| PAC21     | Low Power Crystal Oscillator contribution                                 | VCCLPXTAL                   | 3.3 V   |            | 33.00    |           | μW       |

| PAC22     | MSS Dynamic Power Contribution – Running Drysthone at 100MHz <sup>1</sup> | VCC                         | 1.5 V   |            | 67.50    |           | mW       |

| PAC23     | Temperature Monitor Power<br>Contribution                                 | See Table 2-94 on page 2-79 | -       |            | 1.23     |           | mW       |

$P_{PLL} = 0 W$

## Embedded Nonvolatile Memory Dynamic Contribution—P<sub>eNVM</sub>

#### SoC Mode

The eNVM dynamic power consumption is a piecewise linear function of frequency.

$\mathsf{P}_{eNVM}$  =  $\mathsf{N}_{eNVM\text{-}BLOCKS}$  \*  $\beta_4$  \*  $\mathsf{P}_{AC15}$  \*  $\mathsf{F}_{READ\text{-}eNVM}$  when  $\mathsf{F}_{READ\text{-}eNVM}$   $\leq$  33 MHz,

$P_{eNVM} = N_{eNVM-BLOCKS} * \beta_4 * (P_{AC16} + P_{AC17} * F_{READ-eNVM}) \text{ when } F_{READ-eNVM} > 33 \text{ MHz}$ Where:

N<sub>eNVM-BLOCKS</sub> is the number of eNVM blocks used in the design.

$\beta_4$  is the eNVM enable rate for read operations. Default is 0 (eNVM mainly in idle state).  $F_{READ-eNVM}$  is the eNVM read clock frequency.

#### Standby Mode and Time Keeping Mode

$P_{eNVM} = 0 W$

Main Crystal Oscillator Dynamic Contribution—P<sub>XTL-OSC</sub>

### SoC Mode

$P_{XTL-OSC} = P_{AC18}$

Standby Mode

$P_{XTL-OSC} = 0 W$

#### Time Keeping Mode

$P_{XTL-OSC} = 0 W$

## Low Power Oscillator Crystal Dynamic Contribution—P<sub>LPXTAL-OSC</sub>

## Operating, Standby, and Time Keeping Mode

$P_{LPXTAL-OSC} = P_{AC21}$

### **RC Oscillator Dynamic Contribution**—**P**<sub>RC-OSC</sub>

#### SoC Mode

$P_{RC-OSC} = P_{AC19A} + P_{AC19B}$

#### Standby Mode and Time Keeping Mode

$P_{RC-OSC} = 0 W$

### Analog System Dynamic Contribution—PAB

#### SoC Mode

```

P_{AB} = P_{AC23} * N_{TM} + P_{AC24} * N_{CM} + P_{AC25} * N_{ABPS} + P_{AC26} * N_{SDD} + P_{AC27} * N_{COMP} + P_{ADC} * N_{ADC} + P_{VR}

```

Where:

- N<sub>CM</sub> is the number of current monitor blocks

- N<sub>TM</sub> is the number of temperature monitor blocks

- N<sub>SDD</sub> is the number of sigma-delta DAC blocks

- NABPS is the number of ABPS blocks

- N<sub>ADC</sub> is the number of ADC blocks

N<sub>COMP</sub> is the number of comparator blocks

P<sub>VR</sub>= P<sub>AC28</sub>

$P_{ADC} = P_{AC20A} + P_{AC20B}$

SmartFusion DC and Switching Characteristics

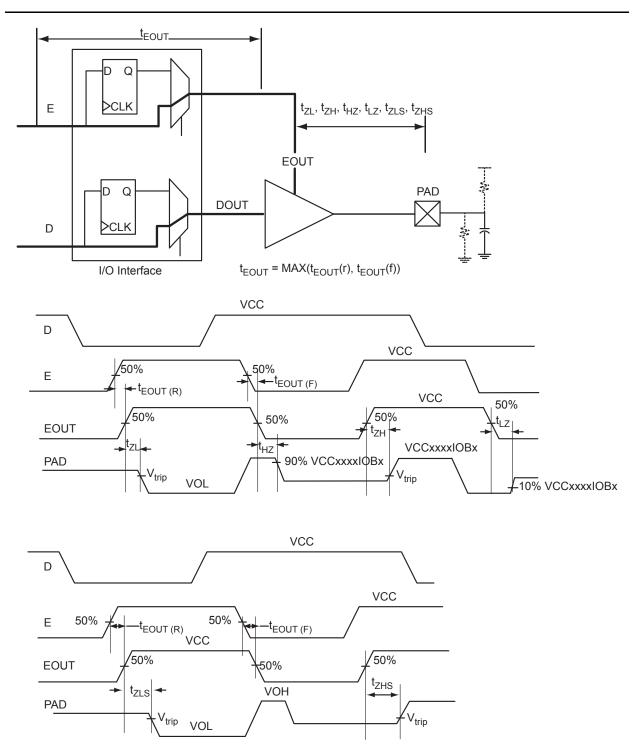

*Figure 2-5* • Tristate Output Buffer Timing Model and Delays (example)

### Table 2-28 • I/O Output Buffer Maximum Resistances<sup>1</sup> Applicable to MSS I/O Banks

| Standard                   | Drive Strength | $R_{PULL	ext{-}DOWN} \ (\Omega)^2$ | R <sub>PULL-UP</sub><br>(Ω) <sup>3</sup> |

|----------------------------|----------------|------------------------------------|------------------------------------------|

| 3.3 V LVTTL / 3.3 V LVCMOS | 8mA            | 50                                 | 150                                      |

| 2.5 V LVCMOS               | 8 mA           | 50                                 | 100                                      |

| 1.8 V LVCMOS               | 4 mA           | 100                                | 112                                      |

| 1.5 V LVCMOS               | 2 mA           | 200                                | 224                                      |

Notes:

These maximum values are provided for informational reasons only. Minimum output buffer resistance values depend on VCCxxxxIOBx, drive strength selection, temperature, and process. For board design considerations and detailed output buffer resistances, use the corresponding IBIS models located on the Microsemi SoC Products Group website.

- 2. R<sub>(PULL-DOWN-MAX)</sub> = (V<sub>OLspec</sub>) / I<sub>OLspec</sub>

- 3. R<sub>(PULL-UP-MAX)</sub> = (V<sub>CCImax</sub> V<sub>OHspec</sub>) / I<sub>OHspec</sub>

# Table 2-29 • I/O Weak Pull-Up/Pull-Down Resistances Minimum and Maximum Weak Pull-Up/Pull-Down Resistance Values

|             | R <sub>(WEAK P</sub><br>(Ω | PULL-UP) <sup>1</sup><br>2) | ${\sf R}_{({\sf WEAK PULL-DOWN})}^2$ ( $\Omega$ ) |       |  |

|-------------|----------------------------|-----------------------------|---------------------------------------------------|-------|--|

| VCCxxxxlOBx | Min.                       | Max.                        | Min.                                              | Max.  |  |

| 3.3 V       | 10 k                       | 45 k                        | 10 k                                              | 45 k  |  |

| 2.5 V       | 11 k                       | 55 k                        | 12 k                                              | 74 k  |  |

| 1.8 V       | 18 k                       | 70 k                        | 17 k                                              | 110 k |  |

| 1.5 V       | 19 k                       | 90 k                        | 19 k                                              | 140 k |  |

Notes:

1. R<sub>(WEAK PULL-UP-MAX)</sub> = (VCCImax – VOHspec) / I<sub>(WEAK PULL-UP-MIN)</sub>

2. R<sub>(WEAK PULL-DOWN-MAX)</sub> = (VOLspec) / I<sub>(WEAK PULL-DOWN-MIN)</sub>

SmartFusion DC and Switching Characteristics

# Single-Ended I/O Characteristics

# 3.3 V LVTTL / 3.3 V LVCMOS

Low-Voltage Transistor–Transistor Logic (LVTTL) is a general-purpose standard (EIA/JESD) for 3.3 V applications. It uses an LVTTL input buffer and push-pull output buffer.

### Table 2-35 • Minimum and Maximum DC Input and Output Levels Applicable to FPGA I/O Banks

| 3.3 V LVTTL /<br>3.3 V LVCMOS | v         | IL        | v         | ін        | VOL       | VOH       | I <sub>OL</sub> | I <sub>OH</sub> | I <sub>OSL</sub>        | I <sub>OSH</sub>        | I <sub>IL</sub> | IIH |

|-------------------------------|-----------|-----------|-----------|-----------|-----------|-----------|-----------------|-----------------|-------------------------|-------------------------|-----------------|-----|

| Drive Strength                | Min.<br>V | Max.<br>V | Min.<br>V | Max.<br>V | Max.<br>V | Min.<br>V | mA              | mA              | Max.<br>mA <sup>1</sup> | Max.<br>mA <sup>1</sup> | μA²             | μA² |

| 2 mA                          | -0.3      | 0.8       | 2         | 3.6       | 0.4       | 2.4       | 2               | 2               | 27                      | 25                      | 15              | 15  |

| 4 mA                          | -0.3      | 0.8       | 2         | 3.6       | 0.4       | 2.4       | 4               | 4               | 27                      | 25                      | 15              | 15  |

| 6 mA                          | -0.3      | 0.8       | 2         | 3.6       | 0.4       | 2.4       | 6               | 6               | 54                      | 51                      | 15              | 15  |

| 8 mA                          | -0.3      | 0.8       | 2         | 3.6       | 0.4       | 2.4       | 8               | 8               | 54                      | 51                      | 15              | 15  |

| 12 mA                         | -0.3      | 0.8       | 2         | 3.6       | 0.4       | 2.4       | 12              | 12              | 109                     | 103                     | 15              | 15  |

| 16 mA                         | -0.3      | 0.8       | 2         | 3.6       | 0.4       | 2.4       | 16              | 16              | 127                     | 132                     | 15              | 15  |

| 24 mA                         | -0.3      | 0.8       | 2         | 3.6       | 0.4       | 2.4       | 24              | 24              | 181                     | 268                     | 10              | 10  |

Notes:

1. Currents are measured at 100°C junction temperature and maximum voltage.

2. Currents are measured at 85°C junction temperature.

3. Software default selection highlighted in gray.

#### Table 2-36 • Minimum and Maximum DC Input and Output Levels Applicable to MSS I/O Banks

| 3.3 V LVTTL /<br>3.3 V LVCMOS | v         | ïL        | v         | н         | VOL       | VOH       | I <sub>OL</sub> | I <sub>OH</sub> | I <sub>OSL</sub>        | I <sub>OSH</sub>        | IIL | I <sub>IH</sub> |

|-------------------------------|-----------|-----------|-----------|-----------|-----------|-----------|-----------------|-----------------|-------------------------|-------------------------|-----|-----------------|

| Drive Strength                | Min.<br>V | Max.<br>V | Min.<br>V | Max.<br>V | Max.<br>V | Min.<br>V | mA              | mA              | Max.<br>mA <sup>1</sup> | Max.<br>mA <sup>1</sup> | μA² | μA²             |

| 8 mA                          | -0.3      | 0.8       | 2         | 3.6       | 0.4       | 2.4       | 8               | 8               | 54                      | 51                      | 15  | 15              |

Notes:

1. Currents are measured at 100°C junction temperature and maximum voltage.

2. Currents are measured at 85°C junction temperature.

3. Software default selection highlighted in gray.

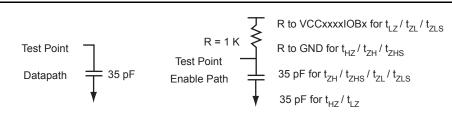

## Figure 2-6 • AC Loading

### Table 2-37 • AC Waveforms, Measuring Points, and Capacitive Loads

| Input Low (V) | Input High (V) | Measuring Point* (V) | V <sub>REF</sub> (typ.) (V) | C <sub>LOAD</sub> (pF) |

|---------------|----------------|----------------------|-----------------------------|------------------------|

| 0             | 3.3            | 1.4                  | -                           | 35                     |

Note: \*Measuring point =  $V_{trip}$ . See Table 2-22 on page 2-24 for a complete table of trip points.

### **Timing Characteristics**

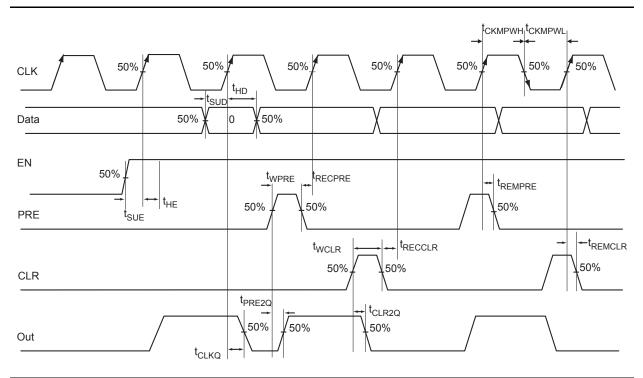

#### Table 2-79 • Register Delays

### Worst Commercial-Case Conditions: T<sub>J</sub> = 85°C, Worst-Case VCC = 1.425 V

| Parameter           | Description                                                   | -1   | Std. | Units |

|---------------------|---------------------------------------------------------------|------|------|-------|

| t <sub>CLKQ</sub>   | Clock-to-Q of the Core Register                               | 0.56 | 0.67 | ns    |

| t <sub>SUD</sub>    | Data Setup Time for the Core Register                         | 0.44 | 0.52 | ns    |

| t <sub>HD</sub>     | Data Hold Time for the Core Register                          | 0.00 | 0.00 | ns    |

| t <sub>SUE</sub>    | Enable Setup Time for the Core Register                       | 0.46 | 0.55 | ns    |

| t <sub>HE</sub>     | Enable Hold Time for the Core Register                        | 0.00 | 0.00 | ns    |

| t <sub>CLR2Q</sub>  | Asynchronous Clear-to-Q of the Core Register                  | 0.41 | 0.49 | ns    |

| t <sub>PRE2Q</sub>  | Asynchronous Preset-to-Q of the Core Register                 | 0.41 | 0.49 | ns    |

| t <sub>REMCLR</sub> | Asynchronous Clear Removal Time for the Core Register         | 0.00 | 0.00 | ns    |

| t <sub>RECCLR</sub> | Asynchronous Clear Recovery Time for the Core Register        | 0.23 | 0.27 | ns    |

| t <sub>REMPRE</sub> | Asynchronous Preset Removal Time for the Core Register        | 0.00 | 0.00 | ns    |

| t <sub>RECPRE</sub> | Asynchronous Preset Recovery Time for the Core Register       | 0.23 | 0.27 | ns    |

| t <sub>WCLR</sub>   | Asynchronous Clear Minimum Pulse Width for the Core Register  | 0.22 | 0.22 | ns    |

| t <sub>WPRE</sub>   | Asynchronous Preset Minimum Pulse Width for the Core Register | 0.22 | 0.22 | ns    |

| t <sub>CKMPWH</sub> | Clock Minimum Pulse Width High for the Core Register          | 0.32 | 0.32 | ns    |

| t <sub>CKMPWL</sub> | Clock Minimum Pulse Width Low for the Core Register           | 0.36 | 0.36 | ns    |

*Note:* For specific junction temperature and voltage supply levels, refer to Table 2-7 on page 2-9 for derating values.

# static Microsemi.

SmartFusion DC and Switching Characteristics

#### *Table 2-88* • RAM512X18

| Parameter             | Description                                                                                                        | -1   | Std. | Units |

|-----------------------|--------------------------------------------------------------------------------------------------------------------|------|------|-------|

| t <sub>AS</sub>       | Address setup time                                                                                                 | 0.25 | 0.30 | ns    |

| t <sub>AH</sub>       | Address hold time                                                                                                  | 0.00 | 0.00 | ns    |

| t <sub>ENS</sub>      | REN, WEN setup time                                                                                                | 0.09 | 0.11 | ns    |

| t <sub>ENH</sub>      | REN, WEN hold time                                                                                                 | 0.06 | 0.07 | ns    |

| t <sub>DS</sub>       | Input data (WD) setup time                                                                                         | 0.19 | 0.22 | ns    |

| t <sub>DH</sub>       | Input data (WD) hold time                                                                                          | 0.00 | 0.00 | ns    |

| t <sub>CKQ1</sub>     | Clock High to new data valid on RD (output retained, WMODE = 0)                                                    | 2.19 | 2.63 | ns    |

| t <sub>CKQ2</sub>     | Clock High to new data valid on RD (pipelined)                                                                     | 0.91 | 1.09 | ns    |

| t <sub>C2CRWH</sub> 1 | Address collision clk-to-clk delay for reliable read access after write on same address—applicable to opening edge | 0.38 | 0.43 | ns    |

| t <sub>C2CWRH</sub> 1 | Address collision clk-to-clk delay for reliable write access after read on same address—applicable to opening edge | 0.44 | 0.50 | ns    |

| t <sub>RSTBQ</sub>    | RESET Low to data out Low on RD (flow-through)                                                                     | 0.94 | 1.12 | ns    |

|                       | RESET Low to data out Low on RD (pipelined)                                                                        | 0.94 | 1.12 | ns    |

| t <sub>REMRSTB</sub>  | RESET removal                                                                                                      | 0.29 | 0.35 | ns    |

| t <sub>RECRSTB</sub>  | RESET recovery                                                                                                     | 1.52 | 1.83 | ns    |

| t <sub>MPWRSTB</sub>  | RESET minimum pulse width                                                                                          | 0.22 | 0.22 | ns    |

| t <sub>CYC</sub>      | Clock cycle time                                                                                                   | 3.28 | 3.28 | ns    |

| F <sub>MAX</sub>      | Maximum clock frequency                                                                                            | 305  | 305  | MHz   |

Notes:

1. For more information, refer to the Simultaneous Read-Write Operations in Dual-Port SRAM for Flash-Based cSoCs and FPGAs application note.

2. For the derating values at specific junction temperature and voltage supply levels, refer to Table 2-7 on page 2-9 for derating values.

# **Timing Characteristics**

### Table 2-89 • FIFO

| Parameter            | Description                                       | -1   | Std. | Units |

|----------------------|---------------------------------------------------|------|------|-------|

| t <sub>ENS</sub>     | REN, WEN Setup Time                               | 1.40 | 1.68 | ns    |

| t <sub>ENH</sub>     | REN, WEN Hold Time                                | 0.02 | 0.02 | ns    |

| t <sub>BKS</sub>     | BLK Setup Time                                    | 0.19 | 0.19 | ns    |

| t <sub>BKH</sub>     | BLK Hold Time                                     | 0.00 | 0.00 | ns    |

| t <sub>DS</sub>      | Input Data (WD) Setup Time                        | 0.19 | 0.22 | ns    |

| t <sub>DH</sub>      | Input Data (WD) Hold Time                         | 0.00 | 0.00 | ns    |

| t <sub>CKQ1</sub>    | Clock High to New Data Valid on RD (flow-through) | 2.39 | 2.87 | ns    |

| t <sub>CKQ2</sub>    | Clock High to New Data Valid on RD (pipelined)    | 0.91 | 1.09 | ns    |

| t <sub>RCKEF</sub>   | RCLK High to Empty Flag Valid                     | 1.74 | 2.09 | ns    |

| t <sub>WCKFF</sub>   | WCLK High to Full Flag Valid                      | 1.66 | 1.99 | ns    |

| t <sub>CKAF</sub>    | Clock HIGH to Almost Empty/Full Flag Valid        | 6.29 | 7.54 | ns    |

| t <sub>RSTFG</sub>   | RESET Low to Empty/Full Flag Valid                | 1.72 | 2.06 | ns    |

| t <sub>RSTAF</sub>   | RESET Low to Almost Empty/Full Flag Valid         | 6.22 | 7.47 | ns    |

| t <sub>RSTBQ</sub>   | RESET Low to Data Out Low on RD (flow-through)    | 0.94 | 1.12 | ns    |

|                      | RESET Low to Data Out Low on RD (pipelined)       | 0.94 | 1.12 | ns    |

| t <sub>REMRSTB</sub> | RESET Removal                                     | 0.29 | 0.35 | ns    |

| t <sub>RECRSTB</sub> | RESET Recovery                                    | 1.52 | 1.83 | ns    |

| t <sub>MPWRSTB</sub> | RESET Minimum Pulse Width                         | 0.22 | 0.22 | ns    |

| t <sub>CYC</sub>     | Clock Cycle Time                                  | 3.28 | 3.28 | ns    |

| F <sub>MAX</sub>     | Maximum Frequency for FIFO                        | 305  | 305  | MHz   |

Note: For specific junction temperature and voltage supply levels, refer to Table 2-7 on page 2-9 for derating values.

# **Programmable Analog Specifications**

# **Current Monitor**

Unless otherwise noted, current monitor performance is specified at 25°C with nominal power supply voltages, with the output measured using the internal voltage reference with the internal ADC in 12-bit mode and 91 Ksps, after digital compensation. All results are based on averaging over 16 samples.

Table 2-93 • Current Monitor Performance Specification

| Specification                                                  | Test Conditions                                                                              | Min.   | Typical           | Max.             | Units                   |

|----------------------------------------------------------------|----------------------------------------------------------------------------------------------|--------|-------------------|------------------|-------------------------|

| Input voltage range (for driving ADC over full range)          |                                                                                              | 0 – 48 | 0 – 50            | 1 – 51           | mV                      |

| Analog gain                                                    | From the differential voltage across the input pads to the ADC input                         |        | 50                |                  | V/V                     |

| Input referred offset voltage                                  | Input referred offset voltage                                                                | 0      | 0.1               | 0.5              | mV                      |

|                                                                | -40°C to +100°C                                                                              | 0      | 0.1               | 0.5              | mV                      |

| Gain error                                                     | Slope of BFSL vs. 50 V/V                                                                     |        | ±0.1              | ±0.5             | % nom.                  |

|                                                                | -40°C to +100°C                                                                              |        |                   | ±0.5             | % nom.                  |

| Overall Accuracy                                               | Peak error from ideal transfer function, 25°C                                                |        | ±(0.1 +<br>0.25%) | ±(0.4 +<br>1.5%) | mV plus<br>%<br>reading |

| Input referred noise                                           | 0 VDC input (no output averaging)                                                            | 0.3    | 0.4               | 0.5              | mVrms                   |

| Common-mode rejection ratio                                    | 0 V to 12 VDC common-mode voltage                                                            | -86    | -87               |                  | dB                      |

| Analog settling time                                           | To 0.1% of final value (with ADC load)                                                       |        |                   |                  |                         |

|                                                                | From CM_STB (High)                                                                           | 5      |                   |                  | μs                      |

|                                                                | From ADC_START (High)                                                                        | 5      |                   | 200              | μs                      |

| Input capacitance                                              |                                                                                              |        | 8                 |                  | pF                      |

| Input biased current                                           | CM[n] or TM[n] pad,<br>40°C to +100°C over maximum input<br>voltage range (plus is into pad) |        |                   |                  |                         |

|                                                                | Strobe = 0; IBIAS on CM[n]                                                                   |        | 0                 |                  | μA                      |

|                                                                | Strobe = 1; IBIAS on CM[n]                                                                   |        | 1                 |                  | μA                      |

|                                                                | Strobe = 0; IBIAS on TM[n]                                                                   |        | 2                 |                  | μA                      |

|                                                                | Strobe = 1; IBIAS on TM[n]                                                                   |        | 1                 |                  | μA                      |

| Power supply rejection ratio                                   | DC (0 – 10 KHz)                                                                              | 41     | 42                |                  | dB                      |

| •                                                              | VCC33A                                                                                       |        | 150               |                  | μA                      |

| monitor power supply current requirements (per current monitor | VCC33AP                                                                                      |        | 140               |                  | μA                      |

| instance, not including ADC or<br>VAREFx)                      | VCC15A                                                                                       |        | 50                |                  | μA                      |

Note: Under no condition should the TM pad ever be greater than 10 mV above the CM pad. This restriction is applicable only if current monitor is used.

# **Serial Peripheral Interface (SPI) Characteristics**

This section describes the DC and switching of the SPI interface. Unless otherwise noted, all output characteristics given for a 35 pF load on the pins and all sequential timing characteristics are related to SPI\_x\_CLK. For timing parameter definitions, refer to Figure 2-47 on page 2-90.

| Symbol | Description and Condition                                      | A2F060 | A2F200 | A2F500 | Unit |

|--------|----------------------------------------------------------------|--------|--------|--------|------|

| sp1    | SPI_x_CLK minimum period                                       |        |        |        |      |

|        | SPI_x_CLK = PCLK/2                                             | 20     | NA     | 20     | ns   |

|        | SPI_x_CLK = PCLK/4                                             | 40     | 40     | 40     | ns   |

|        | SPI_x_CLK = PCLK/8                                             | 80     | 80     | 80     | ns   |

|        | SPI_x_CLK = PCLK/16                                            | 0.16   | 0.16   | 0.16   | μs   |

|        | SPI_x_CLK = PCLK/32                                            | 0.32   | 0.32   | 0.32   | μs   |

|        | SPI_x_CLK = PCLK/64                                            | 0.64   | 0.64   | 0.64   | μs   |

|        | SPI_x_CLK = PCLK/128                                           | 1.28   | 1.28   | 1.28   | μs   |

|        | SPI_x_CLK = PCLK/256                                           | 2.56   | 2.56   | 2.56   | μs   |

| sp2    | SPI_x_CLK minimum pulse width high                             |        |        |        |      |

|        | SPI_x_CLK = PCLK/2                                             | 10     | NA     | 10     | ns   |

|        | SPI_x_CLK = PCLK/4                                             | 20     | 20     | 20     | ns   |

|        | SPI_x_CLK = PCLK/8                                             | 40     | 40     | 40     | ns   |

|        | SPI_x_CLK = PCLK/16                                            | 0.08   | 0.08   | 0.08   | μs   |

|        | SPI_x_CLK = PCLK/32                                            | 0.16   | 0.16   | 0.16   | μs   |

|        | SPI_x_CLK = PCLK/64                                            | 0.32   | 0.32   | 0.32   | μs   |

|        | SPI_x_CLK = PCLK/128                                           | 0.64   | 0.64   | 0.64   | μs   |

|        | SPI_x_CLK = PCLK/256                                           | 1.28   | 1.28   | 1.28   | us   |

| sp3    | SPI_x_CLK minimum pulse width low                              |        |        |        |      |

|        | SPI_x_CLK = PCLK/2                                             | 10     | NA     | 10     | ns   |

|        | SPI_x_CLK = PCLK/4                                             | 20     | 20     | 20     | ns   |

|        | SPI_x_CLK = PCLK/8                                             | 40     | 40     | 40     | ns   |

|        | SPI_x_CLK = PCLK/16                                            | 0.08   | 0.08   | 0.08   | μs   |

|        | SPI_x_CLK = PCLK/32                                            | 0.16   | 0.16   | 0.16   | μs   |

|        | SPI_x_CLK = PCLK/64                                            | 0.32   | 0.32   | 0.32   | μs   |

|        | SPI_x_CLK = PCLK/128                                           | 0.64   | 0.64   | 0.64   | μs   |

|        | SPI_x_CLK = PCLK/256                                           | 1.28   | 1.28   | 1.28   | μs   |

| sp4    | SPI_x_CLK, SPI_x_DO, SPI_x_SS rise time (10%-90%) <sup>1</sup> | 4.7    | 4.7    | 4.7    | ns   |

| sp5    | SPI_x_CLK, SPI_x_DO, SPI_x_SS fall time (10%-90%) <sup>1</sup> | 3.4    | 3.4    | 3.4    | ns   |

### Table 2-100 • SPI Characteristics

Commercial Case Conditions: T<sub>J</sub> = 85°C, VDD = 1.425 V, -1 Speed Grade

Notes:

These values are provided for a load of 35 pF. For board design considerations and detailed output buffer resistances, use the corresponding IBIS models located on the Microsemi SoC Products Group website: http://www.microsemi.com/index.php?option=com\_microsemi&ltemid=489&lang=en&view=salescontact.

2. For allowable pclk configurations, refer to the Serial Peripheral Interface Controller section in the SmartFusion Microcontroller Subsystem User's Guide.

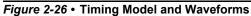

# **3 – SmartFusion Development Tools**

Designing with SmartFusion cSoCs involves three different types of design: FPGA design, embedded design and analog design. These roles can be filled by three different designers, two designers or even a single designer, depending on company structure and project complexity.

# **Types of Design Tools**

Microsemi has developed design tools and flows to meet the needs of these three types of designers so they can work together smoothly on a single project (Figure 3-1).

Figure 3-1 • Three Design Roles

# **FPGA** Design

Libero System-on-Chip (SoC) software is Microsemi's comprehensive software toolset for designing with all Microsemi FPGAs and cSoCs. Libero SoC includes industry-leading synthesis, simulation and debug tools from Synopsys<sup>®</sup> and Mentor Graphics<sup>®</sup>, as well as innovative timing and power optimization and analysis.

Pin Descriptions

# **Analog Front-End Pin-Level Function Multiplexing**

Table 5-2 describes the relationships between the various internal signals found in the analog front-end (AFE) and how they are multiplexed onto the external package pins. Note that, in general, only one function is available for those pads that have numerous functions listed. The exclusion to this rule is when a comparator is used; the ADC can still convert either input side of the comparator.

| Pin   | ADC<br>Channel | DirIn<br>Option | Prescaler | Current<br>Mon. | Temp.<br>Mon. | Compar. | LVTTL      | SDD MUX   | SDD      |

|-------|----------------|-----------------|-----------|-----------------|---------------|---------|------------|-----------|----------|

| ABPS0 | ADC0_CH1       |                 | ABPS0_IN  |                 |               |         |            |           |          |

| ABPS1 | ADC0_CH2       |                 | ABPS1_IN  |                 |               |         |            |           |          |

| ABPS2 | ADC0_CH5       |                 | ABPS2_IN  |                 |               |         |            |           |          |

| ABPS3 | ADC0_CH6       |                 | ABPS3_IN  |                 |               |         |            |           |          |

| ABPS4 | ADC1_CH1       |                 | ABPS4_IN  |                 |               |         |            |           |          |

| ABPS5 | ADC1_CH2       |                 | ABPS5_IN  |                 |               |         |            |           |          |

| ABPS6 | ADC1_CH5       |                 | ABPS6_IN  |                 |               |         |            |           |          |

| ABPS7 | ADC1_CH6       |                 | ABPS7_IN  |                 |               |         |            |           |          |

| ABPS8 | ADC2_CH1       |                 | ABPS8_IN  |                 |               |         |            |           |          |

| ABPS9 | ADC2_CH2       |                 | ABPS9_IN  |                 |               |         |            |           |          |

| ADC0  | ADC0_CH9       | Yes             |           |                 |               | CMP1_P  | LVTTL0_IN  |           |          |

| ADC1  | ADC0_CH10      | Yes             |           |                 |               | CMP1_N  | LVTTL1_IN  | SDDM0_OUT |          |

| ADC2  | ADC0_CH11      | Yes             |           |                 |               | CMP3_P  | LVTTL2_IN  |           |          |

| ADC3  | ADC0_CH12      | Yes             |           |                 |               | CMP3_N  | LVTTL3_IN  | SDDM1_OUT |          |

| ADC4  | ADC1_CH9       | Yes             |           |                 |               | CMP5_P  | LVTTL4_IN  |           |          |

| ADC5  | ADC1_CH10      | Yes             |           |                 |               | CMP5_N  | LVTTL5_IN  | SDDM2_OUT |          |

| ADC6  | ADC1_CH11      | Yes             |           |                 |               | CMP7_P  | LVTTL6_IN  |           |          |

| ADC7  | ADC1_CH12      | Yes             |           |                 |               | CMP7_N  | LVTTL7_IN  | SDDM3_OUT |          |

| ADC8  | ADC2_CH9       | Yes             |           |                 |               | CMP9_P  | LVTTL8_IN  |           |          |

| ADC9  | ADC2_CH10      | Yes             |           |                 |               | CMP9_N  | LVTTL9_IN  | SDDM4_OUT |          |

| ADC10 | ADC2_CH11      | Yes             |           |                 |               |         | LVTTL10_IN |           |          |

| ADC11 | ADC2_CH12      | Yes             |           |                 |               |         | LVTTL11_IN |           |          |

| CM0   | ADC0_CH3       | Yes             |           | CM0_H           |               | CMP0_P  |            |           |          |

| CM1   | ADC0_CH7       | Yes             |           | CM1_H           |               | CMP2_P  |            |           |          |

| CM2   | ADC1_CH3       | Yes             |           | CM2_H           |               | CMP4_P  |            |           |          |

| CM3   | ADC1_CH7       | Yes             |           | CM3_H           |               | CMP6_P  |            |           |          |

| CM4   | ADC2_CH3       | Yes             |           | CM4_H           |               | CMP8_P  |            |           |          |

| SDD0  | ADC0_CH15      |                 |           |                 |               |         |            |           | SDD0_OUT |

| SDD1  | ADC1_CH15      |                 |           |                 |               |         |            |           | SDD1_OUT |

#### Table 5-2 • Relationships Between Signals in the Analog Front-End

Notes:

1. ABPSx\_IN: Input to active bipolar prescaler channel x.

2. CMx\_H/L: Current monitor channel x, high/low side.

3. TMx\_IO: Temperature monitor channel x.

4. CMPx\_P/N: Comparator channel x, positive/negative input.

5. LVTTLx\_IN: LVTTL I/O channel x.

6. SDDMx\_OUT: Output from sigma-delta DAC MUX channel x.

7. SDDx\_OUT: Direct output from sigma-delta DAC channel x.

| Pin  | ADC<br>Channel | DirIn<br>Option | Prescaler | Current<br>Mon. | Temp.<br>Mon. | Compar. | LVTTL | SDD MUX | SDD      |

|------|----------------|-----------------|-----------|-----------------|---------------|---------|-------|---------|----------|

| SDD2 | ADC2_CH15      |                 |           |                 |               |         |       |         | SDD2_OUT |

| TM0  | ADC0_CH4       | Yes             |           | CM0_L           | TM0_IO        | CMP0_N  |       |         |          |

| TM1  | ADC0_CH8       | Yes             |           | CM1_L           | TM1_IO        | CMP2_N  |       |         |          |

| TM2  | ADC1_CH4       | Yes             |           | CM2_L           | TM2_IO        | CMP4_N  |       |         |          |

| TM3  | ADC1_CH8       | Yes             |           | CM3_L           | TM3_IO        | CMP6_N  |       |         |          |

| TM4  | ADC2_CH4       | Yes             |           | CM4_L           | TM4_IO        | CMP8_N  |       |         |          |

### Table 5-2 • Relationships Between Signals in the Analog Front-End

Notes:

1. ABPSx\_IN: Input to active bipolar prescaler channel x.

2. CMx\_H/L: Current monitor channel x, high/low side.

- 3. TMx\_IO: Temperature monitor channel x.

- 4. CMPx\_P/N: Comparator channel x, positive/negative input.

- 5. LVTTLx\_IN: LVTTL I/O channel x.

6. SDDMx\_OUT: Output from sigma-delta DAC MUX channel x.

7. SDDx\_OUT: Direct output from sigma-delta DAC channel x.

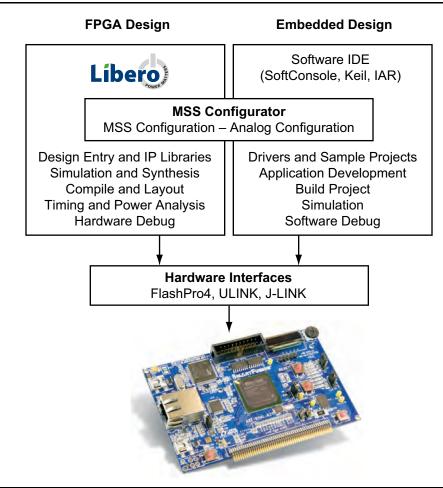

# FG256

## Note

For Package Manufacturing and Environmental information, visit the Resource Center at http://www.microsemi.com/soc/products/solutions/package/docs.aspx.

|            | FG              | 484             |

|------------|-----------------|-----------------|

| Pin Number | A2F200 Function | A2F500 Function |

| M21        | VPP             | VPP             |

| M22        | IO32NDB1V0      | IO41NDB1V0      |

| N1         | GND             | GND             |

| N2         | NC              | IO70PDB5V0      |

| N3         | NC              | IO70NDB5V0      |

| N4         | VCCRCOSC        | VCCRCOSC        |

| N5         | VCCFPGAIOB5     | VCCFPGAIOB5     |

| N6         | NC              | IO68NDB5V0      |

| N7         | VCCFPGAIOB5     | VCCFPGAIOB5     |

| N8         | GND             | GND             |

| N9         | VCC             | VCC             |

| N10        | GND             | GND             |

| N11        | VCC             | VCC             |

| N12        | GND             | GND             |

| N13        | VCC             | VCC             |

| N14        | GND             | GND             |

| N15        | VCC             | VCC             |

| N16        | NC              | GND             |

| N17        | NC              | NC              |

| N18        | VCCFPGAIOB1     | VCCFPGAIOB1     |

| N19        | VCCENVM         | VCCENVM         |

| N20        | GNDENVM         | GNDENVM         |

| N21        | NC              | NC              |

| N22        | GND             | GND             |

| P1         | NC              | IO69NDB5V0      |

| P2         | NC              | IO69PDB5V0      |

| P3         | GNDRCOSC        | GNDRCOSC        |

| P4         | GND             | GND             |

| P5         | NC              | NC              |

| P6         | NC              | NC              |

| P7         | GND             | GND             |

| P8         | VCC             | VCC             |

| P9         | GND             | GND             |

| P10        | VCC             | VCC             |

Notes:

1. Shading denotes pins that do not have completely identical functions from density to density. For example, the bank assignment can be different for an I/O, or the function might be available only on a larger density device.

2. \*: Indicates that the signal assigned to the pins as a CLKBUF/CLKBUF\_LVPECL/CLKBUF\_LVDS goes through a glitchless mux. In order for the glitchless mux to operate correctly, the signal must be a free-running clock signal. Refer to the 'Glitchless MUX' section in the SmartFusion Microcontroller Subsystem User's Guide for more details.

Datasheet Information

| Revision                   | Changes                                                                                                                                                                                                                                                                                                                                                        | Page          |

|----------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------|

| Revision 9<br>(continued)  | The following note was added to Table 2-86 • SmartFusion CCC/PLL Specification in regard to delay increments in programmable delay blocks (SAR 34816):<br>"When the CCC/PLL core is generated by Microsemi core generator software, not all delay values of the specified delay increments are available. Refer to SmartGen online help for more information." | 2-63          |

|                            | Figure 2-36 • FIFO Read and Figure 2-37 • FIFO Write have been added (SAR 34851).                                                                                                                                                                                                                                                                              | 2-72          |

|                            | Information regarding the MSS resetting itself after IAP of the FPGA fabric was added to the "Reprogramming the FPGA Fabric Using the Cortex-M3" section (SAR 37970).                                                                                                                                                                                          | 4-8           |

|                            | Instructions for unused VCC33ADCx pins were revised in "Supply Pins" (SAR 41137).                                                                                                                                                                                                                                                                              | 5-1           |

|                            | Libero IDE was changed to Libero SoC throughout the document (SAR 40264).                                                                                                                                                                                                                                                                                      | N/A           |

| Revision 8<br>(March 2012) | In the "Analog Front-End (AFE)" section, the resolution for the first-order sigma delta DAC was corrected from 12-bit to "8-bit, 16-bit, or 24-bit." The same correction was made in the "SmartFusion cSoC Family Product Table" (SAR 36541).                                                                                                                  | I, II         |

|                            | The "SmartFusion cSoC Family Product Table" was revised to break out the features by package as well as device.                                                                                                                                                                                                                                                | II            |

|                            | The table now indicates that only one SPI is available for the PQ208 package in A2F200 and A2F500, and in the TQ144 package for A2F060 (SAR 33477). The EMC address bus size has been corrected to 26 bits (SAR 35664).                                                                                                                                        |               |

|                            | The "SmartFusion cSoC Device Status" table was revised to change the CS288 package for A2F200 and A2F500 from preliminary to production status (SAR 37811).                                                                                                                                                                                                    | Ш             |

|                            | TQ144 package information for A2F060 was added to the "Package I/Os: MSS + FPGA I/Os" table, "SmartFusion cSoC Device Status" table, "Product Ordering Codes", and "Temperature Grade Offerings" table (SAR 36246).                                                                                                                                            | III, VI       |

|                            | Table 1 • SmartFusion cSoC Package Sizes Dimensions is new (SAR 31178).                                                                                                                                                                                                                                                                                        | Ш             |

|                            | The Halogen-Free Packaging code (H) was removed from the "Product Ordering Codes" table (SAR 34017).                                                                                                                                                                                                                                                           | VI            |

|                            | The "Specifying I/O States During Programming" section is new (SAR 34836).                                                                                                                                                                                                                                                                                     | 1-3           |

|                            | The reference to guidelines for global spines and VersaTile rows, given in the "Global Clock Dynamic Contribution—P <sub>CLOCK</sub> " section, was corrected to the "Device Architecture" chapter in the <i>SmartFusion FPGA Fabric User's Guide</i> (SAR 34742).                                                                                             | 2-15          |

|                            | The AC Loading figures in the "Single-Ended I/O Characteristics" section were updated to match tables in the "Summary of I/O Timing Characteristics – Default I/O Software Settings" section (SAR 34891).                                                                                                                                                      | 2-30,<br>2-24 |

|                            | The following sentence was deleted from the "2.5 V LVCMOS" section (SAR 34799): "It uses a 5 V-tolerant input buffer and push-pull output buffer."                                                                                                                                                                                                             | 2-32          |

|                            | In the SRAM "Timing Characteristics" tables, reference was made to a new application note, <i>Simultaneous Read-Write Operations in Dual-Port SRAM for Flash-Based cSoCs and FPGAs</i> , which covers these cases in detail (SAR 34874).                                                                                                                       | 2-69          |

|                            | The note for Table 2-93 • Current Monitor Performance Specification was modified to include the statement that the restriction on the TM pad being no greater than 10 mV above the CM pad.is applicable only if current monitor is used (SAR 26373).                                                                                                           | 2-78          |

|                            | The unit "FR" in Table 2-96 • ABPS Performance Specifications and Table 2-98 • Analog Sigma-Delta DAC, used to designate full-scale error, was changed to "FS" and clarified with a table note (SAR 35342).                                                                                                                                                    | 2-82,<br>2-85 |

Datasheet Information

| Revision                      | Changes                                                                                                                                                                                                                                                                                                                                                                                                | Page          |

|-------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------|

| Revision 6<br>(continued)     | Dynamic power values were updated in the following tables. The table subtitles changed where FPGA I/O banks were involved to note "I/O assigned to EMC I/O pins" (SAR 30987).                                                                                                                                                                                                                          | 2-10          |

|                               | Table 2-10 • Summary of I/O Input Buffer Power (per pin) – Default I/O Software Settings                                                                                                                                                                                                                                                                                                               | 2-11          |

|                               | Table 2-13 • Summary of I/O Output Buffer Power (per pin) – Default I/O Software Settings.                                                                                                                                                                                                                                                                                                             |               |

|                               | The "Timing Model" was updated (SAR 30986).                                                                                                                                                                                                                                                                                                                                                            | 2-19          |

|                               | Values in the timing tables for the following sections were updated. Table subtitles were updated for FPGA I/O banks to note "I/O assigned to EMC I/O pins" (SAR 30986).                                                                                                                                                                                                                               |               |

|                               | "Overview of I/O Performance" section: Table 2-24, Table 2-25                                                                                                                                                                                                                                                                                                                                          | 2-23          |

|                               | "Detailed I/O DC Characteristics" section: Table 2-38, Table 2-39, Table 2-40, Table 2-44, Table 2-45, Table 2-46, Table 2-50, Table 2-51, Table 2-52, Table 2-56, Table 2-57, Table 2-58, Table 2-61, Table 2-62                                                                                                                                                                                      | 2-26          |

|                               | "LVDS" section: Table 2-65                                                                                                                                                                                                                                                                                                                                                                             | 2-40          |

|                               | "LVPECL" section: Table 2-68                                                                                                                                                                                                                                                                                                                                                                           | 2-42          |

|                               | "Global Tree Timing Characteristics" section: Table 2-80, Table 2-81                                                                                                                                                                                                                                                                                                                                   | 2-59          |

|                               | The "PQ208" section and pin tables are new (SAR 31005).                                                                                                                                                                                                                                                                                                                                                | 5-34          |

|                               | Global clocks were removed from the A2F060 pin table for the "CS288" and "FG256" packages, resulting in changed function names for affected pins (SAR 31033).                                                                                                                                                                                                                                          | 5-43          |

| Revision 5<br>(December 2010) | Table 2-2 • Analog Maximum Ratings was revised. The recommended CM[n] pad voltage (relative to ground) was changed from –11 to –0.3 (SAR 28219).                                                                                                                                                                                                                                                       | 2-2           |

|                               | Table 2-7 • Temperature and Voltage Derating Factors for Timing Delays was revised to change the values for 100°C.                                                                                                                                                                                                                                                                                     | 2-9           |

|                               | Power-down and Sleep modes, and all associated notes, were removed from Table 2-8 • Power Supplies Configuration (SAR 29479). IDC3 and IDC4 were renamed to IDC1 and IDC2 (SAR 29478). These modes are no longer supported. A note was added to the table stating that current monitors and temperature monitors should not be used when Power-down and/or Sleep mode are required by the application. | 2-10          |

|                               | The "Power-Down and Sleep Mode Implementation" section was deleted (SAR 29479).                                                                                                                                                                                                                                                                                                                        | N/A           |

|                               | Values for PAC9 and PAC10 for LVDS and LVPECL were revised in Table 2-10 • Summary of I/O Input Buffer Power (per pin) – Default I/O Software Settings and Table 2-12 • Summary of I/O Output Buffer Power (per pin) – Default I/O Software Settings*.                                                                                                                                                 | 2-10,<br>2-11 |

|                               | Values for PAC1 through PAC4, PDC1, and PDC2 were added for A2F500 in Table 2-14 • Different Components Contributing to Dynamic Power Consumption in SmartFusion cSoCs and Table 2-15 • Different Components Contributing to the Static Power Consumption in SmartFusion cSoCs                                                                                                                         | 2-12,<br>2-13 |

|                               | The equation for "Total Dynamic Power Consumption— $P_{DYN}$ " in "SoC Mode" was revised to add $P_{MSS}$ . The "Microcontroller Subsystem Dynamic Contribution— $P_{MSS}$ " section is new (SAR 29462).                                                                                                                                                                                               | 2-14,<br>2-18 |

|                               | Information in Table 2-24 • Summary of I/O Timing Characteristics—Software Default Settings (applicable to FPGA I/O banks) and Table 2-25 • Summary of I/O Timing Characteristics—Software Default Settings (applicable to MSS I/O banks) was updated.                                                                                                                                                 | 2-25          |

# **Microsemi**.

SmartFusion Customizable System-on-Chip (cSoC)

| Revision                       | Changes                                                                                                                                                                                                                                                                                           | Page            |

|--------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------|

| Revision 5<br>(continued)      | Available values for the Std. speed were added to the timing tables from Table 2-38 • 3.3 V LVTTL / 3.3 V LVCMOS High Slew to Table 2-92 • JTAG 1532 (SAR 29331).                                                                                                                                 | 2-31 to<br>2-76 |

|                                | One or more values changed for the –1 speed in tables covering 3.3 V LVCMOS, 2.5 V LVCMOS, 1.8 V LVCMOS, 1.5 V LVCMOS, Combinatorial Cell Propagation Delays, and A2F200 Global Resources.                                                                                                        |                 |

|                                | Table 2-80 • A2F500 Global Resource is new.                                                                                                                                                                                                                                                       | 2-60            |

|                                | Table 2-90 • eNVM Block Timing, Worst Commercial Case Conditions: $T_J = 85^{\circ}C$ , VCC = 1.425 V was revised (SAR 27585).                                                                                                                                                                    | 2-76            |

|                                | The programmable analog specifications tables were revised with updated information.                                                                                                                                                                                                              | 2-78 to<br>2-87 |

|                                | Table 4-1 • Supported JTAG Programming Hardware was revised by adding a note to indicate "planned support" for several of the items in the table.                                                                                                                                                 | 4-7             |

|                                | The note on JTAGSEL in the "In-System Programming" section was revised to state that SoftConsole selects the appropriate TAP controller using the CTXSELECT JTAG command. When using SoftConsole, the state of JTAGSEL is a "don't care" (SAR 29261).                                             | 4-7             |

|                                | The "CS288" and "FG256" pin tables for A2F060 are new, comparing the A2F060 function with the A2F200 function (SAR 29353).                                                                                                                                                                        | 5-24            |

|                                | The "Handling When Unused" column was removed from the "FG256" pin table for A2F200 and A2F500 (SAR 29691).                                                                                                                                                                                       | 5-42            |

| Revision 4<br>(September 2010) | Table 2-8 • Power Supplies Configuration was revised. VCCRCOSC was moved to a column of its own with new values. VCCENVM was added to the table. Standby mode for VJTAG and VPP was changed from 0 V to N/A. "Disable" was changed to "Off" in the eNVM column. The column for RCOSC was deleted. | 2-10            |

|                                | The "Power-Down and Sleep Mode Implementation" section was revised to include VCCROSC.                                                                                                                                                                                                            | 2-11            |

| Revision 3<br>(September 2010) | The "I/Os and Operating Voltage" section was revised to list "single 3.3 V power supply with on-chip 1.5 V regulator" and "external 1.5 V is allowed" (SAR 27663).                                                                                                                                | I               |

|                                | The CS288 package was added to the "Package I/Os: MSS + FPGA I/Os" table (SAR 27101), "Product Ordering Codes" table, and "Temperature Grade Offerings" table (SAR 27044). The number of direct analog inputs for the FG256 package in A2F060 was changed from 8 to 6.                            | III, VI, VI     |

|                                | Two notes were added to the "SmartFusion cSoC Family Product Table" indicating limitations for features of the A2F500 device:                                                                                                                                                                     | II              |

|                                | Two PLLs are available in CS288 and FG484 (one PLL in FG256).<br>[ADCs, DACs, SCBs, comparators, current monitors, and bipolar high voltage<br>monitors are] Available on FG484 only. FG256 and CS288 packages offer the same<br>programmable analog capabilities as A2F200.                      |                 |

|                                | Table cells were merged in rows containing the same values for easier reading (SAR 24748).                                                                                                                                                                                                        |                 |

|                                | The security feature option was added to the "Product Ordering Codes" table.                                                                                                                                                                                                                      | VI              |