Welcome to **E-XFL.COM**

Embedded - System On Chip (SoC): The Heart of Modern Embedded Systems

Embedded - System On Chip (SoC) refers to an integrated circuit that consolidates all the essential components of a computer system into a single chip. This includes a microprocessor, memory, and other peripherals, all packed into one compact and efficient package. SoCs are designed to provide a complete computing solution, optimizing both space and power consumption, making them ideal for a wide range of embedded applications.

What are **Embedded - System On Chip (SoC)**?

**System On Chip (SoC)** integrates multiple functions of a computer or electronic system onto a single chip. Unlike traditional multi-chip solutions. SoCs combine a central

| Details                 |                                                                  |

|-------------------------|------------------------------------------------------------------|

| Product Status          | Obsolete                                                         |

| Architecture            | MCU, FPGA                                                        |

| Core Processor          | ARM® Cortex®-M3                                                  |

| Flash Size              | 128KB                                                            |

| RAM Size                | 16KB                                                             |

| Peripherals             | DMA, POR, WDT                                                    |

| Connectivity            | EBI/EMI, I <sup>2</sup> C, SPI, UART/USART                       |

| Speed                   | 100MHz                                                           |

| Primary Attributes      | ProASIC®3 FPGA, 60K Gates, 1536D-Flip-Flops                      |

| Operating Temperature   | -40°C ~ 100°C (TJ)                                               |

| Package / Case          | 144-LQFP                                                         |

| Supplier Device Package | 144-TQFP (20x20)                                                 |

| Purchase URL            | https://www.e-xfl.com/product-detail/microsemi/a2f060m3e-1tq144i |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

# Package I/Os: MSS + FPGA I/Os

| Device                  |                 | A2F060 <sup>1</sup> |                 |       | <b>A2F200</b> <sup>2</sup> |       |       |                 | A2F500 <sup>2</sup> |       |       |  |

|-------------------------|-----------------|---------------------|-----------------|-------|----------------------------|-------|-------|-----------------|---------------------|-------|-------|--|

| Package                 | TQ144           | CS288               | FG256           | PQ208 | CS288                      | FG256 | FG484 | PQ208           | CS288               | FG256 | FG484 |  |

| Direct Analog Inputs    | 11              | 11                  | 11              | 8     | 8                          | 8     | 8     | 8               | 8                   | 8     | 12    |  |

| Shared Analog Inputs    | 4               | 4                   | 4               | 16    | 16                         | 16    | 16    | 16              | 16                  | 16    | 20    |  |

| Total Analog Inputs     | 15              | 15                  | 15              | 24    | 24                         | 24    | 24    | 24              | 24                  | 24    | 32    |  |

| Analog Outputs          | 1               | 1                   | 1               | 1     | 2                          | 2     | 2     | 1               | 2                   | 2     | 3     |  |

| MSS I/Os <sup>3,4</sup> | 21 <sup>5</sup> | 28 <sup>5</sup>     | 26 <sup>5</sup> | 22    | 31                         | 25    | 41    | 22              | 31                  | 25    | 41    |  |

| FPGA I/Os               | 33 <sup>6</sup> | 68                  | 66              | 66    | 78                         | 66    | 94    | 66 <sup>6</sup> | 78                  | 66    | 128   |  |

| Total I/Os              | 70              | 112                 | 108             | 113   | 135                        | 117   | 161   | 113             | 135                 | 117   | 204   |  |

#### Notes:

- 1. There are no LVTTL capable direct inputs available on A2F060 devices.

- 2. These pins are shared between direct analog inputs to the ADCs and voltage/current/temperature monitors.

- 3. 16 MSS I/Os are multiplexed and can be used as FPGA I/Os, if not needed for MSS. These I/Os support Schmitt triggers and support only LVTTL and LVCMOS (1.5 / 1.8 / 2.5, 3.3 V) standards.

- 9 MSS I/Os are primarily for 10/100 Ethernet MAC and are also multiplexed and can be used as FPGA I/Os if Ethernet MAC is not used in a design. These I/Os support Schmitt triggers and support only LVTTL and LVCMOS (1.5 / 1.8 / 2.5, 3.3 V standards.

- 5. 10/100 Ethernet MAC is not available on A2F060.

- 6. EMC is not available on the A2F500 PQ208 and A2F060 TQ144 package.

Table 1 • SmartFusion cSoC Package Sizes Dimensions

| Package                         | TQ144   | PQ208   | CS288   | FG256   | FG484   |

|---------------------------------|---------|---------|---------|---------|---------|

| Length × Width (mm\mm)          | 20 × 20 | 28 × 28 | 11 × 11 | 17 × 17 | 23 × 23 |

| Nominal Area (mm <sup>2</sup> ) | 400     | 784     | 121     | 289     | 529     |

| Pitch (mm)                      | 0.5     | 0.5     | 0.5     | 1.0     | 1.0     |

| Height (mm)                     | 1.40    | 3.40    | 1.05    | 1.60    | 2.23    |

# **SmartFusion cSoC Device Status**

| Device | Status                                 |

|--------|----------------------------------------|

| A2F060 | Preliminary: CS288, FG256, TQ144       |

| A2F200 | Production: CS288, FG256, FG484, PQ208 |

| A2F500 | Production: CS288, FG256, FG484, PQ208 |

Revision 13 III

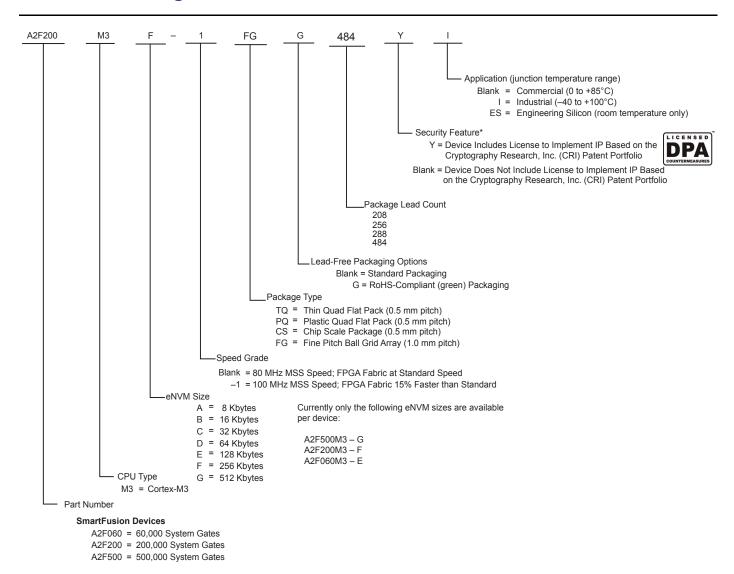

# **Product Ordering Codes**

Note: \*Most devices in the SmartFusion cSoC family can be ordered with the Y suffix. Devices with a package size greater or equal to 5x5 mm are supported. Contact your local Microsemi SoC Products Group sales representative for more information.

# **Temperature Grade Offerings**

| SmartFusion cSoC | A2F060 | A2F200 | A2F500 |

|------------------|--------|--------|--------|

| TQ144            | C, I   | -      | -      |

| PQ208            | -      | C, I   | C, I   |

| CS288            | C, I   | C, I   | C, I   |

| FG256            | C, I   | C, I   | C, I   |

| FG484            | -      | C, I   | C, I   |

#### Notes:

- 1. C = Commercial Temperature Range: 0°C to 85°C Junction

- 2. I = Industrial Temperature Range: -40°C to 100°C Junction

VI Revision 13

| SmartFusion Family Overview                                                                       |

|---------------------------------------------------------------------------------------------------|

| Introduction                                                                                      |

| SmartFusion DC and Switching Characteristics                                                      |

| General Specifications                                                                            |

| Calculating Power Dissipation                                                                     |

| User I/O Characteristics                                                                          |

| VersaTile Characteristics                                                                         |

| Global Resource Characteristics                                                                   |

| RC Oscillator                                                                                     |

| Main and Lower Power Crystal Oscillator       2-62         Clock Conditioning Circuits       2-63 |

| FPGA Fabric SRAM and FIFO Characteristics                                                         |

| Embedded Nonvolatile Memory Block (eNVM)                                                          |

| Embedded FlashROM (eFROM)                                                                         |

| JTAG 1532 Characteristics                                                                         |

| Programmable Analog Specifications 2-78                                                           |

| Serial Peripheral Interface (SPI) Characteristics                                                 |

| Inter-Integrated Circuit (I <sup>2</sup> C) Characteristics                                       |

| SmartFusion Development Tools                                                                     |

| Types of Design Tools                                                                             |

| SmartFusion Ecosystem                                                                             |

| Middleware                                                                                        |

| References                                                                                        |

| SmartEugian Dragramming                                                                           |

| SmartFusion Programming In-System Programming                                                     |

| In-System Programming4-7 In-Application Programming4-8                                            |

| Typical Programming and Erase Times                                                               |

| References                                                                                        |

|                                                                                                   |

| Pin Descriptions                                                                                  |

| Supply Pins                                                                                       |

| User-Defined Supply Pins   5-5     Global I/O Naming Conventions   5-6                            |

| User Pins                                                                                         |

| Special Function Pins                                                                             |

| JTAG Pins                                                                                         |

| Microcontroller Subsystem (MSS) 5-12                                                              |

| Analog Front-End (AFE)                                                                            |

| Analog Front-End Pin-Level Function Multiplexing 5-16                                             |

| TQ144 5-18                                                                                        |

| CS288                                                                                             |

| PQ208                                                                                             |

| FG256                                                                                             |

| 7-0404 5-52                                                                                       |

| Datasheet Information                                                                             |

| List of Changes                                                                                   |

Table 2-14 • Different Components Contributing to Dynamic Power Consumption in SmartFusion cSoCs

|           |                                                      | Power Supply                |        |        |        |        |       |

|-----------|------------------------------------------------------|-----------------------------|--------|--------|--------|--------|-------|

| Parameter | Definition                                           | Name                        | Domain | A2F060 | A2F200 | A2F500 | Units |

| PAC24     | Current Monitor Power Contribution                   | See Table 2-93 on page 2-78 | _      |        | 1.03   |        | mW    |

| PAC25     | ABPS Power Contribution                              | See Table 2-96 on page 2-82 | _      |        | 0.70   |        | mW    |

| PAC26     | Sigma-Delta DAC Power<br>Contribution <sup>2</sup>   | See Table 2-98 on page 2-85 | _      |        | 0.58   |        | mW    |

| PAC27     | Comparator Power Contribution                        | See Table 2-97 on page 2-84 | _      |        | 1.02   |        | mW    |

| PAC28     | Voltage Regulator Power<br>Contribution <sup>3</sup> | See Table 2-99 on page 2-87 | _      |        | 36.30  |        | mW    |

- 1. For a different use of MSS peripherals and resources, refer to SmartPower.

- 2. Assumes Input = Half Scale Operation mode.

- 3. Assumes 100 mA load on 1.5 V domain.

Table 2-15 • Different Components Contributing to the Static Power Consumption in SmartFusion cSoCs

|           |                                                                      | Power Supp                 | oly Device |            |            |           |         |

|-----------|----------------------------------------------------------------------|----------------------------|------------|------------|------------|-----------|---------|

| Parameter | Definition                                                           | Name                       | Domain     | A2F060     | A2F200     | A2F200    | Units   |

| PDC1      | Core static power contribution in SoC mode                           | VCC                        | 1.5 V      | 11.10      | 23.70      | 37.95     | mW      |

| PDC2      | Device static power contribution in Standby Mode                     | See Table 2-8 on page 2-10 | _          | 11.10      | 23.70      | 37.95     | mW      |

| PDC3      | Device static power contribution in<br>Time Keeping mode             | See Table 2-8 on page 2-10 | 3.3 V      | 33.00      | 33.00      | 33.00     | μW      |

| PDC7      | Static contribution per input pin (standard dependent contribution)  | VCCxxxxIOBx/VCC            | See Tabl   | e 2-10 and | d Table 2- | 11 on pag | e 2-11. |

| PDC8      | Static contribution per output pin (standard dependent contribution) | VCCxxxxIOBx/VCC            | See Tabl   | e 2-12 and | d Table 2- | 13 on pag | e 2-11. |

| PDC9      | Static contribution per PLL                                          | VCC                        | 1.5 V      | 2.55       | 2.55       | 2.55      | mW      |

Table 2-16 • eNVM Dynamic Power Consumption

| Parameter   | Description                     | Condition      | Min. | Тур.                         | Max. | Units  |

|-------------|---------------------------------|----------------|------|------------------------------|------|--------|

| eNVM System | eNVM array operating power      | Idle           |      | 795                          |      | μA     |

|             |                                 | Read operation | See  | See Table 2-14 on page 2-12. |      |        |

|             |                                 | Erase          |      | 900                          |      | μA     |

|             |                                 | Write          |      | 900                          |      | μA     |

| PNVMCTRL    | eNVM controller operating power |                |      | 20                           |      | μW/MHz |

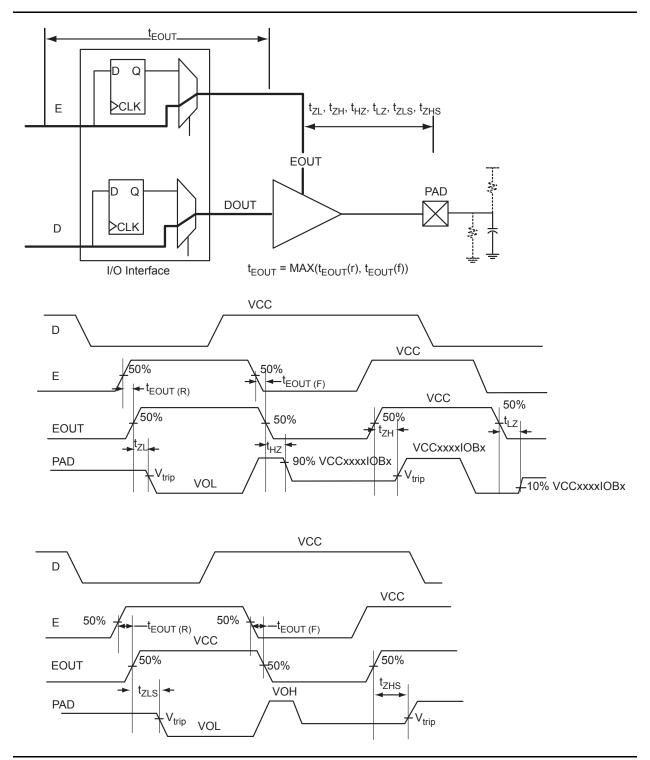

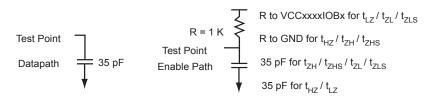

Figure 2-5 • Tristate Output Buffer Timing Model and Delays (example)

2-22 Revision 13

### 1.8 V LVCMOS

Low-voltage CMOS for 1.8 V is an extension of the LVCMOS standard (JESD8-5) used for general-purpose 1.8 V applications. It uses a 1.8 V input buffer and a push-pull output buffer.

Table 2-47 • Minimum and Maximum DC Input and Output Levels

Applicable to FPGA I/O Banks

| 1.8 V<br>LVCMOS   |           | VIL                   | VIH                   |           | VOL       | VOH                   | I <sub>OL</sub> | I <sub>OH</sub> | I <sub>OSL</sub>        | I <sub>osh</sub>        | I <sub>IL</sub> | I <sub>IH</sub> |

|-------------------|-----------|-----------------------|-----------------------|-----------|-----------|-----------------------|-----------------|-----------------|-------------------------|-------------------------|-----------------|-----------------|

| Drive<br>Strength | Min.<br>V | Max.<br>V             | Min.<br>V             | Max.<br>V | Max.<br>V | Min.<br>V             | mΑ              | mA              | Max.<br>mA <sup>1</sup> | Max.<br>mA <sup>1</sup> | μ <b>Α</b> 2    | μΑ <sup>2</sup> |

| 2 mA              | -0.3      | 0.35 *<br>VCCxxxxIOBx | 0.65 *<br>VCCxxxxIOBx | 1.9       | 0.45      | VCCxxxxIOBx<br>- 0.45 | 2               | 2               | 11                      | 9                       | 15              | 15              |

| 4 mA              | -0.3      | 0.35 *<br>VCCxxxxIOBx | 0.65 *<br>VCCxxxxIOBx | 1.9       | 0.45      | VCCxxxxIOBx<br>- 0.45 | 4               | 4               | 22                      | 17                      | 15              | 15              |

| 6 mA              | -0.3      | 0.35 *<br>VCCxxxxIOBx | 0.65 *<br>VCCxxxxIOBx | 1.9       | 0.45      | VCCxxxxIOBx<br>- 0.45 | 6               | 6               | 44                      | 35                      | 15              | 15              |

| 8 mA              | -0.3      | 0.35 *<br>VCCxxxxIOBx | 0.65 *<br>VCCxxxxIOBx | 1.9       | 0.45      | VCCxxxxIOBx<br>- 0.45 | 8               | 8               | 51                      | 45                      | 15              | 15              |

| 12 mA             | -0.3      | 0.35 *<br>VCCxxxxIOBx | 0.65 *<br>VCCxxxxIOBx | 1.9       | 0.45      | VCCxxxxIOBx<br>- 0.45 | 12              | 12              | 74                      | 91                      | 15              | 15              |

| 16 mA             | -0.3      | 0.35 *<br>VCCxxxxIOBx | 0.65 *<br>VCCxxxxIOBx | 1.9       | 0.45      | VCCxxxxIOBx<br>- 0.45 | 16              | 16              | 74                      | 91                      | 15              | 15              |

#### Notes:

- 1. Currents are measured at high temperature (100°C junction temperature) and maximum voltage.

- 2. Currents are measured at 85°C junction temperature.

- 3. Software default selection highlighted in gray.

Table 2-48 • Minimum and Maximum DC Input and Output Levels

Applicable to MSS I/O Banks

| 1.8 V<br>LVCMOS   |           | VIL                   | VIH                   |           | VOL       | VOH                   | l <sub>OL</sub> | I <sub>OH</sub> | I <sub>OSL</sub>        | I <sub>OSH</sub>        | I <sub>IL</sub> | I <sub>IH</sub> |

|-------------------|-----------|-----------------------|-----------------------|-----------|-----------|-----------------------|-----------------|-----------------|-------------------------|-------------------------|-----------------|-----------------|

| Drive<br>Strength | Min.<br>V | Max.<br>V             | Min.<br>V             | Max.<br>V | Max.<br>V | Min.<br>V             | mA              | mA              | Max.<br>mA <sup>1</sup> | Max.<br>mA <sup>1</sup> | μA <sup>2</sup> | μA <sup>2</sup> |

| 4 mA              | -0.3      | 0.35 *<br>VCCxxxxIOBx | 0.65 *<br>VCCxxxxIOBx | 3.6       | 0.45      | VCCxxxxIOBx<br>- 0.45 | 4               | 4               | 22                      | 17                      | 15              | 15              |

#### Notes:

- 1. Currents are measured at high temperature (100°C junction temperature) and maximum voltage.

- 2. Currents are measured at 85°C junction temperature.

- 3. Software default selection highlighted in gray.

Figure 2-8 • AC Loading

Table 2-49 • AC Waveforms, Measuring Points, and Capacitive Loads

| Input Low (V) | Input High (V) | Measuring Point* (V) | V <sub>REF</sub> (typ.) (V) | C <sub>LOAD</sub> (pF) |

|---------------|----------------|----------------------|-----------------------------|------------------------|

| 0             | 1.8            | 0.9                  | -                           | 35                     |

<sup>\*</sup> Measuring point =  $V_{trip.}$  See Table 2-22 on page 2-24 for a complete table of trip points.

2-34 Revision 13

SmartFusion DC and Switching Characteristics

## Table 2-52 • 1.8 V LVCMOS High Slew

Worst Commercial-Case Conditions:  $T_J$  = 85°C, Worst-Case VCC = 1.425 V, Worst-Case VCCxxxxIOBx = 1.7 V Applicable to MSS I/O Banks

| Drive<br>Strength | Speed<br>Grade | t <sub>DOUT</sub> | t <sub>DP</sub> | t <sub>DIN</sub> | t <sub>PY</sub> | t <sub>PYS</sub> | t <sub>EOUT</sub> | t <sub>ZL</sub> | t <sub>ZH</sub> | t <sub>LZ</sub> | t <sub>HZ</sub> | Units |

|-------------------|----------------|-------------------|-----------------|------------------|-----------------|------------------|-------------------|-----------------|-----------------|-----------------|-----------------|-------|

| 4 mA              | Std.           | 0.22              | 2.77            | 0.09             | 1.09            | 1.64             | 0.22              | 2.82            | 2.72            | 2.21            | 2.25            | ns    |

|                   | <b>–</b> 1     | 0.18              | 2.31            | 0.07             | 0.91            | 1.37             | 0.18              | 2.35            | 2.27            | 1.84            | 1.87            | ns    |

### Notes:

- 1. Software default selection highlighted in gray.

- 2. For specific junction temperature and voltage supply levels, refer to Table 2-7 on page 2-9 for derating values.

2-36 Revision 13

Table 2-63 • LVDS Minimum and Maximum DC Input and Output Levels

| DC Parameter                 | Description                 | Min.  | Тур.  | Max.  | Units |

|------------------------------|-----------------------------|-------|-------|-------|-------|

| VCCFPGAIOBx                  | Supply voltage              | 2.375 | 2.5   | 2.625 | V     |

| VOL                          | Output low voltage          | 0.9   | 1.075 | 1.25  | V     |

| VOH                          | Output high voltage         | 1.25  | 1.425 | 1.6   | V     |

| I <sub>OL</sub> <sup>1</sup> | Output lower current        | 0.65  | 0.91  | 1.16  | mA    |

| I <sub>OH</sub> <sup>1</sup> | Output high current         | 0.65  | 0.91  | 1.16  | mA    |

| VI                           | Input voltage               | 0     |       | 2.925 | V     |

| I <sub>IH</sub> <sup>2</sup> | Input high leakage current  |       |       | 15    | μA    |

| I <sub>IL</sub> <sup>2</sup> | Input low leakage current   |       |       | 15    | μΑ    |

| V <sub>ODIFF</sub>           | Differential output voltage | 250   | 350   | 450   | mV    |

| V <sub>OCM</sub>             | Output common mode voltage  | 1.125 | 1.25  | 1.375 | V     |

| V <sub>ICM</sub>             | Input common mode voltage   | 0.05  | 1.25  | 2.35  | V     |

| V <sub>IDIFF</sub>           | Input differential voltage  | 100   | 350   |       | mV    |

- 1.  $I_{OL}/I_{OH}$  defined by  $V_{ODIFF}$ /(resistor network).

- 2. Currents are measured at 85°C junction temperature.

Table 2-64 • AC Waveforms, Measuring Points, and Capacitive Loads

| Input Low (V) | Input High (V) | Measuring Point* (V) | V <sub>REF</sub> (typ.) (V) |  |

|---------------|----------------|----------------------|-----------------------------|--|

| 1.075         | 1.325          | Cross point          | -                           |  |

<sup>\*</sup> Measuring point =  $V_{trip.}$  See Table 2-22 on page 2-24 for a complete table of trip points.

### **Timing Characteristics**

#### Table 2-65 • LVDS

Worst Commercial-Case Conditions:  $T_J$  = 85°C, Worst-Case VCC = 1.425 V, Worst-Case VCCFPGAIOBx = 2.3 V

Applicable to FPGA I/O Banks, I/O Assigned to EMC I/O Pins

| Speed Grade | t <sub>DOUT</sub> | t <sub>DP</sub> | t <sub>DIN</sub> | t <sub>PY</sub> | Units |

|-------------|-------------------|-----------------|------------------|-----------------|-------|

| Std.        | 0.60              | 1.83            | 0.04             | 1.87            | ns    |

| <b>–</b> 1  | 0.50              | 1.53            | 0.03             | 1.55            | ns    |

### Notes:

- For the derating values at specific junction temperature and voltage supply levels, refer to Table 2-7 on page 2-9 for derating values.

- 2. The above mentioned timing parameters correspond to 24mA drive strength.

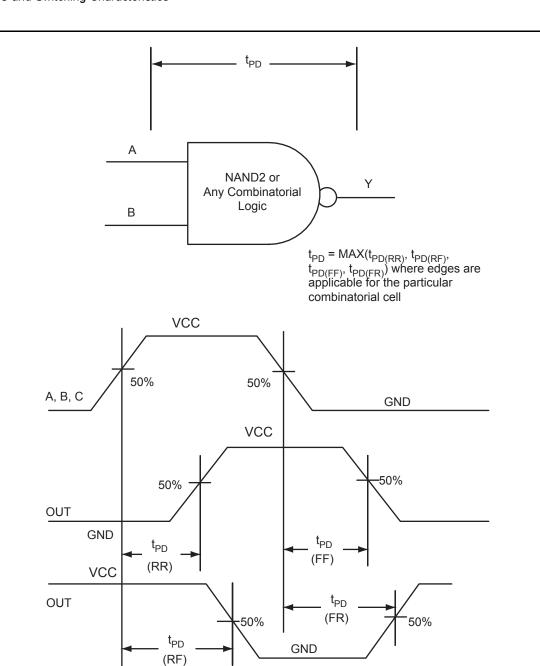

Figure 2-24 • Timing Model and Waveforms

2-56 Revision 13

Table 2-92 • JTAG 1532 Worst Commercial-Case Conditions:  $T_J$  = 85°C, Worst-Case VCC = 1.425 V

| Parameter            | Description           | -1    | Std.  | Units |

|----------------------|-----------------------|-------|-------|-------|

| t <sub>RSTB2Q</sub>  | Reset to Q (data out) | 26.67 | 30.67 | ns    |

| F <sub>TCKMAX</sub>  | TCK Maximum Frequency | 19.00 | 21.85 | MHz   |

| t <sub>TRSTREM</sub> | ResetB Removal Time   | 0.00  | 0.00  | ns    |

| t <sub>TRSTREC</sub> | ResetB Recovery Time  | 0.27  | 0.31  | ns    |

| t <sub>TRSTMPW</sub> | ResetB Minimum Pulse  | TBD   | TBD   | ns    |

Note: For specific junction temperature and voltage supply levels, refer to Table 2-7 on page 2-9 for derating values.

# **Analog Sigma-Delta Digital to Analog Converter (DAC)**

Unless otherwise noted, sigma-delta DAC performance is specified at 25°C with nominal power supply voltages, using the internal sigma-delta modulators with 16-bit inputs, HCLK = 100 MHz, modulator inputs updated at a 100 KHz rate, in voltage output mode with an external 160 pF capacitor to ground, after trimming and digital [pre-]compensation.

Table 2-98 • Analog Sigma-Delta DAC

| Specification                | Test Conditions         | Min.  | Тур.                                    | Max.  | Units |

|------------------------------|-------------------------|-------|-----------------------------------------|-------|-------|

| Resolution                   |                         | 8     |                                         | 24    | Bits  |

| Output range                 |                         |       | 0 to 2.56                               |       | V     |

|                              | Current output mode     |       | 0 to 256                                |       | μΑ    |

| Output Impedance             |                         | 6     | 10                                      | 12    | ΚΩ    |

|                              | Current output mode     | 10    |                                         |       | МΩ    |

| Output voltage compliance    | Current output mode     |       | 0–3.0                                   |       | V     |

|                              | -40°C to +100°C         | 0–2.7 |                                         | 0-3.4 | V     |

| Gain error                   | Voltage output mode     |       | 0.3                                     | ±2    | %     |

|                              | A2F060: -40°C to +100°C |       | 0.3                                     | ±2    | %     |

|                              | A2F200: -40°C to +100°C |       | 1.2                                     | ±5.3  | %     |

|                              | A2F500: -40°C to +100°C |       | 0.3                                     | ±2    | %     |

|                              | Current output mode     |       | 0.3                                     | ±2    | %     |

|                              | A2F060: -40°C to +100°C |       | 0.3                                     | ±2    | %     |

|                              | A2F200: -40°C to +100°C |       | 1.2                                     | ±5.3  | %     |

|                              | A2F500: -40°C to +100°C |       | 0.3                                     | ±2    | %     |

| Output referred offset       | DACBYTE0 = h'00 (8-bit) |       | 0.25                                    | ±1    | mV    |

|                              | -40°C to +100°C         |       | 1                                       | ±2.5  | mV    |

|                              | Current output mode     |       | 0.3                                     | ±1    | μA    |

|                              | -40°C to +100°C         |       | 1                                       | ±2.5  | μΑ    |

| Integral non-linearity       | RMS deviation from BFSL |       | 0.1                                     | 0.3   | % FS* |

| Differential non-linearity   |                         |       | 0.05                                    | 0.4   | % FS* |

| Analog settling time         |                         |       | Refer to<br>Figure 2-44 on<br>page 2-86 |       | μs    |

| Power supply rejection ratio | DC, full scale output   | 33    | 34                                      |       | dB    |

Note: \*FS is full-scale error, defined as the difference between the actual value that triggers the transition to full-scale and the ideal analog full-scale transition value. Full-scale error equals offset error plus gain error. Refer to the Analog-to-Digital Converter chapter of the SmartFusion Programmable Analog User's Guide for more information.

# Inter-Integrated Circuit (I<sup>2</sup>C) Characteristics

This section describes the DC and switching of the  $I^2C$  interface. Unless otherwise noted, all output characteristics given are for a 100 pF load on the pins. For timing parameter definitions, refer to Figure 2-48 on page 2-92.

Table 2-101 •  $I^2C$  Characteristics Commercial Case Conditions:  $T_J = 85^{\circ}C$ ,  $V_{DD} = 1.425 \text{ V}$ , -1 Speed Grade

| Parameter              | Definition                                              | Condition                                    | Value                       | Unit        |

|------------------------|---------------------------------------------------------|----------------------------------------------|-----------------------------|-------------|

| V <sub>IL</sub>        | Minimum input low voltage                               | -                                            | SeeTable 2-36 on page 2-30  | -           |

|                        | Maximum input low voltage                               | -                                            | See Table 2-36              | -           |

| V <sub>IH</sub>        | Minimum input high voltage                              | -                                            | See Table 2-36              | -           |

|                        | Maximum input high voltage                              | -                                            | See Table 2-36              | -           |

| V <sub>OL</sub>        | Maximum output voltage low                              | I <sub>OL</sub> = 8 mA                       | See Table 2-36              | -           |

| I <sub>IL</sub>        | Input current high                                      | -                                            | See Table 2-36              | -           |

| I <sub>IH</sub>        | Input current low                                       | -                                            | See Table 2-36              | -           |

| V <sub>hyst</sub>      | Hysteresis of Schmitt trigger inputs                    | -                                            | See Table 2-33 on page 2-29 | V           |

| T <sub>FALL</sub>      | Fall time <sup>2</sup>                                  | VIHmin to VILMax, C <sub>load</sub> = 400 pF | 15.0                        | ns          |

|                        |                                                         | VIHmin to VILMax, C <sub>load</sub> = 100 pF | 4.0                         | ns          |

| T <sub>RISE</sub>      | Rise time <sup>2</sup>                                  | VILMax to VIHmin, C <sub>load</sub> = 400pF  | 19.5                        | ns          |

|                        |                                                         | VILMax to VIHmin, C <sub>load</sub> = 100pF  | 5.2                         | ns          |

| Cin                    | Pin capacitance                                         | VIN = 0, f = 1.0 MHz                         | 8.0                         | pF          |

| R <sub>pull-up</sub>   | Output buffer maximum pull-down Resistance <sup>1</sup> | -                                            | 50                          | Ω           |

| R <sub>pull-down</sub> | Output buffer maximum pull-up Resistance <sup>1</sup>   | -                                            | 150                         | Ω           |

| D <sub>max</sub>       | Maximum data rate                                       | Fast mode                                    | 400                         | Kbps        |

| t <sub>LOW</sub>       | Low period of I2C_x_SCL <sup>3</sup>                    | -                                            | 1                           | pclk cycles |

| t <sub>HIGH</sub>      | High period of I2C_x_SCL <sup>3</sup>                   | _                                            | 1                           | pclk cycles |

| t <sub>HD;STA</sub>    | START hold time <sup>3</sup>                            | -                                            | 1                           | pclk cycles |

| t <sub>SU;STA</sub>    | START setup time <sup>3</sup>                           | -                                            | 1                           | pclk cycles |

| t <sub>HD;DAT</sub>    | DATA hold time <sup>3</sup>                             | -                                            | 1                           | pclk cycles |

| t <sub>SU;DAT</sub>    | DATA setup time <sup>3</sup>                            | _                                            | 1                           | pclk cycles |

### Notes:

- 1. These maximum values are provided for information only. Minimum output buffer resistance values depend on VCCxxxxIOBx, drive strength selection, temperature, and process. For board design considerations and detailed output buffer resistances, use the corresponding IBIS models located on the SoC Products Group website at http://www.microsemi.com/index.php?option=com\_microsemi&ltemid=489&lang=en&view=salescontact.

- 2. These values are provided for a load of 100 pF and 400 pF. For board design considerations and detailed output buffer resistances, use the corresponding IBIS models located on the SoC Products Group website at <a href="http://www.microsemi.com/index.php?option=com\_microsemi&ltemid=489&lang=en&view=salescontact">http://www.microsemi.com/index.php?option=com\_microsemi&ltemid=489&lang=en&view=salescontact</a>.

- 3. For allowable Pclk configurations, refer to the Inter-Integrated Circuit (I<sup>2</sup>C) Peripherals section in the SmartFusion Microcontroller Subsystem User's Guide.

# Re-Programming the eNVM Blocks Using the Cortex-M3

In this mode the Cortex-M3 is executing the eNVM programming algorithm from eSRAM. Since individual pages (132 bytes) of the eNVM can be write-protected, the programming algorithm software can be protected from inadvertent erasure. When reprogramming the eNVM, both MSS I/Os and FPGA I/Os are available as interfaces for sourcing the new eNVM image. The SoC Products Group provides working example projects for SoftConsole, IAR, and Keil development environments. These can be downloaded via the SoC Products Group Firmware Catalog.

Alternately, the eNVM can be reprogrammed by the Cortex-M3 via the IAP driver. This is necessary when using an encrypted image.

# **Secure Programming**

For background, refer to the "Security in Low Power Flash Devices" chapter of the *Fusion FPGA Fabric User's Guide* on the SoC Products Group website. SmartFusion ISP behaves identically to Fusion ISP. IAP of SmartFusion cSoCs is accomplished by using the IAP driver. Only the FPGA fabric and the eNVM can be reprogrammed with the protection of security measures by using the IAP driver.

# **Typical Programming and Erase Times**

Table 4-3 documents the typical programming and erase times for two components of SmartFusion cSoCs, FPGA fabric and eNVM, using the SoC Products Group's FlashPro hardware and software. These times will be different for other ISP and IAP methods. The **Program** action in FlashPro software includes erase, program, and verify to complete.

The typical programming (including erase) time per page of the eNVM is 8 ms.

Table 4-3 • Typical Programming and Erase Times

|         | FPGA Fabric (seconds) |        |        | eN\    | eNVM (seconds) |        |        | FlashROM (seconds) |        |  |

|---------|-----------------------|--------|--------|--------|----------------|--------|--------|--------------------|--------|--|

|         | A2F060                | A2F200 | A2F500 | A2F060 | A2F200         | A2F500 | A2F060 | A2F200             | A2F500 |  |

| Erase   | 21                    | 21     | 21     | N/A    | N/A            | N/A    | 21     | 21                 | 21     |  |

| Program | 28                    | 35     | 48     | 18     | 39             | 71     | 22     | 22                 | 22     |  |

| Verify  | 2                     | 6      | 12     | 9      | 18             | 37     | 1      | 1                  | 1      |  |

# References

#### **User's Guides**

DirectC User's Guide

http://www.microsemi.com/index.php?option=com\_docman&task=doc\_download&gid=132588 In-System Programming (ISP) of Microsemi's Low-Power Flash Devices Using FlashPro4/3/3X http://www.microsemi.com/index.php?option=com\_docman&task=doc\_download&gid=129973 Programming Flash Devices HandBook

http://www.microsemi.com/index.php?option=com docman&task=doc download&gid=129930

# **Application Notes on IAP Programming Technique**

SmartFusion cSoC: Programming FPGA Fabric and eNVM Using In-Application Programming Interface App Note

http://www.microsemi.com/index.php?option=com\_docman&task=doc\_download&gid=129818 SmartFusion cSoC: Basic Bootloader and Field Upgrade eNVM Through IAP Interface App Note http://www.microsemi.com/index.php?option=com\_docman&task=doc\_download&gid=129823

# **User-Defined Supply Pins**

| Name     | Туре  | Polarity/<br>Bus Size | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

|----------|-------|-----------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| VAREF0   | Input | 1                     | Analog reference voltage for first ADC.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

|          |       |                       | The SmartFusion cSoC can be configured to generate a 2.56 V internal reference that can be used by the ADC. While using the internal reference, the reference voltage is output on the VAREFOUT pin for use as a system reference. If a different reference voltage is required, it can be supplied by an external source and applied to this pin. The valid range of values that can be supplied to the ADC is 1.0 V to 3.3 V. When VAREF0 is internally generated, a bypass capacitor must be connected from this pin to ground. The value of the bypass capacitor should be between 3.3 $\mu\text{F}$ and 22 $\mu\text{F}$ , which is based on the needs of the individual designs. The choice of the capacitor value has an impact on the settling time it takes the VAREF0 signal to reach the required specification of 2.56 V to initiate valid conversions by the ADC. If the lower capacitor value is chosen, the settling time required for VAREF0 to achieve 2.56 V will be shorter than when selecting the larger capacitor value. The above range of capacitor values supports the accuracy specification of the ADC, which is detailed in the datasheet. Designers choosing the smaller capacitor value will not obtain as much margin in the accuracy as that achieved with a larger capacitor value. See the Analog-to-Digital Converter (ADC) section in the SmartFusion Programmable Analog User's Guide for more information. The SoC Products Group recommends customers use 10 $\mu\text{F}$ as the value of the bypass capacitor. Designers choosing to use an extranal VAREF0 pin before initiating conversions by the ADC. To use the internal voltage reference, the VAREFOUT pin must be connected to the appropriate ADC VAREFx input on the PCB. For example, VAREFOUT can be connected to VAREF1 only, if ADC1 alone is used. VAREFOUT can be connected to VAREF1 and VAREF2 together, if ADC0, ADC1, and ADC2 all are used. |

| VAREF1   | Input | 1                     | Analog reference voltage for second ADC See "VAREF0" above for more information.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

| VAREF2   | Input | 1                     | Analog reference voltage for third ADC See "VAREF0" above for more.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

| VAREFOUT | Out   | 1                     | Internal 2.56 V voltage reference output. Can be used to provide the two ADCs with a unique voltage reference externally by connecting VAREFOUT to both VAREF0 and VAREF1. To use the internal voltage reference, you must connect the VAREFOUT pin to the appropriate ADC VAREFx input—either the VAREF0 or VAREF1 pin—on the PCB.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

| Name             | Туре      | Polarity/<br>Bus Size | Description                                                                                                                                   |

|------------------|-----------|-----------------------|-----------------------------------------------------------------------------------------------------------------------------------------------|

| SPI_1_DO         | Out       | 1                     | Data output. Second SPI.                                                                                                                      |

|                  |           |                       | Can also be used as an MSS GPIO (see "GPIO_x" on page 5-6).                                                                                   |

| SPI_1_SS         | Out       | 1                     | Slave select (chip select). Second SPI.                                                                                                       |

|                  |           |                       | Can also be used as an MSS GPIO (see "GPIO_x" on page 5-6).                                                                                   |

| Universal Asynch | ronous Re | ceiver/Trans          | mitter (UART) Peripherals                                                                                                                     |

| UART_0_RXD       | In        | 1                     | Receive data. First UART.                                                                                                                     |

|                  |           |                       | Can also be used as an MSS GPIO (see "GPIO_x" on page 5-6).                                                                                   |

| UART_0_TXD       | Out       | 1                     | Transmit data. First UART.                                                                                                                    |

|                  |           |                       | Can also be used as an MSS GPIO (see "GPIO_x" on page 5-6).                                                                                   |

| UART_1_RXD       | In        | 1                     | Receive data. Second UART.                                                                                                                    |

|                  |           |                       | Can also be used as an MSS GPIO (see "GPIO_x" on page 5-6).                                                                                   |

| UART_1_TXD       | Out       | 1                     | Transmit data. Second UART.                                                                                                                   |

|                  |           |                       | Can also be used as an MSS GPIO (see "GPIO_x" on page 5-6).                                                                                   |

| Ethernet MAC     |           |                       |                                                                                                                                               |

| MAC_CLK          | In        | Rise                  | Receive clock. 50 MHz ± 50 ppm clock source received from RMII PHY.                                                                           |

|                  |           |                       | Can be left floating when unused.                                                                                                             |

| MAC_CRSDV        | In        | High                  | Carrier sense/receive data valid for RMII PHY                                                                                                 |

|                  |           |                       | Can also be used as an FPGA User IO (see "IO" on page 5-6).                                                                                   |

| MAC_MDC          | Out       | Rise                  | RMII management clock                                                                                                                         |

|                  |           |                       | Can also be used as an FPGA User IO (see "IO" on page 5-6).                                                                                   |

| MAC_MDIO         | In/Out    | 1                     | RMII management data input/output                                                                                                             |

|                  |           |                       | Can also be used as an FPGA User IO (see "IO" on page 5-6).                                                                                   |

| MAC_RXDx         | In        | 2                     | Ethernet MAC receive data. Data recovered and decoded by PHY. The RXD[0] signal is the least significant bit.                                 |

|                  |           |                       | Can also be used as an FPGA User I/O (see "IO" on page 5-6).                                                                                  |

| MAC_RXER         | In        | HIGH                  | Ethernet MAC receive error. If MACRX_ER is asserted during reception, the frame is received and status of the frame is updated with MACRX_ER. |

|                  |           |                       | Can also be used as an FPGA user I/O (see "IO" on page 5-6).                                                                                  |

| MAC_TXDx         | Out       | 2                     | Ethernet MAC transmit data. The TXD[0] signal is the least significant bit.                                                                   |

|                  |           |                       | Can also be used as an FPGA user I/O (see "IO" on page 5-6).                                                                                  |

| MAC_TXEN         | Out       | HIGH                  | Ethernet MAC transmit enable. When asserted, indicates valid data for the PHY on the TXD port.                                                |

|                  |           |                       | Can also be used as an FPGA User I/O (see "IO" on page 5-6).                                                                                  |

|            | FG484                     |                           |  |  |  |  |

|------------|---------------------------|---------------------------|--|--|--|--|

| Pin Number | A2F200 Function           | A2F500 Function           |  |  |  |  |

| A1         | GND                       | GND                       |  |  |  |  |

| A2         | NC                        | NC                        |  |  |  |  |

| A3         | NC                        | NC                        |  |  |  |  |

| A4         | GND                       | GND                       |  |  |  |  |

| A5         | EMC_CS0_N/GAB0/IO01NDB0V0 | EMC_CS0_N/GAB0/IO05NDB0V0 |  |  |  |  |

| A6         | EMC_CS1_N/GAB1/IO01PDB0V0 | EMC_CS1_N/GAB1/IO05PDB0V0 |  |  |  |  |

| A7         | GND                       | GND                       |  |  |  |  |

| A8         | EMC_AB[0]/IO04NDB0V0      | EMC_AB[0]/IO06NDB0V0      |  |  |  |  |

| A9         | EMC_AB[1]/IO04PDB0V0      | EMC_AB[1]/IO06PDB0V0      |  |  |  |  |

| A10        | GND                       | GND                       |  |  |  |  |

| A11        | NC                        | NC                        |  |  |  |  |

| A12        | EMC_AB[7]/IO07PDB0V0      | EMC_AB[7]/IO12PDB0V0      |  |  |  |  |

| A13        | GND                       | GND                       |  |  |  |  |

| A14        | EMC_AB[12]/IO10NDB0V0     | EMC_AB[12]/IO14NDB0V0     |  |  |  |  |

| A15        | EMC_AB[13]/IO10PDB0V0     | EMC_AB[13]/IO14PDB0V0     |  |  |  |  |

| A16        | GND                       | GND                       |  |  |  |  |

| A17        | NC                        | IO16NDB0V0                |  |  |  |  |

| A18        | NC                        | IO16PDB0V0                |  |  |  |  |

| A19        | GND                       | GND                       |  |  |  |  |

| A20        | NC                        | NC                        |  |  |  |  |

| A21        | NC                        | NC                        |  |  |  |  |

| A22        | GND                       | GND                       |  |  |  |  |

| AA1        | GPIO_4/IO43RSB4V0         | GPIO_4/IO52RSB4V0         |  |  |  |  |

| AA2        | GPIO_12/IO37RSB4V0        | GPIO_12/IO46RSB4V0        |  |  |  |  |

| AA3        | MAC_MDC/IO48RSB4V0        | MAC_MDC/IO57RSB4V0        |  |  |  |  |

| AA4        | MAC_RXER/IO50RSB4V0       | MAC_RXER/IO59RSB4V0       |  |  |  |  |

| AA5        | MAC_TXD[0]/IO56RSB4V0     | MAC_TXD[0]/IO65RSB4V0     |  |  |  |  |

| AA6        | ABPS0                     | ABPS0                     |  |  |  |  |

| AA7        | TM1                       | TM1                       |  |  |  |  |

| AA8        | ADC1                      | ADC1                      |  |  |  |  |

| AA9        | GND15ADC1                 | GND15ADC1                 |  |  |  |  |

| AA10       | GND33ADC1                 | GND33ADC1                 |  |  |  |  |

| AA11       | CM3                       | CM3                       |  |  |  |  |

| AA12       | GNDTM1                    | GNDTM1                    |  |  |  |  |

- 1. Shading denotes pins that do not have completely identical functions from density to density. For example, the bank assignment can be different for an I/O, or the function might be available only on a larger density device.

- 2. \*: Indicates that the signal assigned to the pins as a CLKBUF/CLKBUF\_LVPECL/CLKBUF\_LVDS goes through a glitchless mux. In order for the glitchless mux to operate correctly, the signal must be a free-running clock signal. Refer to the 'Glitchless MUX' section in the SmartFusion Microcontroller Subsystem User's Guide for more details.

|            | FG484                        |                              |  |  |  |

|------------|------------------------------|------------------------------|--|--|--|

| Pin Number | A2F200 Function              | A2F500 Function              |  |  |  |

| В3         | NC                           | NC                           |  |  |  |

| B4         | NC                           | NC                           |  |  |  |

| B5         | VCCFPGAIOB0                  | VCCFPGAIOB0                  |  |  |  |

| B6         | EMC_RW_N/GAA1/IO00PDB0V0     | EMC_RW_N/GAA1/IO02PDB0V0     |  |  |  |

| B7         | NC                           | IO04PPB0V0                   |  |  |  |

| B8         | VCCFPGAIOB0                  | VCCFPGAIOB0                  |  |  |  |

| B9         | EMC_BYTEN[0]/GAC0/IO02NDB0V0 | EMC_BYTEN[0]/GAC0/IO07NDB0V0 |  |  |  |

| B10        | EMC_AB[2]/IO05NDB0V0         | EMC_AB[2]/IO09NDB0V0         |  |  |  |

| B11        | EMC_AB[3]/IO05PDB0V0         | EMC_AB[3]/IO09PDB0V0         |  |  |  |

| B12        | EMC_AB[6]/IO07NDB0V0         | EMC_AB[6]/IO12NDB0V0         |  |  |  |

| B13        | EMC_AB[14]/IO11NDB0V0        | EMC_AB[14]/IO15NDB0V0        |  |  |  |

| B14        | EMC_AB[15]/IO11PDB0V0        | EMC_AB[15]/IO15PDB0V0        |  |  |  |

| B15        | VCCFPGAIOB0                  | VCCFPGAIOB0                  |  |  |  |

| B16        | EMC_AB[18]/IO13NDB0V0        | EMC_AB[18]/IO18NDB0V0        |  |  |  |

| B17        | EMC_AB[19]/IO13PDB0V0        | EMC_AB[19]/IO18PDB0V0        |  |  |  |

| B18        | VCCFPGAIOB0                  | VCCFPGAIOB0                  |  |  |  |

| B19        | GBB0/IO18NDB0V0              | GBB0/IO24NDB0V0              |  |  |  |

| B20        | GBB1/IO18PDB0V0              | GBB1/IO24PDB0V0              |  |  |  |

| B21        | GND                          | GND                          |  |  |  |

| B22        | GBA2/IO20PDB1V0              | GBA2/IO27PDB1V0              |  |  |  |

| C1         | EMC_DB[14]/GAB2/IO71NDB5V0   | EMC_DB[14]/GAB2/IO88NDB5V0   |  |  |  |

| C2         | NC                           | NC                           |  |  |  |

| C3         | NC                           | NC                           |  |  |  |

| C4         | NC                           | IO01NDB0V0                   |  |  |  |

| C5         | NC                           | IO01PDB0V0                   |  |  |  |

| C6         | EMC_CLK/GAA0/IO00NDB0V0      | EMC_CLK/GAA0/IO02NDB0V0      |  |  |  |

| C7         | NC                           | IO03PPB0V0                   |  |  |  |

| C8         | NC                           | IO04NPB0V0                   |  |  |  |

| C9         | EMC_BYTEN[1]/GAC1/IO02PDB0V0 | EMC_BYTEN[1]/GAC1/IO07PDB0V0 |  |  |  |

| C10        | EMC_OEN1_N/IO03PDB0V0        | EMC_OEN1_N/IO08PDB0V0        |  |  |  |

| C11        | GND                          | GND                          |  |  |  |

| C12        | VCCFPGAIOB0                  | VCCFPGAIOB0                  |  |  |  |

| C13        | EMC_AB[8]/IO08NDB0V0         | EMC_AB[8]/IO13NDB0V0         |  |  |  |

| C14        | EMC_AB[16]/IO12NDB0V0        | EMC_AB[16]/IO17NDB0V0        |  |  |  |

- 1. Shading denotes pins that do not have completely identical functions from density to density. For example, the bank assignment can be different for an I/O, or the function might be available only on a larger density device.

- 2. \*: Indicates that the signal assigned to the pins as a CLKBUF/CLKBUF\_LVPECL/CLKBUF\_LVDS goes through a glitchless mux. In order for the glitchless mux to operate correctly, the signal must be a free-running clock signal. Refer to the 'Glitchless MUX' section in the SmartFusion Microcontroller Subsystem User's Guide for more details.

|            | FG484           |                 |  |

|------------|-----------------|-----------------|--|

| Pin Number | A2F200 Function | A2F500 Function |  |

| L9         | VCC             | VCC             |  |

| L10        | GND             | GND             |  |

| L11        | VCC             | VCC             |  |

| L12        | GND             | GND             |  |

| L13        | VCC             | VCC             |  |

| L14        | GND             | GND             |  |

| L15        | VCC             | VCC             |  |

| L16        | GND             | GND             |  |

| L17        | GNDQ            | GNDQ            |  |

| L18        | GDA2/IO33NDB1V0 | GDA2/IO42NDB1V0 |  |

| L19        | VCCFPGAIOB1     | VCCFPGAIOB1     |  |

| L20        | GDB1/IO30PDB1V0 | GDB1/IO39PDB1V0 |  |

| L21        | GDB0/IO30NDB1V0 | GDB0/IO39NDB1V0 |  |

| L22        | GDC2/IO32PDB1V0 | GDC2/IO41PDB1V0 |  |

| M1         | NC              | IO71PDB5V0      |  |

| M2         | NC              | IO71NDB5V0      |  |

| M3         | VCCFPGAIOB5     | VCCFPGAIOB5     |  |

| M4         | NC              | IO72NPB5V0      |  |

| M5         | GNDQ            | GNDQ            |  |

| M6         | NC              | IO68PDB5V0      |  |

| M7         | GND             | GND             |  |

| M8         | VCC             | VCC             |  |

| M9         | GND             | GND             |  |

| M10        | VCC             | VCC             |  |

| M11        | GND             | GND             |  |

| M12        | VCC             | VCC             |  |

| M13        | GND             | GND             |  |

| M14        | VCC             | VCC             |  |

| M15        | GND             | GND             |  |

| M16        | VCCFPGAIOB1     | VCCFPGAIOB1     |  |

| M17        | NC              | NC              |  |

| M18        | GDB2/IO33PDB1V0 | GDB2/IO42PDB1V0 |  |

| M19        | VJTAG           | VJTAG           |  |

| M20        | GND             | GND             |  |

- 1. Shading denotes pins that do not have completely identical functions from density to density. For example, the bank assignment can be different for an I/O, or the function might be available only on a larger density device.

- 2. \*: Indicates that the signal assigned to the pins as a CLKBUF/CLKBUF\_LVPECL/CLKBUF\_LVDS goes through a glitchless mux. In order for the glitchless mux to operate correctly, the signal must be a free-running clock signal. Refer to the 'Glitchless MUX' section in the SmartFusion Microcontroller Subsystem User's Guide for more details.

## Datasheet Information

| Revision               | Changes                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | Page |

|------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------|

| Revision 3 (continued) | In Table 2-3 • Recommended Operating Conditions <sup>5,6</sup> , the VDDBAT recommended operating range was changed from "2.97 to 3.63" to "2.7 to 3.63" (SAR 25246). Recommended operating range was changed to "3.15 to 3.45" for the following voltages:  VCC33A  VCC33AP  VCC33SDDx  VCCMAINXTAL  VCCLPXTAL  Two notes were added to the table (SAR 27109):  1. The following 3.3 V supplies should be connected together while following proper noise filtering practices: VCC33A, VCC33ADCx, VCC33AP, VCC33SDDx, VCCMAINXTAL, and VCCLPXTAL.  2. The following 1.5 V supplies should be connected together while following proper | 2-3  |

|                        | noise filtering practices: VCC, VCC15A, and VCC15ADCx.  In Table 2-3 • Recommended Operating Conditions <sup>5,6</sup> , the description for VCCLPXTAL was corrected to change "32 Hz" to "32 KHz" (SAR 27110).                                                                                                                                                                                                                                                                                                                                                                                                                         | 2-3  |

|                        | The "Power Supply Sequencing Requirement" section is new (SAR 27178).                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | 2-4  |

|                        | Table 2-8 • Power Supplies Configuration was revised to change most on/off entries to voltages. Note 5 was added, stating that "on" means proper voltage is applied. The values of 6 $\mu$ A and 16 $\mu$ A were removed for IDC1 and IDC2 for 3.3 V. A note was added for IDC1 and IDC2: "Power mode and Sleep mode are consuming higher current than expected in the current version of silicon. These specifications will be updated when new version of the silicon is available" (SAR 27926).                                                                                                                                      | 2-10 |

|                        | The "Power-Down and Sleep Mode Implementation" section is new (SAR 27178).                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 2-11 |

|                        | A note was added to Table 2-86 • SmartFusion CCC/PLL Specification, pertaining to $f_{out\_CCC}$ , stating that "one of the CCC outputs (GLA0) is used as an MSS clock and is limited to 100 MHz (maximum) by software" (SAR 26388).                                                                                                                                                                                                                                                                                                                                                                                                    | 2-63 |

|                        | Table 2-90 • eNVM Block Timing, Worst Commercial Case Conditions: $T_J$ = 85°C, VCC = 1.425 V was revised. Values were included for A2F200 and A2F500, for -1 and Std. speed grades. A note was added to define 6:1:1:1 and 5:1:1:1 (SAR 26166).                                                                                                                                                                                                                                                                                                                                                                                        | 2-76 |

|                        | The units were corrected (mV instead of V) for input referred offset voltage, GDEC[1:0] = 00 in Table 2-96 • ABPS Performance Specifications (SAR 25381).                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | 2-82 |

|                        | The test condition values for operating current (ICC33A, typical) were changed in Table 2-99 • Voltage Regulator (SAR 26465).                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | 2-87 |

|                        | Figure 2-45 • Typical Output Voltage was revised to add legends for the three curves, stating the load represented by each (SAR 25247).                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | 2-88 |

|                        | The "SmartFusion Programming" chapter was moved to this document from the SmartFusion Subsystem Microcontroller User's Guide (SAR 26542). The "Typical Programming and Erase Times" section was added to this chapter.                                                                                                                                                                                                                                                                                                                                                                                                                  | 4-7  |

|                        | Figure 4-1 • TRSTB Logic was revised to change 1.5 V to "VJTAG (1.5 V to 3.3 V nominal)" (SAR 24694).                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | 4-8  |

6-10 Revision 13