Welcome to E-XFL.COM

#### Embedded - System On Chip (SoC): The Heart of Modern Embedded Systems

**Embedded - System On Chip (SoC)** refers to an integrated circuit that consolidates all the essential components of a computer system into a single chip. This includes a microprocessor, memory, and other peripherals, all packed into one compact and efficient package. SoCs are designed to provide a complete computing solution, optimizing both space and power consumption, making them ideal for a wide range of embedded applications.

#### What are **Embedded - System On Chip (SoC)**?

**System On Chip (SoC)** integrates multiple functions of a computer or electronic system onto a single chip. Unlike traditional multi-chip solutions. SoCs combine a central

#### Details

| 2014110                 |                                                                |

|-------------------------|----------------------------------------------------------------|

| Product Status          | Obsolete                                                       |

| Architecture            | MCU, FPGA                                                      |

| Core Processor          | ARM® Cortex®-M3                                                |

| Flash Size              | 128KB                                                          |

| RAM Size                | 16KB                                                           |

| Peripherals             | DMA, POR, WDT                                                  |

| Connectivity            | EBI/EMI, I <sup>2</sup> C, SPI, UART/USART                     |

| Speed                   | 80MHz                                                          |

| Primary Attributes      | ProASIC®3 FPGA, 60K Gates, 1536D-Flip-Flops                    |

| Operating Temperature   | 0°C ~ 85°C (TJ)                                                |

| Package / Case          | 288-TFBGA, CSPBGA                                              |

| Supplier Device Package | 288-CSP (11x11)                                                |

| Purchase URL            | https://www.e-xfl.com/product-detail/microsemi/a2f060m3e-cs288 |

|                         |                                                                |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

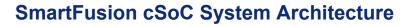

Note: Architecture for A2F200

| Symbol                   | Paramete                              | Commercial                    | Industrial     | Units          |    |

|--------------------------|---------------------------------------|-------------------------------|----------------|----------------|----|

| TJ                       | Junction temperature                  |                               | 0 to +85       | -40 to +100    | °C |

| VCC <sup>2</sup>         | 1.5 V DC core supply voltage          |                               | 1.425 to 1.575 | 1.425 to 1.575 | V  |

| VJTAG                    | JTAG DC voltage                       |                               | 1.425 to 3.6   | 1.425 to 3.6   | V  |

| VPP                      | Programming voltage                   | Programming mode <sup>3</sup> | 3.15 to 3.45   | 3.15 to 3.45   | V  |

|                          |                                       | Operation <sup>4</sup>        | 0 to 3.6       | 0 to 3.6       | V  |

| VCCPLLx                  | Analog power supply (PLL)             | •                             | 1.425 to 1.575 | 1.425 to 1.575 | V  |

| VCCFPGAIOBx/             | 1.5 V DC supply voltage               |                               | 1.425 to 1.575 | 1.425 to 1.575 | V  |

| VCCMSSIOBx <sup>5</sup>  | 1.8 V DC supply voltage               |                               | 1.7 to 1.9     | 1.7 to 1.9     | V  |

|                          | 2.5 V DC supply voltage               |                               | 2.3 to 2.7     | 2.3 to 2.7     | V  |

|                          | 3.3 V DC supply voltage               |                               | 3.0 to 3.6     | 3.0 to 3.6     | V  |

|                          | LVDS differential I/O                 |                               | 2.375 to 2.625 | 2.375 to 2.625 | V  |

|                          | LVPECL differential I/O               |                               | 3.0 to 3.6     | 3.0 to 3.6     | V  |

| VCC33A <sup>6</sup>      | Analog clean 3.3 V supply to t        | he analog circuitry           | 3.15 to 3.45   | 3.15 to 3.45   | V  |

| VCC33ADCx <sup>6</sup>   | Analog 3.3 V supply to ADC            |                               | 3.15 to 3.45   | V              |    |

| VCC33AP <sup>6</sup>     | Analog clean 3.3 V supply to t        | he charge pump                | 3.15 to 3.45   | 3.15 to 3.45   | V  |

| VCC33SDDx <sup>6</sup>   | Analog 3.3 V supply to sigma-         | delta DAC                     | 3.15 to 3.45   | 3.15 to 3.45   | V  |

| VAREFx                   | Voltage reference for ADC             |                               | 2.527 to 3.3   | 2.527 to 3.3   | V  |

| VCCRCOSC                 | Analog supply to the integrate        | d RC oscillator               | 3.15 to 3.45   | 3.15 to 3.45   | V  |

| VDDBAT                   | External battery supply               |                               | 2.7 to 3.63    | 2.7 to 3.63    | V  |

| VCCMAINXTAL <sup>6</sup> | Analog supply to the main cry         | stal oscillator               | 3.15 to 3.45   | 3.15 to 3.45   | V  |

| VCCLPXTAL <sup>6</sup>   | Analog supply to the low p oscillator | ower 32 KHz crystal           | 3.15 to 3.45   | 3.15 to 3.45   | V  |

| VCCENVM                  | Embedded nonvolatile memor            | y supply                      | 1.425 to 1.575 | 1.425 to 1.575 | V  |

| VCCESRAM                 | Embedded SRAM supply                  |                               | 1.425 to 1.575 | 1.425 to 1.575 | V  |

| VCC15A <sup>2</sup>      | Analog 1.5 V supply to the an         | alog circuitry                | 1.425 to 1.575 | 1.425 to 1.575 | V  |

| VCC15ADCx <sup>2</sup>   | Analog 1.5 V supply to the AD         | OC                            | 1.425 to 1.575 | 1.425 to 1.575 | V  |

#### Table 2-3 • Recommended Operating Conditions<sup>5,6</sup>

Notes:

1. All parameters representing voltages are measured with respect to GND unless otherwise specified.

2. The following 1.5 V supplies should be connected together while following proper noise filtering practices: VCC, VCC15A, and VCC15ADCx.

3. The Programming temperature range supported is  $T_{ambient} = 0^{\circ}C$  to 85°C.

4. VPP can be left floating during operation (not programming mode).

5. The ranges given here are for power supplies only. The recommended input voltage ranges specific to each I/O standard are given in Table 2-19 on page 2-23. VCCxxxxIOBx should be at the same voltage within a given I/O bank.

6. The following 3.3 V supplies should be connected together while following proper noise filtering practices: VCC33A, VCC33ADCx, VCC33ADCx, VCC33SDDx, VCCMAINXTAL, and VCCLPXTAL.

## **Microsemi**.

SmartFusion DC and Switching Characteristics

| Product Grade | Storage Temperature         | Element        | Grade Programming<br>Cycles | Retention |

|---------------|-----------------------------|----------------|-----------------------------|-----------|

| Commercial    | Min. T <sub>J</sub> = 0°C   | FPGA/FlashROM  | 500                         | 20 years  |

|               | Max. T <sub>J</sub> = 85°C  | Embedded Flash | < 1,000                     | 20 years  |

|               |                             |                | < 10,000                    | 10 years  |

|               |                             |                | < 15,000                    | 5 years   |

| Industrial    | Min. $T_J = -40^{\circ}C$   | FPGA/FlashROM  | 500                         | 20 years  |

|               | Max. T <sub>J</sub> = 100°C | Embedded Flash | < 1,000                     | 20 years  |

|               |                             |                | < 10,000                    | 10 years  |

|               |                             |                | < 15,000                    | 5 years   |

#### Table 2-4 • FPGA and Embedded Flash Programming, Storage and Operating Limits

#### Table 2-5 • Overshoot and Undershoot Limits <sup>1</sup>

| VCCxxxxlOBx   | Average VCCxxxxlOBx–GND Overshoot or Undershoot<br>Duration as a Percentage of Clock Cycle <sup>2</sup> | Maximum Overshoot/<br>Undershoot <sup>2</sup> |

|---------------|---------------------------------------------------------------------------------------------------------|-----------------------------------------------|

| 2.7 V or less | 10%                                                                                                     | 1.4 V                                         |

|               | 5%                                                                                                      | 1.49 V                                        |

| 3 V           | 10%                                                                                                     | 1.1 V                                         |

|               | 5%                                                                                                      | 1.19 V                                        |

| 3.3 V         | 10%                                                                                                     | 0.79 V                                        |

|               | 5%                                                                                                      | 0.88 V                                        |

| 3.6 V         | 10%                                                                                                     | 0.45 V                                        |

|               | 5%                                                                                                      | 0.54 V                                        |

Notes:

1. Based on reliability requirements at 85°C.

2. The duration is allowed at one out of six clock cycles. If the overshoot/undershoot occurs at one out of two cycles, the maximum overshoot/undershoot has to be reduced by 0.15 V.

3. This table does not provide PCI overshoot/undershoot limits.

## **Power Supply Sequencing Requirement**

SmartFusion cSoCs have an on-chip 1.5 V regulator, but usage of an external 1.5 V supply is also allowed while the on-chip regulator is disabled. In that case, the 3.3 V supplies (VCC33A, etc.) should be powered before 1.5 V (VCC, etc.) supplies. The 1.5 V supplies should be enabled only after 3.3 V supplies reach a value higher than 2.7 V.

# I/O Power-Up and Supply Voltage Thresholds for Power-On Reset (Commercial and Industrial)

Sophisticated power-up management circuitry is designed into every SmartFusion cSoC. These circuits ensure easy transition from the powered-off state to the powered-up state of the device. In addition, the I/O will be in a known state through the power-up sequence. The basic principle is shown in Figure 2-1 on page 2-6.

There are five regions to consider during power-up.

SmartFusion I/Os are activated only if ALL of the following three conditions are met:

- 1. VCC and VCCxxxxIOBx are above the minimum specified trip points (Figure 2-1 on page 2-6).

- 2. VCCxxxxIOBx > VCC 0.75 V (typical)

- 3. Chip is in the SoC Mode.

SmartFusion DC and Switching Characteristics

## **Power Calculation Methodology**

This section describes a simplified method to estimate power consumption of an application. For more accurate and detailed power estimations, use the SmartPower tool in the Libero SoC software.

The power calculation methodology described below uses the following variables:

- The number of PLLs/CCCs as well as the number and the frequency of each output clock generated

- · The number of combinatorial and sequential cells used in the design

- · The internal clock frequencies

- · The number and the standard of I/O pins used in the design

- · The number of RAM blocks used in the design

- · The number of eNVM blocks used in the design

- The analog block used in the design, including the temperature monitor, current monitor, ABPS, sigma-delta DAC, comparator, low power crystal oscillator, RC oscillator and the main crystal oscillator

- Toggle rates of I/O pins as well as VersaTiles—guidelines are provided in Table 2-17 on page 2-18.

- Enable rates of output buffers—guidelines are provided for typical applications in Table 2-18 on page 2-18.

- Read rate and write rate to the memory—guidelines are provided for typical applications in Table 2-18 on page 2-18.

- Read rate to the eNVM blocks

The calculation should be repeated for each clock domain defined in the design.

#### Methodology

#### Total Power Consumption—P<sub>TOTAL</sub>

#### SoC Mode, Standby Mode, and Time Keeping Mode.

$P_{TOTAL} = P_{STAT} + P_{DYN}$

P<sub>STAT</sub> is the total static power consumption.

P<sub>DYN</sub> is the total dynamic power consumption.

#### Total Static Power Consumption—P<sub>STAT</sub>

#### SoC Mode

$\mathsf{P}_{\mathsf{STAT}} = \mathsf{P}_{\mathsf{DC1}} + (\mathsf{N}_{\mathsf{INPUTS}} * \mathsf{P}_{\mathsf{DC7}}) + (\mathsf{N}_{\mathsf{OUTPUTS}} * \mathsf{P}_{\mathsf{DC8}}) + (\mathsf{N}_{\mathsf{PLLS}} * \mathsf{P}_{\mathsf{DC9}})$

N<sub>INPUTS</sub> is the number of I/O input buffers used in the design.

N<sub>OUTPUTS</sub> is the number of I/O output buffers used in the design.

N<sub>PLLS</sub> is the number of PLLs available in the device.

#### Standby Mode

$P_{STAT} = P_{DC2}$

#### Time Keeping Mode

$P_{STAT} = P_{DC3}$

Total Dynamic Power Consumption—P<sub>DYN</sub>

#### SoC Mode

P<sub>DYN</sub> = P<sub>CLOCK</sub> + P<sub>S-CELL</sub> + P<sub>C-CELL</sub> + P<sub>NET</sub> + P<sub>INPUTS</sub> + P<sub>OUTPUTS</sub> + P<sub>MEMORY</sub> + P<sub>PLL</sub> + P<sub>eNVM</sub> + P<sub>XTL-OSC</sub> + P<sub>RC-OSC</sub> + P<sub>AB</sub> + P<sub>LPXTAL-OSC</sub> + P<sub>MSS</sub>

#### Standby Mode

$P_{DYN} = P_{RC-OSC} + P_{LPXTAL-OSC}$

#### Time Keeping Mode

$P_{DYN} = P_{LPXTAL-OSC}$

#### **Global Clock Dynamic Contribution**—**P**<sub>CLOCK</sub>

#### SoC Mode

$P_{CLOCK} = (P_{AC1} + N_{SPINE} * P_{AC2} + N_{ROW} * PAC3 + N_{S-CELL} * P_{AC4}) * F_{CLK}$

N<sub>SPINE</sub> is the number of global spines used in the user design—guidelines are provided in the "Device Architecture" chapter of the *SmartFusion FPGA Fabric User's Guide.*

N<sub>ROW</sub> is the number of VersaTile rows used in the design—guidelines are provided in the "Device Architecture" chapter of the *SmartFusion FPGA Fabric User's Guide*.

F<sub>CLK</sub> is the global clock signal frequency.

N<sub>S-CELL</sub> is the number of VersaTiles used as sequential modules in the design.

#### Standby Mode and Time Keeping Mode

$P_{CLOCK} = 0 W$

#### Sequential Cells Dynamic Contribution—P<sub>S-CELL</sub>

#### SoC Mode

$P_{S-CELL} = N_{S-CELL} * (P_{AC5} + (\alpha_1 / 2) * P_{AC6}) * F_{CLK}$

$N_{S-CELL}$  is the number of VersaTiles used as sequential modules in the design. When a multi-tile sequential cell is used, it should be accounted for as 1.

$\alpha_1$  is the toggle rate of VersaTile outputs—guidelines are provided in Table 2-17 on page 2-18.

F<sub>CLK</sub> is the global clock signal frequency.

#### Standby Mode and Time Keeping Mode

$P_{S-CELL} = 0 W$

#### Combinatorial Cells Dynamic Contribution—P<sub>C-CELL</sub>

#### SoC Mode

$P_{C-CELL} = N_{C-CELL} * (\alpha_1 / 2) * P_{AC7} * F_{CLK}$

N<sub>C-CELL</sub> is the number of VersaTiles used as combinatorial modules in the design.

$\alpha_1$  is the toggle rate of VersaTile outputs—guidelines are provided in Table 2-17 on page 2-18.

F<sub>CLK</sub> is the global clock signal frequency.

#### Standby Mode and Time Keeping Mode

$P_{C-CELL} = 0 W$

#### Routing Net Dynamic Contribution—P<sub>NET</sub>

#### SoC Mode

$\mathsf{P}_{\mathsf{NET}} = (\mathsf{N}_{\mathsf{S}\text{-}\mathsf{CELL}} + \mathsf{N}_{\mathsf{C}\text{-}\mathsf{CELL}}) * (\alpha_1 / 2) * \mathsf{P}_{\mathsf{AC8}} * \mathsf{F}_{\mathsf{CLK}}$

N<sub>S-CELL</sub> is the number VersaTiles used as sequential modules in the design.

$N_{C\mbox{-}C\mbox{-}E\mbox{-}L\mbox{-}L}$  is the number of VersaTiles used as combinatorial modules in the design.

$\alpha_1$  is the toggle rate of VersaTile outputs—guidelines are provided in Table 2-17 on page 2-18.

F<sub>CLK</sub> is the frequency of the clock driving the logic including these nets.

SmartFusion Customizable System-on-Chip (cSoC)

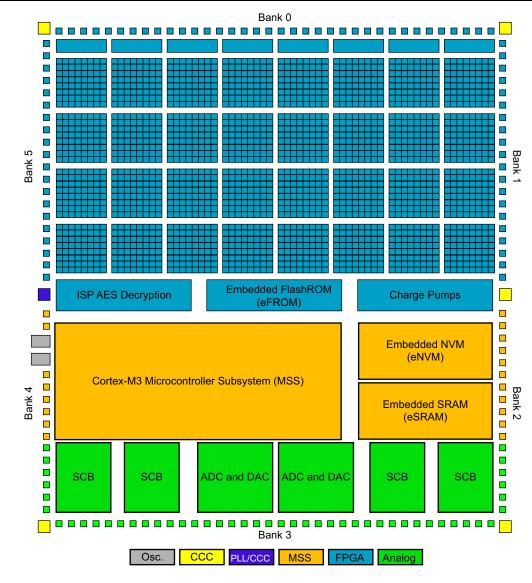

Figure 2-4 • Output Buffer Model and Delays (example)

## **Overview of I/O Performance**

## Summary of I/O DC Input and Output Levels – Default I/O Software Settings

#### Table 2-19 • Summary of Maximum and Minimum DC Input and Output Levels Applicable to Commercial Conditions—Software Default Settings Applicable to FPGA I/O Banks

|                               |                  |      |      | VIL                   | VIH                  |           | VOL                   | VOH                   | I <sub>OL</sub> <sup>1</sup> | I <sub>OH</sub> 1 |

|-------------------------------|------------------|------|------|-----------------------|----------------------|-----------|-----------------------|-----------------------|------------------------------|-------------------|

| I/O Standard                  | Drive<br>Strgth. |      |      | Max.<br>V             | Min.<br>V            | Max.<br>V | Max.<br>V             | Min.<br>V             | mA                           | mA                |

| 3.3 V LVTTL /<br>3.3 V LVCMOS | 12 mA            | High | -0.3 | 0.8                   | 2                    | 3.6       | 0.4                   | 2.4                   | 12                           | 12                |

| 2.5 V LVCMOS                  | 12 mA            | High | -0.3 | 0.7                   | 1.7                  | 3.6       | 0.7                   | 1.7                   | 12                           | 12                |

| 1.8 V LVCMOS                  | 12 mA            | High | -0.3 | 0.35 *<br>VCCxxxxIOBx | 0.65*<br>VCCxxxxIOBx | 3.6       | 0.45                  | VCCxxxxIOBx<br>- 0.45 | 12                           | 12                |

| 1.5 V LVCMOS                  | 12 mA            | High | -0.3 | 0.35 *<br>VCCxxxxIOBx | 0.65*<br>VCCxxxxIOBx | 3.6       | 0.25 *<br>VCCxxxxIOBx | 0.75*<br>VCCxxxxIOBx  | 12                           | 12                |

| 3.3 V PCI                     |                  | -    |      |                       | Per PCI spec         | cificatio | ons                   | -                     | -                            | -                 |

| 3.3 V PCI-X                   |                  |      |      |                       | Per PCI-X spe        | ecificat  | tions                 |                       |                              |                   |

Notes:

1. Currents are measured at 85°C junction temperature.

2. Output slew rate can be extracted by the IBIS Models.

# Table 2-20 • Summary of Maximum and Minimum DC Input and Output Levels Applicable to Commercial Conditions—Software Default Settings Applicable to MSS I/O Banks

|                               |                  |              | VIL  |                      | VIH                  |           | VOL                  | VOH                   | I <sub>OL</sub> <sup>1</sup> | I <sub>OH</sub> 1 |

|-------------------------------|------------------|--------------|------|----------------------|----------------------|-----------|----------------------|-----------------------|------------------------------|-------------------|

| I/O Standard                  | Drive<br>Strgth. | Slew<br>Rate |      | Max.<br>V            | Min.<br>V            | Max.<br>V | Max.<br>V            | Min.<br>V             | mA                           | mA                |

| 3.3 V LVTTL /<br>3.3 V LVCMOS | 8 mA             | High         | -0.3 | 0.8                  | 2                    | 3.6       | 0.4                  | 2.4                   | 8                            | 8                 |

| 2.5 V LVCMOS                  | 8 mA             | High         | -0.3 | 0.7                  | 1.7                  | 3.6       | 0.7                  | 1.7                   | 8                            | 8                 |

| 1.8 V LVCMOS                  | 4 mA             | High         | -0.3 | 0.35*<br>VCCxxxxIOBx | 0.65*<br>VCCxxxxIOBx | 3.6       | 0.45                 | VCCxxxxIOBx<br>- 0.45 | 4                            | 4                 |

| 1.5 V LVCMOS                  | 2 mA             | High         | -0.3 | 0.35*<br>VCCxxxxIOBx | 0.65*<br>VCCxxxxIOBx | 3.6       | 0.25*<br>VCCxxxxIOBx | 0.75*<br>VCCxxxxIOBx  | 2                            | 2                 |

Notes:

1. Currents are measured at 85°C junction temperature.

2. Output slew rate can be extracted by the IBIS Models.

#### Table 2-24 • Summary of I/O Timing Characteristics—Software Default Settings

-1 Speed Grade, Worst Commercial-Case Conditions:  $T_J = 85^{\circ}C$ , Worst Case VCC = 1.425 V, Worst-Case VCCxxxxIOBx (per standard)

| Applicable to FPGA I/O Banks, Assigned to EMC I/O Pins |

|--------------------------------------------------------|

|--------------------------------------------------------|

| I/O Standard                  | Drive Strength    | Slew Rate | Capacitive Load (pF) | External Resistor ( $\Omega$ ) | t <sub>DOUT</sub> (ns) | t <sub>DP</sub> (ns) | t <sub>DIN</sub> (ns) | t <sub>PY</sub> (ns) | t <sub>EoUT</sub> (ns) | t <sub>ZL</sub> (ns) | t <sub>ZH</sub> (ns) | t <sub>LZ</sub> (ns) | t <sub>HZ</sub> (ns) | t <sub>ZLS</sub> (ns) | t <sub>ZHS</sub> (ns) | Units |

|-------------------------------|-------------------|-----------|----------------------|--------------------------------|------------------------|----------------------|-----------------------|----------------------|------------------------|----------------------|----------------------|----------------------|----------------------|-----------------------|-----------------------|-------|

| 3.3 V LVTTL /<br>3.3 V LVCMOS | 12 mA             | High      | 35                   | -                              | 0.50                   | 2.81                 | 0.03                  | 0.81                 | 0.32                   | 2.86                 | 2.23                 | 2.55                 | 2.82                 | 4.58                  | 3.94                  | ns    |

| 2.5 V LVCMOS                  | 12 mA             | High      | 35                   | -                              | 0.50                   | 2.73                 | 0.03                  | 1.03                 | 0.32                   | 2.88                 | 2.69                 | 2.62                 | 2.70                 | 4.60                  | 4.41                  | ns    |

| 1.8 V LVCMOS                  | 12 mA             | High      | 35                   | -                              | 0.50                   | 2.81                 | 0.03                  | 0.95                 | 0.32                   | 2.87                 | 2.38                 | 2.92                 | 3.18                 | 4.58                  | 4.10                  | ns    |

| 1.5 V LVCMOS                  | 12 mA             | High      | 35                   | -                              | 0.50                   | 3.24                 | 0.03                  | 1.12                 | 0.32                   | 3.30                 | 2.79                 | 3.10                 | 3.27                 | 5.02                  | 4.50                  | ns    |

| 3.3 V PCI                     | Per PCI spec      | High      | 10                   | 25 <sup>1</sup>                | 0.50                   | 2.11                 | 0.03                  | 0.68                 | 0.32                   | 2.15                 | 1.57                 | 2.55                 | 2.82                 | 3.87                  | 3.28                  | ns    |

| 3.3 V PCI-X                   | Per PCI-X<br>spec | High      | 10                   | 25 <sup>1</sup>                | 0.50                   | 2.11                 | 0.03                  | 0.64                 | 0.32                   | 2.15                 | 1.57                 | 2.55                 | 2.82                 | 3.87                  | 3.28                  | ns    |

| LVDS                          | 24 mA             | High      | -                    | _                              | 0.50                   | 1.53                 | 0.03                  | 1.55                 | _                      | -                    | -                    | -                    | _                    | _                     | -                     | ns    |

| LVPECL                        | 24 mA             | High      | _                    | _                              | 0.50                   | 1.46                 | 0.03                  | 1.46                 | _                      | _                    | _                    | _                    | _                    | _                     | -                     | ns    |

Notes:

1. Resistance is used to measure I/O propagation delays as defined in PCI specifications. See Figure 2-10 on page 2-39 for connectivity. This resistor is not required during normal operation.

2. For specific junction temperature and voltage supply levels, refer to Table 2-7 on page 2-9 for derating values.

#### Table 2-25 • Summary of I/O Timing Characteristics—Software Default Settings

-1 Speed Grade, Worst Commercial-Case Conditions: T<sub>J</sub> = 85°C, Worst Case VCC = 1.425 V, Worst-Case VCCxxxxIOBx (per standard)

| I/O Standard                  | Drive Strength | Slew Rate | Capacitive Load (pF) | External Resistor | t <sub>bour</sub> (ns) | t <sub>DP</sub> (ns) | t <sub>DIN</sub> (ns) | t <sub>pY</sub> (ns) | t <sub>pYS</sub> (ns) | t <sub>EOUT</sub> (ns) | t <sub>zL</sub> (ns) | t <sub>ZH</sub> (ns) | t <sub>LZ</sub> (ns) | t <sub>HZ</sub> (ns) | Units |

|-------------------------------|----------------|-----------|----------------------|-------------------|------------------------|----------------------|-----------------------|----------------------|-----------------------|------------------------|----------------------|----------------------|----------------------|----------------------|-------|

| 3.3 V LVTTL /<br>3.3 V LVCMOS | 8 mA           | High      | 10                   | -                 | 0.18                   | 1.92                 | 0.07                  | 0.78                 | 1.09                  | 0.18                   | 1.96                 | 1.55                 | 1.83                 | 2.04                 | ns    |

| 2.5 V LVCMOS                  | 8 mA           | High      | 10                   | -                 | 0.18                   | 1.96                 | 0.07                  | 0.99                 | 1.16                  | 0.18                   | 2.00                 | 1.82                 | 1.82                 | 1.93                 | ns    |

| 1.8 V LVCMOS                  | 4 mA           | High      | 10                   | 1                 | 0.18                   | 2.31                 | 0.07                  | 0.91                 | 1.37                  | 0.18                   | 2.35                 | 2.27                 | 1.84                 | 1.87                 | ns    |

| 1.5 V LVCMOS                  | 2 mA           | High      | 10                   | -                 | 0.18                   | 2.70                 | 0.07                  | 1.07                 | 1.55                  | 0.18                   | 2.75                 | 2.67                 | 1.87                 | 1.85                 | ns    |

Notes:

1. Resistance is used to measure I/O propagation delays as defined in PCI specifications. See Figure 2-10 on page 2-39 for connectivity. This resistor is not required during normal operation.

2. For specific junction temperature and voltage supply levels, refer to Table 2-7 on page 2-9 for derating values.

| DC Parameter                 | Description                 | Min.  | Тур.  | Max.  | Units |

|------------------------------|-----------------------------|-------|-------|-------|-------|

| VCCFPGAIOBx                  | Supply voltage              | 2.375 | 2.5   | 2.625 | V     |

| VOL                          | Output low voltage          | 0.9   | 1.075 | 1.25  | V     |

| VOH                          | Output high voltage         | 1.25  | 1.425 | 1.6   | V     |

| I <sub>OL</sub> <sup>1</sup> | Output lower current        | 0.65  | 0.91  | 1.16  | mA    |

| I <sub>OH</sub> <sup>1</sup> | Output high current         | 0.65  | 0.91  | 1.16  | mA    |

| VI                           | Input voltage               | 0     |       | 2.925 | V     |

| I <sub>IH</sub> <sup>2</sup> | Input high leakage current  |       |       | 15    | μΑ    |

| I <sub>IL</sub> <sup>2</sup> | Input low leakage current   |       |       | 15    | μA    |

| V <sub>ODIFF</sub>           | Differential output voltage | 250   | 350   | 450   | mV    |

| V <sub>OCM</sub>             | Output common mode voltage  | 1.125 | 1.25  | 1.375 | V     |

| V <sub>ICM</sub>             | Input common mode voltage   | 0.05  | 1.25  | 2.35  | V     |

| V <sub>IDIFF</sub>           | Input differential voltage  | 100   | 350   |       | mV    |

Notes:

1.  $I_{OL}/I_{OH}$  defined by  $V_{ODIFF}$  (resistor network).

2. Currents are measured at 85°C junction temperature.

#### Table 2-64 • AC Waveforms, Measuring Points, and Capacitive Loads

| Input Low (V) | Input High (V) | Measuring Point* (V) | V <sub>REF</sub> (typ.) (V) |

|---------------|----------------|----------------------|-----------------------------|

| 1.075         | 1.325          | Cross point          | -                           |

\* Measuring point =  $V_{trip.}$  See Table 2-22 on page 2-24 for a complete table of trip points.

#### **Timing Characteristics**

#### Table 2-65 • LVDS

#### Worst Commercial-Case Conditions: T<sub>J</sub> = 85°C, Worst-Case VCC = 1.425 V, Worst-Case VCCFPGAIOBx = 2.3 V Applicable to FPGA I/O Banks, I/O Assigned to EMC I/O Pins

| Speed Grade | t <sub>DOUT</sub> | t <sub>DP</sub> | t <sub>DIN</sub> | t <sub>PY</sub> | Units |

|-------------|-------------------|-----------------|------------------|-----------------|-------|

| Std.        | 0.60              | 1.83            | 0.04             | 1.87            | ns    |

| -1          | 0.50              | 1.53            | 0.03             | 1.55            | ns    |

Notes:

1. For the derating values at specific junction temperature and voltage supply levels, refer to Table 2-7 on page 2-9 for derating values.

2. The above mentioned timing parameters correspond to 24mA drive strength.

SmartFusion DC and Switching Characteristics

### **Timing Waveforms**

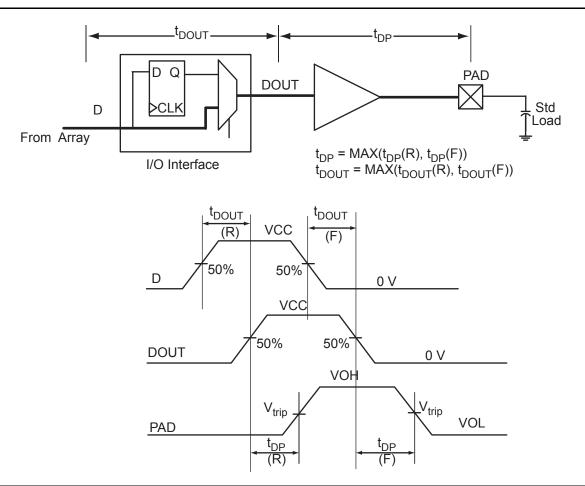

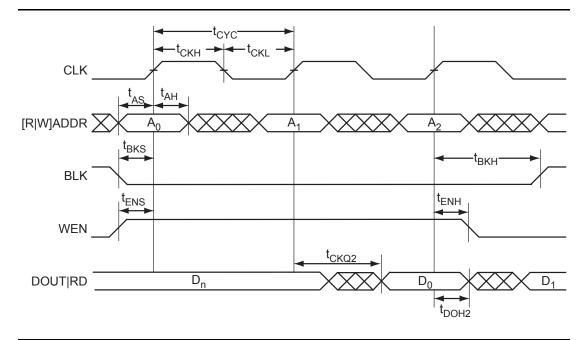

Figure 2-30 • RAM Read for Pass-Through Output. Applicable to both RAM4K9 and RAM512x18.

Figure 2-31 • RAM Read for Pipelined Output Applicable to both RAM4K9 and RAM512x18.

## Analog-to-Digital Converter (ADC)

Unless otherwise noted, ADC direct input performance is specified at 25°C with nominal power supply voltages, with the output measured using the external voltage reference with the internal ADC in 12-bit mode and 500 KHz sampling frequency, after trimming and digital compensation.

| Specification                                                | Test Conditions                                                                | Min. | Тур. | Max. | Units |

|--------------------------------------------------------------|--------------------------------------------------------------------------------|------|------|------|-------|

| Input voltage range (for driving ADC over its full range)    |                                                                                |      | 2.56 |      | V     |

| Gain error                                                   |                                                                                |      | ±0.4 | ±0.7 | %     |

|                                                              | -40°C to +100°C                                                                |      | ±0.4 | ±0.7 | %     |

| Input referred offset voltage                                |                                                                                |      | ±1   | ±2   | mV    |

|                                                              | -40°C to +100°C                                                                |      | ±1   | ±2   |       |

| Integral non-linearity (INL)                                 | RMS deviation from BFSL                                                        |      |      |      |       |

|                                                              | 12-bit mode                                                                    |      | 1.71 |      | LSB   |

|                                                              | 10-bit mode                                                                    |      | 0.60 | 1.00 | LSB   |

|                                                              | 8-bit mode                                                                     |      | 0.2  | 0.33 | LSB   |

| Differential non-linearity (DNL)                             | 12-bit mode                                                                    |      | 2.4  |      | LSB   |

|                                                              | 10-bit mode                                                                    |      | 0.80 | 0.94 | LSB   |

|                                                              | 8-bit mode                                                                     |      | 0.2  | 0.23 | LSB   |

| Signal to noise ratio                                        |                                                                                | 62   | 64   |      | dB    |

| Effective number of bits (ENOB)                              | -1 dBFS input                                                                  |      |      |      |       |

| $ENOB = \frac{SINAD - 1.76 \text{ dB}}{6.02 \text{ dB/bit}}$ | 12-bit mode 10 KHz                                                             | 9.9  | 10   |      | Bits  |

| 6.02 dB/bit                                                  | 12-bit mode 100 KHz                                                            | 9.9  | 10   |      | Bits  |

| EQ 10                                                        | 10-bit mode 10 KHz                                                             | 9.5  | 9.6  |      | Bits  |

|                                                              | 10-bit mode 100 KHz                                                            | 9.5  | 9.6  |      | Bits  |

|                                                              | 8-bit mode 10 KHz                                                              | 7.8  | 7.9  |      | Bits  |

|                                                              | 8-bit mode 100 KHz                                                             | 7.8  | 7.9  |      | Bits  |

| Full power bandwidth                                         | At –3 dB; –1 dBFS input                                                        | 300  |      |      | KHz   |

| Analog settling time                                         | To 0.1% of final value (with 1 Kohm source impedance and with ADC load)        |      | 2    |      | μs    |

| Input capacitance                                            | Switched capacitance (ADC sample capacitor)                                    |      | 12   | 15   | pF    |

|                                                              | Cs: Static capacitance (Figure 2-44 on page 2-86)                              |      |      |      |       |

|                                                              | CM[n] input                                                                    |      | 5    | 7    | pF    |

|                                                              | TM[n] input                                                                    |      | 5    | 7    | pF    |

|                                                              | ADC[n] input                                                                   |      | 5    | 7    | pF    |

| Input resistance                                             | Rin: Series resistance (Figure 2-44)                                           |      | 2    |      | KΩ    |

|                                                              | Rsh: Shunt resistance, exclusive of switched capacitance effects (Figure 2-44) | 10   |      |      | MΩ    |

#### Table 2-95 • ADC Specifications

Note: All 3.3 V supplies are tied together and varied from 3.0 V to 3.6 V. 1.5 V supplies are held constant.

## **3 – SmartFusion Development Tools**

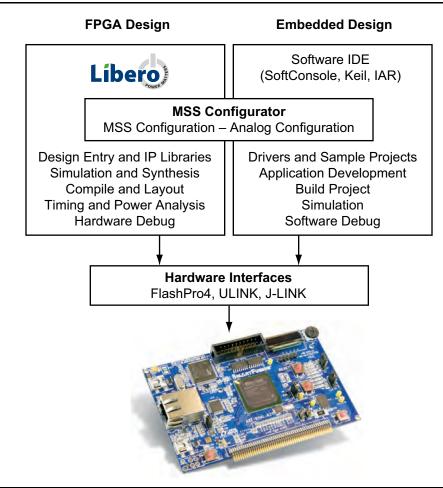

Designing with SmartFusion cSoCs involves three different types of design: FPGA design, embedded design and analog design. These roles can be filled by three different designers, two designers or even a single designer, depending on company structure and project complexity.

## **Types of Design Tools**

Microsemi has developed design tools and flows to meet the needs of these three types of designers so they can work together smoothly on a single project (Figure 3-1).

Figure 3-1 • Three Design Roles

### **FPGA** Design

Libero System-on-Chip (SoC) software is Microsemi's comprehensive software toolset for designing with all Microsemi FPGAs and cSoCs. Libero SoC includes industry-leading synthesis, simulation and debug tools from Synopsys<sup>®</sup> and Mentor Graphics<sup>®</sup>, as well as innovative timing and power optimization and analysis.

Flash File System (RL-Flash) allows your embedded applications to create, save, read, and modify files in standard storage devices such as ROM, RAM, or FlashROM, using a standard serial peripheral interface (SPI). Many ARM-based microcontrollers have a practical requirement for a standard file system. With RL-FlashFS you can implement new features in embedded applications such as data logging, storing program state during standby modes, or storing firmware upgrades.

Micrium, in addition to  $\mu C/OS-III^{(R)}$ , offers the following support for SmartFusion cSoC:

- µC/TCP-IP<sup>™</sup> is a compact, reliable, and high-performance stack built from the ground up by Micrium and has the quality, scalability, and reliability that translates into a rapid configuration of network options, remarkable ease-of-use, and rapid time-to-market.

- µC/Probe<sup>™</sup> is one of the most useful tools in embedded systems design and puts you in the driver's seat, allowing you to take charge of virtually any variable, memory location, and I/O port in your embedded product, while your system is running.

## References

## **PCB** Files

A2F500 SmartFusion Development Kit PCB Files http://www.microsemi.com/index.php?option=com\_docman&task=doc\_download&gid=130770 A2F200 SmartFusion Development Kit PCB Files http://www.microsemi.com/index.php?option=com\_docman&task=doc\_download&gid=130773

## **Application Notes**

*SmartFusion cSoC Board Design Guidelines* http://www.microsemi.com/index.php?option=com\_docman&task=doc\_download&gid=129815

🌜 Microsemi.

SmartFusion Customizable System-on-Chip (cSoC)

| Name        | Туре | Polarity/Bus Size | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

|-------------|------|-------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| NCAP        |      | 1                 | Negative capacitor connection.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

|             |      |                   | This is the negative terminal of the charge pump. A capacitor, with a 2.2 $\mu$ F recommended value, is required to connect between PCAP and NCAP. Analog charge pump capacitors are not needed if none of the analog SCB features are used and none of the SDDs are used. In that case it should be left unconnected.                                                                                                                                                                                                                                                                                                       |

| PCAP        |      | 1                 | Positive Capacitor connection.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

|             |      |                   | This is the positive terminal of the charge pump. A capacitor, with a 2.2 $\mu$ F recommended value, is required to connect between PCAP and NCAP. If this pin is not used, it must be left unconnected/floating. In this case, no capacitor is needed. Analog charge pump capacitors are not needed if none of the analog SCB features are used, and none of the SDDs are used.                                                                                                                                                                                                                                             |

| PTBASE      |      | 1                 | Pass transistor base connection                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

|             |      |                   | This is the control signal of the voltage regulator. This pin should be connected to the base of an external pass transistor used with the 1.5 V internal voltage regulator and can be floating if not used.                                                                                                                                                                                                                                                                                                                                                                                                                 |

| PTEM        |      | 1                 | Pass transistor emitter connection.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

|             |      |                   | This is the feedback input of the voltage regulator.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

|             |      |                   | This pin should be connected to the emitter of an external pass transistor used with the 1.5 V internal voltage regulator and can be floating if not used.                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

| MSS_RESET_N |      | Low               | Low Reset signal which can be used as an external reset and can also<br>be used as a system level reset under control of the Cortex-M3<br>processor. MSS_RESET_N is an output asserted low after power-on<br>reset. The direction of MSS_RESET_N changes during the execution<br>of the Microsemi System Boot when chip-level reset is enabled. The<br>Microsemi System Boot reconfigures MSS_RESET_N to become a<br>reset input signal when chip-level reset is enabled. It has an internal<br>pull-up so it can be left floating. In the current software, the<br>MSS_RESET_N is modeled as an external input signal only. |

| PU_N        | In   | Low               | Push-button is the connection for the external momentary switch used to turn on the 1.5 V voltage regulator and can be floating if not used.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

🌜 Microsemi.

SmartFusion Customizable System-on-Chip (cSoC)

|            | PQ208     |           |  |

|------------|-----------|-----------|--|

| Pin Number | A2F200    | A2F500    |  |

| 63         | TM1       | TM1       |  |

| 64         | CM1       | CM1       |  |

| 65         | ABPS3     | ABPS3     |  |

| 66         | ABPS2     | ABPS2     |  |

| 67         | ADC0      | ADC0      |  |

| 68         | ADC1      | ADC1      |  |

| 69         | ADC2      | ADC2      |  |

| 70         | ADC3      | ADC3      |  |

| 71         | VAREF0    | VAREF0    |  |

| 72         | GND33ADC0 | GND33ADC0 |  |

| 73         | VCC33ADC0 | VCC33ADC0 |  |

| 74         | GND33ADC0 | GND33ADC0 |  |

| 75         | VCC15ADC0 | VCC15ADC0 |  |

| 76         | GND15ADC0 | GND15ADC0 |  |

| 77         | GND15ADC1 | GND15ADC1 |  |

| 78         | VCC15ADC1 | VCC15ADC1 |  |

| 79         | GND33ADC1 | GND33ADC1 |  |

| 80         | VCC33ADC1 | VCC33ADC1 |  |

| 81         | GND33ADC1 | GND33ADC1 |  |

| 82         | VAREF1    | VAREF1    |  |

| 83         | ADC7      | ADC7      |  |

| 84         | ADC6      | ADC6      |  |

| 85         | ADC5      | ADC5      |  |

| 86         | ADC4      | ADC4      |  |

| 87         | ABPS6     | ABPS6     |  |

| 88         | ABPS7     | ABPS7     |  |

| 89         | CM3       | СМЗ       |  |

| 90         | TM3       | TM3       |  |

| 91         | GNDTM1    | GNDTM1    |  |

| 92         | TM2       | TM2       |  |

| 93         | CM2       | CM2       |  |

Notes:

1. Shading denotes pins that do not have completely identical functions from density to density. For example, the bank assignment can be different for an I/O, or the function might be available only on a larger density device.

\*: Indicates that the signal assigned to the pins as a CLKBUF/CLKBUF\_LVPECL/CLKBUF\_LVDS goes through a glitchless mux. In order for the glitchless mux to operate correctly, the signal must be a free-running clock signal. Refer to the 'Glitchless MUX' section in the SmartFusion Microcontroller Subsystem User's Guide for more details. Pin Descriptions

🔨 Microsemi

| Pin FG256 |                 |                 |                 |  |

|-----------|-----------------|-----------------|-----------------|--|

| No.       | A2F060 Function | A2F200 Function | A2F500 Function |  |

| P10       | TM0             | TM3             | TM3             |  |

| P11       | GNDA            | GNDA            | GNDA            |  |

| P12       | VCCMAINXTAL     | VCCMAINXTAL     | VCCMAINXTAL     |  |

| P13       | GNDLPXTAL       | GNDLPXTAL       | GNDLPXTAL       |  |

| P14       | VDDBAT          | VDDBAT          | VDDBAT          |  |

| P15       | PTEM            | PTEM            | PTEM            |  |

| P16       | PTBASE          | PTBASE          | PTBASE          |  |

| R1        | PCAP            | PCAP            | PCAP            |  |

| R2        | SDD0            | SDD0            | SDD0            |  |

| R3        | ADC0            | ABPS0           | ABPS0           |  |

| R4        | ADC3            | TM0             | TM0             |  |

| R5        | NC              | ABPS2           | ABPS2           |  |

| R6        | NC              | ADC1            | ADC1            |  |

| R7        | NC              | VCC33ADC0       | VCC33ADC0       |  |

| R8        | VCC15ADC0       | VCC15ADC1       | VCC15ADC1       |  |

| R9        | ADC10           | ADC7            | ADC7            |  |

| R10       | ABPS1           | ABPS7           | ABPS7           |  |

| R11       | NC              | ABPS4           | ABPS4           |  |

| R12       | MAINXIN         | MAINXIN         | MAINXIN         |  |

| R13       | MAINXOUT        | MAINXOUT        | MAINXOUT        |  |

| R14       | LPXIN           | LPXIN           | LPXIN           |  |

| R15       | LPXOUT          | LPXOUT          | LPXOUT          |  |

| R16       | VCC33A          | VCC33A          | VCC33A          |  |

| T1        | NCAP            | NCAP            | NCAP            |  |

| T2        | ADC1            | ABPS1           | ABPS1           |  |

| Т3        | ADC2            | CM0             | CM0             |  |

| T4        | NC              | GNDTM0          | GNDTM0          |  |

| T5        | NC              | ADC0            | ADC0            |  |

| Т6        | NC              | VAREF0          | VAREF0          |  |

| T7        | NC              | GND33ADC0       | GND33ADC0       |  |

| T8        | GND15ADC0       | GND15ADC1       | GND15ADC1       |  |

1. Shading denotes pins that do not have completely identical functions from density to density. For example, the bank assignment can be different for an I/O, or the function might be available only on a larger density device.

2. \*: Indicates that the signal assigned to the pins as a CLKBUF/CLKBUF\_LVPECL/CLKBUF\_LVDS goes through a glitchless mux. In order for the glitchless mux to operate correctly, the signal must be a free-running clock signal. Refer to the 'Glitchless MUX' section in the SmartFusion Microcontroller Subsystem User's Guide for more details.

🌜 Microsemi.

SmartFusion Customizable System-on-Chip (cSoC)

|            | FG484                     |                           |  |

|------------|---------------------------|---------------------------|--|

| Pin Number | A2F200 Function           | A2F500 Function           |  |

| H7         | GND                       | GND                       |  |

| H8         | VCC                       | VCC                       |  |

| H9         | GND                       | GND                       |  |

| H10        | VCC                       | VCC                       |  |

| H11        | GND                       | GND                       |  |

| H12        | VCC                       | VCC                       |  |

| H13        | GND                       | GND                       |  |

| H14        | VCC                       | VCC                       |  |

| H15        | GND                       | GND                       |  |

| H16        | VCCFPGAIOB1               | VCCFPGAIOB1               |  |

| H17        | IO25NDB1V0                | IO29NDB1V0                |  |

| H18        | GCC2/IO25PDB1V0           | GCC2/IO29PDB1V0           |  |

| H19        | GND                       | GND                       |  |

| H20        | GCC0/IO26NPB1V0           | GCC0/IO35NPB1V0           |  |

| H21        | VCCFPGAIOB1               | VCCFPGAIOB1               |  |

| H22        | GCB0/IO27NDB1V0           | GCB0/IO34NDB1V0           |  |

| J1         | EMC_DB[6]/GEB0/IO62NDB5V0 | EMC_DB[6]/GEB0/IO79NDB5V0 |  |

| J2         | EMC_DB[5]/GEA1/IO61PDB5V0 | EMC_DB[5]/GEA1/IO78PDB5V0 |  |

| J3         | EMC_DB[4]/GEA0/IO61NDB5V0 | EMC_DB[4]/GEA0/IO78NDB5V0 |  |

| J4         | EMC_DB[3]/GEC2/IO60PPB5V0 | EMC_DB[3]/GEC2/IO77PPB5V0 |  |

| J5         | VCCFPGAIOB5               | VCCFPGAIOB5               |  |

| J6         | GFA0/IO64NDB5V0           | GFA0/IO81NDB5V0           |  |

| J7         | VCCFPGAIOB5               | VCCFPGAIOB5               |  |

| J8         | GND                       | GND                       |  |

| J9         | VCC                       | VCC                       |  |

| J10        | GND                       | GND                       |  |

| J11        | VCC                       | VCC                       |  |

| J12        | GND                       | GND                       |  |

| J13        | VCC                       | VCC                       |  |

| J14        | GND                       | GND                       |  |

| J15        | VCC                       | VCC                       |  |

| J16        | GND                       | GND                       |  |

| J17        | NC                        | IO37PDB1V0                |  |

| J18        | VCCFPGAIOB1               | VCCFPGAIOB1               |  |

Notes:

1. Shading denotes pins that do not have completely identical functions from density to density. For example, the bank assignment can be different for an I/O, or the function might be available only on a larger density device.

2. \*: Indicates that the signal assigned to the pins as a CLKBUF/CLKBUF\_LVPECL/CLKBUF\_LVDS goes through a glitchless mux. In order for the glitchless mux to operate correctly, the signal must be a free-running clock signal. Refer to the 'Glitchless MUX' section in the SmartFusion Microcontroller Subsystem User's Guide for more details.

5

|            | FG484                     |                           |  |

|------------|---------------------------|---------------------------|--|

| Pin Number | A2F200 Function           | A2F500 Function           |  |

| J19        | GCA0/IO28NDB1V0           | GCA0/IO36NDB1V0 *         |  |

| J20        | GCA1/IO28PDB1V0           | GCA1/IO36PDB1V0 *         |  |

| J21        | GCC1/IO26PPB1V0           | GCC1/IO35PPB1V0           |  |

| J22        | GCB1/IO27PDB1V0           | GCB1/IO34PDB1V0           |  |

| K1         | GND                       | GND                       |  |

| K2         | EMC_DB[0]/GEA2/IO59NDB5V0 | EMC_DB[0]/GEA2/IO76NDB5V0 |  |

| K3         | EMC_DB[1]/GEB2/IO59PDB5V0 | EMC_DB[1]/GEB2/IO76PDB5V0 |  |

| K4         | NC                        | IO74PPB5V0                |  |

| K5         | EMC_DB[2]/IO60NPB5V0      | EMC_DB[2]/IO77NPB5V0      |  |

| K6         | NC                        | IO75PDB5V0                |  |

| K7         | GND                       | GND                       |  |

| K8         | VCC                       | VCC                       |  |

| K9         | GND                       | GND                       |  |

| K10        | VCC                       | VCC                       |  |

| K11        | GND                       | GND                       |  |

| K12        | VCC                       | VCC                       |  |

| K13        | GND                       | GND                       |  |

| K14        | VCC                       | VCC                       |  |

| K15        | GND                       | GND                       |  |

| K16        | VCCFPGAIOB1               | VCCFPGAIOB1               |  |

| K17        | NC                        | IO37NDB1V0                |  |

| K18        | GDA1/IO31PDB1V0           | GDA1/IO40PDB1V0           |  |

| K19        | GDA0/IO31NDB1V0           | GDA0/IO40NDB1V0           |  |

| K20        | GDC1/IO29PDB1V0           | GDC1/IO38PDB1V0           |  |

| K21        | GDC0/IO29NDB1V0           | GDC0/IO38NDB1V0           |  |

| K22        | GND                       | GND                       |  |

| L1         | NC                        | IO73PDB5V0                |  |

| L2         | NC                        | IO73NDB5V0                |  |

| L3         | NC                        | IO72PPB5V0                |  |

| L4         | GND                       | GND                       |  |

| L5         | NC                        | IO74NPB5V0                |  |

| L6         | NC                        | IO75NDB5V0                |  |

| L7         | VCCFPGAIOB5               | VCCFPGAIOB5               |  |

| L8         | GND                       | GND                       |  |

Notes:

1. Shading denotes pins that do not have completely identical functions from density to density. For example, the bank assignment can be different for an I/O, or the function might be available only on a larger density device.

2. \*: Indicates that the signal assigned to the pins as a CLKBUF/CLKBUF\_LVPECL/CLKBUF\_LVDS goes through a glitchless mux. In order for the glitchless mux to operate correctly, the signal must be a free-running clock signal. Refer to the 'Glitchless MUX' section in the SmartFusion Microcontroller Subsystem User's Guide for more details.

## **Microsemi**.

SmartFusion Customizable System-on-Chip (cSoC)

| Revision                       | Changes                                                                                                                                                                                                                                                                                           | Page            |

|--------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------|

| Revision 5<br>(continued)      | Available values for the Std. speed were added to the timing tables from Table 2-38 • 3.3 V LVTTL / 3.3 V LVCMOS High Slew to Table 2-92 • JTAG 1532 (SAR 29331).                                                                                                                                 | 2-31 to<br>2-76 |

|                                | One or more values changed for the –1 speed in tables covering 3.3 V LVCMOS, 2.5 V LVCMOS, 1.8 V LVCMOS, 1.5 V LVCMOS, Combinatorial Cell Propagation Delays, and A2F200 Global Resources.                                                                                                        |                 |

|                                | Table 2-80 • A2F500 Global Resource is new.                                                                                                                                                                                                                                                       | 2-60            |

|                                | Table 2-90 • eNVM Block Timing, Worst Commercial Case Conditions: $T_J = 85^{\circ}C$ , VCC = 1.425 V was revised (SAR 27585).                                                                                                                                                                    | 2-76            |

|                                | The programmable analog specifications tables were revised with updated information.                                                                                                                                                                                                              | 2-78 to<br>2-87 |

|                                | Table 4-1 • Supported JTAG Programming Hardware was revised by adding a note to indicate "planned support" for several of the items in the table.                                                                                                                                                 | 4-7             |

|                                | The note on JTAGSEL in the "In-System Programming" section was revised to state that SoftConsole selects the appropriate TAP controller using the CTXSELECT JTAG command. When using SoftConsole, the state of JTAGSEL is a "don't care" (SAR 29261).                                             | 4-7             |

|                                | The "CS288" and "FG256" pin tables for A2F060 are new, comparing the A2F060 function with the A2F200 function (SAR 29353).                                                                                                                                                                        | 5-24            |

|                                | The "Handling When Unused" column was removed from the "FG256" pin table for A2F200 and A2F500 (SAR 29691).                                                                                                                                                                                       | 5-42            |

| Revision 4<br>(September 2010) | Table 2-8 • Power Supplies Configuration was revised. VCCRCOSC was moved to a column of its own with new values. VCCENVM was added to the table. Standby mode for VJTAG and VPP was changed from 0 V to N/A. "Disable" was changed to "Off" in the eNVM column. The column for RCOSC was deleted. | 2-10            |

|                                | The "Power-Down and Sleep Mode Implementation" section was revised to include VCCROSC.                                                                                                                                                                                                            | 2-11            |

| Revision 3<br>(September 2010) | The "I/Os and Operating Voltage" section was revised to list "single 3.3 V power supply with on-chip 1.5 V regulator" and "external 1.5 V is allowed" (SAR 27663).                                                                                                                                | I               |

|                                | The CS288 package was added to the "Package I/Os: MSS + FPGA I/Os" table (SAR 27101), "Product Ordering Codes" table, and "Temperature Grade Offerings" table (SAR 27044). The number of direct analog inputs for the FG256 package in A2F060 was changed from 8 to 6.                            | III, VI, VI     |

|                                | Two notes were added to the "SmartFusion cSoC Family Product Table" indicating limitations for features of the A2F500 device:                                                                                                                                                                     | II              |

|                                | Two PLLs are available in CS288 and FG484 (one PLL in FG256).<br>[ADCs, DACs, SCBs, comparators, current monitors, and bipolar high voltage<br>monitors are] Available on FG484 only. FG256 and CS288 packages offer the same<br>programmable analog capabilities as A2F200.                      |                 |

|                                | Table cells were merged in rows containing the same values for easier reading (SAR 24748).                                                                                                                                                                                                        |                 |

|                                | The security feature option was added to the "Product Ordering Codes" table.                                                                                                                                                                                                                      | VI              |