Welcome to E-XFL.COM

#### Embedded - System On Chip (SoC): The Heart of Modern Embedded Systems

**Embedded - System On Chip (SoC)** refers to an integrated circuit that consolidates all the essential components of a computer system into a single chip. This includes a microprocessor, memory, and other peripherals, all packed into one compact and efficient package. SoCs are designed to provide a complete computing solution, optimizing both space and power consumption, making them ideal for a wide range of embedded applications.

#### What are **Embedded - System On Chip (SoC)**?

**System On Chip (SoC)** integrates multiple functions of a computer or electronic system onto a single chip. Unlike traditional multi-chip solutions. SoCs combine a central

#### Details

| Product Status          | Obsolete                                                        |

|-------------------------|-----------------------------------------------------------------|

| Architecture            | MCU, FPGA                                                       |

| Core Processor          | ARM® Cortex®-M3                                                 |

| Flash Size              | 128KB                                                           |

| RAM Size                | 16KB                                                            |

| Peripherals             | DMA, POR, WDT                                                   |

| Connectivity            | EBI/EMI, I <sup>2</sup> C, SPI, UART/USART                      |

| Speed                   | 80MHz                                                           |

| Primary Attributes      | ProASIC®3 FPGA, 60K Gates, 1536D-Flip-Flops                     |

| Operating Temperature   | -40°C ~ 100°C (TJ)                                              |

| Package / Case          | 288-TFBGA, CSPBGA                                               |

| Supplier Device Package | 288-CSP (11x11)                                                 |

| Purchase URL            | https://www.e-xfl.com/product-detail/microsemi/a2f060m3e-cs288i |

|                         |                                                                 |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

Table of Contents

| Datasheet Categories                                                                                 |

|------------------------------------------------------------------------------------------------------|

| Microsemi SoC Products Group Safety Critical, Life Support, and High-Reliability Applications Policy |

SmartFusion Customizable System-on-Chip (cSoC)

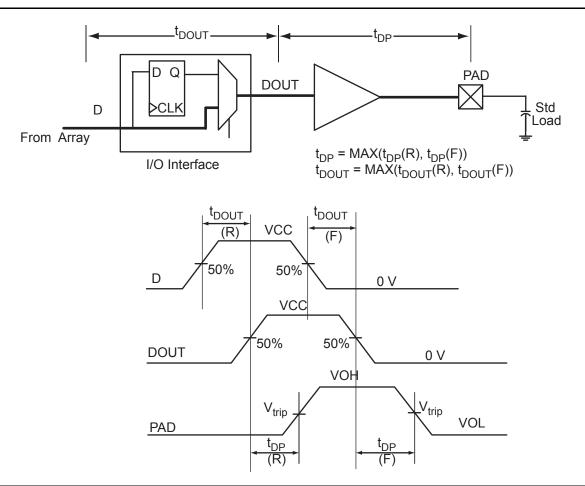

Figure 2-4 • Output Buffer Model and Delays (example)

#### Table 2-28 • I/O Output Buffer Maximum Resistances<sup>1</sup> Applicable to MSS I/O Banks

| Standard                   | Drive Strength | $R_{PULL	ext{-}DOWN} \ (\Omega)^2$ | R <sub>PULL-UP</sub><br>(Ω) <sup>3</sup> |

|----------------------------|----------------|------------------------------------|------------------------------------------|

| 3.3 V LVTTL / 3.3 V LVCMOS | 8mA            | 50                                 | 150                                      |

| 2.5 V LVCMOS               | 8 mA           | 50                                 | 100                                      |

| 1.8 V LVCMOS               | 4 mA           | 100                                | 112                                      |

| 1.5 V LVCMOS               | 2 mA           | 200                                | 224                                      |

Notes:

These maximum values are provided for informational reasons only. Minimum output buffer resistance values depend on VCCxxxxIOBx, drive strength selection, temperature, and process. For board design considerations and detailed output buffer resistances, use the corresponding IBIS models located on the Microsemi SoC Products Group website.

- 2. R<sub>(PULL-DOWN-MAX)</sub> = (V<sub>OLspec</sub>) / I<sub>OLspec</sub>

- 3. R<sub>(PULL-UP-MAX)</sub> = (V<sub>CCImax</sub> V<sub>OHspec</sub>) / I<sub>OHspec</sub>

## Table 2-29 • I/O Weak Pull-Up/Pull-Down Resistances Minimum and Maximum Weak Pull-Up/Pull-Down Resistance Values

|             | R <sub>(WEAK P</sub><br>(Ω | PULL-UP) <sup>1</sup><br>2) | ${R_{(WEAK PULL-DOWN)}^2}_{(\Omega)}$ |       |  |  |

|-------------|----------------------------|-----------------------------|---------------------------------------|-------|--|--|

| VCCxxxxlOBx | Min.                       | Max.                        | Min.                                  | Max.  |  |  |

| 3.3 V       | 10 k                       | 45 k                        | 10 k                                  | 45 k  |  |  |

| 2.5 V       | 11 k                       | 55 k                        | 12 k                                  | 74 k  |  |  |

| 1.8 V       | 18 k                       | 70 k                        | 17 k                                  | 110 k |  |  |

| 1.5 V       | 19 k                       | 90 k                        | 19 k                                  | 140 k |  |  |

Notes:

1. R<sub>(WEAK PULL-UP-MAX)</sub> = (VCCImax – VOHspec) / I<sub>(WEAK PULL-UP-MIN)</sub>

2. R<sub>(WEAK PULL-DOWN-MAX)</sub> = (VOLspec) / I<sub>(WEAK PULL-DOWN-MIN)</sub>

### 🌜 Microsemi.

SmartFusion DC and Switching Characteristics

#### **Timing Characteristics**

# Table 2-56 • 1.5 V LVCMOS High Slew Worst Commercial-Case Conditions: T<sub>J</sub> = 85°C, Worst-Case VCC = 1.425 V, Worst-Case VCCxxxxIOBx = 1.425 V Applies bla to EDCA VO Basks VC Applies to EMC VO Bins

Applicable to FPGA I/O Banks, I/O Assigned to EMC I/O Pins

| Drive<br>Strength | Speed<br>Grade | t <sub>DOUT</sub> | t <sub>DP</sub> | t <sub>DIN</sub> | t <sub>PY</sub> | t <sub>EOUT</sub> | t <sub>ZL</sub> | t <sub>zH</sub> | t <sub>LZ</sub> | t <sub>HZ</sub> | t <sub>zLS</sub> | t <sub>zHS</sub> | Units |

|-------------------|----------------|-------------------|-----------------|------------------|-----------------|-------------------|-----------------|-----------------|-----------------|-----------------|------------------|------------------|-------|

| 2 m               | Std.           | 0.60              | 7.79            | 0.04             | 1.34            | 0.39              | 6.43            | 7.79            | 3.19            | 2.59            | 8.49             | 9.85             | ns    |

|                   | –1             | 0.50              | 6.49            | 0.03             | 1.12            | 0.32              | 5.36            | 6.49            | 2.66            | 2.16            | 7.08             | 8.21             | ns    |

| 4 mA              | Std.           | 0.60              | 4.95            | 0.04             | 1.34            | 0.39              | 4.61            | 4.96            | 3.53            | 3.19            | 6.67             | 7.02             | ns    |

|                   | –1             | 0.50              | 4.13            | 0.03             | 1.12            | 0.32              | 3.85            | 4.13            | 2.94            | 2.66            | 5.56             | 5.85             | ns    |

| 6 mA              | Std.           | 0.60              | 4.36            | 0.04             | 1.34            | 0.39              | 4.34            | 4.36            | 3.60            | 3.34            | 6.40             | 6.42             | ns    |

|                   | –1             | 0.50              | 3.64            | 0.03             | 1.12            | 0.32              | 3.62            | 3.64            | 3.00            | 2.78            | 5.33             | 5.35             | ns    |

| 8 mA              | Std.           | 0.60              | 3.89            | 0.04             | 1.34            | 0.39              | 3.96            | 3.34            | 3.72            | 3.92            | 6.02             | 5.40             | ns    |

|                   | -1             | 0.50              | 3.24            | 0.03             | 1.12            | 0.32              | 3.30            | 2.79            | 3.10            | 3.27            | 5.02             | 4.50             | ns    |

| 12 mA             | Std.           | 0.60              | 3.89            | 0.04             | 1.34            | 0.39              | 3.96            | 3.34            | 3.72            | 3.92            | 6.02             | 5.40             | ns    |

|                   | -1             | 0.50              | 3.24            | 0.03             | 1.12            | 0.32              | 3.30            | 2.79            | 3.10            | 3.27            | 5.02             | 4.50             | ns    |

Notes:

1. Software default selection highlighted in gray.

2. For specific junction temperature and voltage supply levels, refer to Table 2-7 on page 2-9 for derating values.

#### Table 2-57 • 1.5 V LVCMOS Low Slew

Worst Commercial-Case Conditions:  $T_J = 85^{\circ}C$ , Worst-Case VCC = 1.425 V, Worst-Case VCCxxxxIOBx = 1.4 V Applicable to FPGA I/O Banks, I/O Assigned to EMC I/O Pins

| Drive<br>Strength | Speed<br>Grade | t <sub>DOUT</sub> | t <sub>DP</sub> | t <sub>DIN</sub> | t <sub>PY</sub> | t <sub>EOUT</sub> | t <sub>ZL</sub> | t <sub>zH</sub> | t <sub>LZ</sub> | t <sub>HZ</sub> | t <sub>zLS</sub> | t <sub>zHS</sub> | Units |

|-------------------|----------------|-------------------|-----------------|------------------|-----------------|-------------------|-----------------|-----------------|-----------------|-----------------|------------------|------------------|-------|

| 2 mA              | Std.           | 0.60              | 11.96           | 0.04             | 1.34            | 0.39              | 12.18           | 11.70           | 3.20            | 2.47            | 14.24            | 13.76            | ns    |

|                   | -1             | 0.50              | 9.96            | 0.03             | 1.12            | 0.32              | 10.15           | 9.75            | 2.67            | 2.06            | 11.86            | 11.46            | ns    |

| 4 mA              | Std.           | 0.60              | 9.51            | 0.04             | 1.34            | 0.39              | 9.68            | 8.76            | 3.54            | 3.07            | 11.74            | 10.82            | ns    |

|                   | -1             | 0.50              | 7.92            | 0.03             | 1.12            | 0.32              | 8.07            | 7.30            | 2.95            | 2.56            | 9.79             | 9.02             | ns    |

| 6 mA              | Std.           | 0.60              | 8.86            | 0.04             | 1.34            | 0.39              | 9.03            | 8.17            | 3.61            | 3.22            | 11.08            | 10.23            | ns    |

|                   | -1             | 0.50              | 7.39            | 0.03             | 1.12            | 0.32              | 7.52            | 6.81            | 3.01            | 2.68            | 9.24             | 8.52             | ns    |

| 8 mA              | Std.           | 0.60              | 8.44            | 0.04             | 1.34            | 0.39              | 8.60            | 8.18            | 3.73            | 3.78            | 10.66            | 10.24            | ns    |

|                   | -1             | 0.50              | 7.04            | 0.03             | 1.12            | 0.32              | 7.17            | 6.82            | 3.11            | 3.15            | 8.88             | 8.53             | ns    |

| 12 mA             | Std.           | 0.60              | 8.44            | 0.04             | 1.34            | 0.39              | 8.60            | 8.18            | 3.73            | 3.78            | 10.66            | 10.24            | ns    |

|                   | -1             | 0.50              | 7.04            | 0.03             | 1.12            | 0.32              | 7.17            | 6.82            | 3.11            | 3.15            | 8.88             | 8.53             | ns    |

Note: For specific junction temperature and voltage supply levels, refer to Table 2-7 on page 2-9 for derating values.

#### Table 2-58 • 1.5 V LVCMOS High Slew

Worst Commercial-Case Conditions: T<sub>J</sub> = 85°C, Worst-Case VCC = 1.425 V, Worst-Case VCCxxxxIOBx = 3.0 V Applicable to MSS I/O Banks

| Drive<br>Strength | Speed<br>Grade | t <sub>DOUT</sub> | t <sub>DP</sub> | t <sub>DIN</sub> | t <sub>PY</sub> | t <sub>PYS</sub> | t <sub>EOUT</sub> | t <sub>zL</sub> | t <sub>zH</sub> | t <sub>LZ</sub> | t <sub>HZ</sub> | Units |

|-------------------|----------------|-------------------|-----------------|------------------|-----------------|------------------|-------------------|-----------------|-----------------|-----------------|-----------------|-------|

| 2 mA              | Std.           | 0.22              | 3.24            | 0.09             | 1.28            | 1.86             | 0.22              | 3.30            | 3.20            | 2.24            | 2.21            | ns    |

|                   | -1             | 0.18              | 2.70            | 0.07             | 1.07            | 1.55             | 0.18              | 2.75            | 2.67            | 1.87            | 1.85            | ns    |

Notes:

1. Software default selection highlighted in gray.

2. For specific junction temperature and voltage supply levels, refer to Table 2-7 on page 2-9 for derating values.

### 🌜 Microsemi.

SmartFusion DC and Switching Characteristics

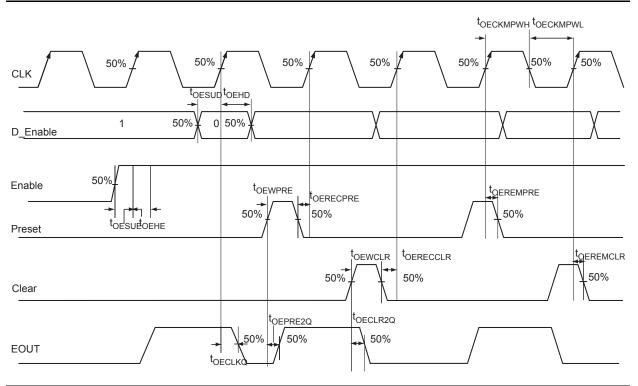

### **Output Enable Register**

Figure 2-18 • Output Enable Register Timing Diagram

#### **Timing Characteristics**

Table 2-73 • Output Enable Register Propagation DelaysWorst Commercial-Case Conditions: TJ = 85°C, Worst-Case VCC = 1.425 V

| Parameter             | Description                                                            | -1   | Std. | Units |

|-----------------------|------------------------------------------------------------------------|------|------|-------|

| t <sub>OECLKQ</sub>   | Clock-to-Q of the Output Enable Register                               | 0.45 | 0.54 | ns    |

| t <sub>OESUD</sub>    | Data Setup Time for the Output Enable Register                         | 0.32 | 0.38 | ns    |

| t <sub>OEHD</sub>     | Data Hold Time for the Output Enable Register                          | 0.00 | 0.00 | ns    |

| t <sub>OESUE</sub>    | Enable Setup Time for the Output Enable Register                       | 0.44 | 0.53 | ns    |

| t <sub>OEHE</sub>     | Enable Hold Time for the Output Enable Register                        | 0.00 | 0.00 | ns    |

| t <sub>OECLR2Q</sub>  | Asynchronous Clear-to-Q of the Output Enable Register                  | 0.68 | 0.81 | ns    |

| t <sub>OEPRE2Q</sub>  | Asynchronous Preset-to-Q of the Output Enable Register                 | 0.68 | 0.81 | ns    |

| t <sub>OEREMCLR</sub> | Asynchronous Clear Removal Time for the Output Enable Register         | 0.00 | 0.00 | ns    |

| t <sub>OERECCLR</sub> | Asynchronous Clear Recovery Time for the Output Enable Register        | 0.23 | 0.27 | ns    |

| t <sub>OEREMPRE</sub> | Asynchronous Preset Removal Time for the Output Enable Register        | 0.00 | 0.00 | ns    |

| t <sub>OERECPRE</sub> | Asynchronous Preset Recovery Time for the Output Enable Register       | 0.23 | 0.27 | ns    |

| tOEWCLR               | Asynchronous Clear Minimum Pulse Width for the Output Enable Register  | 0.22 | 0.22 | ns    |

| t <sub>OEWPRE</sub>   | Asynchronous Preset Minimum Pulse Width for the Output Enable Register | 0.22 | 0.22 | ns    |

| t <sub>OECKMPWH</sub> | Clock Minimum Pulse Width High for the Output Enable Register          | 0.36 | 0.36 | ns    |

| t <sub>OECKMPWL</sub> | Clock Minimum Pulse Width Low for the Output Enable Register           | 0.32 | 0.32 | ns    |

Note: For specific junction temperature and voltage supply levels, refer to Table 2-7 on page 2-9 for derating values.

| Parameter            | Description           | -1    | Std.  | Units |  |

|----------------------|-----------------------|-------|-------|-------|--|

| t <sub>RSTB2Q</sub>  | Reset to Q (data out) | 26.67 | 30.67 | ns    |  |

| F <sub>TCKMAX</sub>  | TCK Maximum Frequency | 19.00 | 21.85 | MHz   |  |

| t <sub>TRSTREM</sub> | ResetB Removal Time   | 0.00  | 0.00  | ns    |  |

| t <sub>TRSTREC</sub> | ResetB Recovery Time  | 0.27  | 0.31  | ns    |  |

| t <sub>TRSTMPW</sub> | ResetB Minimum Pulse  | TBD   | TBD   | ns    |  |

#### Table 2-92 • JTAG 1532 Worst Commercial-Case Conditions: T<sub>J</sub> = 85°C, Worst-Case VCC = 1.425 V

Note: For specific junction temperature and voltage supply levels, refer to Table 2-7 on page 2-9 for derating values.

### **Compile and Debug**

Microsemi's SoftConsole is a free Eclipse-based IDE that enables the rapid production of C and C++ executables for Microsemi FPGA and cSoCs using Cortex-M3, Cortex-M1 and Core8051s. For SmartFusion support, SoftConsole includes the GNU C/C++ compiler and GDB debugger. Additional examples can be found on the SoftConsole page:

- Using UART with SmartFusion: SoftConsole Standalone Flow Tutorial

- Design Files

- Displaying POT Level with LEDs: Libero SoC and SoftConsole Flow Tutorial for SmartFusion

- Design Files

IAR Embedded Workbench<sup>®</sup> for ARM/Cortex is an integrated development environment for building and debugging embedded ARM applications using assembler, C and C++. It includes a project manager, editor, build and debugger tools with support for RTOS-aware debugging on hardware or in a simulator.

- Designing SmartFusion cSoC with IAR Systems

- IAR Embedded Workbench IDE User Guide for ARM

- Download Evaluation or Kickstart version of IAR Embedded Workbench for ARM

Keil's Microcontroller Development Kit comes in two editions: MDK-ARM and MDK Basic. Both editions feature  $\mu$ Vision<sup>®</sup>, the ARM Compiler, MicroLib, and RTX, but the MDK Basic edition is limited to 256K so that small applications are more affordable.

- Designing SmartFusion cSoC with Keil

- Using Keil µVision and Microsemi SmartFusion cSoC

- Programming file for use with this tutorial

- Keil Microcontroller Development Kit for ARM Product Manuals

- Download Evaluation version of Keil MDK-ARM

| COMPLIANT<br>RRM® Cortex® Hicrocontroller<br>Software Interface Standard | Microsemi.            | An ARM <sup>®</sup> Company | <b>SYSTEMS</b>        |

|--------------------------------------------------------------------------|-----------------------|-----------------------------|-----------------------|

| Software IDE                                                             | SoftConsole           | Vision IDE                  | Embedded Workbench    |

| Website                                                                  | www.microsemi.com/soc | www.keil.com                | www.iar.com           |

| Free versions from SoC<br>Products Group                                 | Free with Libero SoC  | 32 K code limited           | 32 K code limited     |

| Available from Vendor                                                    | N/A                   | Full version                | Full version          |

| Compiler                                                                 | GNU GCC               | RealView C/C++              | IAR ARM Compiler      |

| Debugger                                                                 | GDB debug             | Vision Debugger             | C-SPY Debugger        |

| Instruction Set Simulator                                                | No                    | Vision Simulator            | Yes                   |

| Debug Hardware                                                           | FlashPro4             | ULINK2 or ULINK-ME          | J-LINK or J-LINK Lite |

### **Operating Systems**

FreeRTOS<sup>™</sup> is a portable, open source, royalty free, mini real-time kernel (a free-to-download and freeto-deploy RTOS that can be used in commercial applications without any requirement to expose your proprietary source code). FreeRTOS is scalable and designed specifically for small embedded systems. This FreeRTOS version ported by Microsemi is 6.0.1. For more information, visit the FreeRTOS website: www.freertos.org

- SmartFusion Webserver Demo Using uIP and FreeRTOS

- SmartFusion cSoC: Running Webserver, TFTP on IwIP TCP/IP Stack Application Note

Flash File System (RL-Flash) allows your embedded applications to create, save, read, and modify files in standard storage devices such as ROM, RAM, or FlashROM, using a standard serial peripheral interface (SPI). Many ARM-based microcontrollers have a practical requirement for a standard file system. With RL-FlashFS you can implement new features in embedded applications such as data logging, storing program state during standby modes, or storing firmware upgrades.

Micrium, in addition to  $\mu C/OS-III^{(R)}$ , offers the following support for SmartFusion cSoC:

- µC/TCP-IP<sup>™</sup> is a compact, reliable, and high-performance stack built from the ground up by Micrium and has the quality, scalability, and reliability that translates into a rapid configuration of network options, remarkable ease-of-use, and rapid time-to-market.

- µC/Probe<sup>™</sup> is one of the most useful tools in embedded systems design and puts you in the driver's seat, allowing you to take charge of virtually any variable, memory location, and I/O port in your embedded product, while your system is running.

### References

### **PCB** Files

A2F500 SmartFusion Development Kit PCB Files http://www.microsemi.com/index.php?option=com\_docman&task=doc\_download&gid=130770 A2F200 SmartFusion Development Kit PCB Files http://www.microsemi.com/index.php?option=com\_docman&task=doc\_download&gid=130773

### **Application Notes**

SmartFusion cSoC Board Design Guidelines http://www.microsemi.com/index.php?option=com\_docman&task=doc\_download&gid=129815

### **Re-Programming the eNVM Blocks Using the Cortex-M3**

In this mode the Cortex-M3 is executing the eNVM programming algorithm from eSRAM. Since individual pages (132 bytes) of the eNVM can be write-protected, the programming algorithm software can be protected from inadvertent erasure. When reprogramming the eNVM, both MSS I/Os and FPGA I/Os are available as interfaces for sourcing the new eNVM image. The SoC Products Group provides working example projects for SoftConsole, IAR, and Keil development environments. These can be downloaded via the SoC Products Group Firmware Catalog.

Alternately, the eNVM can be reprogrammed by the Cortex-M3 via the IAP driver. This is necessary when using an encrypted image.

### Secure Programming

For background, refer to the "Security in Low Power Flash Devices" chapter of the *Fusion FPGA Fabric User's Guide* on the SoC Products Group website. SmartFusion ISP behaves identically to Fusion ISP. IAP of SmartFusion cSoCs is accomplished by using the IAP driver. Only the FPGA fabric and the eNVM can be reprogrammed with the protection of security measures by using the IAP driver.

### **Typical Programming and Erase Times**

Table 4-3 documents the typical programming and erase times for two components of SmartFusion cSoCs, FPGA fabric and eNVM, using the SoC Products Group's FlashPro hardware and software. These times will be different for other ISP and IAP methods. The **Program** action in FlashPro software includes erase, program, and verify to complete.

The typical programming (including erase) time per page of the eNVM is 8 ms.

|         | FPGA Fabric (seconds) |        |        | eN     | VM (secon | ids)   | FlashROM (seconds) |        |        |  |

|---------|-----------------------|--------|--------|--------|-----------|--------|--------------------|--------|--------|--|

|         | A2F060                | A2F200 | A2F500 | A2F060 | A2F200    | A2F500 | A2F060             | A2F200 | A2F500 |  |

| Erase   | 21                    | 21     | 21     | N/A    | N/A       | N/A    | 21                 | 21     | 21     |  |

| Program | 28                    | 35     | 48     | 18     | 39        | 71     | 22                 | 22     | 22     |  |

| Verify  | 2                     | 6      | 12     | 9      | 18        | 37     | 1                  | 1      | 1      |  |

#### Table 4-3 • Typical Programming and Erase Times

### References

### **User's Guides**

#### DirectC User's Guide

http://www.microsemi.com/index.php?option=com\_docman&task=doc\_download&gid=132588 In-System Programming (ISP) of Microsemi's Low-Power Flash Devices Using FlashPro4/3/3X http://www.microsemi.com/index.php?option=com\_docman&task=doc\_download&gid=129973 Programming Flash Devices HandBook

http://www.microsemi.com/index.php?option=com\_docman&task=doc\_download&gid=129930

### **Application Notes on IAP Programming Technique**

SmartFusion cSoC: Programming FPGA Fabric and eNVM Using In-Application Programming Interface App Note

http://www.microsemi.com/index.php?option=com\_docman&task=doc\_download&gid=129818 SmartFusion cSoC: Basic Bootloader and Field Upgrade eNVM Through IAP Interface App Note http://www.microsemi.com/index.php?option=com\_docman&task=doc\_download&gid=129823

| Name        | Туре   | Description                                                                                                                                                                                                                                                  |

|-------------|--------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| VCCFPGAIOB5 | Supply | Digital supply to the FPGA fabric I/O bank 5 (west FPGA I/O bank) for the output buffers and I/O logic.                                                                                                                                                      |

|             |        | Each bank can have a separate VCCFPGAIO connection. All I/Os in a bank will run off the same VCCFPGAIO supply. VCCFPGAIO can be 1.5 V, 1.8 V, 2.5 V, or 3.3 V, nominal voltage. Unused I/O banks should have their corresponding VCCFPGAIO pins tied to GND. |

| VCCLPXTAL   | Supply | Analog supply to the low power 32 KHz crystal oscillator. Always power this pin. <sup>1</sup>                                                                                                                                                                |

| VCCMAINXTAL | Supply | Analog supply to the main crystal oscillator circuit. Always power this pin. <sup>1</sup>                                                                                                                                                                    |

| VCCMSSIOB2  | Supply | Supply voltage to the microcontroller subsystem I/O bank 2 (east MSS I/O bank) for the<br>output buffers and I/O logic.                                                                                                                                      |

|             |        | Each bank can have a separate VCCMSSIO connection. All I/Os in a bank will run off the same VCCMSSIO supply. VCCMSSIO can be 1.5 V, 1.8 V, 2.5 V, or 3.3 V, nominal voltage. Unused I/O banks should have their corresponding VCCMSSIO pins tied to GND.     |

| VCCMSSIOB4  | Supply | Supply voltage to the microcontroller subsystem I/O bank 4 (west MSS I/O bank) for the output buffers and I/O logic.                                                                                                                                         |

|             |        | Each bank can have a separate VCCMSSIO connection. All I/Os in a bank will run off the same VCCMSSIO supply. VCCMSSIO can be 1.5 V, 1.8 V, 2.5 V, or 3.3 V, nominal voltage. Unused I/O banks should have their corresponding VCCMSSIO pins tied to GND.     |

| VCCPLLx     | Supply | Analog 1.5 V supply to the PLL. Always power this pin.                                                                                                                                                                                                       |

| VCCRCOSC    | Supply | Analog supply to the integrated RC oscillator circuit. Always power this pin. <sup>1</sup>                                                                                                                                                                   |

| VCOMPLAx    | Supply | Analog ground for the PLL                                                                                                                                                                                                                                    |

| VDDBAT      | Supply | External battery connection to the low power 32 KHz crystal oscillator (along with VCCLPXTAL), RTC, and battery switchover circuit. Can be pulled down if unused.                                                                                            |

Notes:

1. The following 3.3 V supplies should be connected together while following proper noise filtering practices: VCC33A, VCC33ADCx, VCC33ADCx, VCC33SDDx, VCCMAINXTAL, and VCCLPXTAL.

2. The following 1.5 V supplies should be connected together while following proper noise filtering practices: VCC, VCC15A, and VCC15ADCx.

3. For more details on VCCPLLx capacitor recommendations, refer to the application note AC359, SmartFusion cSoC Board Design Guidelines, the "PLL Power Supply Decoupling Scheme" section.

Pin Descriptions

# **Special Function Pins**

| Name     | Туре | Polarity/Bus Size | Description                                                                                                                                                                                                                                                                                                          |

|----------|------|-------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| NC       |      |                   | No connect                                                                                                                                                                                                                                                                                                           |

|          |      |                   | This pin is not connected to circuitry within the device. These pins can<br>be driven to any voltage or can be left floating with no effect on the<br>operation of the device.                                                                                                                                       |

| DC       |      |                   | Do not connect.                                                                                                                                                                                                                                                                                                      |

|          |      |                   | This pin should not be connected to any signals on the PCB. These pins should be left unconnected.                                                                                                                                                                                                                   |

| LPXIN    | In   | 1                 | Low power 32 KHz crystal oscillator.                                                                                                                                                                                                                                                                                 |

|          |      |                   | Input from the 32 KHz oscillator. Pin for connecting a low power 32 KHz watch crystal. If not used, the LPXIN pin can be left floating. For more information, see the PLLs, Clock Conditioning Circuitry, and On-Chip Crystal Oscillators section in the <i>SmartFusion Microcontroller Subsystem User's Guide</i> . |

| LPXOUT   | In   | 1                 | Low power 32 KHz crystal oscillator.                                                                                                                                                                                                                                                                                 |

|          |      |                   | Output to the 32 KHz oscillator. Pin for connecting a low power 32 KHz watch crystal. If not used, the LPXOUT pin can be left floating. For more information, see the PLLs, Clock Conditioning Circuitry, and On-Chip Crystal Oscillators section in the <i>SmartFusion Microcontroller Subsystem User's Guide</i> . |

| MAINXIN  | In   | 1                 | Main crystal oscillator circuit.                                                                                                                                                                                                                                                                                     |

|          |      |                   | Input to the crystal oscillator circuit. Pin for connecting an external crystal, ceramic resonator, or RC network. When using an external crystal or ceramic oscillator, external capacitors are also recommended. Refer to documentation from the crystal oscillator manufacturer for proper capacitor value.       |

|          |      |                   | If an external RC network or clock input is used, the RC components are connected to the MAINXIN pin, with MAINXOUT left floating. When the main crystal oscillator is not being used, MAINXIN and MAINXOUT pins can be left floating.                                                                               |

|          |      |                   | For more information, see the PLLs, Clock Conditioning Circuitry, and On-Chip Crystal Oscillators section in the <i>SmartFusion Microcontroller Subsystem User's Guide</i> .                                                                                                                                         |

| MAINXOUT | Out  | 1                 | Main crystal oscillator circuit.                                                                                                                                                                                                                                                                                     |

|          |      |                   | Output from the crystal oscillator circuit. Pin for connecting external crystal or ceramic resonator. When using an external crystal or ceramic oscillator, external capacitors are also recommended. Refer to documentation from the crystal oscillator manufacturer for proper capacitor value.                    |

|          |      |                   | If an external RC network or clock input is used, the RC components are connected to the MAINXIN pin, with MAINXOUT left floating. When the main crystal oscillator is not being used, MAINXIN and MAINXOUT pins can be left floating.                                                                               |

|          |      |                   | For more information, see the PLLs, Clock Conditioning Circuitry, and On-Chip Crystal Oscillators section in the <i>SmartFusion Microcontroller Subsystem User's Guide</i> .                                                                                                                                         |

SmartFusion Customizable System-on-Chip (cSoC)

#### Table 5-1 • Recommended Tie-Off Values for the TCK and TRST Pins

| VJTAG          | Tie-Off Resistance <sup>1, 2</sup> |

|----------------|------------------------------------|

| VJTAG at 3.3 V | 200 Ω to 1 kΩ                      |

| VJTAG at 2.5 V | 200 Ω to 1 kΩ                      |

| VJTAG at 1.8 V | 500 Ω to 1 kΩ                      |

| VJTAG at 1.5 V | 500 Ω to 1 kΩ                      |

Notes:

1. The TCK pin can be pulled up/down.

2. The TRST pin can only be pulled down.

1. Equivalent parallel resistance if more than one device is on JTAG chain.

**CS288** Pin A2F060 Function A2F200 Function A2E500 Eunction No. IO17NDB0V0 GBA2/IO20PDB1V0 GBA2/IO27PDB1V0 C21 EMC DB[14]/IO45NDB5V0 EMC DB[14]/GAB2/IO71NDB5V0 EMC DB[14]/GAB2/IO88NDB5V0 D1 D3 VCCFPGAIOB5 VCCFPGAIOB5 VCCFPGAIOB5 D19 GND GND GND VCCFPGAIOB1 D21 VCCFPGAIOB1 VCCFPGAIOB1 EMC DB[13]/GAC2/IO70PDB5V0 EMC DB[13]/GAC2/IO87PDB5V0 E1 EMC DB[13]/IO44PDB5V0 EMC DB[12]/IO44NDB5V0 EMC DB[12]/IO70NDB5V0 EMC DB[12]/IO87NDB5V0 E3 E5 GNDQ GNDQ GNDQ EMC BYTEN[0]/IO02NDB0V0 EMC BYTEN[0]/GAC0/IO02NDB0V0 EMC BYTEN[0]/GAC0/IO07NDB0V0 E6 EMC BYTEN[1]/IO02PDB0V0 EMC BYTEN[1]/GAC1/IO02PDB0V0 EMC BYTEN[1]/GAC1/IO07PDB0V0 E7 EMC OEN1 N/IO03PDB0V0 EMC OEN1 N/IO03PDB0V0 EMC OEN1 N/IO08PDB0V0 F8 EMC AB[3]/IO05PDB0V0 EMC AB[3]/IO05PDB0V0 EMC AB[3]/IO09PDB0V0 E9 E10 EMC AB[10]/IO09NDB0V0 EMC AB[10]/IO09NDB0V0 EMC AB[10]/IO11NDB0V0 EMC AB[7]/IO07PDB0V0 EMC AB[7]/IO07PDB0V0 EMC AB[7]/IO12PDB0V0 F11 E12 EMC AB[13]/IO10PDB0V0 EMC AB[13]/IO10PDB0V0 EMC AB[13]/IO14PDB0V0 E13 EMC AB[16]/IO12NDB0V0 EMC AB[16]/IO12NDB0V0 EMC AB[16]/IO17NDB0V0 E14 EMC AB[17]/IO12PDB0V0 EMC AB[17]/IO12PDB0V0 EMC AB[17]/IO17PDB0V0 E15 GCC0/IO18NPB0V0 GCB0/IO27NDB1V0 GCB0/IO34NDB1V0 E16 GCA1/IO20PPB0V0 GCB1/IO27PDB1V0 GCB1/IO34PDB1V0 E17 GCC1/IO18PPB0V0 GCB2/IO24PDB1V0 GCB2/IO33PDB1V0 GCA0/IO36NDB1V0 \* E19 GCB2/IO22PPB1V0 GCA0/IO28NDB1V0 E21 IO21NDB1V0 GCA1/IO28PDB1V0 GCA1/IO36PDB1V0 \* VCCFPGAIOB5 F1 VCCFPGAIOB5 VCCFPGAIOB5 F3 GFB2/IO42NDB5V0 GFB2/IO68NDB5V0 GFB2/IO85NDB5V0 F5 GFA2/IO42PDB5V0 GFA2/IO68PDB5V0 GFA2/IO85PDB5V0 F6 EMC DB[11]/IO43PDB5V0 EMC DB[11]/IO69PDB5V0 EMC DB[11]/IO86PDB5V0 F7 GND GND GND NC GFC1/IO66PPB5V0 GFC1/IO83PPB5V0 F8 F9 VCCFPGAIOB0 VCCFPGAIOB0 VCCFPGAIOB0 EMC AB[11]/IO09PDB0V0 F10 EMC AB[11]/IO09PDB0V0 EMC AB[11]/IO11PDB0V0 F11 EMC AB[6]/IO07NDB0V0 EMC AB[6]/IO07NDB0V0 EMC AB[6]/IO12NDB0V0

#### Notes:

🔨 🤄 Microsemi

Pin Descriptions

1. Shading denotes pins that do not have completely identical functions from density to density. For example, the bank assignment can be different for an I/O, or the function might be available only on a larger density device.

\*: Indicates that the signal assigned to the pins as a CLKBUF/CLKBUF\_LVPECL/CLKBUF\_LVDS goes through a glitchless mux. In order for the glitchless mux to operate correctly, the signal must be a free-running clock signal. Refer to the 'Glitchless MUX' section in the SmartFusion Microcontroller Subsystem User's Guide for more details.

|            | PQ208                 |                       |  |

|------------|-----------------------|-----------------------|--|

| Pin Number | A2F200                | A2F500                |  |

| 32         | VCCRCOSC              | VCCRCOSC              |  |

| 33         | MSS_RESET_N           | MSS_RESET_N           |  |

| 34         | VCCESRAM              | VCCESRAM              |  |

| 35         | MAC_MDC/IO48RSB4V0    | MAC_MDC/IO57RSB4V0    |  |

| 36         | MAC_MDIO/IO49RSB4V0   | MAC_MDIO/IO58RSB4V0   |  |

| 37         | MAC_TXEN/IO52RSB4V0   | MAC_TXEN/IO61RSB4V0   |  |

| 38         | MAC_CRSDV/IO51RSB4V0  | MAC_CRSDV/IO60RSB4V0  |  |

| 39         | MAC_RXER/IO50RSB4V0   | MAC_RXER/IO59RSB4V0   |  |

| 40         | GND                   | GND                   |  |

| 41         | VCCMSSIOB4            | VCCMSSIOB4            |  |

| 42         | VCC                   | VCC                   |  |

| 43         | MAC_TXD[0]/IO56RSB4V0 | MAC_TXD[0]/IO65RSB4V0 |  |

| 44         | MAC_TXD[1]/IO55RSB4V0 | MAC_TXD[1]/IO64RSB4V0 |  |

| 45         | MAC_RXD[0]/IO54RSB4V0 | MAC_RXD[0]/IO63RSB4V0 |  |

| 46         | MAC_RXD[1]/IO53RSB4V0 | MAC_RXD[1]/IO62RSB4V0 |  |

| 47         | MAC_CLK               | MAC_CLK               |  |

| 48         | GNDSDD0               | GNDSDD0               |  |

| 49         | VCC33SDD0             | VCC33SDD0             |  |

| 50         | VCC15A                | VCC15A                |  |

| 51         | PCAP                  | PCAP                  |  |

| 52         | NCAP                  | NCAP                  |  |

| 53         | VCC33AP               | VCC33AP               |  |

| 54         | VCC33N                | VCC33N                |  |

| 55         | SDD0                  | SDD0                  |  |

| 56         | GNDA                  | GNDA                  |  |

| 57         | GNDAQ                 | GNDAQ                 |  |

| 58         | ABPS0                 | ABPS0                 |  |

| 59         | ABPS1                 | ABPS1                 |  |

| 60         | CM0                   | СМО                   |  |

| 61         | ТМО                   | ТМО                   |  |

| 62         | GNDTM0                | GNDTM0                |  |

Notes:

1. Shading denotes pins that do not have completely identical functions from density to density. For example, the bank assignment can be different for an I/O, or the function might be available only on a larger density device.

2. \*: Indicates that the signal assigned to the pins as a CLKBUF/CLKBUF\_LVPECL/CLKBUF\_LVDS goes through a glitchless mux. In order for the glitchless mux to operate correctly, the signal must be a free-running clock signal. Refer to the 'Glitchless MUX' section in the SmartFusion Microcontroller Subsystem User's Guide for more details.

🌜 Microsemi.

SmartFusion Customizable System-on-Chip (cSoC)

|            | PQ208           |                   |

|------------|-----------------|-------------------|

| Pin Number | A2F200          | A2F500            |

| 125        | TMS             | TMS               |

| 126        | TDO             | TDO               |

| 127        | TRSTB           | TRSTB             |

| 128        | VJTAG           | VJTAG             |

| 129        | VDDBAT          | VDDBAT            |

| 130        | VCCLPXTAL       | VCCLPXTAL         |

| 131        | LPXOUT          | LPXOUT            |

| 132        | LPXIN           | LPXIN             |

| 133        | GNDLPXTAL       | GNDLPXTAL         |

| 134        | GNDMAINXTAL     | GNDMAINXTAL       |

| 135        | MAINXOUT        | MAINXOUT          |

| 136        | MAINXIN         | MAINXIN           |

| 137        | VCCMAINXTAL     | VCCMAINXTAL       |

| 138        | GND             | GND               |

| 139        | VCC             | VCC               |

| 140        | VPP             | VPP               |

| 141        | VCCFPGAIOB1     | VCCFPGAIOB1       |

| 142        | GDA0/IO31NDB1V0 | GDA0/IO40NDB1V0   |

| 143        | GDA1/IO31PDB1V0 | GDA1/IO40PDB1V0   |

| 144        | GDC0/IO29NSB1V0 | GDC0/IO38NSB1V0   |

| 145        | GCA0/IO28NDB1V0 | GCA0/IO36NDB1V0 * |

| 146        | GCA1/IO28PDB1V0 | GCA1/IO36PDB1V0 * |

| 147        | VCCFPGAIOB1     | VCCFPGAIOB1       |

| 148        | GND             | GND               |

| 149        | VCC             | VCC               |

| 150        | IO25NDB1V0      | IO30NDB1V0        |

| 151        | GCC2/IO25PDB1V0 | GBC2/IO30PDB1V0   |

| 152        | IO23NDB1V0      | IO28NDB1V0        |

| 153        | GCA2/IO23PDB1V0 | GCA2/IO28PDB1V0 * |

| 154        | GBC2/IO21PSB1V0 | GBB2/IO27NDB1V0   |

| 155        | GBA2/IO20PSB1V0 | GBA2/IO27PDB1V0   |

Notes:

1. Shading denotes pins that do not have completely identical functions from density to density. For example, the bank assignment can be different for an I/O, or the function might be available only on a larger density device.

2. \*: Indicates that the signal assigned to the pins as a CLKBUF/CLKBUF\_LVPECL/CLKBUF\_LVDS goes through a glitchless mux. In order for the glitchless mux to operate correctly, the signal must be a free-running clock signal. Refer to the 'Glitchless MUX' section in the SmartFusion Microcontroller Subsystem User's Guide for more details.

🌜 Microsemi.

SmartFusion Customizable System-on-Chip (cSoC)

|            | FG484                     |                           |  |

|------------|---------------------------|---------------------------|--|

| Pin Number | A2F200 Function           | A2F500 Function           |  |

| H7         | GND                       | GND                       |  |

| H8         | VCC                       | VCC                       |  |

| H9         | GND                       | GND                       |  |

| H10        | VCC                       | VCC                       |  |

| H11        | GND                       | GND                       |  |

| H12        | VCC                       | VCC                       |  |

| H13        | GND                       | GND                       |  |

| H14        | VCC                       | VCC                       |  |

| H15        | GND                       | GND                       |  |

| H16        | VCCFPGAIOB1               | VCCFPGAIOB1               |  |

| H17        | IO25NDB1V0                | IO29NDB1V0                |  |

| H18        | GCC2/IO25PDB1V0           | GCC2/IO29PDB1V0           |  |

| H19        | GND                       | GND                       |  |

| H20        | GCC0/IO26NPB1V0           | GCC0/IO35NPB1V0           |  |

| H21        | VCCFPGAIOB1               | VCCFPGAIOB1               |  |

| H22        | GCB0/IO27NDB1V0           | GCB0/IO34NDB1V0           |  |

| J1         | EMC_DB[6]/GEB0/IO62NDB5V0 | EMC_DB[6]/GEB0/IO79NDB5V0 |  |

| J2         | EMC_DB[5]/GEA1/IO61PDB5V0 | EMC_DB[5]/GEA1/IO78PDB5V0 |  |

| J3         | EMC_DB[4]/GEA0/IO61NDB5V0 | EMC_DB[4]/GEA0/IO78NDB5V0 |  |

| J4         | EMC_DB[3]/GEC2/IO60PPB5V0 | EMC_DB[3]/GEC2/IO77PPB5V0 |  |

| J5         | VCCFPGAIOB5               | VCCFPGAIOB5               |  |

| J6         | GFA0/IO64NDB5V0           | GFA0/IO81NDB5V0           |  |

| J7         | VCCFPGAIOB5               | VCCFPGAIOB5               |  |

| J8         | GND                       | GND                       |  |

| J9         | VCC                       | VCC                       |  |

| J10        | GND                       | GND                       |  |

| J11        | VCC                       | VCC                       |  |

| J12        | GND                       | GND                       |  |

| J13        | VCC                       | VCC                       |  |

| J14        | GND                       | GND                       |  |

| J15        | VCC                       | VCC                       |  |

| J16        | GND                       | GND                       |  |

| J17        | NC                        | IO37PDB1V0                |  |

| J18        | VCCFPGAIOB1               | VCCFPGAIOB1               |  |

Notes:

1. Shading denotes pins that do not have completely identical functions from density to density. For example, the bank assignment can be different for an I/O, or the function might be available only on a larger density device.

2. \*: Indicates that the signal assigned to the pins as a CLKBUF/CLKBUF\_LVPECL/CLKBUF\_LVDS goes through a glitchless mux. In order for the glitchless mux to operate correctly, the signal must be a free-running clock signal. Refer to the 'Glitchless MUX' section in the SmartFusion Microcontroller Subsystem User's Guide for more details.

|            | FG484                 |                       |  |

|------------|-----------------------|-----------------------|--|

| Pin Number | A2F200 Function       | A2F500 Function       |  |

| T1         | GND                   | GND                   |  |

| T2         | VCCMSSIOB4            | VCCMSSIOB4            |  |

| Т3         | GPIO_8/IO39RSB4V0     | GPIO_8/IO48RSB4V0     |  |

| T4         | GPIO_11/IO57RSB4V0    | GPIO_11/IO66RSB4V0    |  |

| T5         | GND                   | GND                   |  |

| Т6         | MAC_CLK               | MAC_CLK               |  |

| Τ7         | VCCMSSIOB4            | VCCMSSIOB4            |  |

| Т8         | VCC33SDD0             | VCC33SDD0             |  |

| Т9         | VCC15A                | VCC15A                |  |

| T10        | GNDAQ                 | GNDAQ                 |  |

| T11        | GND33ADC0             | GND33ADC0             |  |

| T12        | ADC7                  | ADC7                  |  |

| T13        | NC                    | TM4                   |  |

| T14        | NC                    | VAREF2                |  |

| T15        | VAREFOUT              | VAREFOUT              |  |

| T16        | VCCMSSIOB2            | VCCMSSIOB2            |  |

| T17        | SPI_1_DO/GPIO_24      | SPI_1_DO/GPIO_24      |  |

| T18        | GND                   | GND                   |  |

| T19        | NC                    | NC                    |  |

| T20        | NC                    | NC                    |  |

| T21        | VCCMSSIOB2            | VCCMSSIOB2            |  |

| T22        | GND                   | GND                   |  |

| U1         | GND                   | GND                   |  |

| U2         | GPIO_5/IO42RSB4V0     | GPIO_5/IO51RSB4V0     |  |

| U3         | GPIO_10/IO58RSB4V0    | GPIO_10/IO67RSB4V0    |  |

| U4         | VCCMSSIOB4            | VCCMSSIOB4            |  |

| U5         | MAC_RXD[1]/IO53RSB4V0 | MAC_RXD[1]/IO62RSB4V0 |  |

| U6         | NC                    | NC                    |  |

| U7         | VCC33AP               | VCC33AP               |  |

| U8         | VCC33N                | VCC33N                |  |

| U9         | CM1                   | CM1                   |  |

| U10        | VAREF0                | VAREF0                |  |

| U11        | GND33ADC1             | GND33ADC1             |  |

| U12        | ADC4                  | ADC4                  |  |

Notes:

1. Shading denotes pins that do not have completely identical functions from density to density. For example, the bank assignment can be different for an I/O, or the function might be available only on a larger density device.

2. \*: Indicates that the signal assigned to the pins as a CLKBUF/CLKBUF\_LVPECL/CLKBUF\_LVDS goes through a glitchless mux. In order for the glitchless mux to operate correctly, the signal must be a free-running clock signal. Refer to the 'Glitchless MUX' section in the SmartFusion Microcontroller Subsystem User's Guide for more details.

SmartFusion Customizable System-on-Chip (cSoC)

| Revision                   | Changes                                                                                                                                                                                                                                                             | Page                   |

|----------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------|

| Revision 7                 | Usage instructions, such as how to handle the pin when unused, were added for the                                                                                                                                                                                   | 5-2                    |

| (continued)                | following supply pins (SAR 29769):                                                                                                                                                                                                                                  | through                |

|                            | "VCC15A"                                                                                                                                                                                                                                                            | 5-3                    |

|                            | "VCC15ADC0" through "VCC15ADC2"                                                                                                                                                                                                                                     |                        |

|                            | "VCC33ADC0" through "VCC33ADC2"                                                                                                                                                                                                                                     |                        |

|                            | "VCC33AP"                                                                                                                                                                                                                                                           |                        |

|                            | "VCC33ADC2"                                                                                                                                                                                                                                                         |                        |

|                            | "VCCLPXTAL"                                                                                                                                                                                                                                                         |                        |

|                            | "VCCMAINXTAL"                                                                                                                                                                                                                                                       |                        |

|                            | "VCCMSSIOB2"                                                                                                                                                                                                                                                        |                        |

|                            | "VCCPLLx"                                                                                                                                                                                                                                                           |                        |

|                            | "VCCRCOSC"                                                                                                                                                                                                                                                          |                        |

|                            | "VDDBAT"                                                                                                                                                                                                                                                            |                        |

|                            | The "IO" description was revised to clarify the definitions of u, I/O pair, and w, differential pair (SAR 31147). Information on configuration of unused I/Os (including unused MSS I/Os, SAR 26891) was added (SAR 32643).                                         | 5-6                    |

|                            | Usage instructions were added for the following pins (SAR 29769):                                                                                                                                                                                                   | 5-9                    |

|                            | "MSS_RESET_N"                                                                                                                                                                                                                                                       | through                |

|                            | "TCK"                                                                                                                                                                                                                                                               | 5-13                   |

|                            | "TMS"                                                                                                                                                                                                                                                               |                        |

|                            | "TRSTB"                                                                                                                                                                                                                                                             |                        |

|                            | "MAC_CLK"                                                                                                                                                                                                                                                           |                        |

|                            | Package names used in the "Pin Assignment Tables" section were revised to match standards given in <i>Package Mechanical Drawings</i> (SAR 27395).                                                                                                                  | 5-18                   |

|                            | The pin assignments for A2F060 for "TQ144" and "FG256" have been revised due to the device status change from advance to preliminary (SAR 33068).                                                                                                                   | 5-18,<br>5-42          |

|                            | The "TQ144" and "FG256" pin assignment sections previously compared functions between A2F060/A2F200 devices in one table and A2F200/A2F500 in a separate table. Functions for all three devices have now been combined into one table for each package (SAR 33072). |                        |

|                            | The "PQ208" pin table was revised for A2F500 to remove EMC functions, which are not available for this device/package combination (SAR 33041).                                                                                                                      | 5-34                   |

| Revision 6<br>(March 2011) | The "PQ208" package was added to product tables and "Product Ordering Codes" for A2F200 and A2F500 (SAR 31005).                                                                                                                                                     | Ш                      |

|                            | The "Package I/Os: MSS + FPGA I/Os" table was revised to add the CS288 package for A2F060 and the PQ208 package for A2F200 and A2F500. A row was added for shared analog inputs (SAR 31034).                                                                        | Ш                      |

|                            | The "SmartFusion cSoC Device Status" table was updated (SAR 31084).                                                                                                                                                                                                 | Ш                      |

|                            | VCCESRAM was added to Table 2-1 • Absolute Maximum Ratings, Table 2-3 • Recommended Operating Conditions <sup>5,6</sup> , Table 2-8 • Power Supplies Configuration, and the "Supply Pins" table (SAR 31035).                                                        | 2-1, 2-3,<br>2-10, 5-1 |

|                            | The following note was removed from Table 2-8 • Power Supplies Configuration (SAR 30984):                                                                                                                                                                           | 2-10                   |

|                            | "Current monitors and temperature monitors should not be used when Power-Down and/or Sleep mode are required by the application."                                                                                                                                   |                        |

Datasheet Information

| Revision                      | Changes                                                                                                                                                                                                                                                                                                                                                                                                | Page          |

|-------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------|

| Revision 6<br>(continued)     | Dynamic power values were updated in the following tables. The table subtitles changed where FPGA I/O banks were involved to note "I/O assigned to EMC I/O pins" (SAR 30987).                                                                                                                                                                                                                          | 2-10          |

|                               | Table 2-10 • Summary of I/O Input Buffer Power (per pin) – Default I/O Software Settings                                                                                                                                                                                                                                                                                                               | 2-11          |

|                               | Table 2-13 • Summary of I/O Output Buffer Power (per pin) – Default I/O Software Settings.                                                                                                                                                                                                                                                                                                             |               |

|                               | The "Timing Model" was updated (SAR 30986).                                                                                                                                                                                                                                                                                                                                                            | 2-19          |

|                               | Values in the timing tables for the following sections were updated. Table subtitles were updated for FPGA I/O banks to note "I/O assigned to EMC I/O pins" (SAR 30986).                                                                                                                                                                                                                               |               |

|                               | "Overview of I/O Performance" section: Table 2-24, Table 2-25                                                                                                                                                                                                                                                                                                                                          | 2-23          |

|                               | "Detailed I/O DC Characteristics" section: Table 2-38, Table 2-39, Table 2-40, Table 2-44, Table 2-45, Table 2-46, Table 2-50, Table 2-51, Table 2-52, Table 2-56, Table 2-57, Table 2-58, Table 2-61, Table 2-62                                                                                                                                                                                      | 2-26          |

|                               | "LVDS" section: Table 2-65                                                                                                                                                                                                                                                                                                                                                                             | 2-40          |

|                               | "LVPECL" section: Table 2-68                                                                                                                                                                                                                                                                                                                                                                           | 2-42          |

|                               | "Global Tree Timing Characteristics" section: Table 2-80, Table 2-81                                                                                                                                                                                                                                                                                                                                   | 2-59          |

|                               | The "PQ208" section and pin tables are new (SAR 31005).                                                                                                                                                                                                                                                                                                                                                | 5-34          |

|                               | Global clocks were removed from the A2F060 pin table for the "CS288" and "FG256" packages, resulting in changed function names for affected pins (SAR 31033).                                                                                                                                                                                                                                          | 5-43          |

| Revision 5<br>(December 2010) | Table 2-2 • Analog Maximum Ratings was revised. The recommended CM[n] pad voltage (relative to ground) was changed from –11 to –0.3 (SAR 28219).                                                                                                                                                                                                                                                       | 2-2           |

|                               | Table 2-7 • Temperature and Voltage Derating Factors for Timing Delays was revised to change the values for 100°C.                                                                                                                                                                                                                                                                                     | 2-9           |

|                               | Power-down and Sleep modes, and all associated notes, were removed from Table 2-8 • Power Supplies Configuration (SAR 29479). IDC3 and IDC4 were renamed to IDC1 and IDC2 (SAR 29478). These modes are no longer supported. A note was added to the table stating that current monitors and temperature monitors should not be used when Power-down and/or Sleep mode are required by the application. | 2-10          |

|                               | The "Power-Down and Sleep Mode Implementation" section was deleted (SAR 29479).                                                                                                                                                                                                                                                                                                                        | N/A           |

|                               | Values for PAC9 and PAC10 for LVDS and LVPECL were revised in Table 2-10 • Summary of I/O Input Buffer Power (per pin) – Default I/O Software Settings and Table 2-12 • Summary of I/O Output Buffer Power (per pin) – Default I/O Software Settings*.                                                                                                                                                 | 2-10,<br>2-11 |

|                               | Values for PAC1 through PAC4, PDC1, and PDC2 were added for A2F500 in Table 2-14 • Different Components Contributing to Dynamic Power Consumption in SmartFusion cSoCs and Table 2-15 • Different Components Contributing to the Static Power Consumption in SmartFusion cSoCs                                                                                                                         | 2-12,<br>2-13 |

|                               | The equation for "Total Dynamic Power Consumption— $P_{DYN}$ " in "SoC Mode" was revised to add $P_{MSS}$ . The "Microcontroller Subsystem Dynamic Contribution— $P_{MSS}$ " section is new (SAR 29462).                                                                                                                                                                                               | 2-14,<br>2-18 |

|                               | Information in Table 2-24 • Summary of I/O Timing Characteristics—Software Default Settings (applicable to FPGA I/O banks) and Table 2-25 • Summary of I/O Timing Characteristics—Software Default Settings (applicable to MSS I/O banks) was updated.                                                                                                                                                 | 2-25          |

Datasheet Information

| Revision                  | Changes                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | Page |

|---------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------|

| Revision 3<br>(continued) | In Table 2-3 • Recommended Operating Conditions <sup>5,6</sup> , the VDDBAT recommended<br>operating range was changed from "2.97 to 3.63" to "2.7 to 3.63" (SAR 25246).<br>Recommended operating range was changed to "3.15 to 3.45" for the following<br>voltages:<br>VCC33A<br>VCC33ADCx<br>VCC33AP<br>VCC33SDDx<br>VCCMAINXTAL<br>VCCLPXTAL<br>Two notes were added to the table (SAR 27109):<br>1. The following 3.3 V supplies should be connected together while following proper<br>noise filtering practices: VCC33A, VCC33ADCx, VCC33AP, VCC33SDDx,<br>VCCMAINXTAL, and VCCLPXTAL.<br>2. The following 1.5 V supplies should be connected together while following proper | 2-3  |

|                           | noise filtering practices: VCC, VCC15A, and VCC15ADCx.<br>In Table 2-3 • Recommended Operating Conditions <sup>5,6</sup> , the description for                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | 2-3  |

|                           | VCCLPXTAL was corrected to change "32 Hz" to "32 KHz" (SAR 27110).                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |      |

|                           | The "Power Supply Sequencing Requirement" section is new (SAR 27178).                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | 2-4  |

|                           | Table 2-8 • Power Supplies Configuration was revised to change most on/off entries to voltages. Note 5 was added, stating that "on" means proper voltage is applied. The values of 6 $\mu$ A and 16 $\mu$ A were removed for IDC1 and IDC2 for 3.3 V. A note was added for IDC1 and IDC2: "Power mode and Sleep mode are consuming higher current than expected in the current version of silicon. These specifications will be updated when new version of the silicon is available" (SAR 27926).                                                                                                                                                                                  | 2-10 |

|                           | The "Power-Down and Sleep Mode Implementation" section is new (SAR 27178).                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | 2-11 |

|                           | A note was added to Table 2-86 • SmartFusion CCC/PLL Specification, pertaining to $f_{out\_CCC}$ , stating that "one of the CCC outputs (GLA0) is used as an MSS clock and is limited to 100 MHz (maximum) by software" (SAR 26388).                                                                                                                                                                                                                                                                                                                                                                                                                                                | 2-63 |