Welcome to E-XFL.COM

Embedded - System On Chip (SoC): The Heart of Modern Embedded Systems

**Embedded - System On Chip (SoC)** refers to an integrated circuit that consolidates all the essential components of a computer system into a single chip. This includes a microprocessor, memory, and other peripherals, all packed into one compact and efficient package. SoCs are designed to provide a complete computing solution, optimizing both space and power consumption, making them ideal for a wide range of embedded applications.

#### What are Embedded - System On Chip (SoC)?

**System On Chip (SoC)** integrates multiple functions of a computer or electronic system onto a single chip. Unlike traditional multi-chip solutions. SoCs combine a central

#### Details

E·XFI

| Product Status          | Obsolete                                                        |

|-------------------------|-----------------------------------------------------------------|

| Architecture            | MCU, FPGA                                                       |

| Core Processor          | ARM® Cortex®-M3                                                 |

| Flash Size              | 128KB                                                           |

| RAM Size                | 16KB                                                            |

| Peripherals             | DMA, POR, WDT                                                   |

| Connectivity            | EBI/EMI, I <sup>2</sup> C, SPI, UART/USART                      |

| Speed                   | 80MHz                                                           |

| Primary Attributes      | ProASIC®3 FPGA, 60K Gates, 1536D-Flip-Flops                     |

| Operating Temperature   | -40°C ~ 100°C (TJ)                                              |

| Package / Case          | 256-LBGA                                                        |

| Supplier Device Package | 256-FPBGA (17x17)                                               |

| Purchase URL            | https://www.e-xfl.com/product-detail/microsemi/a2f060m3e-fg256i |

|                         |                                                                 |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

SmartFusion Family Overview

## ProASIC3 FPGA Fabric

The SmartFusion cSoC family, based on the proven, low power, firm-error immune ProASIC<sup>®</sup>3 flash FPGA architecture, benefits from the advantages only flash-based devices offer:

### Reduced Cost of Ownership

Advantages to the designer extend beyond low unit cost, high performance, and ease of use. Flashbased SmartFusion cSoCs are Instant On and do not need to be loaded from an external boot PROM at each power-up. On-board security mechanisms prevent access to the programming information and enable secure remote updates of the FPGA logic. Designers can perform secure remote in-system programming (ISP) to support future design iterations and critical field upgrades, with confidence that valuable IP cannot be compromised or copied. Secure ISP can be performed using the industry standard AES algorithm with MAC data authentication on the device.

### Low Power

Flash-based SmartFusion cSoCs exhibit power characteristics similar to those of an ASIC, making them an ideal choice for power-sensitive applications. With SmartFusion cSoCs, there is no power-on current and no high current transition, both of which are common with SRAM-based FPGAs.

SmartFusion cSoCs also have low dynamic power consumption and support very low power timekeeping mode, offering further power savings.

### Security

As the nonvolatile, flash-based SmartFusion cSoC family requires no boot PROM, there is no vulnerable external bitstream. SmartFusion cSoCs incorporate FlashLock<sup>®</sup>, which provides a unique combination of reprogrammability and design security without external overhead, advantages that only a device with nonvolatile flash programming can offer.

SmartFusion cSoCs utilize a 128-bit flash-based key lock and a separate AES key to provide security for programmed IP and configuration data. The FlashROM data in Fusion devices can also be encrypted prior to loading. Additionally, the flash memory blocks can be programmed during runtime using the AES-128 block cipher encryption standard (FIPS Publication 192).

SmartFusion cSoCs with AES-based security are designed to provide protection for remote field updates over public networks, such as the Internet, and help to ensure that valuable IP remains out of the hands of system overbuilders, system cloners, and IP thieves. As an additional security measure, the FPGA configuration data of a programmed Fusion device cannot be read back, although secure design verification is possible. During design, the user controls and defines both internal and external access to the flash memory blocks.

Security, built into the FPGA fabric, is an inherent component of the SmartFusion cSoC family. The flash cells are located beneath seven metal layers, and many device design and layout techniques have been used to make invasive attacks extremely difficult. SmartFusion cSoCs, with FlashLock and AES security, are unique in being highly resistant to both invasive and noninvasive attacks. Your valuable IP is protected with industry standard security measures, making remote ISP feasible. A SmartFusion cSoC provides the highest security available for programmable logic designs.

## Single Chip

Flash-based FPGAs store their configuration information in on-chip flash cells. Once programmed, the configuration data is an inherent part of the FPGA structure, and no external configuration data needs to be loaded at system power-up (unlike SRAM-based FPGAs). Therefore, flash-based SmartFusion cSoCs do not require system configuration components such as electrically erasable programmable read-only memories (EEPROMs) or microcontrollers to load device configuration data during power-up. This reduces bill-of-materials costs and PCB area, and increases system security and reliability.

### Instant On

Flash-based SmartFusion cSoCs are Instant On. Instant On SmartFusion cSoCs greatly simplify total system design and reduce total system cost by eliminating the need for complex programmable logic devices (CPLDs). SmartFusion Instant On clocking (PLLs) replace off-chip clocking resources. In addition, glitches and brownouts in system power will not corrupt the SmartFusion flash configuration. Unlike SRAM-based FPGAs, the device will not have to be reloaded when system power is restored.

This enables reduction or complete removal of expensive voltage monitor and brownout detection devices from the PCB design. Flash-based SmartFusion cSoCs simplify total system design and reduce cost and design risk, while increasing system reliability.

### Immunity to Firm Errors

Firm errors occur most commonly when high-energy neutrons, generated in the atmosphere, strike a configuration cell of an SRAM FPGA. The energy of the collision can change the state of the configuration cell and thus change the logic, routing, or I/O configuration behavior in an unpredictable way.

Another source of radiation-induced firm errors is alpha particles. For alpha radiation to cause a soft or firm error, its source must be in very close proximity to the affected circuit. The alpha source must be in the package molding compound or in the die itself. While low-alpha molding compounds are being used increasingly, this helps reduce but does not entirely eliminate alpha-induced firm errors.

Firm errors are impossible to prevent in SRAM FPGAs. The consequence of this type of error can be a complete system failure. Firm errors do not occur in SmartFusion cSoCs. Once it is programmed, the flash cell configuration element of SmartFusion cSoCs cannot be altered by high energy neutrons and is therefore immune to errors from them. Recoverable (or soft) errors occur in the user data SRAMs of all FPGA devices. These can easily be mitigated by using error detection and correction (EDAC) circuitry built into the FPGA fabric.

## Specifying I/O States During Programming

You can modify the I/O states during programming in FlashPro. In FlashPro, this feature is supported for PDB files generated from Designer v8.5 or greater. See the *FlashPro User's Guide* for more information.

Note: PDB files generated from Designer v8.1 to Designer v8.4 (including all service packs) have limited display of Pin Numbers only.

The I/Os are controlled by the JTAG Boundary Scan register during programming, except for the analog pins (AC, AT and AV). The Boundary Scan register of the AG pin can be used to enable/disable the gate driver in software v9.0.

- 1. Load a PDB from the FlashPro GUI. You must have a PDB loaded to modify the I/O states during programming.

- 2. From the FlashPro GUI, click PDB Configuration. A FlashPoint Programming File Generator window appears.

- 3. Click the Specify I/O States During Programming button to display the Specify I/O States During Programming dialog box.

- 4. Sort the pins as desired by clicking any of the column headers to sort the entries by that header. Select the I/Os you wish to modify (Figure 1-1 on page 1-4).

- Set the I/O Output State. You can set Basic I/O settings if you want to use the default I/O settings for your pins, or use Custom I/O settings to customize the settings for each pin. Basic I/O state settings:

1 - I/O is set to drive out logic High

0 - I/O is set to drive out logic Low

Last Known State – I/O is set to the last value that was driven out prior to entering the programming mode, and then held at that value during programming

Z -Tri-State: I/O is tristated

SmartFusion DC and Switching Characteristics

# **Power Consumption of Various Internal Resources**

Table 2-14 • Different Components Contributing to Dynamic Power Consumption in SmartFusion cSoCs

|           |                                                                           | Power Supp                  |         | Device                          |          |           |          |

|-----------|---------------------------------------------------------------------------|-----------------------------|---------|---------------------------------|----------|-----------|----------|

| Parameter | Definition                                                                | Name                        | Domain  | A2F060                          | A2F200   | A2F500    | Units    |

| PAC1      | Clock contribution of a Global Rib                                        | VCC                         | 1.5 V   | 3.39                            | 3.40     | 5.05      | µW/MHz   |

| PAC2      | Clock contribution of a Global Spine                                      | VCC                         | 1.5 V   | 1.14                            | 1.83     | 2.50      | µW/MHz   |

| PAC3      | Clock contribution of a VersaTile row                                     | VCC                         | 1.5 V   | 1.15                            | 1.15     | 1.15      | µW/MHz   |

| PAC4      | Clock contribution of a VersaTile used as a sequential module             | VCC                         | 1.5 V   | 0.12                            | 0.12     | 0.12      | µW/MHz   |

| PAC5      | First contribution of a VersaTile used as a sequential module             | VCC                         | 1.5 V   | 0.07                            | 0.07     | 0.07      | µW/MHz   |

| PAC6      | Second contribution of a VersaTile used as a sequential module            | VCC                         | 1.5 V   | 0.29                            | 0.29     | 0.29      | µW/MHz   |

| PAC7      | Contribution of a VersaTile used as<br>a combinatorial module             | VCC                         | 1.5 V   | 0.29                            | 0.29     | 0.29      | µW/MHz   |

| PAC8      | Average contribution of a routing net                                     | VCC                         | 1.5 V   | 1.04                            | 0.79     | 0.79      | µW/MHz   |

| PAC9      | Contribution of an I/O input pin (standard dependent)                     | VCCxxxxIOBx/VCC             | See Tab | ole 2-10 a                      | nd Table | 2-11 on p | age 2-11 |

| PAC10     | Contribution of an I/O output pin (standard dependent)                    | VCCxxxxIOBx/VCC             | See Tab | ee Table 2-12 and Table 2-13 on |          |           | age 2-11 |

| PAC11     | Average contribution of a RAM block during a read operation               | VCC                         | 1.5 V   | 25.00                           |          |           | µW/MHz   |

| PAC12     | Average contribution of a RAM block during a write operation              | VCC                         | 1.5 V   | 30.00                           |          |           | µW/MHz   |

| PAC13     | Dynamic Contribution for PLL                                              | VCC                         | 1.5 V   |                                 | 2.60     |           | µW/MHz   |

| PAC15     | Contribution of NVM block during a read operation (F < 33MHz)             | VCC                         | 1.5 V   |                                 | 358.00   |           | µW/MHz   |

| PAC16     | 1st contribution of NVM block during<br>a read operation (F > 33MHz)      | VCC                         | 1.5 V   |                                 | 12.88    |           | mW       |

| PAC17     | 2nd contribution of NVM block<br>during a read operation (F > 33MHz)      | VCC                         | 1.5 V   |                                 | 4.80     |           | µW/MHz   |

| PAC18     | Main Crystal Oscillator contribution                                      | VCCMAINXTAL                 | 3.3 V   |                                 | 1.98     |           | mW       |

| PAC19a    | RC Oscillator contribution                                                | VCCRCOSC                    | 3.3 V   |                                 | 3.30     |           | mW       |

| PAC19b    | RC Oscillator contribution                                                | VCC                         | 1.5 V   |                                 | 3.00     |           | mW       |

| PAC20a    | Analog Block Dynamic Power<br>Contribution of the ADC                     | VCC33ADCx                   | 3.3 V   |                                 | 8.25     |           | mW       |

| PAC20b    | Analog Block Dynamic Power<br>Contribution of the ADC                     | VCC15ADCx                   | 1.5 V   |                                 | 3.00     |           | mW       |

| PAC21     | Low Power Crystal Oscillator contribution                                 | VCCLPXTAL                   | 3.3 V   |                                 | 33.00    |           | μW       |

| PAC22     | MSS Dynamic Power Contribution – Running Drysthone at 100MHz <sup>1</sup> | VCC                         | 1.5 V   |                                 | 67.50    |           | mW       |

| PAC23     | Temperature Monitor Power<br>Contribution                                 | See Table 2-94 on page 2-79 | -       |                                 | 1.23     |           | mW       |

### **Timing Characteristics**

Table 2-50 • 1.8 V LVCMOS High Slew

Worst Commercial-Case Conditions: T<sub>J</sub> = 85°C, Worst-Case VCC = 1.425 V, Worst-Case VCCxxxxIOBx = 1.7 V Applicable to FPGA I/O Banks, I/O Assigned to EMC I/O Pins

| Drive<br>Strength | Speed<br>Grade | t <sub>DOUT</sub> | t <sub>DP</sub> | t <sub>DIN</sub> | t <sub>PY</sub> | t <sub>EOUT</sub> | t <sub>ZL</sub> | t <sub>zH</sub> | t <sub>LZ</sub> | t <sub>HZ</sub> | t <sub>zLS</sub> | t <sub>zHS</sub> | Units |

|-------------------|----------------|-------------------|-----------------|------------------|-----------------|-------------------|-----------------|-----------------|-----------------|-----------------|------------------|------------------|-------|

| e                 | orado          | 50001             | ٩UP             | SDIN             | Ψř              | LOOI              | •2L             | •ZH             | ۴LZ             | ٩٢              | ·2L5             | ·2H5             | 0     |

| 2 mA              | Std.           | 0.60              | 11.06           | 0.04             | 1.14            | 0.39              | 8.61            | 11.06           | 2.61            | 1.59            | 10.67            | 13.12            | ns    |

|                   | –1             | 0.50              | 9.22            | 0.03             | 0.95            | 0.32              | 7.17            | 9.22            | 2.18            | 1.33            | 8.89             | 10.93            | ns    |

| 4 mA              | Std.           | 0.60              | 6.46            | 0.04             | 1.14            | 0.39              | 5.53            | 6.46            | 3.04            | 2.66            | 7.59             | 8.51             | ns    |

|                   | –1             | 0.50              | 5.38            | 0.03             | 0.95            | 0.32              | 4.61            | 5.38            | 2.54            | 2.22            | 6.33             | 7.10             | ns    |

| 6 mA              | Std.           | 0.60              | 4.16            | 0.04             | 1.14            | 0.39              | 3.99            | 4.16            | 3.34            | 3.18            | 6.05             | 6.22             | ns    |

|                   | -1             | 0.50              | 3.47            | 0.03             | 0.95            | 0.32              | 3.32            | 3.47            | 2.78            | 2.65            | 5.04             | 5.18             | ns    |

| 8 mA              | Std.           | 0.60              | 3.69            | 0.04             | 1.14            | 0.39              | 3.76            | 3.67            | 3.40            | 3.31            | 5.81             | 5.73             | ns    |

|                   | –1             | 0.50              | 3.07            | 0.03             | 0.95            | 0.32              | 3.13            | 3.06            | 2.84            | 2.76            | 4.85             | 4.78             | ns    |

| 12 mA             | Std.           | 0.60              | 3.38            | 0.04             | 1.14            | 0.39              | 3.44            | 2.86            | 3.50            | 3.82            | 5.50             | 4.91             | ns    |

|                   | –1             | 0.50              | 2.81            | 0.03             | 0.95            | 0.32              | 2.87            | 2.38            | 2.92            | 3.18            | 4.58             | 4.10             | ns    |

| 16 mA             | Std.           | 0.60              | 3.38            | 0.04             | 1.14            | 0.39              | 3.44            | 2.86            | 3.50            | 3.82            | 5.50             | 4.91             | ns    |

|                   | –1             | 0.50              | 2.81            | 0.03             | 0.95            | 0.32              | 2.87            | 2.38            | 2.92            | 3.18            | 4.58             | 4.10             | ns    |

Notes:

1. Software default selection highlighted in gray.

2. For specific junction temperature and voltage supply levels, refer to Table 2-7 on page 2-9 for derating values.

#### Table 2-51 • 1.8 V LVCMOS Low Slew

Worst Commercial-Case Conditions:  $T_J$  = 85°C, Worst-Case VCC = 1.425 V, Worst-Case VCCxxxxIOBx = 1.7 V Applicable to FPGA I/O Banks, I/O Assigned to EMC I/O Pins

| Drive<br>Strength | Speed<br>Grade | t <sub>DOUT</sub> | t <sub>DP</sub> | t <sub>DIN</sub> | t <sub>PY</sub> | t <sub>EOUT</sub> | t <sub>ZL</sub> | t <sub>zH</sub> | t <sub>LZ</sub> | t <sub>HZ</sub> | t <sub>zLS</sub> | t <sub>zHS</sub> | Units |

|-------------------|----------------|-------------------|-----------------|------------------|-----------------|-------------------|-----------------|-----------------|-----------------|-----------------|------------------|------------------|-------|

| 2 mA              | Std.           | 0.60              | 14.24           | 0.04             | 1.14            | 0.39              | 13.47           | 14.24           | 2.62            | 1.54            | 15.53            | 16.30            | ns    |

|                   | -1             | 0.50              | 11.87           | 0.03             | 0.95            | 0.32              | 11.23           | 11.87           | 2.18            | 1.28            | 12.94            | 13.59            | ns    |

| 4 mA              | Std.           | 0.60              | 9.74            | 0.04             | 1.14            | 0.39              | 9.92            | 9.62            | 3.05            | 2.57            | 11.98            | 11.68            | ns    |

|                   | -1             | 0.50              | 8.11            | 0.03             | 0.95            | 0.32              | 8.26            | 8.02            | 2.54            | 2.14            | 9.98             | 9.74             | ns    |

| 6 mA              | Std.           | 0.60              | 7.67            | 0.04             | 1.14            | 0.39              | 7.81            | 7.24            | 3.34            | 3.08            | 9.87             | 9.30             | ns    |

|                   | -1             | 0.50              | 6.39            | 0.03             | 0.95            | 0.32              | 6.51            | 6.03            | 2.79            | 2.56            | 8.23             | 7.75             | ns    |

| 8 mA              | Std.           | 0.60              | 7.15            | 0.04             | 1.14            | 0.39              | 7.29            | 6.75            | 3.41            | 3.21            | 9.34             | 8.80             | ns    |

|                   | -1             | 0.50              | 5.96            | 0.03             | 0.95            | 0.32              | 6.07            | 5.62            | 2.84            | 2.68            | 7.79             | 7.34             | ns    |

| 12 mA             | Std.           | 0.60              | 6.76            | 0.04             | 1.14            | 0.39              | 6.89            | 6.75            | 3.50            | 3.70            | 8.95             | 8.81             | ns    |

|                   | -1             | 0.50              | 5.64            | 0.03             | 0.95            | 0.32              | 5.74            | 5.62            | 2.92            | 3.08            | 7.46             | 7.34             | ns    |

| 16 mA             | Std.           | 0.60              | 6.76            | 0.04             | 1.14            | 0.39              | 6.89            | 6.75            | 3.50            | 3.70            | 8.95             | 8.81             | ns    |

|                   | -1             | 0.50              | 5.64            | 0.03             | 0.95            | 0.32              | 5.74            | 5.62            | 2.92            | 3.08            | 7.46             | 7.34             | ns    |

Note: For specific junction temperature and voltage supply levels, refer to Table 2-7 on page 2-9 for derating values.

| DC Parameter | Description                    | Min.  | Max. | Min.  | Max. | Min.  | Max. | Units |

|--------------|--------------------------------|-------|------|-------|------|-------|------|-------|

| VCCFPGAIOBx  | Supply Voltage                 | 3.    | 0    | 3     | .3   | 3     | .6   | V     |

| VOL          | Output Low Voltage             | 0.96  | 1.27 | 1.06  | 1.43 | 1.30  | 1.57 | V     |

| VOH          | Output High Voltage            | 1.8   | 2.11 | 1.92  | 2.28 | 2.13  | 2.41 | V     |

| VIL, VIH     | Input Low, Input High Voltages | 0     | 3.6  | 0     | 3.6  | 0     | 3.6  | V     |

| VODIFF       | Differential Output Voltage    | 0.625 | 0.97 | 0.625 | 0.97 | 0.625 | 0.97 | V     |

| VOCM         | Output Common-Mode Voltage     | 1.762 | 1.98 | 1.762 | 1.98 | 1.762 | 1.98 | V     |

| VICM         | Input Common-Mode Voltage      | 1.01  | 2.57 | 1.01  | 2.57 | 1.01  | 2.57 | V     |

| VIDIFF       | Input Differential Voltage     | 300   |      | 300   |      | 300   |      | mV    |

### Table 2-66 • Minimum and Maximum DC Input and Output Levels

#### Table 2-67 • AC Waveforms, Measuring Points, and Capacitive Loads

| Input Low (V) | Input High (V) | Measuring Point* (V) | V <sub>REF</sub> (typ.) (V) |

|---------------|----------------|----------------------|-----------------------------|

| 1.64          | 1.94           | Cross point          | -                           |

\* Measuring point =  $V_{trip.}$  See Table 2-22 on page 2-24 for a complete table of trip points.

### **Timing Characteristics**

### Table 2-68 • LVPECL

Worst Commercial-Case Conditions:  $T_J$  = 85°C, Worst-Case VCC = 1.425 V, Worst-Case VCCFPGAIOBx = 3.0 V Applicable to FPGA I/O Banks, I/O Assigned to EMC I/O Pins

| Speed Grade | t <sub>DOUT</sub> | t <sub>DP</sub> | t <sub>DIN</sub> | t <sub>PY</sub> | Units |

|-------------|-------------------|-----------------|------------------|-----------------|-------|

| Std.        | 0.60              | 1.76            | 0.04             | 1.76            | ns    |

| -1          | 0.50              | 1.46            | 0.03             | 1.46            | ns    |

Notes:

1. For the derating values at specific junction temperature and voltage supply levels, refer to Table 2-7 on page 2-9 for derating values.

2. The above mentioned timing parameters correspond to 24mA drive strength.

# **Global Resource Characteristics**

## A2F200 Clock Tree Topology

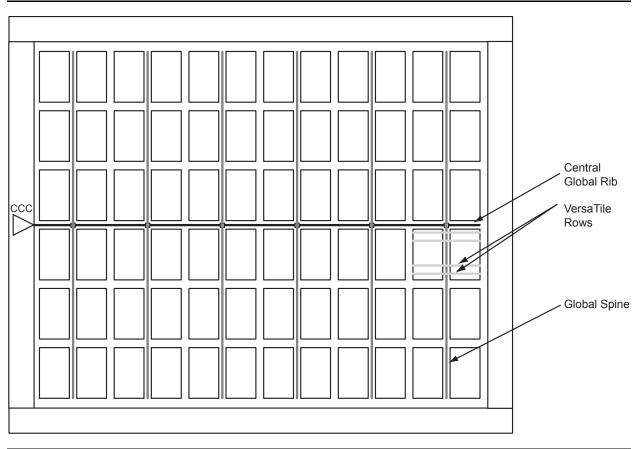

Clock delays are device-specific. Figure 2-27 is an example of a global tree used for clock routing. The global tree presented in Figure 2-27 is driven by a CCC located on the west side of the A2F200 device. It is used to drive all D-flip-flops in the device.

Figure 2-27 • Example of Global Tree Use in an A2F200 Device for Clock Routing

## **Global Tree Timing Characteristics**

Global clock delays include the central rib delay, the spine delay, and the row delay. Delays do not include I/O input buffer clock delays, as these are I/O standard–dependent, and the clock may be driven and conditioned internally by the CCC module. For more details on clock conditioning capabilities, refer to the "Clock Conditioning Circuits" section on page 2-63. Table 2-80 through Table 2-82 on page 2-61 present minimum and maximum global clock delays for the SmartFusion cSoCs. Minimum and maximum delays are measured with minimum and maximum loading.

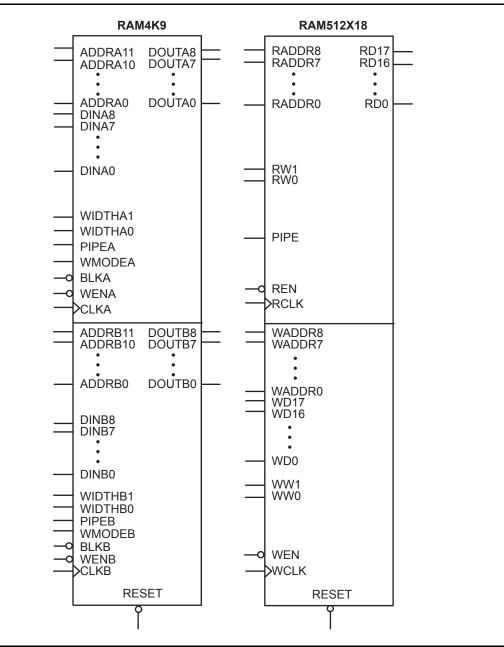

# **FPGA Fabric SRAM and FIFO Characteristics**

## **FPGA Fabric SRAM**

Figure 2-29 • RAM Models

| Parameter            | Description           | -1    | Std.  | Units |  |

|----------------------|-----------------------|-------|-------|-------|--|

| t <sub>RSTB2Q</sub>  | Reset to Q (data out) | 26.67 | 30.67 | ns    |  |

| F <sub>TCKMAX</sub>  | TCK Maximum Frequency | 19.00 | 21.85 | MHz   |  |

| t <sub>TRSTREM</sub> | ResetB Removal Time   | 0.00  | 0.00  | ns    |  |

| t <sub>TRSTREC</sub> | ResetB Recovery Time  | 0.27  | 0.31  | ns    |  |

| t <sub>TRSTMPW</sub> | ResetB Minimum Pulse  | TBD   | TBD   | ns    |  |

### Table 2-92 • JTAG 1532 Worst Commercial-Case Conditions: T<sub>J</sub> = 85°C, Worst-Case VCC = 1.425 V

Note: For specific junction temperature and voltage supply levels, refer to Table 2-7 on page 2-9 for derating values.

# static Microsemi.

SmartFusion DC and Switching Characteristics

## Comparator

Unless otherwise specified, performance is specified at 25°C with nominal power supply voltages.

| Specification                                                   | Test Condition    | IS                                   | Min. | Тур.  | Max. | Units |

|-----------------------------------------------------------------|-------------------|--------------------------------------|------|-------|------|-------|

| Input voltage range                                             | Minimum           |                                      |      | 0     |      | V     |

|                                                                 | Maximum           |                                      |      | 2.56  |      | V     |

| Input offset voltage                                            | HYS[1:0] = 00     |                                      |      | ±1    | ±3   | mV    |

|                                                                 | (no hysteresis)   |                                      |      |       |      |       |

| Input bias current                                              | Comparator 1,     | 3, 5, 7, 9 (measured at 2.56 V)      |      | 40    | 100  | nA    |

|                                                                 | Comparator 0,     | 2, 4, 6, 8 (measured at 2.56 V)      |      | 150   | 300  | nA    |

| Input resistance                                                |                   |                                      | 10   |       |      | M :   |

| Power supply rejection ratio                                    | DC (0 – 10 KHz    | <u>z</u> )                           | 50   | 60    |      | dB    |

| Propagation delay                                               | 100 mV overdri    | ve                                   |      |       |      |       |

|                                                                 | HYS[1:0] = 00     |                                      |      |       |      |       |

|                                                                 | (no hysteresis)   |                                      |      | 15    | 18   | ns    |

|                                                                 | 100 mV overdri    | ve                                   |      |       |      |       |

|                                                                 | HYS[1:0] = 10     |                                      |      |       |      |       |

|                                                                 | (with hysteresis) |                                      |      | 25    | 30   | ns    |

| Hysteresis                                                      | HYS[1:0] = 00     | Typical (25°C)                       | 0    | 0     | ±5   | mV    |

| (± refers to rising and falling threshold shifts, respectively) |                   | Across all corners (-40°C to +100°C) | 0    |       | ±5   | mV    |

| threshold shifts, respectively)                                 | HYS[1:0] = 01     | Typical (25°C)                       | ±3   | ± 16  | ±30  | mV    |

|                                                                 |                   | Across all corners (-40°C to +100°C) | 0    |       | ±36  | mV    |

|                                                                 | HYS[1:0] = 10     | Typical (25°C)                       | ±19  | ± 31  | ±48  | mV    |

|                                                                 |                   | Across all corners (-40°C to +100°C) | ±12  |       | ±54  | mV    |

|                                                                 | HYS[1:0] = 11     | Typical (25°C)                       | ±80  | ± 105 | ±190 | mV    |

|                                                                 |                   | Across all corners (-40°C to +100°C) | ±80  |       | ±194 | mV    |

| Comparator current                                              | VCC33A = 3.3      | V (operational mode); COMP_EN = 1    | 1    | •     |      | L     |

| requirements<br>(per comparator)                                | VCC33A            |                                      |      | 150   | 165  | μA    |

|                                                                 | VCC33AP           |                                      | 1    | 140   | 165  | μA    |

|                                                                 | VCC15A            |                                      |      |       | 3    | μA    |

# Inter-Integrated Circuit (I<sup>2</sup>C) Characteristics

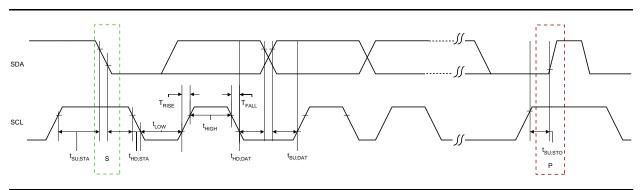

This section describes the DC and switching of the I C interface. Unless otherwise noted, all output characteristics given are for a 100 pF load on the pins. For timing parameter definitions, refer to Figure 2-48 on page 2-92.

### Table 2-101 • I<sup>2</sup>C Characteristics

### Commercial Case Conditions: T<sub>J</sub> = 85°C, V<sub>DD</sub> = 1.425 V, –1 Speed Grade

| Parameter              | Definition                                                  | Condition                                    | Value                       | Unit        |

|------------------------|-------------------------------------------------------------|----------------------------------------------|-----------------------------|-------------|

| V <sub>IL</sub>        | Minimum input low voltage                                   | _                                            | SeeTable 2-36 on page 2-30  | _           |

|                        | Maximum input low voltage                                   | -                                            | See Table 2-36              | -           |

| V <sub>IH</sub>        | Minimum input high voltage                                  | _                                            | See Table 2-36              | -           |

|                        | Maximum input high voltage                                  | _                                            | See Table 2-36              | -           |

| V <sub>OL</sub>        | Maximum output voltage low                                  | I <sub>OL</sub> = 8 mA                       | See Table 2-36              | _           |

| IIL                    | Input current high                                          | _                                            | See Table 2-36              | -           |

| I <sub>IH</sub>        | Input current low                                           | _                                            | See Table 2-36              | -           |

| V <sub>hyst</sub>      | Hysteresis of Schmitt trigger inputs                        | _                                            | See Table 2-33 on page 2-29 | V           |

| T <sub>FALL</sub>      | Fall time <sup>2</sup>                                      | VIHmin to VILMax, C <sub>load</sub> = 400 pF | 15.0                        | ns          |

|                        |                                                             | VIHmin to VILMax, C <sub>load</sub> = 100 pF | 4.0                         | ns          |

| T <sub>RISE</sub>      | Rise time <sup>2</sup>                                      | VILMax to VIHmin, C <sub>load</sub> = 400pF  | 19.5                        | ns          |

|                        |                                                             | VILMax to VIHmin, C <sub>load</sub> = 100pF  | 5.2                         | ns          |

| Cin                    | Pin capacitance                                             | VIN = 0, f = 1.0 MHz                         | 8.0                         | pF          |

| R <sub>pull-up</sub>   | Output buffer maximum pull-<br>down Resistance <sup>1</sup> | _                                            | 50                          | :           |

| R <sub>pull-down</sub> | Output buffer maximum pull-up Resistance <sup>1</sup>       | _                                            | 150                         | :           |

| D <sub>max</sub>       | Maximum data rate                                           | Fast mode                                    | 400                         | Kbps        |

| t <sub>LOW</sub>       | Low period of I2C_x_SCL <sup>3</sup>                        | _                                            | 1                           | pclk cycles |

| t <sub>HIGH</sub>      | High period of I2C_x_SCL <sup>3</sup>                       | _                                            | 1                           | pclk cycles |

| t <sub>HD;STA</sub>    | START hold time <sup>3</sup>                                | _                                            | 1                           | pclk cycles |

| t <sub>SU;STA</sub>    | START setup time <sup>3</sup>                               | _                                            | 1                           | pclk cycles |

| t <sub>HD;DAT</sub>    | DATA hold time <sup>3</sup>                                 | -                                            | 1                           | pclk cycles |

| t <sub>SU;DAT</sub>    | DATA setup time <sup>3</sup>                                | _                                            | 1                           | pclk cycles |

Notes:

1. These maximum values are provided for information only. Minimum output buffer resistance values depend on VCCxxxxIOBx, drive strength selection, temperature, and process. For board design considerations and detailed output buffer resistances, use the corresponding IBIS models located on the SoC Products Group website at http://www.microsemi.com/index.php?option=com\_microsemi&Itemid=489&Iang=en&view=salescontact.

These values are provided for a load of 100 pF and 400 pF. For board design considerations and detailed output buffer resistances, use the corresponding IBIS models located on the SoC Products Group website at http://www.microsemi.com/index.php?option=com\_microsemi&Itemid=489&Iang=en&view=salescontact.

3. For allowable Pclk configurations, refer to the Inter-Integrated Circuit (I<sup>2</sup>C) Peripherals section in the SmartFusion Microcontroller Subsystem User's Guide.

# **Microsemi**.

SmartFusion DC and Switching Characteristics

#### Table 2-101 • I<sup>2</sup>C Characteristics Commercial Case Conditions: T<sub>J</sub> = 85°C, V<sub>DD</sub> = 1.425 V, –1 Speed Grade (continued)

| Parameter           | Definition                   | Definition Condition |    |             |

|---------------------|------------------------------|----------------------|----|-------------|

| t <sub>SU;STO</sub> | STOP setup time <sup>3</sup> | -                    | 1  | pclk cycles |

| t <sub>FILT</sub>   | Maximum spike width filtered | -                    | 50 | ns          |

Notes:

- 1. These maximum values are provided for information only. Minimum output buffer resistance values depend on VCCxxxxIOBx, drive strength selection, temperature, and process. For board design considerations and detailed output buffer resistances, use the corresponding IBIS models located on the SoC Products Group website at http://www.microsemi.com/index.php?option=com\_microsemi&ltemid=489&lang=en&view=salescontact.

- These values are provided for a load of 100 pF and 400 pF. For board design considerations and detailed output buffer resistances, use the corresponding IBIS models located on the SoC Products Group website at http://www.microsemi.com/index.php?option=com\_microsemi&Itemid=489&Iang=en&view=salescontact.

- 3. For allowable Pclk configurations, refer to the Inter-Integrated Circuit (I<sup>2</sup>C) Peripherals section in the SmartFusion Microcontroller Subsystem User's Guide.

Figure 2-48 • I2C Timing Parameter Definition

## **Embedded Design**

Microsemi offers FREE SoftConsole Eclipse based IDE, which includes the GNU C/C++ compiler and GDB debugger. Microsemi also offers evaluation versions of software from Keil and IAR, with full versions available from respective suppliers.

## **Analog Design**

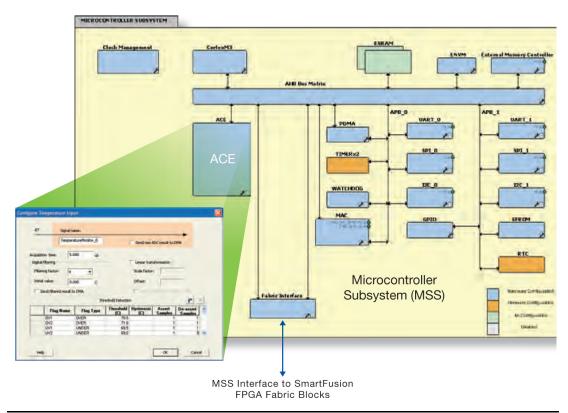

The MSS configurator provides graphical configuration for current, voltage and temperature monitors, sample sequencing setup and post-processing configuration, as well as DAC output.

The MSS configurator creates a bridge between the FPGA fabric and embedded designers so device configuration can be easily shared between multiple developers.

The MSS configurator includes the following:

- A simple configurator for the embedded designer to control the MSS peripherals and I/Os

- A method to import and view a hardware configuration from the FPGA flow into the embedded flow containing the memory map

- · Automatic generation of drivers for any peripherals or soft IP used in the system configuration

- · Comprehensive analog configuration for the programmable analog components

- Creation of a standard MSS block to be used in SmartDesign for connection of FPGA fabric designs and IP

Figure 3-2 • MSS Configurator

## **Compile and Debug**

Microsemi's SoftConsole is a free Eclipse-based IDE that enables the rapid production of C and C++ executables for Microsemi FPGA and cSoCs using Cortex-M3, Cortex-M1 and Core8051s. For SmartFusion support, SoftConsole includes the GNU C/C++ compiler and GDB debugger. Additional examples can be found on the SoftConsole page:

- Using UART with SmartFusion: SoftConsole Standalone Flow Tutorial

- Design Files

- Displaying POT Level with LEDs: Libero SoC and SoftConsole Flow Tutorial for SmartFusion

- Design Files

IAR Embedded Workbench<sup>®</sup> for ARM/Cortex is an integrated development environment for building and debugging embedded ARM applications using assembler, C and C++. It includes a project manager, editor, build and debugger tools with support for RTOS-aware debugging on hardware or in a simulator.

- Designing SmartFusion cSoC with IAR Systems

- IAR Embedded Workbench IDE User Guide for ARM

- Download Evaluation or Kickstart version of IAR Embedded Workbench for ARM

Keil's Microcontroller Development Kit comes in two editions: MDK-ARM and MDK Basic. Both editions feature  $\mu$ Vision<sup>®</sup>, the ARM Compiler, MicroLib, and RTX, but the MDK Basic edition is limited to 256K so that small applications are more affordable.

- Designing SmartFusion cSoC with Keil

- Using Keil µVision and Microsemi SmartFusion cSoC

- Programming file for use with this tutorial

- Keil Microcontroller Development Kit for ARM Product Manuals

- Download Evaluation version of Keil MDK-ARM

| COMPLIANT<br>RRM® Cortex® Hicrocontroller<br>Software Interface Standard | Microsemi.            | An ARM <sup>®</sup> Company | <b>SYSTEMS</b>        |

|--------------------------------------------------------------------------|-----------------------|-----------------------------|-----------------------|

| Software IDE                                                             | SoftConsole           | Vision IDE                  | Embedded Workbench    |

| Website                                                                  | www.microsemi.com/soc | www.keil.com                | www.iar.com           |

| Free versions from SoC<br>Products Group                                 | Free with Libero SoC  | 32 K code limited           | 32 K code limited     |

| Available from Vendor                                                    | N/A                   | Full version                | Full version          |

| Compiler                                                                 | GNU GCC               | RealView C/C++              | IAR ARM Compiler      |

| Debugger                                                                 | GDB debug             | Vision Debugger             | C-SPY Debugger        |

| Instruction Set Simulator                                                | No                    | Vision Simulator            | Yes                   |

| Debug Hardware                                                           | FlashPro4             | ULINK2 or ULINK-ME          | J-LINK or J-LINK Lite |

## **Operating Systems**

FreeRTOS<sup>™</sup> is a portable, open source, royalty free, mini real-time kernel (a free-to-download and freeto-deploy RTOS that can be used in commercial applications without any requirement to expose your proprietary source code). FreeRTOS is scalable and designed specifically for small embedded systems. This FreeRTOS version ported by Microsemi is 6.0.1. For more information, visit the FreeRTOS website: www.freertos.org

- SmartFusion Webserver Demo Using uIP and FreeRTOS

- SmartFusion cSoC: Running Webserver, TFTP on IwIP TCP/IP Stack Application Note

Emcraft Systems provides porting of the open-source U-boot firmware and uClinux<sup>™</sup> kernel to the SmartFusion cSoC, a Linux<sup>®</sup>-based cross-development framework, and other complementary components. Combined with the release of its A2F-Linux Evaluation Kit, this provides a low-cost platform for evaluation and development of Linux (uClinux) on the Cortex-M3 CPU core of the Microsemi SmartFusion cSoC.

• Emcraft Linux on Microsemi's SmartFusion cSoC

Keil offers the RTX Real-Time Kernel as a royalty-free, deterministic RTOS designed for ARM and Cortex-M devices. It allows you to create programs that simultaneously perform multiple functions and helps to create applications which are better structured and more easily maintained.

- The RTX Real-Time Kernel is included with MDK-ARM. Download the Evaluation version of Keil MDK-ARM.

- RTX source code is available as part of Keil/ARM Real-Time Library (RL-ARM), a group of tightlycoupled libraries designed to solve the real-time and communication challenges of embedded systems based on ARM-powered microcontroller devices. The RL-ARM library now supports SmartFusion cSoCs and designers with additional key features listed in the "Middleware" section on page 3-5.

Micrium supports SmartFusion cSoCs with the company's flagship  $\mu$ C/OS family, recognized for a variety of features and benefits, including unparalleled reliability, performance, dependability, impeccable source code and vast documentation. Micrium supports the following products for SmartFusion cSoCs and continues to work with Microsemi on additional projects.

- SmartFusion Quickstart Guide for Micrium µC/OS-III Examples

- Design Files

µC/OS-III™, Micrium's newest RTOS, is designed to save time on your next embedded project and puts greater control of the software in your hands.

RoweBots provides an ultra tiny Linux-compatible RTOS called Unison for SmartFusion. Unison consists of a set of modular software components, which, like Linux, are either free or commercially licensed. Unison offers POSIX<sup>®</sup> and Linux compatibility with hard real-time performance, complete I/O modules and an easily understood environment for device driver programming. Seamless integration with FPGA and analog features are fast and easy.

- Unison V4-based products include a free Unison V4 Linux and POSIX-compatible kernel with serial I/O, file system, six demonstration programs, upgraded documentation and source code for Unison V4, and free (for non-commercial use) Unison V4 TCP/IP server. Commercial license upgrade is available for Unison V4 TCP/IP server with three demonstration programs, DHCP client and source code.

- Unison V5-based products include commercial Unison V5 Linux- and POSIX-compatible kernel with serial I/O, file system, extensive feature set, full documentation, source code and more than 20 demonstration programs, Unison V5 TCP/IPv4 with extended feature set, sockets interface, multiple network interfaces, PPP support, DHCP client, documentation, source code and six demonstration programs, and multiple other features.

# Middleware

Microsemi has ported both uIP and IwIP for Ethernet support as well as including TFTP file service.

- SmartFusion Webserver Demo Using uIP and FreeRTOS

- SmartFusion: Running Webserver, TFTP on IwIP TCP/IP Stack Application Note

The Keil/ARM Real-Time Library (RL-ARM)<sup>1</sup>, in addition to RTX source, includes the following:

RL-TCPnet (TCP/IP) – The Keil RL-TCPnet library, supporting full TCP/IP and UDP protocols, is a full networking suite specifically written for small ARM and Cortex-M processor-based microcontrollers. TCPnet is now ported to and supports SmartFusion Cortex-M3. It is highly optimized, has a small code footprint, and gives excellent performance, providing a wide range of application level protocols and examples such as FTP, SNMP, SOAP and AJAX. An HTTP server example of TCPnet working in a SmartFusion design is available.

<sup>1.</sup> The CAN and USB functions within RL-ARM are not supported for SmartFusion cSoC.

**CS288** Pin A2F060 Function A2F200 Function A2E500 Eunction No. IO17NDB0V0 GBA2/IO20PDB1V0 GBA2/IO27PDB1V0 C21 EMC DB[14]/IO45NDB5V0 EMC DB[14]/GAB2/IO71NDB5V0 EMC DB[14]/GAB2/IO88NDB5V0 D1 D3 VCCFPGAIOB5 VCCFPGAIOB5 VCCFPGAIOB5 D19 GND GND GND VCCFPGAIOB1 D21 VCCFPGAIOB1 VCCFPGAIOB1 EMC DB[13]/GAC2/IO70PDB5V0 EMC DB[13]/GAC2/IO87PDB5V0 E1 EMC DB[13]/IO44PDB5V0 EMC DB[12]/IO44NDB5V0 EMC DB[12]/IO70NDB5V0 EMC DB[12]/IO87NDB5V0 E3 E5 GNDQ GNDQ GNDQ EMC BYTEN[0]/IO02NDB0V0 EMC BYTEN[0]/GAC0/IO02NDB0V0 EMC BYTEN[0]/GAC0/IO07NDB0V0 E6 EMC BYTEN[1]/IO02PDB0V0 EMC BYTEN[1]/GAC1/IO02PDB0V0 EMC BYTEN[1]/GAC1/IO07PDB0V0 E7 EMC OEN1 N/IO03PDB0V0 EMC OEN1 N/IO03PDB0V0 EMC OEN1 N/IO08PDB0V0 F8 EMC AB[3]/IO05PDB0V0 EMC AB[3]/IO05PDB0V0 EMC AB[3]/IO09PDB0V0 E9 E10 EMC AB[10]/IO09NDB0V0 EMC AB[10]/IO09NDB0V0 EMC AB[10]/IO11NDB0V0 EMC AB[7]/IO07PDB0V0 EMC AB[7]/IO07PDB0V0 EMC AB[7]/IO12PDB0V0 F11 E12 EMC AB[13]/IO10PDB0V0 EMC AB[13]/IO10PDB0V0 EMC AB[13]/IO14PDB0V0 E13 EMC AB[16]/IO12NDB0V0 EMC AB[16]/IO12NDB0V0 EMC AB[16]/IO17NDB0V0 E14 EMC AB[17]/IO12PDB0V0 EMC AB[17]/IO12PDB0V0 EMC AB[17]/IO17PDB0V0 E15 GCC0/IO18NPB0V0 GCB0/IO27NDB1V0 GCB0/IO34NDB1V0 E16 GCA1/IO20PPB0V0 GCB1/IO27PDB1V0 GCB1/IO34PDB1V0 E17 GCC1/IO18PPB0V0 GCB2/IO24PDB1V0 GCB2/IO33PDB1V0 GCA0/IO36NDB1V0 \* E19 GCB2/IO22PPB1V0 GCA0/IO28NDB1V0 E21 IO21NDB1V0 GCA1/IO28PDB1V0 GCA1/IO36PDB1V0 \* VCCFPGAIOB5 F1 VCCFPGAIOB5 VCCFPGAIOB5 F3 GFB2/IO42NDB5V0 GFB2/IO68NDB5V0 GFB2/IO85NDB5V0 F5 GFA2/IO42PDB5V0 GFA2/IO68PDB5V0 GFA2/IO85PDB5V0 F6 EMC DB[11]/IO43PDB5V0 EMC DB[11]/IO69PDB5V0 EMC DB[11]/IO86PDB5V0 F7 GND GND GND NC GFC1/IO66PPB5V0 GFC1/IO83PPB5V0 F8 F9 VCCFPGAIOB0 VCCFPGAIOB0 VCCFPGAIOB0 EMC AB[11]/IO09PDB0V0 F10 EMC AB[11]/IO09PDB0V0 EMC AB[11]/IO11PDB0V0 F11 EMC AB[6]/IO07NDB0V0 EMC AB[6]/IO07NDB0V0 EMC AB[6]/IO12NDB0V0

#### Notes:

🔨 🤄 Microsemi

Pin Descriptions

1. Shading denotes pins that do not have completely identical functions from density to density. For example, the bank assignment can be different for an I/O, or the function might be available only on a larger density device.

\*: Indicates that the signal assigned to the pins as a CLKBUF/CLKBUF\_LVPECL/CLKBUF\_LVDS goes through a glitchless mux. In order for the glitchless mux to operate correctly, the signal must be a free-running clock signal. Refer to the 'Glitchless MUX' section in the SmartFusion Microcontroller Subsystem User's Guide for more details.

|            | PQ208                 |                       |  |

|------------|-----------------------|-----------------------|--|

| Pin Number | A2F200                | A2F500                |  |

| 32         | VCCRCOSC              | VCCRCOSC              |  |

| 33         | MSS_RESET_N           | MSS_RESET_N           |  |

| 34         | VCCESRAM              | VCCESRAM              |  |

| 35         | MAC_MDC/IO48RSB4V0    | MAC_MDC/IO57RSB4V0    |  |

| 36         | MAC_MDIO/IO49RSB4V0   | MAC_MDIO/IO58RSB4V0   |  |

| 37         | MAC_TXEN/IO52RSB4V0   | MAC_TXEN/IO61RSB4V0   |  |

| 38         | MAC_CRSDV/IO51RSB4V0  | MAC_CRSDV/IO60RSB4V0  |  |

| 39         | MAC_RXER/IO50RSB4V0   | MAC_RXER/IO59RSB4V0   |  |

| 40         | GND                   | GND                   |  |

| 41         | VCCMSSIOB4            | VCCMSSIOB4            |  |

| 42         | VCC                   | VCC                   |  |

| 43         | MAC_TXD[0]/IO56RSB4V0 | MAC_TXD[0]/IO65RSB4V0 |  |

| 44         | MAC_TXD[1]/IO55RSB4V0 | MAC_TXD[1]/IO64RSB4V0 |  |

| 45         | MAC_RXD[0]/IO54RSB4V0 | MAC_RXD[0]/IO63RSB4V0 |  |

| 46         | MAC_RXD[1]/IO53RSB4V0 | MAC_RXD[1]/IO62RSB4V0 |  |

| 47         | MAC_CLK               | MAC_CLK               |  |

| 48         | GNDSDD0               | GNDSDD0               |  |

| 49         | VCC33SDD0             | VCC33SDD0             |  |

| 50         | VCC15A                | VCC15A                |  |

| 51         | PCAP                  | PCAP                  |  |

| 52         | NCAP                  | NCAP                  |  |

| 53         | VCC33AP               | VCC33AP               |  |

| 54         | VCC33N                | VCC33N                |  |

| 55         | SDD0                  | SDD0                  |  |

| 56         | GNDA                  | GNDA                  |  |

| 57         | GNDAQ                 | GNDAQ                 |  |

| 58         | ABPS0                 | ABPS0                 |  |

| 59         | ABPS1                 | ABPS1                 |  |

| 60         | CM0                   | СМО                   |  |

| 61         | ТМО                   | ТМО                   |  |

| 62         | GNDTM0                | GNDTM0                |  |

Notes:

1. Shading denotes pins that do not have completely identical functions from density to density. For example, the bank assignment can be different for an I/O, or the function might be available only on a larger density device.

2. \*: Indicates that the signal assigned to the pins as a CLKBUF/CLKBUF\_LVPECL/CLKBUF\_LVDS goes through a glitchless mux. In order for the glitchless mux to operate correctly, the signal must be a free-running clock signal. Refer to the 'Glitchless MUX' section in the SmartFusion Microcontroller Subsystem User's Guide for more details.

🌜 Microsemi.

SmartFusion Customizable System-on-Chip (cSoC)

| Pin |                 | FG256           |                 |

|-----|-----------------|-----------------|-----------------|

| No. | A2F060 Function | A2F200 Function | A2F500 Function |

| Т9  | VAREF0          | VAREF1          | VAREF1          |

| T10 | ABPS0           | ABPS6           | ABPS6           |

| T11 | NC              | ABPS5           | ABPS5           |

| T12 | NC              | SDD1            | SDD1            |

| T13 | GNDVAREF        | GNDVAREF        | GNDVAREF        |

| T14 | GNDMAINXTAL     | GNDMAINXTAL     | GNDMAINXTAL     |

| T15 | VCCLPXTAL       | VCCLPXTAL       | VCCLPXTAL       |

| T16 | PU_N            | PU_N            | PU_N            |

Notes:

1. Shading denotes pins that do not have completely identical functions from density to density. For example, the bank assignment can be different for an I/O, or the function might be available only on a larger density device.

2. \*: Indicates that the signal assigned to the pins as a CLKBUF/CLKBUF\_LVPECL/CLKBUF\_LVDS goes through a glitchless mux. In order for the glitchless mux to operate correctly, the signal must be a free-running clock signal. Refer to the 'Glitchless MUX' section in the SmartFusion Microcontroller Subsystem User's Guide for more details.

|            | FG484                           |                            |  |

|------------|---------------------------------|----------------------------|--|

| Pin Number | A2F200 Function A2F500 Function |                            |  |

| C15        | EMC_AB[17]/IO12PDB0V0           | EMC_AB[17]/IO17PDB0V0      |  |

| C16        | EMC_AB[24]/IO16NDB0V0           | EMC_AB[24]/IO20NDB0V0      |  |

| C17        | EMC_AB[22]/IO15NDB0V0           | EMC_AB[22]/IO19NDB0V0      |  |

| C18        | EMC_AB[23]/IO15PDB0V0           | EMC_AB[23]/IO19PDB0V0      |  |

| C19        | GBA0/IO19NPB0V0                 | GBA0/IO23NPB0V0            |  |

| C20        | NC                              | NC                         |  |

| C21        | GBC2/IO21PDB1V0                 | GBC2/IO30PDB1V0            |  |

| C22        | GBB2/IO20NDB1V0                 | GBB2/IO27NDB1V0            |  |

| D1         | GND                             | GND                        |  |

| D2         | EMC_DB[12]/IO70NDB5V0           | EMC_DB[12]/IO87NDB5V0      |  |

| D3         | EMC_DB[13]/GAC2/IO70PDB5V0      | EMC_DB[13]/GAC2/IO87PDB5V0 |  |

| D4         | NC                              | NC                         |  |

| D5         | NC                              | NC                         |  |

| D6         | GND                             | GND                        |  |

| D7         | NC                              | IO00NPB0V0                 |  |

| D8         | NC                              | IO03NPB0V0                 |  |

| D9         | GND                             | GND                        |  |

| D10        | EMC_OEN0_N/IO03NDB0V0           | EMC_OEN0_N/IO08NDB0V0      |  |

| D11        | EMC_AB[10]/IO09NDB0V0           | EMC_AB[10]/IO11NDB0V0      |  |

| D12        | EMC_AB[11]/IO09PDB0V0           | EMC_AB[11]/IO11PDB0V0      |  |

| D13        | EMC_AB[9]/IO08PDB0V0            | EMC_AB[9]/IO13PDB0V0       |  |

| D14        | GND                             | GND                        |  |

| D15        | GBC1/IO17PPB0V0                 | GBC1/IO22PPB0V0            |  |

| D16        | EMC_AB[25]/IO16PDB0V0           | EMC_AB[25]/IO20PDB0V0      |  |

| D17        | GND                             | GND                        |  |

| D18        | GBA1/IO19PPB0V0                 | GBA1/IO23PPB0V0            |  |

| D19        | NC                              | NC                         |  |

| D20        | NC                              | NC                         |  |

| D21        | IO21NDB1V0                      | IO30NDB1V0                 |  |

| D22        | GND                             | GND                        |  |

| E1         | GFC2/IO67PPB5V0                 | GFC2/IO84PPB5V0            |  |

| E2         | VCCFPGAIOB5                     | VCCFPGAIOB5                |  |

| E3         | GFA2/IO68PDB5V0                 | GFA2/IO85PDB5V0            |  |

| E4         | GND                             | GND                        |  |

| Notes:     | 1                               |                            |  |

Notes:

1. Shading denotes pins that do not have completely identical functions from density to density. For example, the bank assignment can be different for an I/O, or the function might be available only on a larger density device.

\*: Indicates that the signal assigned to the pins as a CLKBUF/CLKBUF\_LVPECL/CLKBUF\_LVDS goes through a glitchless mux. In order for the glitchless mux to operate correctly, the signal must be a free-running clock signal. Refer to the 'Glitchless MUX' section in the SmartFusion Microcontroller Subsystem User's Guide for more details.

🕓 Microsemi.

SmartFusion Customizable System-on-Chip (cSoC)

|            | FG484           |                 |  |

|------------|-----------------|-----------------|--|

| Pin Number | A2F200 Function | A2F500 Function |  |

| L9         | VCC             | VCC             |  |

| L10        | GND             | GND             |  |

| L11        | VCC             | VCC             |  |

| L12        | GND             | GND             |  |

| L13        | VCC             | VCC             |  |

| L14        | GND             | GND             |  |

| L15        | VCC             | VCC             |  |

| L16        | GND             | GND             |  |

| L17        | GNDQ            | GNDQ            |  |

| L18        | GDA2/IO33NDB1V0 | GDA2/IO42NDB1V0 |  |

| L19        | VCCFPGAIOB1     | VCCFPGAIOB1     |  |

| L20        | GDB1/IO30PDB1V0 | GDB1/IO39PDB1V0 |  |

| L21        | GDB0/IO30NDB1V0 | GDB0/IO39NDB1V0 |  |

| L22        | GDC2/IO32PDB1V0 | GDC2/IO41PDB1V0 |  |

| M1         | NC              | IO71PDB5V0      |  |

| M2         | NC              | IO71NDB5V0      |  |

| M3         | VCCFPGAIOB5     | VCCFPGAIOB5     |  |

| M4         | NC              | IO72NPB5V0      |  |

| M5         | GNDQ            | GNDQ            |  |

| M6         | NC              | IO68PDB5V0      |  |

| M7         | GND             | GND             |  |

| M8         | VCC             | VCC             |  |

| M9         | GND             | GND             |  |

| M10        | VCC             | VCC             |  |

| M11        | GND             | GND             |  |

| M12        | VCC             | VCC             |  |

| M13        | GND             | GND             |  |

| M14        | VCC             | VCC             |  |

| M15        | GND             | GND             |  |

| M16        | VCCFPGAIOB1     | VCCFPGAIOB1     |  |

| M17        | NC              | NC              |  |

| M18        | GDB2/IO33PDB1V0 | GDB2/IO42PDB1V0 |  |

| M19        | VJTAG           | VJTAG           |  |

| M20        | GND             | GND             |  |

Notes:

1. Shading denotes pins that do not have completely identical functions from density to density. For example, the bank assignment can be different for an I/O, or the function might be available only on a larger density device.

2. \*: Indicates that the signal assigned to the pins as a CLKBUF/CLKBUF\_LVPECL/CLKBUF\_LVDS goes through a glitchless mux. In order for the glitchless mux to operate correctly, the signal must be a free-running clock signal. Refer to the 'Glitchless MUX' section in the SmartFusion Microcontroller Subsystem User's Guide for more details.

# **Microsemi**.

SmartFusion Customizable System-on-Chip (cSoC)

| Revision                       | Changes                                                                                                                                                                                                                                                                                                                                                                                                                                    | Page |

|--------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------|

| Revision 10<br>(continued)     | Corrected the Start-up time unit from "ms" to "µs" in Table 2-99 • Voltage Regulator (SAR 39395).                                                                                                                                                                                                                                                                                                                                          | 2-87 |

|                                | Added the "References" section for "SmartFusion Development Tools" (SAR 43460).                                                                                                                                                                                                                                                                                                                                                            | 3-1  |

|                                | Updated the "References" section for Programming (SAR 43304). Added the "Application Notes on IAP Programming Technique" section (SAR 43458).                                                                                                                                                                                                                                                                                              | 4-9  |

|                                | A note was added to the "Supply Pins" table, referring to the <i>SmartFusion cSoC</i><br><i>Board Design Guidelines</i> application note for details on VCCPLLx capacitor<br>recommendations (SAR 42183).                                                                                                                                                                                                                                  | 5-1  |

|                                | In the "Supply Pins" section, the VPP capacitor value section has been modified to:<br>"For proper programming, $0.01\mu$ F, and $0.1\mu$ F to $1\mu$ F capacitors, (both rated at 16 V)<br>are to be connected in parallel across VPP and GND, and positioned as close to the<br>FPGA pins as possible." (SAR 43569).                                                                                                                     | 5-1  |

|                                | In the "User-Defined Supply Pins" section, added description 'These pins are located in Bank-2 (GPIO_16 to GPIO_31) for A2F060, A2F200, and A2F500 devices.' for GPIO_x (SAR 28595).                                                                                                                                                                                                                                                       | 5-5  |

|                                | Updated the MAINXIN and MAINXOUT pin descriptions in the "Special Function Pins" section to read "If an external RC network or clock input is used, the RC components are connected to the MAINXIN pin, with MAINXOUT left floating. When the main crystal oscillator is not being used, MAINXIN and MAINXOUT pins can be left floating." (SAR 42807).                                                                                     | 5-8  |

|                                | Live at Power-Up (LAPU) has been replaced with 'Instant On'.                                                                                                                                                                                                                                                                                                                                                                               | NA   |

| Revision 9<br>(September 2012) | The number of signal conditioning blocks (SCBs) for A2F500 in the "SmartFusion cSoC Family Product Table" was corrected to 4. Previously it had incorrectly been listed as 2 (SAR 39536).                                                                                                                                                                                                                                                  | II   |

|                                | The "Product Ordering Codes" section was revised to clarify that only one eNVM size for each device is currently available (SAR 40333).                                                                                                                                                                                                                                                                                                    | VI   |

|                                | Information pertaining to analog I/Os was added to the "Specifying I/O States During Programming" section on page 1-3 (SAR 34836).                                                                                                                                                                                                                                                                                                         | 1-3  |

|                                | The formulas in the table notes for Table 2-29 • I/O Weak Pull-Up/Pull-Down Resistances were corrected (SAR 34757).                                                                                                                                                                                                                                                                                                                        | 2-27 |

|                                | Maximum values for VIL and VIH were corrected in LVPECL Table 2-66 • Minimum and Maximum DC Input and Output Levels (SAR 37695).                                                                                                                                                                                                                                                                                                           | 2-43 |

|                                | Minimum pulse width High and Low values were added to the tables in the "Global Tree Timing Characteristics" section. The maximum frequency for global clock parameter was removed from these tables because a frequency on the global is only an indication of what the global network can do. There are other limiters such as the SRAM, I/Os, and PLL. SmartTime software should be used to determine the design frequency (SAR 29270). | 2-59 |

|                                | The temperature range for accuracy in Table 2-83 • Electrical Characteristics of the RC Oscillator was changed from "0°C to 85°C" to "-40°C to 100°C" (SAR 33670). The units for jitter were changed from ps to ps RMS (SAR 34270).                                                                                                                                                                                                        | 2-61 |

|                                | In Table 2-84 • Electrical Characteristics of the Main Crystal Oscillator, the output jitter for the 10 MHz crystal was corrected from 50 ps RMS to 1 ns RS (SAR 32939). Values for the startup time of VILXTAL were added (SAR 25248).                                                                                                                                                                                                    | 2-62 |

|                                | In Table 2-85 • Electrical Characteristics of the Low Power Oscillator, output jitter was changed from 50 ps RMS to 30 ps RMS (SAR 32939). A value for ISTBXTAL standby current was added (SAR 25249). Startup time for a test load of 30 pF was added (SAR 27436).                                                                                                                                                                        | 2-62 |