Welcome to E-XFL.COM

#### Embedded - System On Chip (SoC): The Heart of Modern Embedded Systems

**Embedded - System On Chip (SoC)** refers to an integrated circuit that consolidates all the essential components of a computer system into a single chip. This includes a microprocessor, memory, and other peripherals, all packed into one compact and efficient package. SoCs are designed to provide a complete computing solution, optimizing both space and power consumption, making them ideal for a wide range of embedded applications.

#### What are Embedded - System On Chip (SoC)?

**System On Chip (SoC)** integrates multiple functions of a computer or electronic system onto a single chip. Unlike traditional multi-chip solutions. SoCs combine a central

#### Details

E·XFI

| Product Status          | Obsolete                                                       |

|-------------------------|----------------------------------------------------------------|

| Architecture            | MCU, FPGA                                                      |

| Core Processor          | ARM® Cortex®-M3                                                |

| Flash Size              | 128KB                                                          |

| RAM Size                | 16KB                                                           |

| Peripherals             | DMA, POR, WDT                                                  |

| Connectivity            | EBI/EMI, I <sup>2</sup> C, SPI, UART/USART                     |

| Speed                   | 80MHz                                                          |

| Primary Attributes      | ProASIC®3 FPGA, 60K Gates, 1536D-Flip-Flops                    |

| Operating Temperature   | 0°C ~ 85°C (TJ)                                                |

| Package / Case          | 144-LQFP                                                       |

| Supplier Device Package | 144-TQFP (20x20)                                               |

| Purchase URL            | https://www.e-xfl.com/product-detail/microsemi/a2f060m3e-tq144 |

|                         |                                                                |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

SmartFusion Family Overview

# ProASIC3 FPGA Fabric

The SmartFusion cSoC family, based on the proven, low power, firm-error immune ProASIC<sup>®</sup>3 flash FPGA architecture, benefits from the advantages only flash-based devices offer:

### Reduced Cost of Ownership

Advantages to the designer extend beyond low unit cost, high performance, and ease of use. Flashbased SmartFusion cSoCs are Instant On and do not need to be loaded from an external boot PROM at each power-up. On-board security mechanisms prevent access to the programming information and enable secure remote updates of the FPGA logic. Designers can perform secure remote in-system programming (ISP) to support future design iterations and critical field upgrades, with confidence that valuable IP cannot be compromised or copied. Secure ISP can be performed using the industry standard AES algorithm with MAC data authentication on the device.

### Low Power

Flash-based SmartFusion cSoCs exhibit power characteristics similar to those of an ASIC, making them an ideal choice for power-sensitive applications. With SmartFusion cSoCs, there is no power-on current and no high current transition, both of which are common with SRAM-based FPGAs.

SmartFusion cSoCs also have low dynamic power consumption and support very low power timekeeping mode, offering further power savings.

### Security

As the nonvolatile, flash-based SmartFusion cSoC family requires no boot PROM, there is no vulnerable external bitstream. SmartFusion cSoCs incorporate FlashLock<sup>®</sup>, which provides a unique combination of reprogrammability and design security without external overhead, advantages that only a device with nonvolatile flash programming can offer.

SmartFusion cSoCs utilize a 128-bit flash-based key lock and a separate AES key to provide security for programmed IP and configuration data. The FlashROM data in Fusion devices can also be encrypted prior to loading. Additionally, the flash memory blocks can be programmed during runtime using the AES-128 block cipher encryption standard (FIPS Publication 192).

SmartFusion cSoCs with AES-based security are designed to provide protection for remote field updates over public networks, such as the Internet, and help to ensure that valuable IP remains out of the hands of system overbuilders, system cloners, and IP thieves. As an additional security measure, the FPGA configuration data of a programmed Fusion device cannot be read back, although secure design verification is possible. During design, the user controls and defines both internal and external access to the flash memory blocks.

Security, built into the FPGA fabric, is an inherent component of the SmartFusion cSoC family. The flash cells are located beneath seven metal layers, and many device design and layout techniques have been used to make invasive attacks extremely difficult. SmartFusion cSoCs, with FlashLock and AES security, are unique in being highly resistant to both invasive and noninvasive attacks. Your valuable IP is protected with industry standard security measures, making remote ISP feasible. A SmartFusion cSoC provides the highest security available for programmable logic designs.

### Single Chip

Flash-based FPGAs store their configuration information in on-chip flash cells. Once programmed, the configuration data is an inherent part of the FPGA structure, and no external configuration data needs to be loaded at system power-up (unlike SRAM-based FPGAs). Therefore, flash-based SmartFusion cSoCs do not require system configuration components such as electrically erasable programmable read-only memories (EEPROMs) or microcontrollers to load device configuration data during power-up. This reduces bill-of-materials costs and PCB area, and increases system security and reliability.

#### Instant On

Flash-based SmartFusion cSoCs are Instant On. Instant On SmartFusion cSoCs greatly simplify total system design and reduce total system cost by eliminating the need for complex programmable logic devices (CPLDs). SmartFusion Instant On clocking (PLLs) replace off-chip clocking resources. In addition, glitches and brownouts in system power will not corrupt the SmartFusion flash configuration. Unlike SRAM-based FPGAs, the device will not have to be reloaded when system power is restored.

# **Thermal Characteristics**

### Introduction

The temperature variable in the SoC Products Group Designer software refers to the junction temperature, not the ambient, case, or board temperatures. This is an important distinction because dynamic and static power consumption will cause the chip's junction temperature to be higher than the ambient, case, or board temperatures. EQ 1 through EQ 3 give the relationship between thermal resistance, temperature gradient, and power.

$$\theta_{JA} = \frac{T_J - \theta_A}{P}$$

$\theta_{\text{JC}}$

EQ 1

$$\theta_{\mathsf{JB}} = \frac{\mathsf{T}_{\mathsf{J}} - \mathsf{T}_{\mathsf{B}}}{\mathsf{P}}$$

EQ 2

$$=\frac{I_{J}-I_{C}}{P}$$

EQ 3

where

- $\theta_{JA}$  = Junction-to-air thermal resistance

- $\theta_{JB}$  = Junction-to-board thermal resistance

- $\theta_{JC}$  = Junction-to-case thermal resistance

- T<sub>J</sub> = Junction temperature

- T<sub>A</sub> = Ambient temperature

- T<sub>B</sub> = Board temperature (measured 1.0 mm away from the package edge)

T<sub>C</sub> = Case temperature

P = Total power dissipated by the device

#### Table 2-6 • Package Thermal Resistance

|                   |           | $\theta_{JA}$ |         |     |               |       |

|-------------------|-----------|---------------|---------|-----|---------------|-------|

| Product           | Still Air | 1.0 m/s       | 2.5 m/s | θJC | $\theta_{JB}$ | Units |

| A2F200M3F-FG256   | 33.7      | 30.0          | 28.3    | 9.3 | 24.8          | °C/W  |

| A2F200M3F-FG484   | 21.8      | 18.2          | 16.7    | 7.7 | 16.8          | °C/W  |

| A2F200M3F-CS288   | 26.6      | 20.2          | 18.1    | 7.3 | 9.4           | °C/W  |

| A2F200M3F-PQG208I | 38.5      | 34.6          | 33.1    | 0.7 | 31.6          | °C/W  |

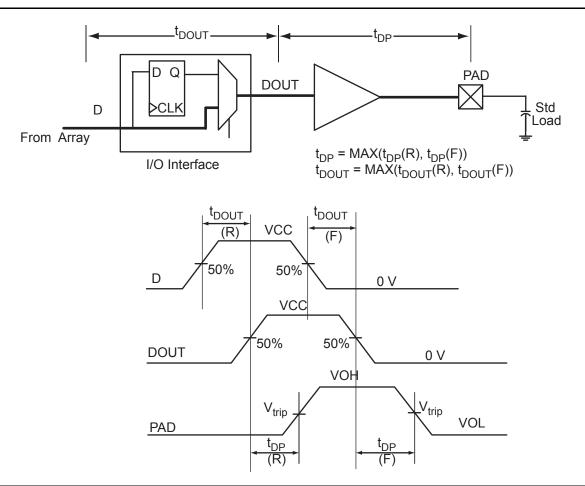

Figure 2-4 • Output Buffer Model and Delays (example)

# **Overview of I/O Performance**

# Summary of I/O DC Input and Output Levels – Default I/O Software Settings

#### Table 2-19 • Summary of Maximum and Minimum DC Input and Output Levels Applicable to Commercial Conditions—Software Default Settings Applicable to FPGA I/O Banks

|                               |                  |      |      | VIL                   | VIH                  | VIH       |                       | VOH                   | I <sub>OL</sub> <sup>1</sup> | I <sub>OH</sub> 1 |

|-------------------------------|------------------|------|------|-----------------------|----------------------|-----------|-----------------------|-----------------------|------------------------------|-------------------|

| I/O Standard                  | Drive<br>Strgth. |      |      | Max.<br>V             | Min.<br>V            | Max.<br>V | Max.<br>V             | Min.<br>V             | mA                           | mA                |

| 3.3 V LVTTL /<br>3.3 V LVCMOS | 12 mA            | High | -0.3 | 0.8                   | 2                    | 3.6       | 0.4                   | 2.4                   | 12                           | 12                |

| 2.5 V LVCMOS                  | 12 mA            | High | -0.3 | 0.7                   | 1.7                  | 3.6       | 0.7                   | 1.7                   | 12                           | 12                |

| 1.8 V LVCMOS                  | 12 mA            | High | -0.3 | 0.35 *<br>VCCxxxxIOBx | 0.65*<br>VCCxxxxIOBx | 3.6       | 0.45                  | VCCxxxxIOBx<br>- 0.45 | 12                           | 12                |

| 1.5 V LVCMOS                  | 12 mA            | High | -0.3 | 0.35 *<br>VCCxxxxIOBx | 0.65*<br>VCCxxxxIOBx | 3.6       | 0.25 *<br>VCCxxxxIOBx | 0.75*<br>VCCxxxxIOBx  | 12                           | 12                |

| 3.3 V PCI                     |                  | -    |      |                       | Per PCI spec         | cificatio | ons                   | -                     | -                            | -                 |

| 3.3 V PCI-X                   |                  |      |      |                       | Per PCI-X spe        | ecificat  | tions                 |                       |                              |                   |

Notes:

1. Currents are measured at 85°C junction temperature.

2. Output slew rate can be extracted by the IBIS Models.

# Table 2-20 • Summary of Maximum and Minimum DC Input and Output Levels Applicable to Commercial Conditions—Software Default Settings Applicable to MSS I/O Banks

|                               |                  |              |      |                      |                      | VIL       | VIH                  |                       | VOL | VOH | I <sub>OL</sub> <sup>1</sup> | I <sub>OH</sub> 1 |

|-------------------------------|------------------|--------------|------|----------------------|----------------------|-----------|----------------------|-----------------------|-----|-----|------------------------------|-------------------|

| I/O Standard                  | Drive<br>Strgth. | Slew<br>Rate |      | Max.<br>V            | Min.<br>V            | Max.<br>V | Max.<br>V            | Min.<br>V             | mA  | mA  |                              |                   |

| 3.3 V LVTTL /<br>3.3 V LVCMOS | 8 mA             | High         | -0.3 | 0.8                  | 2                    | 3.6       | 0.4                  | 2.4                   | 8   | 8   |                              |                   |

| 2.5 V LVCMOS                  | 8 mA             | High         | -0.3 | 0.7                  | 1.7                  | 3.6       | 0.7                  | 1.7                   | 8   | 8   |                              |                   |

| 1.8 V LVCMOS                  | 4 mA             | High         | -0.3 | 0.35*<br>VCCxxxxIOBx | 0.65*<br>VCCxxxxIOBx | 3.6       | 0.45                 | VCCxxxxIOBx<br>- 0.45 | 4   | 4   |                              |                   |

| 1.5 V LVCMOS                  | 2 mA             | High         | -0.3 | 0.35*<br>VCCxxxxIOBx | 0.65*<br>VCCxxxxIOBx | 3.6       | 0.25*<br>VCCxxxxIOBx | 0.75*<br>VCCxxxxIOBx  | 2   | 2   |                              |                   |

Notes:

1. Currents are measured at 85°C junction temperature.

2. Output slew rate can be extracted by the IBIS Models.

SmartFusion DC and Switching Characteristics

# **Differential I/O Characteristics**

### **Physical Implementation**

Configuration of the I/O modules as a differential pair is handled by SoC Products Group Designer software when the user instantiates a differential I/O macro in the design.

Differential I/Os can also be used in conjunction with the embedded Input Register (InReg), Output Register (OutReg), Enable Register (EnReg), and Double Data Rate (DDR). However, there is no support for bidirectional I/Os or tristates with the LVPECL standards.

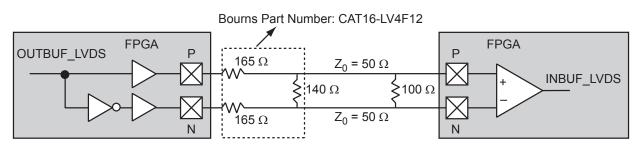

### LVDS

Low-Voltage Differential Signaling (ANSI/TIA/EIA-644) is a high-speed, differential I/O standard. It requires that one data bit be carried through two signal lines, so two pins are needed. It also requires external resistor termination.

The full implementation of the LVDS transmitter and receiver is shown in an example in Figure 2-11. The building blocks of the LVDS transmitter-receiver are one transmitter macro, one receiver macro, three board resistors at the transmitter end, and one resistor at the receiver end. The values for the three driver resistors are different from those used in the LVPECL implementation because the output standard specifications are different.

Along with LVDS I/O, SmartFusion cSoCs also support bus LVDS structure and multipoint LVDS (M-LVDS) configuration (up to 40 nodes).

Figure 2-11 • LVDS Circuit Diagram and Board-Level Implementation

# **Timing Characteristics**

|                    | mercial-Case Conditions   | ,<br>,          | 1    |      |       |

|--------------------|---------------------------|-----------------|------|------|-------|

| Combinatorial Cell | Equation                  | Parameter       | -1   | Std. | Units |

| INV                | Y = !A                    | t <sub>PD</sub> | 0.41 | 0.49 | ns    |

| AND2               | $Y = A \cdot B$           | t <sub>PD</sub> | 0.48 | 0.57 | ns    |

| NAND2              | Y = !(A · B)              | t <sub>PD</sub> | 0.48 | 0.57 | ns    |

| OR2                | Y = A + B                 | t <sub>PD</sub> | 0.49 | 0.59 | ns    |

| NOR2               | Y = !(A + B)              | t <sub>PD</sub> | 0.49 | 0.59 | ns    |

| XOR2               | Y = A ⊕ B                 | t <sub>PD</sub> | 0.75 | 0.90 | ns    |

| MAJ3               | Y = MAJ(A, B, C)          | t <sub>PD</sub> | 0.71 | 0.85 | ns    |

| XOR3               | $Y = A \oplus B \oplus C$ | t <sub>PD</sub> | 0.89 | 1.07 | ns    |

| MUX2               | Y = A !S + B S            | t <sub>PD</sub> | 0.51 | 0.62 | ns    |

| AND3               | $Y = A \cdot B \cdot C$   | t <sub>PD</sub> | 0.57 | 0.68 | ns    |

#### Table 2-78 • Combinatorial Cell Propagation Delays Worst Commercial-Case Conditions: T = 85°C. Worst-Case VCC = 1.425 V

Note: For specific junction temperature and voltage supply levels, refer to Table 2-7 on page 2-9 for derating values.

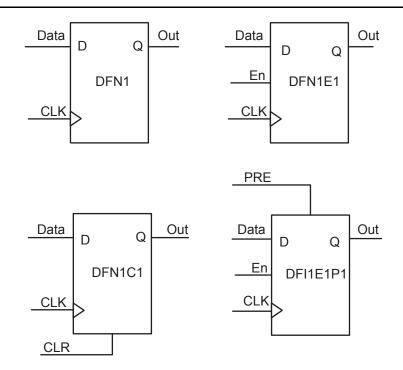

## VersaTile Specifications as a Sequential Module

The SmartFusion library offers a wide variety of sequential cells, including flip-flops and latches. Each has a data input and optional enable, clear, or preset. In this section, timing characteristics are presented for a representative sample from the library. For more details, refer to the *IGLOO/e, Fusion, ProASIC3/E, and SmartFusion Macro Library Guide*.

Figure 2-25 • Sample of Sequential Cells

# **Programmable Analog Specifications**

# **Current Monitor**

Unless otherwise noted, current monitor performance is specified at 25°C with nominal power supply voltages, with the output measured using the internal voltage reference with the internal ADC in 12-bit mode and 91 Ksps, after digital compensation. All results are based on averaging over 16 samples.

Table 2-93 • Current Monitor Performance Specification

| Specification                                                  | Test Conditions                                                                              | Min.   | Typical           | Max.             | Units                   |

|----------------------------------------------------------------|----------------------------------------------------------------------------------------------|--------|-------------------|------------------|-------------------------|

| Input voltage range (for driving ADC over full range)          |                                                                                              | 0 – 48 | 0 – 50            | 1 – 51           | mV                      |

| Analog gain                                                    | From the differential voltage across the input pads to the ADC input                         |        | 50                |                  | V/V                     |

| Input referred offset voltage                                  | Input referred offset voltage                                                                | 0      | 0.1               | 0.5              | mV                      |

|                                                                | -40°C to +100°C                                                                              | 0      | 0.1               | 0.5              | mV                      |

| Gain error                                                     | Slope of BFSL vs. 50 V/V                                                                     |        | ±0.1              | ±0.5             | % nom.                  |

|                                                                | -40°C to +100°C                                                                              |        |                   | ±0.5             | % nom.                  |

| Overall Accuracy                                               | Peak error from ideal transfer function, 25°C                                                |        | ±(0.1 +<br>0.25%) | ±(0.4 +<br>1.5%) | mV plus<br>%<br>reading |

| Input referred noise                                           | 0 VDC input (no output averaging)                                                            | 0.3    | 0.4               | 0.5              | mVrms                   |

| Common-mode rejection ratio                                    | 0 V to 12 VDC common-mode voltage                                                            | -86    | -87               |                  | dB                      |

| Analog settling time                                           | To 0.1% of final value (with ADC load)                                                       |        |                   |                  |                         |

|                                                                | From CM_STB (High)                                                                           | 5      |                   |                  | μs                      |

|                                                                | From ADC_START (High)                                                                        | 5      |                   | 200              | μs                      |

| Input capacitance                                              |                                                                                              |        | 8                 |                  | pF                      |

| Input biased current                                           | CM[n] or TM[n] pad,<br>40°C to +100°C over maximum input<br>voltage range (plus is into pad) |        |                   |                  |                         |

|                                                                | Strobe = 0; IBIAS on CM[n]                                                                   |        | 0                 |                  | μA                      |

|                                                                | Strobe = 1; IBIAS on CM[n]                                                                   |        | 1                 |                  | μA                      |

|                                                                | Strobe = 0; IBIAS on TM[n]                                                                   |        | 2                 |                  | μA                      |

|                                                                | Strobe = 1; IBIAS on TM[n]                                                                   |        | 1                 |                  | μA                      |

| Power supply rejection ratio                                   | DC (0 – 10 KHz)                                                                              | 41     | 42                |                  | dB                      |

|                                                                | VCC33A                                                                                       |        | 150               |                  | μA                      |

| monitor power supply current requirements (per current monitor | VCC33AP                                                                                      |        | 140               |                  | μA                      |

| instance, not including ADC or VAREFx)                         | VCC15A                                                                                       |        | 50                |                  | μA                      |

Note: Under no condition should the TM pad ever be greater than 10 mV above the CM pad. This restriction is applicable only if current monitor is used.

# 4 – SmartFusion Programming

SmartFusion cSoCs have three separate flash areas that can be programmed:

- 1. The FPGA fabric

- 2. The embedded nonvolatile memories (eNVMs)

- 3. The embedded flash ROM (eFROM)

There are essentially three methodologies for programming these areas:

- 1. In-system programming (ISP)

- 2. In-application programming (IAP)

- a. A2F060 and A2F500: The FPGA fabric, eNVM, and eFROM

- b. A2F200: Only the FPGA fabric and the eNVM

- 3. Pre-programming (non-ISP)

Programming, whether ISP or IAP methodologies are employed, can be done in two ways:

- 1. Securely using the on chip AES decryption logic

- 2. In plain text

# **In-System Programming**

In-System Programming is performed with the aid of external JTAG programming hardware. Table 4-1 describes the JTAG programming hardware that will program a SmartFusion cSoC and Table 4-2 defines the JTAG pins that provide the interface for the programming hardware.

#### Table 4-1 • Supported JTAG Programming Hardware

| Dongle      | Source             | JTAG | SWD <sup>1</sup> | SWV <sup>2</sup> | Program<br>FPGA  | Program<br>eFROM | Program<br>eNVM |

|-------------|--------------------|------|------------------|------------------|------------------|------------------|-----------------|

| FlashPro3/4 | SoC Products Group | Yes  | No               | No               | Yes              | Yes              | Yes             |

| ULINK Pro   | Keil               | Yes  | Yes              | Yes              | Yes <sup>3</sup> | Yes <sup>3</sup> | Yes             |

| ULINK2      | Keil               | Yes  | Yes              | Yes              | Yes <sup>3</sup> | Yes <sup>3</sup> | Yes             |

| IAR J-Link  | IAR                | Yes  | Yes              | Yes              | Yes <sup>3</sup> | Yes <sup>3</sup> | Yes             |

Notes:

- 1. SWD = ARM Serial Wire Debug

- 2. SWV = ARM Serial Wire Viewer

- 3. Planned support

#### Table 4-2 • JTAG Pin Descriptions

| Pin Name | Description                                                       |

|----------|-------------------------------------------------------------------|

| JTAGSEL  | ARM Cortex-M3 or FPGA test access port (TAP) controller selection |

| TRSTB    | Test reset bar                                                    |

| тск      | Test clock                                                        |

| TMS      | Test mode select                                                  |

| TDI      | Test data input                                                   |

| TDO      | Test data output                                                  |

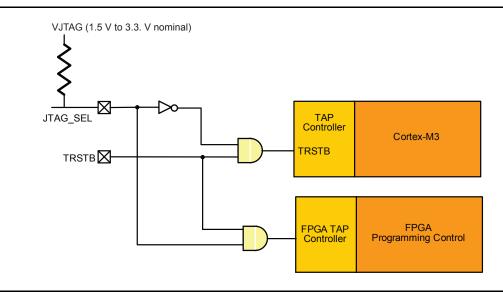

The JTAGSEL pin selects the FPGA TAP controller or the Cortex-M3 debug logic. When JTAGSEL is asserted, the FPGA TAP controller is selected and the TRSTB input into the Cortex-M3 is held in a reset state (logic 0), as depicted in Figure 4-1. Users should tie the JTAGSEL pin high externally.

Microsemi's free Eclipse-based IDE, SoftConsole, has the ability to control the JTAGSEL pin directly with the FlashPro4 programmer. Manual jumpers are provided on the evaluation and development kits to allow manual selection of this function for the J-Link and ULINK debuggers.

Note: Standard ARM JTAG connectors do not have access to the JTAGSEL pin. SoftConsole automatically selects the appropriate TAP controller using the CTXSELECT JTAG command. When using SoftConsole, the state of JTAGSEL is a "don't care."

Figure 4-1 • TRSTB Logic

# **In-Application Programming**

In-application programming refers to the ability to reprogram the various flash areas under direct supervision of the Cortex-M3.

### **Reprogramming the FPGA Fabric Using the Cortex-M3**

In this mode, the Cortex-M3 is executing the programming algorithm on-chip. The IAP driver can be incorporated into the design project and executed from eNVM or eSRAM. The SoC Products Group provides working example projects for SoftConsole, IAR, and Keil development environments. These can be downloaded via the SoC Products Group Firmware Catalog. The new bitstream to be programmed into the FPGA can reside on the user's printed circuit board (PCB) in a separate SPI flash memory. Alternately, the user can modify the existing projects supplied by the SoC Products Group and, via custom handshaking software, throttle the download of the new image and program the FPGA a piece at a time in real time. A cost-effective and reliable approach would be to store the bitstream in an external SPI flash. Another option is storing a redundant bitstream image in an external SPI flash and loading the newest version into the FPGA only when receiving an IAP command. Since the FPGA I/Os are tristated or held at predefined or last known state during FPGA programming, the user must use MSS I/Os to interface to external memories. Since there are two SPI controllers in the MSS, the user can dedicate one to an SPI flash and the other to the particulars of an application. The amount of flash memory required to program the FPGA always exceeds the size of the eNVM block that is on-chip. The external memory controller (EMC) cannot be used as an interface to a memory device for storage of a bitstream because its I/O pads are FPGA I/Os; hence they are tristated when the FPGA is in a programming state.

The MSS resets itself after IAP of the FPGA fabric. This reset is internally asserted on MSS\_RESETN by the power supply monitor (PSM) and reset controller of the MSS.

Pin Descriptions

# **Special Function Pins**

| Name     | Туре | Polarity/Bus Size | Description                                                                                                                                                                                                                                                                                                          |

|----------|------|-------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| NC       |      |                   | No connect                                                                                                                                                                                                                                                                                                           |

|          |      |                   | This pin is not connected to circuitry within the device. These pins can<br>be driven to any voltage or can be left floating with no effect on the<br>operation of the device.                                                                                                                                       |

| DC       |      |                   | Do not connect.                                                                                                                                                                                                                                                                                                      |

|          |      |                   | This pin should not be connected to any signals on the PCB. These pins should be left unconnected.                                                                                                                                                                                                                   |

| LPXIN    | In   | 1                 | Low power 32 KHz crystal oscillator.                                                                                                                                                                                                                                                                                 |

|          |      |                   | Input from the 32 KHz oscillator. Pin for connecting a low power 32 KHz watch crystal. If not used, the LPXIN pin can be left floating. For more information, see the PLLs, Clock Conditioning Circuitry, and On-Chip Crystal Oscillators section in the <i>SmartFusion Microcontroller Subsystem User's Guide</i> . |

| LPXOUT   | In   | 1                 | Low power 32 KHz crystal oscillator.                                                                                                                                                                                                                                                                                 |

|          |      |                   | Output to the 32 KHz oscillator. Pin for connecting a low power 32 KHz watch crystal. If not used, the LPXOUT pin can be left floating. For more information, see the PLLs, Clock Conditioning Circuitry, and On-Chip Crystal Oscillators section in the <i>SmartFusion Microcontroller Subsystem User's Guide</i> . |

| MAINXIN  | In   | 1                 | Main crystal oscillator circuit.                                                                                                                                                                                                                                                                                     |

|          |      |                   | Input to the crystal oscillator circuit. Pin for connecting an external crystal, ceramic resonator, or RC network. When using an external crystal or ceramic oscillator, external capacitors are also recommended. Refer to documentation from the crystal oscillator manufacturer for proper capacitor value.       |

|          |      |                   | If an external RC network or clock input is used, the RC components are connected to the MAINXIN pin, with MAINXOUT left floating. When the main crystal oscillator is not being used, MAINXIN and MAINXOUT pins can be left floating.                                                                               |

|          |      |                   | For more information, see the PLLs, Clock Conditioning Circuitry, and On-Chip Crystal Oscillators section in the <i>SmartFusion Microcontroller Subsystem User's Guide</i> .                                                                                                                                         |

| MAINXOUT | Out  | 1                 | Main crystal oscillator circuit.                                                                                                                                                                                                                                                                                     |

|          |      |                   | Output from the crystal oscillator circuit. Pin for connecting external crystal or ceramic resonator. When using an external crystal or ceramic oscillator, external capacitors are also recommended. Refer to documentation from the crystal oscillator manufacturer for proper capacitor value.                    |

|          |      |                   | If an external RC network or clock input is used, the RC components are connected to the MAINXIN pin, with MAINXOUT left floating. When the main crystal oscillator is not being used, MAINXIN and MAINXOUT pins can be left floating.                                                                               |

|          |      |                   | For more information, see the PLLs, Clock Conditioning Circuitry, and On-Chip Crystal Oscillators section in the <i>SmartFusion Microcontroller Subsystem User's Guide</i> .                                                                                                                                         |

🌜 Microsemi.

| Name        | Туре | Polarity/Bus Size | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

|-------------|------|-------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| NCAP        |      | 1                 | Negative capacitor connection.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

|             |      |                   | This is the negative terminal of the charge pump. A capacitor, with a 2.2 $\mu$ F recommended value, is required to connect between PCAP and NCAP. Analog charge pump capacitors are not needed if none of the analog SCB features are used and none of the SDDs are used. In that case it should be left unconnected.                                                                                                                                                                                                                                                                                                       |

| PCAP        |      | 1                 | Positive Capacitor connection.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

|             |      |                   | This is the positive terminal of the charge pump. A capacitor, with a 2.2 $\mu$ F recommended value, is required to connect between PCAP and NCAP. If this pin is not used, it must be left unconnected/floating. In this case, no capacitor is needed. Analog charge pump capacitors are not needed if none of the analog SCB features are used, and none of the SDDs are used.                                                                                                                                                                                                                                             |

| PTBASE      |      | 1                 | Pass transistor base connection                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

|             |      |                   | This is the control signal of the voltage regulator. This pin should be connected to the base of an external pass transistor used with the 1.5 V internal voltage regulator and can be floating if not used.                                                                                                                                                                                                                                                                                                                                                                                                                 |

| PTEM        |      | 1                 | Pass transistor emitter connection.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

|             |      |                   | This is the feedback input of the voltage regulator.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

|             |      |                   | This pin should be connected to the emitter of an external pass transistor used with the 1.5 V internal voltage regulator and can be floating if not used.                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

| MSS_RESET_N |      | Low               | Low Reset signal which can be used as an external reset and can also<br>be used as a system level reset under control of the Cortex-M3<br>processor. MSS_RESET_N is an output asserted low after power-on<br>reset. The direction of MSS_RESET_N changes during the execution<br>of the Microsemi System Boot when chip-level reset is enabled. The<br>Microsemi System Boot reconfigures MSS_RESET_N to become a<br>reset input signal when chip-level reset is enabled. It has an internal<br>pull-up so it can be left floating. In the current software, the<br>MSS_RESET_N is modeled as an external input signal only. |

| PU_N        | In   | Low               | Push-button is the connection for the external momentary switch used to turn on the 1.5 V voltage regulator and can be floating if not used.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

# **Microsemi**.

| Name             | Туре       | Polarity/<br>Bus Size | Description                                                                                                                                   |

|------------------|------------|-----------------------|-----------------------------------------------------------------------------------------------------------------------------------------------|

| SPI_1_DO         | Out        | 1                     | Data output. Second SPI.                                                                                                                      |

|                  |            |                       | Can also be used as an MSS GPIO (see "GPIO_x" on page 5-6).                                                                                   |

| SPI_1_SS         | Out        | 1                     | Slave select (chip select). Second SPI.                                                                                                       |

|                  |            |                       | Can also be used as an MSS GPIO (see "GPIO_x" on page 5-6).                                                                                   |

| Universal Asynch | hronous Re | eceiver/Trans         | mitter (UART) Peripherals                                                                                                                     |

| UART_0_RXD       | In         | 1                     | Receive data. First UART.                                                                                                                     |

|                  |            |                       | Can also be used as an MSS GPIO (see "GPIO_x" on page 5-6).                                                                                   |

| UART_0_TXD       | Out        | 1                     | Transmit data. First UART.                                                                                                                    |

|                  |            |                       | Can also be used as an MSS GPIO (see "GPIO_x" on page 5-6).                                                                                   |

| UART_1_RXD       | In         | 1                     | Receive data. Second UART.                                                                                                                    |

|                  |            |                       | Can also be used as an MSS GPIO (see "GPIO_x" on page 5-6).                                                                                   |

| UART_1_TXD       | Out        | 1                     | Transmit data. Second UART.                                                                                                                   |

|                  |            |                       | Can also be used as an MSS GPIO (see "GPIO_x" on page 5-6).                                                                                   |

| Ethernet MAC     |            |                       |                                                                                                                                               |

| MAC_CLK          | In         | Rise                  | Receive clock. 50 MHz $\pm$ 50 ppm clock source received from RMII PHY.                                                                       |

|                  |            |                       | Can be left floating when unused.                                                                                                             |

| MAC_CRSDV        | In         | High                  | Carrier sense/receive data valid for RMII PHY                                                                                                 |

|                  |            |                       | Can also be used as an FPGA User IO (see "IO" on page 5-6).                                                                                   |

| MAC_MDC          | Out        | Rise                  | RMII management clock                                                                                                                         |

|                  |            |                       | Can also be used as an FPGA User IO (see "IO" on page 5-6).                                                                                   |

| MAC_MDIO         | In/Out     | 1                     | RMII management data input/output                                                                                                             |

|                  |            |                       | Can also be used as an FPGA User IO (see "IO" on page 5-6).                                                                                   |

| MAC_RXDx         | In         | 2                     | Ethernet MAC receive data. Data recovered and decoded by PHY. The RXD[0] signal is the least significant bit.                                 |

|                  |            |                       | Can also be used as an FPGA User I/O (see "IO" on page 5-6).                                                                                  |

| MAC_RXER         | In         | HIGH                  | Ethernet MAC receive error. If MACRX_ER is asserted during reception, the frame is received and status of the frame is updated with MACRX_ER. |

|                  |            |                       | Can also be used as an FPGA user I/O (see "IO" on page 5-6).                                                                                  |

| MAC_TXDx         | Out        | 2                     | Ethernet MAC transmit data. The TXD[0] signal is the least significant bit.                                                                   |

|                  |            |                       | Can also be used as an FPGA user I/O (see "IO" on page 5-6).                                                                                  |

| MAC_TXEN         | Out        | HIGH                  | Ethernet MAC transmit enable. When asserted, indicates valid data for the PHY on the TXD port.                                                |

|                  |            |                       | Can also be used as an FPGA User I/O (see "IO" on page 5-6).                                                                                  |

|      |      |                                                                                                                            | Associated With |      |  |

|------|------|----------------------------------------------------------------------------------------------------------------------------|-----------------|------|--|

| Name | Туре | Description                                                                                                                | ADC/SDD         | SCB  |  |

| TM0  | In   | SCB 0 / low side of current monitor / comparator                                                                           | ADC0            | SCB0 |  |

|      |      | Negative input / high side of temperature monitor. See the Temperature Monitor section.                                    |                 |      |  |

| TM1  | In   | SCB 1 / low side of current monitor / comparator. Negative input / high side of temperature monitor.                       | ADC0            | SCB1 |  |

| TM2  | In   | SCB 2 / low side of current monitor / comparator. Negative input / high side of temperature monitor.                       | ADC1            | SCB2 |  |

| TM3  | In   | SCB 3 low side of current monitor / comparator. Negative input / high side of temperature monitor.                         | ADC1            | SCB3 |  |

| TM4  | In   | SCB 4 low side of current monitor / comparator. Negative input / high side of temperature monitor.                         | ADC2            | SCB4 |  |

| SDD0 | Out  | Output of SDD0                                                                                                             | SDD0            | N/A  |  |

|      |      | See the Sigma-Delta Digital-to-Analog Converter (DAC) section in the <i>SmartFusion Programmable Analog User's Guide</i> . |                 |      |  |

| SDD1 | Out  | Output of SDD1                                                                                                             | SDD1            | N/A  |  |

| SDD2 | Out  | Output of SDD2                                                                                                             | SDD2            | N/A  |  |

Note: Unused analog inputs should be grounded. This aids in shielding and prevents an undesired coupling path.

|                            | TQ144             |  |

|----------------------------|-------------------|--|

| Pin Number A2F060 Function |                   |  |

| 1                          | VCCPLL0           |  |

| 2                          | VCOMPLA0          |  |

| 3                          | GNDQ              |  |

| 4                          | GFA2/IO42PDB5V0   |  |

| 5                          | GFB2/IO42NDB5V0   |  |

| 6                          | GFC2/IO41PDB5V0   |  |

| 7                          | IO41NDB5V0        |  |

| 8                          | VCC               |  |

| 9                          | GND               |  |

| 10                         | VCCFPGAIOB5       |  |

| 11                         | IO38PDB5V0        |  |

| 12                         | IO38NDB5V0        |  |

| 13                         | IO36PDB5V0        |  |

| 14                         | IO36NDB5V0        |  |

| 15                         | GND               |  |

| 16                         | GNDRCOSC          |  |

| 17                         | VCCRCOSC          |  |

| 18                         | MSS_RESET_N       |  |

| 19                         | GPIO_0/IO33RSB4V0 |  |

| 20                         | GPIO_1/IO32RSB4V0 |  |

| 21                         | GPIO_2/IO31RSB4V0 |  |

| 22                         | GPIO_3/IO30RSB4V0 |  |

| 23                         | GPIO_4/IO29RSB4V0 |  |

| 24                         | GND               |  |

| 25                         | VCCMSSIOB4        |  |

| 26                         | VCC               |  |

| 27                         | GPIO_5/IO28RSB4V0 |  |

| 28                         | GPIO_6/IO27RSB4V0 |  |

| 29                         | GPIO_7/IO26RSB4V0 |  |

| 30                         | GPIO_8/IO25RSB4V0 |  |

| 31                         | VCCESRAM          |  |

| 32                         | GNDSDD0           |  |

| 33                         | VCC33SDD0         |  |

| 34                         | VCC15A            |  |

| 35                         | PCAP              |  |

| 36                         | NCAP              |  |

SmartFusion Customizable System-on-Chip (cSoC)

| Pin | CS288              |                       |                       |  |

|-----|--------------------|-----------------------|-----------------------|--|

| No. | A2F060 Function    | A2F200 Function       | A2F500 Function       |  |

| P19 | VCCMSSIOB2         | VCCMSSIOB2            | VCCMSSIOB2            |  |

| P21 | GND                | GND                   | GND                   |  |

| R1  | GPIO_2/IO31RSB4V0  | MAC_MDIO/IO49RSB4V0   | MAC_MDIO/IO58RSB4V0   |  |

| R3  | GPIO_1/IO32RSB4V0  | MAC_TXEN/IO52RSB4V0   | MAC_TXEN/IO61RSB4V0   |  |

| R5  | GPIO_3/IO30RSB4V0  | MAC_TXD[0]/IO56RSB4V0 | MAC_TXD[0]/IO65RSB4V0 |  |

| R6  | GPIO_10/IO35RSB4V0 | MAC_CRSDV/IO51RSB4V0  | MAC_CRSDV/IO60RSB4V0  |  |

| R9  | GNDA               | GNDA                  | GNDA                  |  |

| R13 | GNDA               | GNDA                  | GNDA                  |  |

| R16 | UART_1_RXD/GPIO_29 | UART_1_RXD/GPIO_29    | UART_1_RXD/GPIO_29    |  |

| R17 | UART_1_TXD/GPIO_28 | UART_1_TXD/GPIO_28    | UART_1_TXD/GPIO_28    |  |

| R19 | I2C_0_SDA/GPIO_22  | I2C_0_SDA/GPIO_22     | I2C_0_SDA/GPIO_22     |  |

| R21 | I2C_1_SDA/GPIO_30  | I2C_1_SDA/GPIO_30     | I2C_1_SDA/GPIO_30     |  |

| T1  | GND                | GND                   | GND                   |  |

| Т3  | NC                 | MAC_TXD[1]/IO55RSB4V0 | MAC_TXD[1]/IO64RSB4V0 |  |

| T5  | NC                 | MAC_RXD[1]/IO53RSB4V0 | MAC_RXD[1]/IO62RSB4V0 |  |

| Т6  | GPIO_11/IO34RSB4V0 | MAC_RXER/IO50RSB4V0   | MAC_RXER/IO59RSB4V0   |  |

| T7  | NC                 | CM1                   | CM1                   |  |

| Т8  | NC                 | ADC1                  | ADC1                  |  |

| Т9  | NC                 | GND33ADC0             | GND33ADC0             |  |

| T10 | NC                 | VCC15ADC0             | VCC15ADC0             |  |

| T11 | GND33ADC0          | GND33ADC1             | GND33ADC1             |  |

| T12 | VAREF0             | VAREF1                | VAREF1                |  |

| T13 | ADC7               | ADC4                  | ADC4                  |  |

| T14 | TM0                | TM3                   | TM3                   |  |

| T15 | SPI_1_SS/GPIO_27   | SPI_1_SS/GPIO_27      | SPI_1_SS/GPIO_27      |  |

| T16 | VCCMSSIOB2         | VCCMSSIOB2            | VCCMSSIOB2            |  |

| T17 | UART_0_RXD/GPIO_21 | UART_0_RXD/GPIO_21    | UART_0_RXD/GPIO_21    |  |

| T19 | UART_0_TXD/GPIO_20 | UART_0_TXD/GPIO_20    | UART_0_TXD/GPIO_20    |  |

| T21 | I2C_1_SCL/GPIO_31  | I2C_1_SCL/GPIO_31     | I2C_1_SCL/GPIO_31     |  |

| U1  | NC                 | MAC_RXD[0]/IO54RSB4V0 | MAC_RXD[0]/IO63RSB4V0 |  |

| U3  | VCCMSSIOB4         | VCCMSSIOB4            | VCCMSSIOB4            |  |

Notes:

1. Shading denotes pins that do not have completely identical functions from density to density. For example, the bank assignment can be different for an I/O, or the function might be available only on a larger density device.

2. \*: Indicates that the signal assigned to the pins as a CLKBUF/CLKBUF\_LVPECL/CLKBUF\_LVDS goes through a glitchless mux. In order for the glitchless mux to operate correctly, the signal must be a free-running clock signal. Refer to the 'Glitchless MUX' section in the SmartFusion Microcontroller Subsystem User's Guide for more details.

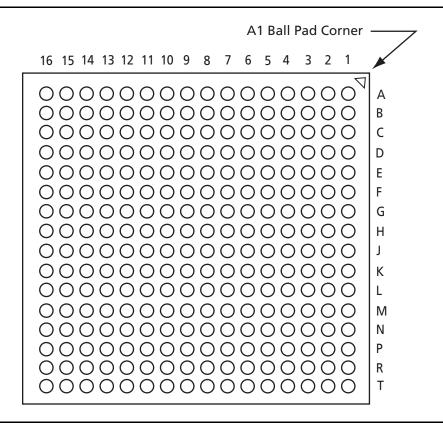

# FG256

### Note

For Package Manufacturing and Environmental information, visit the Resource Center at http://www.microsemi.com/soc/products/solutions/package/docs.aspx.

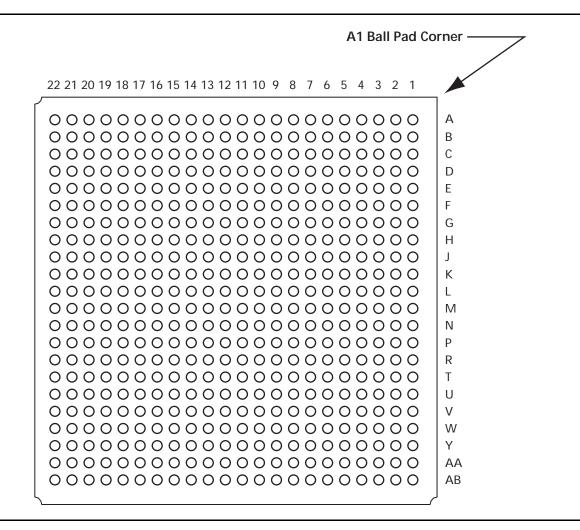

# FG484

#### Note

For Package Manufacturing and Environmental information, visit the Resource Center at http://www.microsemi.com/soc/products/solutions/package/docs.aspx.

🌜 Microsemi.

SmartFusion Customizable System-on-Chip (cSoC)

|            | FG484                        |                              |  |  |

|------------|------------------------------|------------------------------|--|--|

| Pin Number | A2F200 Function              | A2F500 Function              |  |  |

| В3         | NC                           | NC                           |  |  |

| B4         | NC                           | NC                           |  |  |

| B5         | VCCFPGAIOB0                  | VCCFPGAIOB0                  |  |  |

| B6         | EMC_RW_N/GAA1/IO00PDB0V0     | EMC_RW_N/GAA1/IO02PDB0V0     |  |  |

| B7         | NC                           | IO04PPB0V0                   |  |  |

| B8         | VCCFPGAIOB0                  | VCCFPGAIOB0                  |  |  |

| B9         | EMC_BYTEN[0]/GAC0/IO02NDB0V0 | EMC_BYTEN[0]/GAC0/IO07NDB0V0 |  |  |

| B10        | EMC_AB[2]/IO05NDB0V0         | EMC_AB[2]/IO09NDB0V0         |  |  |

| B11        | EMC_AB[3]/IO05PDB0V0         | EMC_AB[3]/IO09PDB0V0         |  |  |

| B12        | EMC_AB[6]/IO07NDB0V0         | EMC_AB[6]/IO12NDB0V0         |  |  |

| B13        | EMC_AB[14]/IO11NDB0V0        | EMC_AB[14]/IO15NDB0V0        |  |  |

| B14        | EMC_AB[15]/IO11PDB0V0        | EMC_AB[15]/IO15PDB0V0        |  |  |

| B15        | VCCFPGAIOB0                  | VCCFPGAIOB0                  |  |  |

| B16        | EMC_AB[18]/IO13NDB0V0        | EMC_AB[18]/IO18NDB0V0        |  |  |

| B17        | EMC_AB[19]/IO13PDB0V0        | EMC_AB[19]/IO18PDB0V0        |  |  |

| B18        | VCCFPGAIOB0                  | VCCFPGAIOB0                  |  |  |

| B19        | GBB0/IO18NDB0V0              | GBB0/IO24NDB0V0              |  |  |

| B20        | GBB1/IO18PDB0V0              | GBB1/IO24PDB0V0              |  |  |

| B21        | GND                          | GND                          |  |  |

| B22        | GBA2/IO20PDB1V0              | GBA2/IO27PDB1V0              |  |  |

| C1         | EMC_DB[14]/GAB2/IO71NDB5V0   | EMC_DB[14]/GAB2/IO88NDB5V0   |  |  |

| C2         | NC                           | NC                           |  |  |

| C3         | NC                           | NC                           |  |  |

| C4         | NC                           | IO01NDB0V0                   |  |  |

| C5         | NC                           | IO01PDB0V0                   |  |  |

| C6         | EMC_CLK/GAA0/IO00NDB0V0      | EMC_CLK/GAA0/IO02NDB0V0      |  |  |

| C7         | NC                           | IO03PPB0V0                   |  |  |

| C8         | NC                           | IO04NPB0V0                   |  |  |

| C9         | EMC_BYTEN[1]/GAC1/IO02PDB0V0 | EMC_BYTEN[1]/GAC1/IO07PDB0V0 |  |  |

| C10        | EMC_OEN1_N/IO03PDB0V0        | EMC_OEN1_N/IO08PDB0V0        |  |  |

| C11        | GND                          | GND                          |  |  |

| C12        | VCCFPGAIOB0                  | VCCFPGAIOB0                  |  |  |

| C13        | EMC_AB[8]/IO08NDB0V0         | EMC_AB[8]/IO13NDB0V0         |  |  |

| C14        | EMC_AB[16]/IO12NDB0V0        | EMC_AB[16]/IO17NDB0V0        |  |  |

Notes:

1. Shading denotes pins that do not have completely identical functions from density to density. For example, the bank assignment can be different for an I/O, or the function might be available only on a larger density device.

2. \*: Indicates that the signal assigned to the pins as a CLKBUF/CLKBUF\_LVPECL/CLKBUF\_LVDS goes through a glitchless mux. In order for the glitchless mux to operate correctly, the signal must be a free-running clock signal. Refer to the 'Glitchless MUX' section in the SmartFusion Microcontroller Subsystem User's Guide for more details.

🌜 Microsemi.

| Revision                    | Changes                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | Page         |

|-----------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------|

| Revision 8<br>(continued)   | The description of "In-application programming (IAP)" methodology was changed to state the difference for A2F060 and A2F500 compared to A2F200 (SAR 37808).                                                                                                                                                                                                                                                                                                                                 | 4-7          |

|                             | The "Global I/O Naming Conventions" section is new (SARs 28996, 31147). The description for IO "User Pins" was revised accordingly and moved out of the table and into a new section: "User I/O Naming Conventions".                                                                                                                                                                                                                                                                        | 5-6, 5-6     |

|                             | The descriptions for "MAINXIN" and "MAINXOUT" were revised to state how they should be handled if using an external RC network or clock input (SAR 32594).                                                                                                                                                                                                                                                                                                                                  | 5-8          |

|                             | The description and type was revised for the "MSS_RESET_N" pin (SAR 34133).                                                                                                                                                                                                                                                                                                                                                                                                                 | 5-9          |

|                             | The "TQ144" section and pin table for A2F060 are new (SAR 36246).                                                                                                                                                                                                                                                                                                                                                                                                                           | 5-18         |

| Revision 7<br>(August 2011) | The title of the datasheet was changed from SmartFusion Intelligent Mixed Signal FPGAs to SmartFusion Customizable System-on-Chip (cSoC). Terminology throughout was changed accordingly. The term cSoC defines a category of devices that include at least FPGA fabric and a processor subsystem of some sort. It can also include any of the following: analog, SerDes, ASIC blocks, customer specific IP, or application-specific IP. SmartFusion is Microsemi's first cSoC (SAR 33071). | N/A          |

|                             | The "SmartFusion cSoC Family Product Table" was revised to remove the note stating that the A2F060 device is under definition and subject to change (SAR 33070). A note was added for EMC, stating that it is not available on A2F500 for the PQ208 package (SAR 33041).                                                                                                                                                                                                                    | II           |

|                             | The "SmartFusion cSoC Device Status" table was revised. The status for A2F060 CS288 and FG256 moved from Advance to Preliminary. A2F200 PQ208 and A2F500 PQ208 moved from Advance to Production (SAR 33069).                                                                                                                                                                                                                                                                                | Ш            |

|                             | The "Package I/Os: MSS + FPGA I/Os" table was revised. The number of direct analog inputs for A2F060 packages increased from 6 to 11. The number of MSS I/Os for the A2F060 FG256 package increased from 25 to 26 (SAR 33070). A note was added stating that EMC is not available for the A2F500 PQ208 package (SAR 33041).                                                                                                                                                                 | III          |

|                             | The note associated with the "SmartFusion cSoC System Architecture" diagram was corrected from "Architecture for A2F500" to "Architecture for A2F200" (SAR 32578).                                                                                                                                                                                                                                                                                                                          | V            |

|                             | The Licensed DPA Logo was added to the "Product Ordering Codes" section. The trademarked Licensed DPA Logo identifies that a product is covered by a DPA counter-measures license from Cryptography Research (SAR 32151).                                                                                                                                                                                                                                                                   | VI           |

|                             | The "Security" section and "Secure Programming" section were updated to clarify that although no existing security measures can give an absolute guarantee, SmartFusion cSoCs implement the best security available in the industry (SAR 32865).                                                                                                                                                                                                                                            | 1-2, 4-9     |

|                             | Storage temperature, $T_{STG}$ , and junction temperature, $T_J$ , were added to Table 2-1 • Absolute Maximum Ratings (SAR 30863).                                                                                                                                                                                                                                                                                                                                                          | 2-1          |

|                             | AC/DC characteristics for A2F060 were added to the "SmartFusion DC and Switching Characteristics" chapter (SAR 33132). The following tables were updated:                                                                                                                                                                                                                                                                                                                                   |              |

|                             | Table 2-14 • Different Components Contributing to Dynamic Power Consumption inSmartFusion cSoCs                                                                                                                                                                                                                                                                                                                                                                                             | 2-12         |

|                             | Table 2-15 • Different Components Contributing to the Static Power Consumption inSmartFusion cSoCs                                                                                                                                                                                                                                                                                                                                                                                          | 2-13         |

|                             | Table 2-90 • eNVM Block Timing, Worst Commercial Case Conditions: T_J = 85°C, VCC = 1.425 V                                                                                                                                                                                                                                                                                                                                                                                                 | 2-76         |

|                             | Table 2-98 • Analog Sigma-Delta DAC                                                                                                                                                                                                                                                                                                                                                                                                                                                         | 2-85<br>2-89 |

|                             | Table 2-100 • SPI Characteristics                                                                                                                                                                                                                                                                                                                                                                                                                                                           |              |

Microsemi Corporate Headquarters One Enterprise, Aliso Viejo, CA 92656 USA

Within the USA: +1 (800) 713-4113 Outside the USA: +1 (949) 380-6100 Sales: +1 (949) 380-6136 Fax: +1 (949) 215-4996

#### E-mail: sales.support@microsemi.com

© 2015 Microsemi Corporation. All rights reserved. Microsemi and the Microsemi logo are trademarks of Microsemi Corporation. All other trademarks and service marks are the property of their respective owners.

Microsemi Corporation (Nasdaq: MSCC) offers a comprehensive portfolio of semiconductor and system solutions for communications, defense & security, aerospace and industrial markets. Products include high-performance and radiation-hardened analog mixed-signal integrated circuits, FPGAs, SoCs and ASICs; power management products; timing and synchronization devices and precise time solutions, setting the world's standard for time; voice processing devices; RF solutions; discrete components; security technologies and scalable anti-tamper products; Power-over-Ethernet ICs and midspans; as well as custom design capabilities and services. Microsemi is headquartered in Aliso Viejo, Calif., and has approximately 3,400 employees globally. Learn more at **www.microsemi.com**.

Microsemi makes no warranty, representation, or guarantee regarding the information contained herein or the suitability of its products and services for any particular purpose, nor does Microsemi assume any liability whatsoever arising out of the application or use of any product or circuit. The products sold hereunder and any other products sold by Microsemi have been subject to limited testing and should not be used in conjunction with mission-critical equipment or applications. Any performance specifications are believed to be reliable but are not verified, and Buyer must conduct and complete all performance and other testing of the products, alone and together with, or installed in, any end-products. Buyer shall not rely on any data and performance specifications or parameters provided by Microsemi. It is the Buyer's responsibility to independently determine suitability of any products and to test and verify the same. The information provided by Microsemi hereunder is provided "as is, where is" and with all faults, and the entire risk associated with such information is entirely with the Buyer. Microsemi does not grant, explicitly or implicitly, to any party any patent rights, licenses, or any other IP rights, whether with regard to such information itself or anything described by such information. Information provided in this document is proprietary to Microsemi, and Microsemi reserves the right to make any changes to the information in this document or to any products and services at any time without notice.