Welcome to E-XFL.COM

Embedded - System On Chip (SoC): The Heart of Modern Embedded Systems

**Embedded - System On Chip (SoC)** refers to an integrated circuit that consolidates all the essential components of a computer system into a single chip. This includes a microprocessor, memory, and other peripherals, all packed into one compact and efficient package. SoCs are designed to provide a complete computing solution, optimizing both space and power consumption, making them ideal for a wide range of embedded applications.

### What are Embedded - System On Chip (SoC)?

**System On Chip (SoC)** integrates multiple functions of a computer or electronic system onto a single chip. Unlike traditional multi-chip solutions. SoCs combine a central

#### Details

E·XFI

| Product Status          | Obsolete                                                        |

|-------------------------|-----------------------------------------------------------------|

| Architecture            | MCU, FPGA                                                       |

| Core Processor          | ARM® Cortex®-M3                                                 |

| Flash Size              | 128KB                                                           |

| RAM Size                | 16KB                                                            |

| Peripherals             | DMA, POR, WDT                                                   |

| Connectivity            | EBI/EMI, I <sup>2</sup> C, SPI, UART/USART                      |

| Speed                   | 80MHz                                                           |

| Primary Attributes      | ProASIC®3 FPGA, 60K Gates, 1536D-Flip-Flops                     |

| Operating Temperature   | 0°C ~ 85°C (TJ)                                                 |

| Package / Case          | 144-LQFP                                                        |

| Supplier Device Package | 144-TQFP (20x20)                                                |

| Purchase URL            | https://www.e-xfl.com/product-detail/microsemi/a2f060m3e-tqg144 |

|                         |                                                                 |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

Table of Contents

| Datasheet Categories                                                                                 |

|------------------------------------------------------------------------------------------------------|

| Microsemi SoC Products Group Safety Critical, Life Support, and High-Reliability Applications Policy |

# 🌜 Microsemi.

SmartFusion DC and Switching Characteristics

### Standby Mode and Time Keeping Mode

$P_{NET} = 0 W$

### I/O Input Buffer Dynamic Contribution—PINPUTS

### SoC Mode

$\mathsf{P}_{\mathsf{INPUTS}}$  =  $\mathsf{N}_{\mathsf{INPUTS}}$  \*  $(\alpha_2$  / 2) \*  $\mathsf{P}_{\mathsf{AC9}}$  \*  $\mathsf{F}_{\mathsf{CLK}}$  Where:

N<sub>INPUTS</sub> is the number of I/O input buffers used in the design.

$\alpha_2$  is the I/O buffer toggle rate—guidelines are provided in Table 2-17 on page 2-18.

F<sub>CLK</sub> is the global clock signal frequency.

### Standby Mode and Time Keeping Mode

P<sub>INPUTS</sub> = 0 W

### I/O Output Buffer Dynamic Contribution—POUTPUTS

### SoC Mode

$\mathsf{P}_{OUTPUTS} = \mathsf{N}_{OUTPUTS} * (\alpha_2 / 2) * \beta_1 * \mathsf{P}_{AC10} * \mathsf{F}_{CLK}$  Where:

N<sub>OUTPUTS</sub> is the number of I/O output buffers used in the design.

$\alpha_2$  is the I/O buffer toggle rate—guidelines are provided in Table 2-17 on page 2-18.

$\beta_1$  is the I/O buffer enable rate—guidelines are provided in Table 2-18 on page 2-18.

F<sub>CLK</sub> is the global clock signal frequency.

### Standby Mode and Time Keeping Mode

P<sub>OUTPUTS</sub> = 0 W

### FPGA Fabric SRAM Dynamic Contribution—P<sub>MEMORY</sub>

### SoC Mode

$P_{MEMORY} = (N_{BLOCKS} * P_{AC11} * \beta_2 * F_{READ-CLOCK}) + (N_{BLOCKS} * P_{AC12} * \beta_3 * F_{WRITE-CLOCK})$ Where:

N<sub>BLOCKS</sub> is the number of RAM blocks used in the design.

$F_{READ-CLOCK}$  is the memory read clock frequency.

$\beta_2$  is the RAM enable rate for read operations—guidelines are provided in Table 2-18 on page 2-18.

$\beta_3$  the RAM enable rate for write operations—guidelines are provided in Table 2-18 on page 2-18. F<sub>WRITE-CLOCK</sub> is the memory write clock frequency.

### Standby Mode and Time Keeping Mode

P<sub>MEMORY</sub> = 0 W

### PLL/CCC Dynamic Contribution—P<sub>PLL</sub>

### SoC Mode

P<sub>PLL</sub> = P<sub>AC13</sub> \* F<sub>CLKOUT</sub>

F<sub>CLKIN</sub> is the input clock frequency.

F<sub>CLKOUT</sub> is the output clock frequency.<sup>1</sup>

### Standby Mode and Time Keeping Mode

<sup>1.</sup> The PLL dynamic contribution depends on the input clock frequency, the number of output clock signals generated by the PLL, and the frequency of each output clock. If a PLL is used to generate more than one output clock, include each output clock in the formula output clock by adding its corresponding contribution (P<sub>AC14</sub> \* F<sub>CLKOUT</sub> product) to the total PLL contribution.

# **User I/O Characteristics**

## **Timing Model**

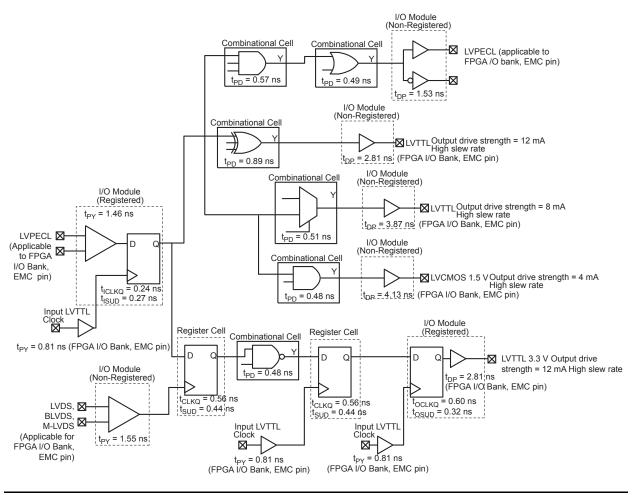

Figure 2-2 • Timing Model Operating Conditions: –1 Speed, Commercial Temperature Range (T<sub>J</sub> = 85°C), Worst Case VCC = 1.425 V

SmartFusion DC and Switching Characteristics

## **Differential I/O Characteristics**

### Physical Implementation

Configuration of the I/O modules as a differential pair is handled by SoC Products Group Designer software when the user instantiates a differential I/O macro in the design.

Differential I/Os can also be used in conjunction with the embedded Input Register (InReg), Output Register (OutReg), Enable Register (EnReg), and Double Data Rate (DDR). However, there is no support for bidirectional I/Os or tristates with the LVPECL standards.

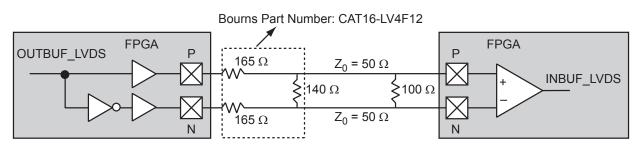

### LVDS

Low-Voltage Differential Signaling (ANSI/TIA/EIA-644) is a high-speed, differential I/O standard. It requires that one data bit be carried through two signal lines, so two pins are needed. It also requires external resistor termination.

The full implementation of the LVDS transmitter and receiver is shown in an example in Figure 2-11. The building blocks of the LVDS transmitter-receiver are one transmitter macro, one receiver macro, three board resistors at the transmitter end, and one resistor at the receiver end. The values for the three driver resistors are different from those used in the LVPECL implementation because the output standard specifications are different.

Along with LVDS I/O, SmartFusion cSoCs also support bus LVDS structure and multipoint LVDS (M-LVDS) configuration (up to 40 nodes).

Figure 2-11 • LVDS Circuit Diagram and Board-Level Implementation

| DC Parameter                 | Description                 | Min.  | Тур.  | Max.  | Units |

|------------------------------|-----------------------------|-------|-------|-------|-------|

| VCCFPGAIOBx                  | Supply voltage              | 2.375 | 2.5   | 2.625 | V     |

| VOL                          | Output low voltage          | 0.9   | 1.075 | 1.25  | V     |

| VOH                          | Output high voltage         | 1.25  | 1.425 | 1.6   | V     |

| I <sub>OL</sub> <sup>1</sup> | Output lower current        | 0.65  | 0.91  | 1.16  | mA    |

| I <sub>OH</sub> <sup>1</sup> | Output high current         | 0.65  | 0.91  | 1.16  | mA    |

| VI                           | Input voltage               | 0     |       | 2.925 | V     |

| I <sub>IH</sub> <sup>2</sup> | Input high leakage current  |       |       | 15    | μΑ    |

| I <sub>IL</sub> <sup>2</sup> | Input low leakage current   |       |       | 15    | μA    |

| V <sub>ODIFF</sub>           | Differential output voltage | 250   | 350   | 450   | mV    |

| V <sub>OCM</sub>             | Output common mode voltage  | 1.125 | 1.25  | 1.375 | V     |

| V <sub>ICM</sub>             | Input common mode voltage   | 0.05  | 1.25  | 2.35  | V     |

| V <sub>IDIFF</sub>           | Input differential voltage  | 100   | 350   |       | mV    |

Notes:

1.  $I_{OL}/I_{OH}$  defined by  $V_{ODIFF}$  (resistor network).

2. Currents are measured at 85°C junction temperature.

### Table 2-64 • AC Waveforms, Measuring Points, and Capacitive Loads

| Input Low (V) | Input High (V) | Measuring Point* (V) | V <sub>REF</sub> (typ.) (V) |

|---------------|----------------|----------------------|-----------------------------|

| 1.075         | 1.325          | Cross point          | -                           |

\* Measuring point =  $V_{trip.}$  See Table 2-22 on page 2-24 for a complete table of trip points.

### **Timing Characteristics**

### Table 2-65 • LVDS

### Worst Commercial-Case Conditions: T<sub>J</sub> = 85°C, Worst-Case VCC = 1.425 V, Worst-Case VCCFPGAIOBx = 2.3 V Applicable to FPGA I/O Banks, I/O Assigned to EMC I/O Pins

| Speed Grade | t <sub>DOUT</sub> | t <sub>DP</sub> | t <sub>DIN</sub> | t <sub>PY</sub> | Units |

|-------------|-------------------|-----------------|------------------|-----------------|-------|

| Std.        | 0.60              | 1.83            | 0.04             | 1.87            | ns    |

| -1          | 0.50              | 1.53            | 0.03             | 1.55            | ns    |

Notes:

1. For the derating values at specific junction temperature and voltage supply levels, refer to Table 2-7 on page 2-9 for derating values.

2. The above mentioned timing parameters correspond to 24mA drive strength.

# 🌜 Microsemi.

SmartFusion DC and Switching Characteristics

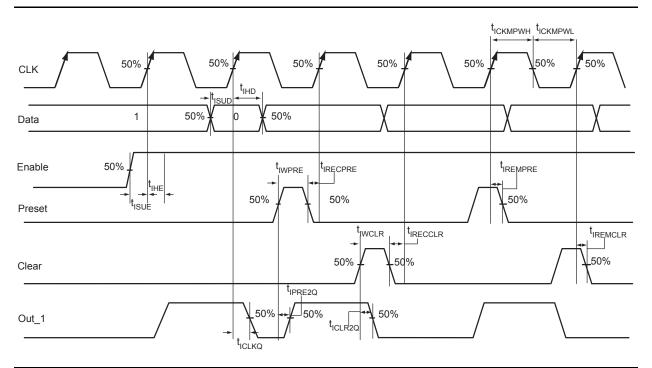

## Input Register

### **Timing Characteristics**

# Table 2-71 • Input Data Register Propagation DelaysWorst Commercial-Case Conditions: TJ = 85°C, Worst-Case VCC = 1.425 V

| Parameter            | Description                                                         | -1   | Std. | Units |

|----------------------|---------------------------------------------------------------------|------|------|-------|

| t <sub>ICLKQ</sub>   | Clock-to-Q of the Input Data Register                               | 0.24 | 0.29 | ns    |

| t <sub>ISUD</sub>    | Data Setup Time for the Input Data Register                         | 0.27 | 0.32 | ns    |

| t <sub>IHD</sub>     | Data Hold Time for the Input Data Register                          | 0.00 | 0.00 | ns    |

| t <sub>ISUE</sub>    | Enable Setup Time for the Input Data Register                       | 0.38 | 0.45 | ns    |

| t <sub>IHE</sub>     | Enable Hold Time for the Input Data Register                        | 0.00 | 0.00 | ns    |

| t <sub>ICLR2Q</sub>  | Asynchronous Clear-to-Q of the Input Data Register                  | 0.46 | 0.55 | ns    |

| t <sub>IPRE2Q</sub>  | Asynchronous Preset-to-Q of the Input Data Register                 | 0.46 | 0.55 | ns    |

| t <sub>IREMCLR</sub> | Asynchronous Clear Removal Time for the Input Data Register         | 0.00 | 0.00 | ns    |

| t <sub>IRECCLR</sub> | Asynchronous Clear Recovery Time for the Input Data Register        | 0.23 | 0.27 | ns    |

| t <sub>IREMPRE</sub> | Asynchronous Preset Removal Time for the Input Data Register        | 0.00 | 0.00 | ns    |

| t <sub>IRECPRE</sub> | Asynchronous Preset Recovery Time for the Input Data Register       | 0.23 | 0.27 | ns    |

| t <sub>IWCLR</sub>   | Asynchronous Clear Minimum Pulse Width for the Input Data Register  | 0.22 | 0.22 | ns    |

| t <sub>IWPRE</sub>   | Asynchronous Preset Minimum Pulse Width for the Input Data Register | 0.22 | 0.22 | ns    |

| t <sub>ICKMPWH</sub> | Clock Minimum Pulse Width High for the Input Data Register          | 0.36 | 0.36 | ns    |

| t <sub>ICKMPWL</sub> | Clock Minimum Pulse Width Low for the Input Data Register           | 0.32 | 0.32 | ns    |

*Note:* For the derating values at specific junction temperature and voltage supply levels, refer to Table 2-7 on page 2-9 for derating values.

**Timing Characteristics**

### Table 2-80 • A2F500 Global Resource

### Worst Commercial-Case Conditions: T<sub>J</sub> = 85°C, VCC = 1.425 V

|                      |                                           | -1                |                   | Std.              |                   |       |

|----------------------|-------------------------------------------|-------------------|-------------------|-------------------|-------------------|-------|

| Parameter            | Description                               | Min. <sup>1</sup> | Max. <sup>2</sup> | Min. <sup>1</sup> | Max. <sup>2</sup> | Units |

| t <sub>RCKL</sub>    | Input Low Delay for Global Clock          | 1.54              | 1.73              | 1.84              | 2.08              | ns    |

| t <sub>RCKH</sub>    | Input High Delay for Global Clock         | 1.53              | 1.76              | 1.84              | 2.12              | ns    |

| t <sub>RCKMPWH</sub> | Minimum Pulse Width High for Global Clock | 0.85              |                   | 1.00              |                   | ns    |

| t <sub>RCKMPWL</sub> | Minimum Pulse Width Low for Global Clock  | 0.85              |                   | 1.00              |                   | ns    |

| t <sub>RCKSW</sub>   | Maximum Skew for Global Clock             |                   | 0.23              |                   | 0.28              | ns    |

Notes:

1. Value reflects minimum load. The delay is measured from the CCC output to the clock pin of a sequential element, located in a lightly loaded row (single element is connected to the global net).

2. Value reflects maximum load. The delay is measured on the clock pin of the farthest sequential element, located in a fully loaded row (all available flip-flops are connected to the global net in the row).

3. For specific junction temperature and voltage-supply levels, refer to Table 2-7 on page 2-9 for derating values.

### Table 2-81 • A2F200 Global Resource

### Worst Commercial-Case Conditions: T<sub>J</sub> = 85°C, VCC = 1.425 V

|                      |                                           | -1                |                   | Std.              |                   |       |

|----------------------|-------------------------------------------|-------------------|-------------------|-------------------|-------------------|-------|

| Parameter            | Description                               | Min. <sup>1</sup> | Max. <sup>2</sup> | Min. <sup>1</sup> | Max. <sup>2</sup> | Units |

| t <sub>RCKL</sub>    | Input Low Delay for Global Clock          | 0.74              | 0.99              | 0.88              | 1.19              | ns    |

| t <sub>RCKH</sub>    | Input High Delay for Global Clock         | 0.76              | 1.05              | 0.91              | 1.26              | ns    |

| t <sub>RCKMPWH</sub> | Minimum Pulse Width High for Global Clock | 0.85              |                   | 1.00              |                   | ns    |

| t <sub>RCKMPWL</sub> | Minimum Pulse Width Low for Global Clock  | 0.85              |                   | 1.00              |                   | ns    |

| t <sub>RCKSW</sub>   | Maximum Skew for Global Clock             |                   | 0.29              |                   | 0.35              | ns    |

Notes:

1. Value reflects minimum load. The delay is measured from the CCC output to the clock pin of a sequential element, located in a lightly loaded row (single element is connected to the global net).

2. Value reflects maximum load. The delay is measured on the clock pin of the farthest sequential element, located in a fully loaded row (all available flip-flops are connected to the global net in the row).

3. For specific junction temperature and voltage-supply levels, refer to Table 2-7 on page 2-9 for derating values.

### **Timing Characteristics**

### Table 2-87 • RAM4K9

### Worst Commercial-Case Conditions: T<sub>J</sub> = 85°C, Worst-Case VCC = 1.425 V

| Parameter             | Description                                                                                                         | -1   | Std. | Units |

|-----------------------|---------------------------------------------------------------------------------------------------------------------|------|------|-------|

| t <sub>AS</sub>       | Address setup time                                                                                                  | 0.25 | 0.30 | ns    |

| t <sub>AH</sub>       | Address hold time                                                                                                   | 0.00 | 0.00 | ns    |

| t <sub>ENS</sub>      | REN, WEN setup time                                                                                                 | 0.15 | 0.17 | ns    |

| t <sub>ENH</sub>      | REN, WEN hold time                                                                                                  | 0.10 | 0.12 | ns    |

| t <sub>BKS</sub>      | BLK setup time                                                                                                      | 0.24 | 0.28 | ns    |

| t <sub>BKH</sub>      | BLK hold time                                                                                                       | 0.02 | 0.02 | ns    |

| t <sub>DS</sub>       | Input data (DIN) setup time                                                                                         | 0.19 | 0.22 | ns    |

| t <sub>DH</sub>       | Input data (DIN) hold time                                                                                          | 0.00 | 0.00 | ns    |

| t <sub>CKQ1</sub>     | Clock High to new data valid on DOUT (output retained, WMODE = 0)                                                   | 1.81 | 2.18 | ns    |

|                       | Clock High to new data valid on DOUT (flow-through, WMODE = 1)                                                      | 2.39 | 2.87 | ns    |

| t <sub>CKQ2</sub>     | Clock High to new data valid on DOUT (pipelined)                                                                    | 0.91 | 1.09 | ns    |

| t <sub>C2CWWH</sub> 1 | Address collision clk-to-clk delay for reliable write after write on same address—applicable to rising edge         |      | 0.26 | ns    |

| t <sub>C2CRWH</sub> 1 | Address collision clk-to-clk delay for reliable read access after write on same address—applicable to opening edge  | 0.34 | 0.38 | ns    |

| t <sub>C2CWRH</sub> 1 | Address collision clk-to-clk delay for reliable write access after read on same address— applicable to opening edge | 0.37 | 0.42 | ns    |

| t <sub>RSTBQ</sub>    | RESET Low to data out Low on DOUT (flow-through)                                                                    | 0.94 | 1.12 | ns    |

|                       | RESET Low to Data Out Low on DOUT (pipelined)                                                                       | 0.94 | 1.12 | ns    |

| t <sub>REMRSTB</sub>  | RESET removal                                                                                                       | 0.29 | 0.35 | ns    |

| t <sub>RECRSTB</sub>  | RESET recovery                                                                                                      | 1.52 | 1.83 | ns    |

| t <sub>MPWRSTB</sub>  | RESET minimum pulse width                                                                                           | 0.22 | 0.22 | ns    |

| t <sub>CYC</sub>      | Clock cycle time                                                                                                    | 3.28 | 3.28 | ns    |

| F <sub>MAX</sub>      | Maximum clock frequency                                                                                             | 305  | 305  | MHz   |

Notes:

1. For more information, refer to the Simultaneous Read-Write Operations in Dual-Port SRAM for Flash-Based cSoCs and FPGAs application note.

2. For the derating values at specific junction temperature and voltage supply levels, refer to Table 2-7 on page 2-9 for derating values.

## **Timing Characteristics**

### Table 2-89 • FIFO

| Parameter            | Description                                       | -1   | Std. | Units |

|----------------------|---------------------------------------------------|------|------|-------|

| t <sub>ENS</sub>     | REN, WEN Setup Time                               | 1.40 | 1.68 | ns    |

| t <sub>ENH</sub>     | REN, WEN Hold Time                                | 0.02 | 0.02 | ns    |

| t <sub>BKS</sub>     | BLK Setup Time                                    | 0.19 | 0.19 | ns    |

| t <sub>BKH</sub>     | BLK Hold Time                                     | 0.00 | 0.00 | ns    |

| t <sub>DS</sub>      | Input Data (WD) Setup Time                        | 0.19 | 0.22 | ns    |

| t <sub>DH</sub>      | Input Data (WD) Hold Time                         | 0.00 | 0.00 | ns    |

| t <sub>CKQ1</sub>    | Clock High to New Data Valid on RD (flow-through) | 2.39 | 2.87 | ns    |

| t <sub>CKQ2</sub>    | Clock High to New Data Valid on RD (pipelined)    | 0.91 | 1.09 | ns    |

| t <sub>RCKEF</sub>   | RCLK High to Empty Flag Valid                     | 1.74 | 2.09 | ns    |

| t <sub>WCKFF</sub>   | WCLK High to Full Flag Valid                      | 1.66 | 1.99 | ns    |

| t <sub>CKAF</sub>    | Clock HIGH to Almost Empty/Full Flag Valid        | 6.29 | 7.54 | ns    |

| t <sub>RSTFG</sub>   | RESET Low to Empty/Full Flag Valid                | 1.72 | 2.06 | ns    |

| t <sub>RSTAF</sub>   | RESET Low to Almost Empty/Full Flag Valid         | 6.22 | 7.47 | ns    |

| t <sub>RSTBQ</sub>   | RESET Low to Data Out Low on RD (flow-through)    | 0.94 | 1.12 | ns    |

|                      | RESET Low to Data Out Low on RD (pipelined)       | 0.94 | 1.12 | ns    |

| t <sub>REMRSTB</sub> | RESET Removal                                     | 0.29 | 0.35 | ns    |

| t <sub>RECRSTB</sub> | RESET Recovery                                    | 1.52 | 1.83 | ns    |

| t <sub>MPWRSTB</sub> | RESET Minimum Pulse Width                         | 0.22 | 0.22 | ns    |

| t <sub>CYC</sub>     | Clock Cycle Time                                  | 3.28 | 3.28 | ns    |

| F <sub>MAX</sub>     | Maximum Frequency for FIFO                        | 305  | 305  | MHz   |

Note: For specific junction temperature and voltage supply levels, refer to Table 2-7 on page 2-9 for derating values.

# Embedded Nonvolatile Memory Block (eNVM)

## **Electrical Characteristics**

Table 2-90 describes the eNVM maximum performance.

### *Table 2-90* • eNVM Block Timing, Worst Commercial Case Conditions: T<sub>J</sub> = 85°C, VCC = 1.425 V

|           |                                                                         | A2F060 |      | A2F200 |      | A2F500 |      |       |

|-----------|-------------------------------------------------------------------------|--------|------|--------|------|--------|------|-------|

| Parameter | Description                                                             | -1     | Std. | -1     | Std. | -1     | Std. | Units |

|           | Maximum frequency for clock for the control logic – 5 cycles (5:1:1:1*) | 50     | 50   | 50     | 50   | 50     | 50   | MHz   |

|           | Maximum frequency for clock for the control logic – 6 cycles (6:1:1:1*) | 100    | 80   | 100    | 80   | 100    | 80   | MHz   |

*Note:* \*6:1:1:1 indicates 6 cycles for the first access and 1 each for the next three accesses. 5:1:1:1 indicates 5 cycles for the first access and 1 each for the next three accesses.

Note: \*Moving from 5:1:1:1 mode to 6:1:1:1 mode results in throughput change that is dependent on the system functionality. When the Cortex-M3 code is executed from eNVM - with sequential firmware (sequential address reads), the throughput reduction can be around 10%.

# **Embedded FlashROM (eFROM)**

## **Electrical Characteristics**

Table 2-91 describes the eFROM maximum performance

| Parameter         | Description                     | -1    | Std.  | Units |

|-------------------|---------------------------------|-------|-------|-------|

| t <sub>CK2Q</sub> | Clock to out per configuration* | 28.68 | 32.98 | ns    |

| F <sub>max</sub>  | Maximum Clock frequency         | 15.00 | 15.00 | MHz   |

## **JTAG 1532 Characteristics**

JTAG timing delays do not include JTAG I/Os. To obtain complete JTAG timing, add I/O buffer delays to the corresponding standard selected; refer to the I/O timing characteristics in the "User I/O Characteristics" section on page 2-19 for more details.

### **Timing Characteristics**

### Table 2-92 • JTAG 1532

Worst Commercial-Case Conditions: T<sub>J</sub> = 85°C, Worst-Case VCC = 1.425 V

| Parameter          | Description                 | -1   | Std. | Units |

|--------------------|-----------------------------|------|------|-------|

| t <sub>DISU</sub>  | Test Data Input Setup Time  | 0.67 | 0.77 | ns    |

| t <sub>DIHD</sub>  | Test Data Input Hold Time   | 1.33 | 1.53 | ns    |

| t <sub>TMSSU</sub> | Test Mode Select Setup Time | 0.67 | 0.77 | ns    |

| t <sub>TMDHD</sub> | Test Mode Select Hold Time  | 1.33 | 1.53 | ns    |

| t <sub>TCK2Q</sub> | Clock to Q (data out)       | 8.00 | 9.20 | ns    |

Note: For specific junction temperature and voltage supply levels, refer to Table 2-7 on page 2-9 for derating values.

## **Temperature Monitor**

Unless otherwise noted, temperature monitor performance is specified with a 2N3904 diode-connected bipolar transistor from National Semiconductor or Infineon Technologies, nominal power supply voltages, with the output measured using the internal voltage reference with the internal ADC in 12-bit mode and 62.5 Ksps. After digital compensation. Unless otherwise noted, the specifications pertain to conditions where the SmartFusion cSoC and the sensing diode are at the same temperature.

| Table 2-94 • Temperature Monitor Performance Specifications |

|-------------------------------------------------------------|

|-------------------------------------------------------------|

| Specification                                                  | Test Conditions                                                                                         | Min.  | Typical | Max.   | Units  |

|----------------------------------------------------------------|---------------------------------------------------------------------------------------------------------|-------|---------|--------|--------|

| Input diode temperature range                                  |                                                                                                         | -55   |         | 150    | °C     |

|                                                                |                                                                                                         | 233.2 |         | 378.15 | K      |

| Temperature sensitivity                                        |                                                                                                         |       | 2.5     |        | mV/K   |

| Intercept                                                      | Extrapolated to 0K                                                                                      |       | 0       |        | V      |

| Input referred temperature offset error                        | At 25°C (298.15K)                                                                                       |       | ±1      | 1.5    | °C     |

| Gain error                                                     | Slope of BFSL vs. 2.5 mV/K                                                                              |       | ±1      | 2.5    | % nom. |

| Overall accuracy                                               | Peak error from ideal transfer function                                                                 |       | ±2      | ±3     | °C     |

| Input referred noise                                           | At 25°C (298.15K) – no output averaging                                                                 |       | 4       |        | °C rms |

| Output current                                                 | Idle mode                                                                                               |       | 100     |        | μA     |

|                                                                | Final measurement phases                                                                                |       | 10      |        | μA     |

| Analog settling time                                           | Measured to 0.1% of final value, (with ADC load)                                                        |       |         |        |        |

|                                                                | From TM_STB (High)                                                                                      | 5     |         |        | μs     |

|                                                                | From ADC_START (High)                                                                                   | 5     |         | 105    | μs     |

| AT parasitic capacitance                                       |                                                                                                         |       |         | 500    | pF     |

| Power supply rejection ratio                                   | DC (0–10 KHz)                                                                                           | 1.2   | 0.7     |        | °C/V   |

| Input referred temperature sensitivity error                   | Variation due to device temperature<br>(–40°C to +100°C). External temperature<br>sensor held constant. |       | 0.005   | 0.008  | °C/°C  |

| Temperature monitor (TM)                                       | VCC33A                                                                                                  |       | 200     |        | μA     |

| operational power supply current requirements (per temperature | VCC33AP                                                                                                 |       | 150     |        | μA     |

| monitor instance, not including ADC or VAREFx)                 | VCC15A                                                                                                  |       | 50      |        | μA     |

Note: All results are based on averaging over 64 samples.

| Specification                                                | Test Conditions                                | Min.  | Тур.  | Max. | Units |

|--------------------------------------------------------------|------------------------------------------------|-------|-------|------|-------|

| Input referred offset voltage                                |                                                |       |       |      |       |

|                                                              | GDEC[1:0] = 11                                 | -0.31 | -0.07 | 0.31 | % FS* |

|                                                              | -40°C to +100°C                                | -1.00 |       | 1.47 | % FS* |

|                                                              | GDEC[1:0] = 10                                 | -0.34 | -0.07 | 0.34 | % FS* |

|                                                              | -40°C to +100°C                                | -0.90 |       | 1.37 | % FS* |

|                                                              | GDEC[1:0] = 01                                 | -0.61 | -0.07 | 0.35 | % FS* |

|                                                              | -40°C to +100°C                                | -1.05 |       | 1.35 | % FS* |

|                                                              | GDEC[1:0] = 00                                 | -0.39 | -0.07 | 0.35 | % FS* |

|                                                              | -40°C to +100°C                                | -1.06 |       | 1.38 | % FS* |

| SINAD                                                        |                                                | 53    | 56    |      | dB    |

| Non-linearity                                                | RMS deviation from BFSL                        |       |       | 0.5  | % FS* |

| Effective number of bits (ENOB)                              | GDEC[1:0] = 11<br>(±2.56 range), –1 dBFS input |       |       |      |       |

| $ENOB = \frac{SINAD - 1.76 \text{ dB}}{6.02 \text{ dB/bit}}$ | 12-bit mode 10 KHz                             | 8.6   | 9.1   |      | Bits  |

| EQ 11                                                        | 12-bit mode 100 KHz                            | 8.6   | 9.1   |      | Bits  |

|                                                              | 10-bit mode 10 KHz                             | 8.5   | 8.9   |      | Bits  |

|                                                              | 10-bit mode 100 KHz                            | 8.5   | 8.9   |      | Bits  |

|                                                              | 8-bit mode 10 KHz                              | 7.7   | 7.8   |      | Bits  |

|                                                              | 8-bit mode 100 KHz                             | 7.7   | 7.8   |      | Bits  |

| Large-signal bandwidth                                       | –1 dBFS input                                  |       | 1     |      | MHz   |

| Analog settling time                                         | To 0.1% of final value (with ADC load)         |       |       | 10   | μs    |

| Input resistance                                             |                                                |       | 1     |      | MΩ    |

| Power supply rejection ratio                                 | DC (0–1 KHz)                                   | 38    | 40    |      | dB    |

| ABPS power supply current                                    | ABPS_EN = 1 (operational mode)                 |       | -     |      | •     |

| requirements (not including ADC or<br>VAREFx)                | VCC33A                                         |       | 123   | 134  | μA    |

|                                                              | VCC33AP                                        |       | 89    | 94   | μA    |

|                                                              | VCC15A                                         |       | 1     |      | μA    |

| Table 2-96 • ABPS Performance Specifications | (continued) |

|----------------------------------------------|-------------|

|----------------------------------------------|-------------|

Note: \*FS is full-scale error, defined as the difference between the actual value that triggers the transition to full-scale and the ideal analog full-scale transition value. Full-scale error equals offset error plus gain error. Refer to the Analog-to-Digital Converter chapter of the SmartFusion Programmable Analog User's Guide for more information.

SmartFusion DC and Switching Characteristics

### Table 2-98 • Analog Sigma-Delta DAC (continued)

| Specification                                                            | Test Conditions                                  | Min. | Тур. | Max. | Units |

|--------------------------------------------------------------------------|--------------------------------------------------|------|------|------|-------|

| Sigma-delta DAC power supply current requirements (not including VAREFx) | Input = 0, EN = 1<br>(operational mode)          |      |      |      |       |

|                                                                          | VCC33SDDx                                        |      | 30   | 35   | μA    |

|                                                                          | VCC15A                                           |      | 3    | 5    | μA    |

|                                                                          | Input = Half scale, EN = 1<br>(operational mode) |      |      |      |       |

|                                                                          | VCC33SDDx                                        |      | 160  | 165  | μA    |

|                                                                          | VCC15A                                           |      | 33   | 35   | μA    |

|                                                                          | Input = Full scale, EN = 1<br>(operational mode) |      |      |      |       |

|                                                                          | VCC33SDDx                                        |      | 280  | 285  | μA    |

|                                                                          | VCC15A                                           |      | 70   | 75   | μA    |

Note: \*FS is full-scale error, defined as the difference between the actual value that triggers the transition to full-scale and the ideal analog full-scale transition value. Full-scale error equals offset error plus gain error. Refer to the Analog-to-Digital Converter chapter of the SmartFusion Programmable Analog User's Guide for more information.

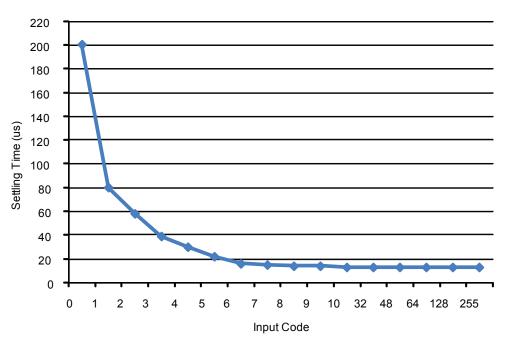

### Sigma Delta DAC Settling Time

Figure 2-44 • Sigma-Delta DAC Setting Time

# **Serial Peripheral Interface (SPI) Characteristics**

This section describes the DC and switching of the SPI interface. Unless otherwise noted, all output characteristics given for a 35 pF load on the pins and all sequential timing characteristics are related to SPI\_x\_CLK. For timing parameter definitions, refer to Figure 2-47 on page 2-90.

| Symbol | Description and Condition                                      | A2F060 | A2F200 | A2F500 | Unit |  |  |  |

|--------|----------------------------------------------------------------|--------|--------|--------|------|--|--|--|

| sp1    | SPI_x_CLK minimum period                                       |        |        | LU     |      |  |  |  |

|        | SPI_x_CLK = PCLK/2                                             | 20     | NA     | 20     | ns   |  |  |  |

|        | SPI_x_CLK = PCLK/4                                             | 40     | 40     | 40     | ns   |  |  |  |

|        | SPI_x_CLK = PCLK/8                                             | 80     | 80     | 80     | ns   |  |  |  |

|        | SPI_x_CLK = PCLK/16                                            | 0.16   | 0.16   | 0.16   | μs   |  |  |  |

|        | SPI_x_CLK = PCLK/32                                            | 0.32   | 0.32   | 0.32   | μs   |  |  |  |

|        | SPI_x_CLK = PCLK/64                                            | 0.64   | 0.64   | 0.64   | μs   |  |  |  |

|        | SPI_x_CLK = PCLK/128                                           | 1.28   | 1.28   | 1.28   | μs   |  |  |  |

|        | SPI_x_CLK = PCLK/256                                           | 2.56   | 2.56   | 2.56   | μs   |  |  |  |

| sp2    | SPI_x_CLK minimum pulse width high                             |        |        |        |      |  |  |  |

|        | SPI_x_CLK = PCLK/2                                             | 10     | NA     | 10     | ns   |  |  |  |

|        | SPI_x_CLK = PCLK/4                                             | 20     | 20     | 20     | ns   |  |  |  |

|        | SPI_x_CLK = PCLK/8                                             | 40     | 40     | 40     | ns   |  |  |  |

|        | SPI_x_CLK = PCLK/16                                            | 0.08   | 0.08   | 0.08   | μs   |  |  |  |

|        | SPI_x_CLK = PCLK/32                                            | 0.16   | 0.16   | 0.16   | μs   |  |  |  |

|        | SPI_x_CLK = PCLK/64                                            | 0.32   | 0.32   | 0.32   | μs   |  |  |  |

|        | SPI_x_CLK = PCLK/128                                           | 0.64   | 0.64   | 0.64   | μs   |  |  |  |

|        | SPI_x_CLK = PCLK/256                                           | 1.28   | 1.28   | 1.28   | us   |  |  |  |

| sp3    | SPI_x_CLK minimum pulse width low                              |        |        |        |      |  |  |  |

|        | SPI_x_CLK = PCLK/2                                             | 10     | NA     | 10     | ns   |  |  |  |

|        | SPI_x_CLK = PCLK/4                                             | 20     | 20     | 20     | ns   |  |  |  |

|        | SPI_x_CLK = PCLK/8                                             | 40     | 40     | 40     | ns   |  |  |  |

|        | SPI_x_CLK = PCLK/16                                            | 0.08   | 0.08   | 0.08   | μs   |  |  |  |

|        | SPI_x_CLK = PCLK/32                                            | 0.16   | 0.16   | 0.16   | μs   |  |  |  |

|        | SPI_x_CLK = PCLK/64                                            | 0.32   | 0.32   | 0.32   | μs   |  |  |  |

|        | SPI_x_CLK = PCLK/128                                           | 0.64   | 0.64   | 0.64   | μs   |  |  |  |

|        | SPI_x_CLK = PCLK/256                                           | 1.28   | 1.28   | 1.28   | μs   |  |  |  |

| sp4    | SPI_x_CLK, SPI_x_DO, SPI_x_SS rise time (10%-90%) <sup>1</sup> | 4.7    | 4.7    | 4.7    | ns   |  |  |  |

| sp5    | SPI_x_CLK, SPI_x_DO, SPI_x_SS fall time (10%-90%) <sup>1</sup> | 3.4    | 3.4    | 3.4    | ns   |  |  |  |

### Table 2-100 • SPI Characteristics

Commercial Case Conditions: T<sub>J</sub> = 85°C, VDD = 1.425 V, -1 Speed Grade

Notes:

These values are provided for a load of 35 pF. For board design considerations and detailed output buffer resistances, use the corresponding IBIS models located on the Microsemi SoC Products Group website: http://www.microsemi.com/index.php?option=com\_microsemi&ltemid=489&lang=en&view=salescontact.

2. For allowable pclk configurations, refer to the Serial Peripheral Interface Controller section in the SmartFusion Microcontroller Subsystem User's Guide.

| Name        | Туре   | Description                                                                                                                                                                                                                                                  |

|-------------|--------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| VCCFPGAIOB5 | Supply | Digital supply to the FPGA fabric I/O bank 5 (west FPGA I/O bank) for the output buffers and I/O logic.                                                                                                                                                      |

|             |        | Each bank can have a separate VCCFPGAIO connection. All I/Os in a bank will run off the same VCCFPGAIO supply. VCCFPGAIO can be 1.5 V, 1.8 V, 2.5 V, or 3.3 V, nominal voltage. Unused I/O banks should have their corresponding VCCFPGAIO pins tied to GND. |

| VCCLPXTAL   | Supply | Analog supply to the low power 32 KHz crystal oscillator. Always power this pin. <sup>1</sup>                                                                                                                                                                |

| VCCMAINXTAL | Supply | Analog supply to the main crystal oscillator circuit. Always power this pin. <sup>1</sup>                                                                                                                                                                    |

| VCCMSSIOB2  | Supply | Supply voltage to the microcontroller subsystem I/O bank 2 (east MSS I/O bank) for the<br>output buffers and I/O logic.                                                                                                                                      |

|             |        | Each bank can have a separate VCCMSSIO connection. All I/Os in a bank will run off the same VCCMSSIO supply. VCCMSSIO can be 1.5 V, 1.8 V, 2.5 V, or 3.3 V, nominal voltage. Unused I/O banks should have their corresponding VCCMSSIO pins tied to GND.     |

| VCCMSSIOB4  | Supply | Supply voltage to the microcontroller subsystem I/O bank 4 (west MSS I/O bank) for the output buffers and I/O logic.                                                                                                                                         |

|             |        | Each bank can have a separate VCCMSSIO connection. All I/Os in a bank will run off the same VCCMSSIO supply. VCCMSSIO can be 1.5 V, 1.8 V, 2.5 V, or 3.3 V, nominal voltage. Unused I/O banks should have their corresponding VCCMSSIO pins tied to GND.     |

| VCCPLLx     | Supply | Analog 1.5 V supply to the PLL. Always power this pin.                                                                                                                                                                                                       |

| VCCRCOSC    | Supply | Analog supply to the integrated RC oscillator circuit. Always power this pin. <sup>1</sup>                                                                                                                                                                   |

| VCOMPLAx    | Supply | Analog ground for the PLL                                                                                                                                                                                                                                    |

| VDDBAT      | Supply | External battery connection to the low power 32 KHz crystal oscillator (along with VCCLPXTAL), RTC, and battery switchover circuit. Can be pulled down if unused.                                                                                            |

Notes:

1. The following 3.3 V supplies should be connected together while following proper noise filtering practices: VCC33A, VCC33ADCx, VCC33ADCx, VCC33SDDx, VCCMAINXTAL, and VCCLPXTAL.

2. The following 1.5 V supplies should be connected together while following proper noise filtering practices: VCC, VCC15A, and VCC15ADCx.

3. For more details on VCCPLLx capacitor recommendations, refer to the application note AC359, SmartFusion cSoC Board Design Guidelines, the "PLL Power Supply Decoupling Scheme" section.

# **JTAG Pins**

SmartFusion cSoCs have a separate bank for the dedicated JTAG pins. The JTAG pins can be run at any voltage from 1.5 V to 3.3 V (nominal). VCC must also be powered for the JTAG state machine to operate, even if the device is in bypass mode; VJTAG alone is insufficient. Both VJTAG and VCC to the SmartFusion cSoC part must be supplied to allow JTAG signals to transition the SmartFusion cSoC. Isolating the JTAG power supply in a separate I/O bank gives greater flexibility with supply selection and simplifies power supply and PCB design. If the JTAG interface is neither used nor planned to be used, the VJTAG pin together with the TRSTB pin could be tied to GND.

| Name    | Туре | Polarity/<br>Bus Size | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

|---------|------|-----------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| JTAGSEL | In   | 1                     | JTAG controller selection                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

|         |      |                       | Depending on the state of the JTAGSEL pin, an external JTAG controller will either see the FPGA fabric TAP/auxiliary TAP (High) or the Cortex-M3 JTAG debug interface (Low).                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

|         |      |                       | The JTAGSEL pin should be connected to an external pull-up resistor such that the default configuration selects the FPGA fabric TAP.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

| ТСК     | In   | 1                     | Test clock                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

|         |      |                       | Serial input for JTAG boundary scan, ISP, and UJTAG. The TCK pin does not have an internal pull-up/-down resistor. If JTAG is not used, it is recommended to tie off TCK to GND or $V_{JTAG}$ through a resistor placed close to the FPGA pin. This prevents JTAG operation in case TMS enters an undesired state.                                                                                                                                                                                                                                                                                                                                 |

|         |      |                       | Note that to operate at all V <sub>JTAG</sub> voltages, 500 $\Omega$ to 1 k $\Omega$ will satisfy the requirements. Refer to Table 5-1 on page 5-11 for more information.                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

|         |      |                       | Can be left floating when unused.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

| TDI     | In   | 1                     | Test data                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

|         |      |                       | Serial input for JTAG boundary scan, ISP, and UJTAG usage. There is an internal weak pull-up resistor on the TDI pin.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

| TDO     | Out  | 1                     | Test data                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

|         |      |                       | Serial output for JTAG boundary scan, ISP, and UJTAG usage.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

| TMS     | In   | HIGH                  | Test mode select                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

|         |      |                       | The TMS pin controls the use of the IEEE1532 boundary scan pins (TCK, TDI, TDO, TRST). There is an internal weak pull-up resistor on the TMS pin.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

|         |      |                       | Can be left floating when unused.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

| TRSTB   | In   | HIGH                  | Boundary scan reset pin                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

|         |      |                       | The TRST pin functions as an active low input to asynchronously initialize (or reset) the boundary scan circuitry. There is an internal weak pull-up resistor on the TRST pin. If JTAG is not used, an external pull-down resistor could be included to ensure the TAP is held in reset mode. The resistor values must be chosen from Table 5-1 on page 5-11 and must satisfy the parallel resistance value requirement. The values in Table 5-1 on page 5-11 correspond to the resistor recommended when a single device is used. The values correspond to the equivalent parallel resistor when multiple devices are connected via a JTAG chain. |

|         |      |                       | In critical applications, an upset in the JTAG circuit could allow entering an undesired JTAG state. In such cases, it is recommended that you tie off TRST to GND through a resistor placed close to the FPGA pin.                                                                                                                                                                                                                                                                                                                                                                                                                                |

|         |      |                       | The TRSTB pin also resets the serial wire JTAG – debug port (SWJ-DP) circuitry within the Cortex-M3.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

|         |      |                       | Can be left floating when unused.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

|            | PQ208                 |                 |  |

|------------|-----------------------|-----------------|--|

| Pin Number | A2F200                | A2F500          |  |

| 156        | GNDQ                  | GNDQ            |  |

| 157        | GNDQ                  | GNDQ            |  |

| 158        | VCCFPGAIOB0           | VCCFPGAIOB0     |  |

| 159        | GBA1/IO19PDB0V0       | GBA1/IO23PDB0V0 |  |

| 160        | GBA0/IO19NDB0V0       | GBA0/IO23NDB0V0 |  |

| 161        | VCCFPGAIOB0           | VCCFPGAIOB0     |  |

| 162        | GND                   | GND             |  |

| 163        | VCC                   | VCC             |  |

| 164        | EMC_AB[25]/IO16PDB0V0 | IO21PDB0V0      |  |

| 165        | EMC_AB[24]/IO16NDB0V0 | IO21NDB0V0      |  |

| 166        | EMC_AB[23]/IO15PDB0V0 | IO20PDB0V0      |  |

| 167        | EMC_AB[22]/IO15NDB0V0 | IO20NDB0V0      |  |

| 168        | EMC_AB[21]/IO14PDB0V0 | IO19PDB0V0      |  |

| 169        | EMC_AB[20]/IO14NDB0V0 | IO19NDB0V0      |  |

| 170        | EMC_AB[19]/IO13PDB0V0 | IO18PDB0V0      |  |

| 171        | EMC_AB[18]/IO13NDB0V0 | IO18NDB0V0      |  |

| 172        | EMC_AB[17]/IO12PDB0V0 | IO17PDB0V0      |  |

| 173        | EMC_AB[16]/IO12NDB0V0 | IO17NDB0V0      |  |

| 174        | VCCFPGAIOB0           | VCCFPGAIOB0     |  |

| 175        | GND                   | GND             |  |

| 176        | VCC                   | VCC             |  |

| 177        | EMC_AB[15]/IO11PDB0V0 | IO14PDB0V0      |  |

| 178        | EMC_AB[14]/IO11NDB0V0 | IO14NDB0V0      |  |

| 179        | EMC_AB[13]/IO10PDB0V0 | IO13PDB0V0      |  |

| 180        | EMC_AB[12]/IO10NDB0V0 | IO13NDB0V0      |  |

| 181        | EMC_AB[11]/IO09PDB0V0 | IO12PDB0V0      |  |

| 182        | EMC_AB[10]/IO09NDB0V0 | IO12NDB0V0      |  |

| 183        | EMC_AB[9]/IO08PDB0V0  | IO11PDB0V0      |  |

| 184        | EMC_AB[8]/IO08NDB0V0  | IO11NDB0V0      |  |

| 185        | EMC_AB[7]/IO07PDB0V0  | IO10PDB0V0      |  |

| 186        | EMC_AB[6]/IO07NDB0V0  | IO10NDB0V0      |  |

Notes:

1. Shading denotes pins that do not have completely identical functions from density to density. For example, the bank assignment can be different for an I/O, or the function might be available only on a larger density device.

\*: Indicates that the signal assigned to the pins as a CLKBUF/CLKBUF\_LVPECL/CLKBUF\_LVDS goes through a glitchless mux. In order for the glitchless mux to operate correctly, the signal must be a free-running clock signal. Refer to the 'Glitchless MUX' section in the SmartFusion Microcontroller Subsystem User's Guide for more details.

Datasheet Information

| Revision                  | Changes                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | Page |

|---------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------|

| Revision 3<br>(continued) | In Table 2-3 • Recommended Operating Conditions <sup>5,6</sup> , the VDDBAT recommended<br>operating range was changed from "2.97 to 3.63" to "2.7 to 3.63" (SAR 25246).<br>Recommended operating range was changed to "3.15 to 3.45" for the following<br>voltages:<br>VCC33A<br>VCC33ADCx<br>VCC33AP<br>VCC33SDDx<br>VCCMAINXTAL<br>VCCLPXTAL<br>Two notes were added to the table (SAR 27109):<br>1. The following 3.3 V supplies should be connected together while following proper<br>noise filtering practices: VCC33A, VCC33ADCx, VCC33AP, VCC33SDDx,<br>VCCMAINXTAL, and VCCLPXTAL.<br>2. The following 1.5 V supplies should be connected together while following proper | 2-3  |

|                           | noise filtering practices: VCC, VCC15A, and VCC15ADCx.<br>In Table 2-3 • Recommended Operating Conditions <sup>5,6</sup> , the description for                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | 2-3  |

|                           | VCCLPXTAL was corrected to change "32 Hz" to "32 KHz" (SAR 27110).                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |      |

|                           | The "Power Supply Sequencing Requirement" section is new (SAR 27178).                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | 2-4  |

|                           | Table 2-8 • Power Supplies Configuration was revised to change most on/off entries to voltages. Note 5 was added, stating that "on" means proper voltage is applied. The values of 6 $\mu$ A and 16 $\mu$ A were removed for IDC1 and IDC2 for 3.3 V. A note was added for IDC1 and IDC2: "Power mode and Sleep mode are consuming higher current than expected in the current version of silicon. These specifications will be updated when new version of the silicon is available" (SAR 27926).                                                                                                                                                                                  | 2-10 |

|                           | The "Power-Down and Sleep Mode Implementation" section is new (SAR 27178).                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | 2-11 |

|                           | A note was added to Table 2-86 • SmartFusion CCC/PLL Specification, pertaining to $f_{out\_CCC}$ , stating that "one of the CCC outputs (GLA0) is used as an MSS clock and is limited to 100 MHz (maximum) by software" (SAR 26388).                                                                                                                                                                                                                                                                                                                                                                                                                                                | 2-63 |

|                           | Table 2-90 • eNVM Block Timing, Worst Commercial Case Conditions: $T_J = 85^{\circ}C$ , VCC = 1.425 V was revised. Values were included for A2F200 and A2F500, for -1 and Std. speed grades. A note was added to define 6:1:1:1 and 5:1:1:1 (SAR 26166).                                                                                                                                                                                                                                                                                                                                                                                                                            | 2-76 |

|                           | The units were corrected (mV instead of V) for input referred offset voltage, GDEC[1:0] = 00 in Table 2-96 • ABPS Performance Specifications (SAR 25381).                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | 2-82 |

|                           | The test condition values for operating current (ICC33A, typical) were changed in Table 2-99 • Voltage Regulator (SAR 26465).                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | 2-87 |

|                           | Figure 2-45 • Typical Output Voltage was revised to add legends for the three curves, stating the load represented by each (SAR 25247).                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 2-88 |

|                           | The "SmartFusion Programming" chapter was moved to this document from the SmartFusion Subsystem Microcontroller User's Guide (SAR 26542). The "Typical Programming and Erase Times" section was added to this chapter.                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 4-7  |

|                           | Figure 4-1 • TRSTB Logic was revised to change 1.5 V to "VJTAG (1.5 V to 3.3 V nominal)" (SAR 24694).                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | 4-8  |

SmartFusion Customizable System-on-Chip (cSoC)

| Revision                   | Changes                                                                                                                                                                                                                                  | Page |

|----------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------|

| (continued)                | "SmartFusion Development Tools" section was replaced with new content.                                                                                                                                                                   |      |

|                            | The pin description tables were revised by adding additional pins to reflect the pinout for A2F500.                                                                                                                                      |      |

|                            | The descriptions for "GNDSDD1" and "VCC33SDD1" were revised.                                                                                                                                                                             |      |

|                            | The description for "VCC33A" was revised.                                                                                                                                                                                                |      |

|                            | The pin tables for the "FG256" and "FG484" were replaced with tables that compare pin functions across densities for each package.                                                                                                       |      |

| Draft B<br>(December 2009) | The "Digital I/Os" section was renamed to the "I/Os and Operating Voltage" section and information was added regarding digital and analog VCC.                                                                                           |      |

|                            | The "SmartFusion cSoC Family Product Table" and "Package I/Os: MSS + FPGA I/Os" section were revised.                                                                                                                                    | П    |

|                            | The terminology for the analog blocks was changed to "programmable analog," consisting of two blocks: the analog front-end and analog compute engine. This is reflected throughout the text and in the "SmartFusion cSoC Block Diagram". | IV   |

|                            | The "Product Ordering Codes" table was revised to add G as an ordering code for eNVM size.                                                                                                                                               | VI   |