Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

#### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Product Status             | Active                                                                 |

|----------------------------|------------------------------------------------------------------------|

| Core Processor             | ARM® Cortex®-M4                                                        |

| Core Size                  | 32-Bit Single-Core                                                     |

| Speed                      | 100MHz                                                                 |

| Connectivity               | I <sup>2</sup> C, IrDA, LINbus, MMC/SD/SDIO, SPI, UART/USART, USB OTG  |

| Peripherals                | Brown-out Detect/Reset, DMA, I <sup>2</sup> S, POR, PWM, WDT           |

| Number of I/O              | 36                                                                     |

| Program Memory Size        | 512KB (512K x 8)                                                       |

| Program Memory Type        | FLASH                                                                  |

| EEPROM Size                | -                                                                      |

| RAM Size                   | 128K x 8                                                               |

| Voltage - Supply (Vcc/Vdd) | 1.7V ~ 3.6V                                                            |

| Data Converters            | A/D 10x12b                                                             |

| Oscillator Type            | Internal                                                               |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                      |

| Mounting Type              | Surface Mount                                                          |

| Package / Case             | 48-UFQFN Exposed Pad                                                   |

| Supplier Device Package    | 48-UFQFPN (7x7)                                                        |

| Purchase URL               | https://www.e-xfl.com/product-detail/stmicroelectronics/stm32f411ceu6u |

|                            |                                                                        |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

## 4 Pinouts and pin description

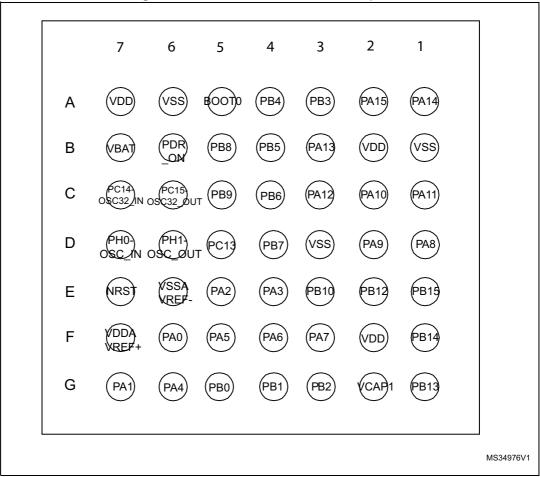

Figure 9. STM32F411xC/xE WLCSP49 pinout

1. The above figure shows the package bump side.

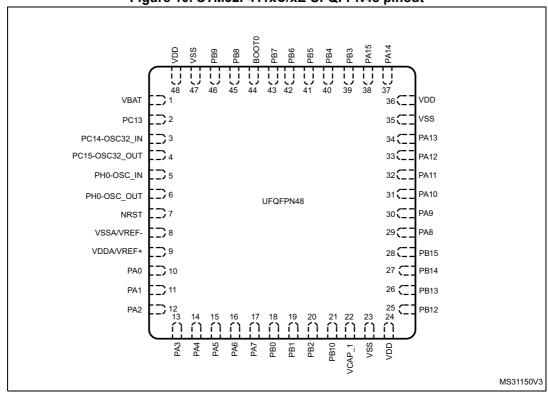

Figure 10. STM32F411xC/xE UFQFPN48 pinout

1. The above figure shows the package top view.

#### STM32F411xC STM32F411xE

|   |                  |        |       |        |       |       |            |       | -      |        |           |        |

|---|------------------|--------|-------|--------|-------|-------|------------|-------|--------|--------|-----------|--------|

|   | 1                | 2      | 3     | 4      | 5     | 6     | 7          | 8     | 9      | 10     | 11        | 12     |

| A | (PE3)            | (PE1)  | (РВ8) | (BOO)0 | (PD7) | (PD5) | РВ4        | (РВЗ) | (PA15) | (PA14) | PA13      | (PA12) |

| в | PE4              | (PE2)  | (PB9) | (PB7)  | (PB6) | (PD6) |            | (PD3) | (PD1)  | C12    | PC10      | (PA11) |

| с |                  | MP PE5 | (PE0) | VDD    | (PB5) |       | <br>       | (PD2) | PD0    | C11    | (CAP<br>2 | PA10   |

| D | FC14<br>OSC32_IN | PE6    | VSS   |        |       |       | <br>       |       |        | (PA9)  | (PA8)     | PC9    |

| E | PC15)<br>05C32_0 | VBAT   | BYPAS | S_REG  |       |       |            |       |        | PC8    | PC7       | PC6    |

| F | PH0<br>SC N      | VSS    |       |        |       |       | <br> <br>+ |       |        |        | VSS       | vss    |

| G | PH1<br>OSCOL     |        |       |        |       |       | <br>       |       |        |        | VDD       | VDD    |

| н | PCO              | NRS    |       | DN     |       |       | <br>       |       |        | D15    | PD14      | PD13   |

| J | VSSA             | PC1    | PC2   |        |       |       |            |       |        | ©D12   | PD11      | PD10   |

| к | VRET-            | PC3    | (PA2) | (PA5)  | (PC4) |       | <br>       | (PD9) | (PB11) | PB15   | PB14      | PB13   |

| L | VREF+            | PAO    | (PA3) | (PA6)  | PC5   | (PB2) | (PE8)      | PE10  | PE12   | PB10   | (VCAP)    | PB12   |

| м | VDDA             | (PA1)  | (PA4) | (PA7)  | (PB0) | (PB1) | PE7        | (PE9) | (PE11) | PE13   | PE14      | PE15   |

#### Figure 13. STM32F411xC/xE UFBGA100 pinout

1. This figure shows the package top view

## 6.3.5 Embedded reset and power control block characteristics

The parameters given in *Table 19* are derived from tests performed under ambient temperature and  $V_{DD}$  supply voltage @ 3.3V.

| Symbol                              | Parameter                | Conditions                  | Min                 | Тур  | Мах  | Unit |  |

|-------------------------------------|--------------------------|-----------------------------|---------------------|------|------|------|--|

|                                     |                          | PLS[2:0]=000 (rising edge)  | 2.09                | 2.14 | 2.19 |      |  |

|                                     |                          | PLS[2:0]=000 (falling edge) | 1.98                | 2.04 | 2.08 |      |  |

|                                     |                          | PLS[2:0]=001 (rising edge)  | 2.23                | 2.30 | 2.37 |      |  |

|                                     |                          | PLS[2:0]=001 (falling edge) | 2.13                | 2.19 | 2.25 |      |  |

|                                     |                          | PLS[2:0]=010 (rising edge)  | 2.39                | 2.45 | 2.51 |      |  |

|                                     |                          | PLS[2:0]=010 (falling edge) | 2.29                | 2.35 | 2.39 |      |  |

|                                     |                          | PLS[2:0]=011 (rising edge)  | 2.54                | 2.60 | 2.65 |      |  |

| N/                                  | Programmable voltage     | PLS[2:0]=011 (falling edge) | 2.44                | 2.51 | 2.56 | V    |  |

| V <sub>PVD</sub>                    | detector level selection | PLS[2:0]=100 (rising edge)  | 2.70                | 2.76 | 2.82 | V    |  |

|                                     |                          | PLS[2:0]=100 (falling edge) | 2.59                | 2.66 | 2.71 |      |  |

|                                     |                          | PLS[2:0]=101 (rising edge)  | 2.86                | 2.93 | 2.99 |      |  |

|                                     |                          | PLS[2:0]=101 (falling edge) | 2.77                | 2.82 | 2.89 |      |  |

|                                     |                          | PLS[2:0]=110 (rising edge)  | 2.96                | 3.03 | 3.10 |      |  |

|                                     |                          | PLS[2:0]=110 (falling edge) | 2.85                | 2.93 | 2.99 |      |  |

|                                     |                          | PLS[2:0]=111 (rising edge)  | 3.07                | 3.14 | 3.21 |      |  |

|                                     |                          | PLS[2:0]=111 (falling edge) | 2.95                | 3.03 | 3.09 |      |  |

| V <sub>PVDhyst</sub> <sup>(2)</sup> | PVD hysteresis           | -                           | -                   | 100  | -    | mV   |  |

|                                     | Power-on/power-down      | Falling edge                | 1.60 <sup>(1)</sup> | 1.68 | 1.76 | V    |  |

| V <sub>POR/PDR</sub>                | reset threshold          | Rising edge                 | 1.64                | 1.72 | 1.80 | v    |  |

| V <sub>PDRhyst</sub> <sup>(2)</sup> | PDR hysteresis           | -                           | -                   | 40   | -    | mV   |  |

| V                                   | Brownout level 1         | Falling edge                | 2.13                | 2.19 | 2.24 |      |  |

| V <sub>BOR1</sub>                   | threshold                | Rising edge                 | 2.23                | 2.29 | 2.33 |      |  |

| V                                   | Brownout level 2         | Falling edge                | 2.44                | 2.50 | 2.56 | V    |  |

| V <sub>BOR2</sub>                   | threshold                | Rising edge                 | 2.53                | 2.59 | 2.63 | V    |  |

| M                                   | Brownout level 3         | Falling edge                | 2.75                | 2.83 | 2.88 |      |  |

| V <sub>BOR3</sub>                   | threshold                | Rising edge                 | 2.85                | 2.92 | 2.97 |      |  |

| V <sub>BORhyst</sub> <sup>(2)</sup> | BOR hysteresis           | -                           | -                   | 100  | -    | mV   |  |

| T <sub>RSTTEMPO</sub>               | POR reset timing         | -                           | 0.5                 | 1.5  | 3.0  | ms   |  |

|                 |                                 |                                            | Тур                        |                           | Ma                        | ax <sup>(1)</sup>         |                            |                            |      |

|-----------------|---------------------------------|--------------------------------------------|----------------------------|---------------------------|---------------------------|---------------------------|----------------------------|----------------------------|------|

| Symbol Paramete | Parameter                       | Conditions                                 | f <sub>HCLK</sub><br>(MHz) | Т <sub>А</sub> =<br>25 °С | Т <sub>А</sub> =<br>25 °С | Т <sub>А</sub> =<br>85 °С | Т <sub>А</sub> =<br>105 °С | Т <sub>А</sub> =<br>125 °С | Unit |

|                 |                                 |                                            | 100                        | 21.4                      | 23.0                      | 23.6                      | 24.0                       | 25.0                       |      |

|                 |                                 | External clock,                            | 84                         | 17.2                      | 18.9 <sup>(5)</sup>       | 19.1                      | 19.2                       | 20.2                       |      |

|                 |                                 | PLL ON <sup>(2)</sup> , all<br>peripherals | 64                         | 11.9                      | 12.9                      | 13.2                      | 13.7                       | 14.6                       |      |

|                 |                                 | enabled <sup>(3)(4)</sup>                  | 50                         | 9.4                       | 10.1                      | 10.4                      | 11.0                       | 11.9                       |      |

|                 |                                 |                                            | 20                         | 4.3                       | 4.8                       | 5.0                       | 5.6                        | 6.5                        |      |

|                 |                                 | HSI, PLL off, all                          | 16                         | 3.0                       | 3.3                       | 3.6                       | 4.3                        | 5.2                        |      |

| I               | Supply<br>current in <b>Run</b> | peripherals<br>enabled <sup>(4)</sup>      | 1                          | 0.5                       | 0.7                       | 1.0                       | 1.7                        | 2.6                        | mA   |

| I <sub>DD</sub> | mode                            |                                            | 100                        | 12.7                      | 14.0                      | 14.4                      | 14.8                       | 15.8                       | mA   |

|                 |                                 | External clock,                            | 84                         | 10.2                      | 11.6 <sup>(5)</sup>       | 11.8                      | 12.0                       | 13.0                       |      |

|                 |                                 | PLL on <sup>(2)</sup> )all<br>peripherals  | 64                         | 7.1                       | 7.9                       | 8.2                       | 8.7                        | 9.7                        |      |

|                 |                                 | disabled <sup>(3)</sup>                    | 50                         | 5.6                       | 6.3                       | 6.5                       | 7.1                        | 8.0                        |      |

|                 |                                 |                                            | 20                         | 2.5                       | 3.0                       | 3.3                       | 3.9                        | 4.8                        | ]    |

|                 |                                 | HSI, PLL off, all                          | 16                         | 1.9                       | 2.1                       | 2.4                       | 3.0                        | 3.9                        |      |

|                 |                                 | peripherals<br>disabled <sup>(4)</sup>     | 1                          | 0.4                       | 0.5                       | 0.9                       | 1.6                        | 2.5                        |      |

# Table 20. Typical and maximum current consumption, code with data processing (ART accelerator disabled) running from SRAM - V<sub>DD</sub> = 1.7 V

1. Guaranteed by characterization results.

2. Refer to Table 41 and RM0383 for the possible PLL VCO setting

3. When analog peripheral blocks such as ADC, HSE, LSE, HSI, or LSI are ON, an additional power consumption has to be considered.

4. When the ADC is ON (ADON bit set in the ADC\_CR2 register), add an additional power consumption of 1.6 mA for the analog part.

5. Guaranteed by test in production.

#### **On-chip peripheral current consumption**

The MCU is placed under the following conditions:

- At startup, all I/O pins are in analog input configuration.

- All peripherals are disabled unless otherwise mentioned.

- The ART accelerator is ON.

- Voltage Scale 2 mode selected, internal digital voltage V12 = 1.26 V.

- HCLK is the system clock at 84 MHz. f<sub>PCLK1</sub> = f<sub>HCLK</sub>/2, and f<sub>PCLK2</sub> = f<sub>HCLK</sub>.

The given value is calculated by measuring the difference of current consumption

- with all peripherals clocked off

- with only one peripheral clocked on

- Ambient operating temperature is 25 °C and V<sub>DD</sub>=3.3 V.

| Peripheral              |                     | I <sub>DD</sub> (Тур) | Unit   |

|-------------------------|---------------------|-----------------------|--------|

|                         | GPIOA               | 1.55                  |        |

|                         | GPIOB               | 1.55                  |        |

|                         | GPIOC               | 1.55                  |        |

| -                       | GPIOD               | 1.55                  |        |

| -                       | GPIOE               | 1.55                  |        |

| -                       | GPIOH               | 1.55                  |        |

|                         | CRC                 | 0.36                  |        |

| AHB1<br>(up to 100 MHz) | DMA1 <sup>(1)</sup> | 14.96                 | µA/MHz |

|                         | DMA1 <sup>(2)</sup> | 1.54N+2.66            |        |

|                         | DMA2 <sup>(1)</sup> | 14.96                 |        |

|                         | DMA2 <sup>(2)</sup> | 1.54N+2.66            |        |

|                         | TIM2                | 11.19                 |        |

|                         | TIM3                | 8.57                  |        |

| -                       | TIM4                | 8.33                  |        |

| -                       | TIM5                | 11.19                 |        |

| -                       | PWR                 | 0.71                  |        |

| APB1                    | USART2              | 3.33                  |        |

| (up to 50 MHz)          | I2C1/2/3            | 3.10                  | µA/MHz |

|                         | SPI2 <sup>(3)</sup> | 2.62                  |        |

|                         | SPI3 <sup>(3)</sup> | 2.86                  |        |

|                         | I2S2                | 1.90                  |        |

|                         | I2S3                | 1.67                  |        |

|                         | WWDG                | 0.71                  |        |

## Table 33. Peripheral current consumption

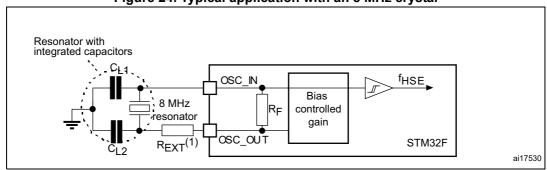

Figure 24. Typical application with an 8 MHz crystal

1. R<sub>EXT</sub> value depends on the crystal characteristics.

#### Low-speed external clock generated from a crystal/ceramic resonator

The low-speed external (LSE) clock can be supplied with a 32.768 kHz crystal/ceramic resonator oscillator. All the information given in this paragraph are based on characterization results obtained with typical external components specified in *Table 38*. In the application, the resonator and the load capacitors have to be placed as close as possible to the oscillator pins in order to minimize output distortion and startup stabilization time. Refer to the crystal resonator manufacturer for more details on the resonator characteristics (frequency, package, accuracy).

The LSE high-power mode allows to cover a wider range of possible crystals but with a cost of higher power consumption.

| Symbol                              | Parameter                                  | Conditions                  | Min | Тур  | Max  | Unit |  |

|-------------------------------------|--------------------------------------------|-----------------------------|-----|------|------|------|--|

| R <sub>F</sub>                      | Feedback resistor                          | -                           | -   | 18.4 | -    | MΩ   |  |

| I <sub>DD</sub>                     | LSE current                                | Low-power mode<br>(default) | -   | -    | 1    | μA   |  |

|                                     | consumption                                | High-drive mode             | -   | -    | 3    |      |  |

| C crit max                          | Maximum critical crystal<br>9 <sub>m</sub> | Startup, low-power mode     | -   | -    | 0.56 |      |  |

| G <sub>m</sub> _crit_max            |                                            | Startup, high-drive mode    | -   | -    | 1.50 | µA/V |  |

| t <sub>SU(LSE)</sub> <sup>(2)</sup> | startup time                               | $V_{DD}$ is stabilized      | -   | 2    | -    | s    |  |

Table 38. LSE oscillator characteristics (f<sub>LSE</sub> = 32.768 kHz) <sup>(1)</sup>

1. Guaranteed by design.

t<sub>SU(LSE)</sub> is the startup time measured from the moment it is enabled (by software) to a stabilized 32.768 kHz oscillation is reached. This value is guaranteed by characterization. It is measured for a standard crystal resonator and it can vary significantly with the crystal manufacturer.

Note:For information on selecting the crystal, refer to the application note AN2867 "Oscillator<br/>design guide for ST microcontrollers" available from the ST website www.st.com.For information about the LSE high-power mode, refer to the reference manual RM0383.

## 6.3.11 PLL spread spectrum clock generation (SSCG) characteristics

The spread spectrum clock generation (SSCG) feature allows to reduce electromagnetic interferences (see *Table 49: EMI characteristics for LQFP100*). It is available only on the main PLL.

| Symbol            | Parameter                              | Min  | Тур | Max <sup>(1)</sup> | Unit |

|-------------------|----------------------------------------|------|-----|--------------------|------|

| f <sub>Mod</sub>  | Modulation frequency                   | -    | -   | 10                 | kHz  |

| md                | Peak modulation depth                  | 0.25 | -   | 2                  | %    |

| MODEPER * INCSTEP | (Modulation period) * (Increment Step) | -    | -   | 2 <sup>15</sup> -1 | -    |

| Table 43 | SSCG | parameter | constraints |

|----------|------|-----------|-------------|

|          | 0000 | parameter | constraints |

1. Guaranteed by design.

#### Equation 1

The frequency modulation period (MODEPER) is given by the equation below:

$MODEPER = round[f_{PLL IN} / (4 \times f_{Mod})]$

$f_{\text{PLL}\ \text{IN}}$  and  $f_{\text{Mod}}$  must be expressed in Hz.

As an example:

If  $f_{PLL_IN} = 1$  MHz, and  $f_{MOD} = 1$  kHz, the modulation depth (MODEPER) is given by equation 1:

MODEPER = round  $[10^{6}/(4 \times 10^{3})] = 250$

#### **Equation 2**

Equation 2 allows to calculate the increment step (INCSTEP):

INCSTEP = round[

$$((2^{15} - 1) \times md \times PLLN)/(100 \times 5 \times MODEPER)$$

]

$f_{\text{VCO OUT}}$  must be expressed in MHz.

With a modulation depth (md) =  $\pm 2$  % (4 % peak to peak), and PLLN = 240 (in MHz):

INCSTEP = round[ $((2^{15}-1) \times 2 \times 240)/(100 \times 5 \times 250)$ ] = 126md(quantitazed)%

An amplitude quantization error may be generated because the linear modulation profile is obtained by taking the quantized values (rounded to the nearest integer) of MODPER and INCSTEP. As a result, the achieved modulation depth is quantized. The percentage quantized modulation depth is given by the following formula:

$$md_{quantized}$$

% = (MODEPER × INCSTEP × 100 × 5)/ ((2<sup>15</sup> - 1) × PLLN)

As a result:

$$md_{quantized}$$

% =  $(250 \times 126 \times 100 \times 5)/((2^{15} - 1) \times 240)$  = 2.002%(peak)

DocID026289 Rev 6

#### Static latchup

Two complementary static tests are required on six parts to assess the latchup performance:

- A supply overvoltage is applied to each power supply pin

- A current injection is applied to each input, output and configurable I/O pin

These tests are compliant with EIA/JESD 78A IC latchup standard.

| Table 51. I | Electrical | sensitivities |

|-------------|------------|---------------|

|-------------|------------|---------------|

| Symbol | Parameter             | Conditions                                     | Class      |

|--------|-----------------------|------------------------------------------------|------------|

| LU     | Static latch-up class | $T_A = + 125 \text{ °C conforming to JESD78A}$ | II level A |

### 6.3.15 I/O current injection characteristics

As a general rule, current injection to the I/O pins, due to external voltage below  $V_{SS}$  or above  $V_{DD}$  (for standard, 3 V-capable I/O pins) should be avoided during normal product operation. However, in order to give an indication of the robustness of the microcontroller in cases when abnormal injection accidentally happens, susceptibility tests are performed on a sample basis during device characterization.

#### Functional susceptibility to I/O current injection

While a simple application is executed on the device, the device is stressed by injecting current into the I/O pins programmed in floating input mode. While current is injected into the I/O pin, one at a time, the device is checked for functional failures.

The failure is indicated by an out of range parameter: ADC error above a certain limit (>5 LSB TUE), out of conventional limits of induced leakage current on adjacent pins (out of  $-5 \mu$ A/+0  $\mu$ A range), or other functional failure (for example reset, oscillator frequency deviation).

Negative induced leakage current is caused by negative injection and positive induced leakage current by positive injection.

The test results are given in Table 52.

|                  |                                                                                                                                                                    | Functional s       |                    |      |

|------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------|--------------------|------|

| Symbol           | Description                                                                                                                                                        | Negative injection | Positive injection | Unit |

|                  | Injected current on BOOT0 pin                                                                                                                                      | -0                 | NA                 |      |

|                  | Injected current on NRST pin                                                                                                                                       | -0                 | NA                 |      |

| I <sub>INJ</sub> | Injected current on PB3, PB4, PB5, PB6, PB7,<br>PB8, PB9, PC13, PC14, PC15, PH1, PDR_ON,<br>PC0, PC1,PC2, PC3, PD1, PD5, PD6, PD7, PE0,<br>PE2, PE3, PE4, PE5, PE6 | -0                 | NA                 | mA   |

|                  | Injected current on any other FT pin                                                                                                                               | -5                 | NA                 |      |

|                  | Injected current on any other pins                                                                                                                                 | -5                 | +5                 |      |

## Table 52. I/O current injection susceptibility<sup>(1)</sup>

1. NA = not applicable.

| Symbol                         | Parameter                                                             |                                               | Conditions        | Min | Тур | Мах | Unit |

|--------------------------------|-----------------------------------------------------------------------|-----------------------------------------------|-------------------|-----|-----|-----|------|

| R <sub>PU</sub>                | Weak pull-up<br>R <sub>PU</sub> equivalent<br>resistor <sup>(6)</sup> | All pins<br>except for<br>PA10<br>(OTG_FS_ID) | $V_{IN} = V_{SS}$ | 30  | 40  | 50  |      |

|                                | Tesistor                                                              | PA10<br>(OTG_FS_ID)                           | -                 | 7   | 10  | 14  | kΩ   |

| R <sub>PD</sub>                | Weak pull-down<br>equivalent<br>resistor <sup>(7)</sup>               | All pins<br>except for<br>PA10<br>(OTG_FS_ID) | $V_{IN} = V_{DD}$ | 30  | 40  | 50  | Ν22  |

| resistor                       | TESISION                                                              | PA10<br>(OTG_FS_ID)                           | -                 | 7   | 10  | 14  |      |

| C <sub>IO</sub> <sup>(8)</sup> | I/O pin capacitance                                                   |                                               | _                 | -   | 5   | -   | pF   |

Table 53. I/O static characteristics (continued)

1. Guaranteed by test in production.

2. Guaranteed by design.

3. With a minimum of 200 mV.

- 4. Leakage could be higher than the maximum value, if negative current is injected on adjacent pins, Refer to Table 52: I/O current injection susceptibility

- To sustain a voltage higher than VDD +0.3 V, the internal pull-up/pull-down resistors must be disabled. Leakage could be higher than the maximum value, if negative current is injected on adjacent pins.Refer to Table 52: I/O current injection susceptibility

- 6. Pull-up resistors are designed with a true resistance in series with a switchable PMOS. This PMOS contribution to the series resistance is minimum (~10% order).

- Pull-down resistors are designed with a true resistance in series with a switchable NMOS. This NMOS contribution to the series resistance is minimum (~10% order).

- 8. Hysteresis voltage between Schmitt trigger switching levels. Guaranteed by characterization results.

All I/Os are CMOS and TTL compliant (no software configuration required). Their characteristics cover more than the strict CMOS-technology or TTL parameters. The coverage of these requirements for FT and TC I/Os is shown in *Figure 30*.

| OSPEEDRy<br>[1:0] bit<br>value <sup>(1)</sup> | Symbol                  | Parameter                                                       | Conditions                                       | Min | Тур | Мах                | Unit |

|-----------------------------------------------|-------------------------|-----------------------------------------------------------------|--------------------------------------------------|-----|-----|--------------------|------|

|                                               |                         |                                                                 | C <sub>L</sub> = 30 pF, V <sub>DD</sub> ≥ 2.70 V | -   | -   | 100 <sup>(4)</sup> |      |

|                                               | F <sub>max(IO)out</sub> | Maximum frequency <sup>(3)</sup>                                | C <sub>L</sub> = 30 pF, V <sub>DD</sub> ≥ 1.7 V  | -   | -   | 50 <sup>(4)</sup>  | MHz  |

|                                               |                         |                                                                 | C <sub>L</sub> = 30 pF, V <sub>DD</sub> ≥ 2.70 V | -   | -   | 4                  |      |

| 11                                            | t <sub>f(IO)out</sub> / | Output high to low level fall time and output low to high       | C <sub>L</sub> = 30 pF, V <sub>DD</sub> ≥ 1.7 V  | -   | -   | 6                  | ns   |

|                                               | t <sub>r(IO)out</sub>   | level rise time                                                 | C <sub>L</sub> = 10 pF, V <sub>DD</sub> ≥ 2.70 V | -   | -   | 2.5                | 115  |

|                                               |                         |                                                                 | C <sub>L</sub> = 10 pF, V <sub>DD</sub> ≥ 1.7 V  | -   | -   | 4                  |      |

| -                                             | t <sub>EXTIpw</sub>     | Pulse width of external signals detected by the EXTI controller |                                                  | 10  | -   | -                  | ns   |

Table 55. I/O AC characteristics<sup>(1)(2)</sup> (continued)

1. Guaranteed by characterization results.

2. The I/O speed is configured using the OSPEEDRy[1:0] bits. Refer to the STM32F4xx reference manual for a description of the GPIOx\_SPEEDR GPIO port output speed register.

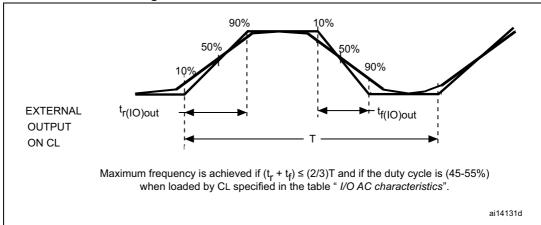

3. The maximum frequency is defined in *Figure 31*.

4. For maximum frequencies above 50 MHz and  $V_{DD}$  > 2.4 V, the compensation cell should be used.

#### Figure 31. I/O AC characteristics definition

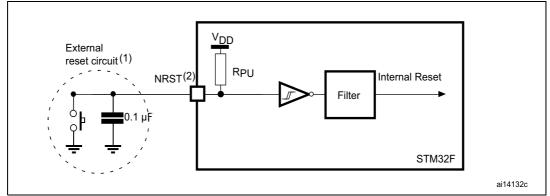

## 6.3.17 NRST pin characteristics

The NRST pin input driver uses CMOS technology. It is connected to a permanent pull-up resistor,  $R_{PU}$  (see *Table 53*).

Unless otherwise specified, the parameters given in *Table 56* are derived from tests performed under the ambient temperature and V<sub>DD</sub> supply voltage conditions summarized in *Table 14*. Refer to *Table 53: I/O static characteristics* for the values of VIH and VIL for NRST pin.

| Symbol                               | Parameter                                       | Conditions              | Min | Тур | Мах | Unit |

|--------------------------------------|-------------------------------------------------|-------------------------|-----|-----|-----|------|

| R <sub>PU</sub>                      | Weak pull-up equivalent resistor <sup>(1)</sup> | $V_{IN} = V_{SS}$       | 30  | 40  | 50  | kΩ   |

| V <sub>F(NRST)</sub> <sup>(2)</sup>  | NRST Input filtered pulse                       |                         | -   | -   | 100 | ns   |

| V <sub>NF(NRST)</sub> <sup>(2)</sup> | NRST Input not filtered pulse                   | V <sub>DD</sub> > 2.7 V | 300 | -   | -   | ns   |

| T <sub>NRST_OUT</sub>                |                                                 |                         | 20  | -   | -   | μs   |

1. The pull-up is designed with a true resistance in series with a switchable PMOS. This PMOS contribution to the series resistance must be minimum (~10% order).

2. Guaranteed by design.

#### Figure 32. Recommended NRST pin protection

1. The reset network protects the device against parasitic resets.

The user must ensure that the level on the NRST pin can go below the V<sub>IL(NRST)</sub> max level specified in Table 56. Otherwise the reset is not taken into account by the device.

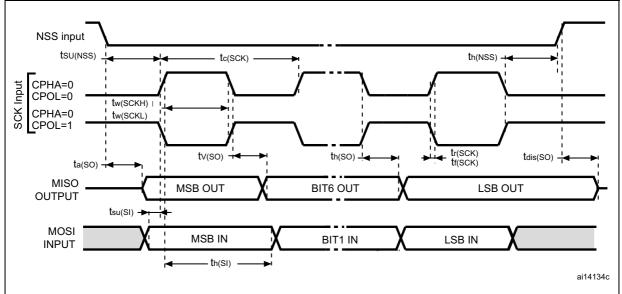

| Symbol               | Parameter                | Conditions                                                         | Min | Тур | Мах  | Unit |

|----------------------|--------------------------|--------------------------------------------------------------------|-----|-----|------|------|

| t <sub>a(SO</sub> )  | Data output access time  | Slave mode                                                         | 7   | -   | 21   | ns   |

| t <sub>dis(SO)</sub> | Data output disable time | Slave mode                                                         | 5   | -   | 12   | ns   |

| +                    | Data output valid time   | Slave mode (after enable edge),<br>2.7 V < $V_{DD}$ < 3.6 V        | -   | 11  | 13   | ns   |

| t <sub>v(SO)</sub>   |                          | Slave mode (after enable edge),<br>1.7 V < $V_{DD}$ < 3.6 V        | -   | 11  | 18.5 | ns   |

| t <sub>h(SO)</sub>   | Data output hold time    | Slave mode (after enable edge),<br>1.7 V < V <sub>DD</sub> < 3.6 V | 8   | -   | -    | ns   |

| t <sub>v(MO)</sub>   | Data output valid time   | Master mode (after enable edge)                                    | -   | 4   | 6    | ns   |

| t <sub>h(MO)</sub>   | Data output hold time    | Master mode (after enable edge)                                    | 0   | -   | -    | ns   |

| Table 60. SPI | dynamic | characteristics <sup>(1)</sup> | (continued) |

|---------------|---------|--------------------------------|-------------|

|---------------|---------|--------------------------------|-------------|

1. Guaranteed by characterization results.

2. Maximum frequency in Slave transmitter mode is determined by the sum of  $t_{v(SO)}$  and  $t_{su(MI)}$  which has to fit into SCK low or high phase preceding the SCK sampling edge. This value can be achieved when the SPI communicates with a master having  $t_{su(MI)} = 0$  while Duty(SCK) = 50%

#### **Electrical characteristics**

| Symbol                            | Parameter                                                                          | Conditions                                                                            | Min   | Тур | Max              | Unit               |

|-----------------------------------|------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------|-------|-----|------------------|--------------------|

| t <sub>lat</sub> (2)              | Injection trigger conversion                                                       | f <sub>ADC</sub> = 30 MHz                                                             | -     | -   | 0.100            | μs                 |

| 'lat` '                           | latency                                                                            |                                                                                       | -     | -   | 3 <sup>(5)</sup> | 1/f <sub>ADC</sub> |

| t <sub>latr</sub> (2)             | Regular trigger conversion                                                         | f <sub>ADC</sub> = 30 MHz                                                             | -     | -   | 0.067            | μs                 |

| 'latr'                            | latency                                                                            |                                                                                       | -     | -   | 2 <sup>(5)</sup> | 1/f <sub>ADC</sub> |

| t <sub>S</sub> <sup>(2)</sup>     | Sampling time                                                                      | f <sub>ADC</sub> = 30 MHz                                                             | 0.100 | -   | 16               | μs                 |

|                                   |                                                                                    |                                                                                       | 3     | -   | 480              | 1/f <sub>ADC</sub> |

| t <sub>STAB</sub> <sup>(2)</sup>  | Power-up time                                                                      |                                                                                       | -     | 2   | 3                | μs                 |

|                                   |                                                                                    | f <sub>ADC</sub> = 30 MHz<br>12-bit resolution                                        | 0.50  | -   | 16.40            | μs                 |

|                                   |                                                                                    | f <sub>ADC</sub> = 30 MHz<br>10-bit resolution                                        | 0.43  | -   | 16.34            | μs                 |

| t <sub>CONV</sub> <sup>(2)</sup>  | t <sub>CONV</sub> <sup>(2)</sup> Total conversion time (including sampling time)   | f <sub>ADC</sub> = 30 MHz<br>8-bit resolution                                         | 0.37  | -   | 16.27            | μs                 |

|                                   |                                                                                    | f <sub>ADC</sub> = 30 MHz<br>6-bit resolution                                         | 0.30  | -   | 16.20            | μs                 |

|                                   |                                                                                    | 9 to 492 (t <sub>S</sub> for sampling +n-bit resolution for successive approximation) |       |     |                  | 1/f <sub>ADC</sub> |

|                                   |                                                                                    | 12-bit resolution<br>Single ADC                                                       | -     | -   | 2                | Msps               |

| f <sub>S</sub> <sup>(2)</sup>     | Sampling rate<br>(f <sub>ADC</sub> = 30 MHz, and<br>t <sub>S</sub> = 3 ADC cycles) | 12-bit resolution<br>Interleave Dual ADC<br>mode                                      | -     | -   | 3.75             | Msps               |

|                                   |                                                                                    | 12-bit resolution<br>Interleave Triple ADC<br>mode                                    | -     | -   | 6                | Msps               |

| I <sub>VREF+</sub> <sup>(2)</sup> | ADC V <sub>REF</sub> DC current<br>consumption in conversion<br>mode               |                                                                                       | -     | 300 | 500              | μA                 |

| I <sub>VDDA</sub> <sup>(2)</sup>  | ADC V <sub>DDA</sub> DC current<br>consumption in conversion<br>mode               |                                                                                       | -     | 1.6 | 1.8              | mA                 |

#### Table 65. ADC characteristics (continued)

1. V<sub>DDA</sub> minimum value of 1.7 V is possible with the use of an external power supply supervisor (refer to Section 3.15.2: Internal reset OFF).

2. Guaranteed by characterization results.

3.  $V_{REF+}$  is internally connected to  $V_{DDA}$  and  $V_{REF-}$  is internally connected to  $V_{SSA}$ .

4.  $R_{ADC}$  maximum value is given for V<sub>DD</sub>=1.7 V, and minimum value for V<sub>DD</sub>=3.3 V.

5. For external triggers, a delay of  $1/f_{PCLK2}$  must be added to the latency specified in *Table 65*.

DocID026289 Rev 6

## 6.3.22 V<sub>BAT</sub> monitoring characteristics

| Symbol                                | Parameter                                                            |    | Тур | Max | Unit |

|---------------------------------------|----------------------------------------------------------------------|----|-----|-----|------|

| R                                     | Resistor bridge for V <sub>BAT</sub>                                 |    | 50  | -   | KΩ   |

| Q                                     | Ratio on V <sub>BAT</sub> measurement                                | -  | 4   | -   |      |

| Er <sup>(1)</sup>                     | Error on Q                                                           | -1 | -   | +1  | %    |

| T <sub>S_vbat</sub> <sup>(2)(2)</sup> | ADC sampling time when reading the V <sub>BAT</sub><br>1 mV accuracy |    | -   | -   | μs   |

Table 73. V<sub>BAT</sub> monitoring characteristics

1. Guaranteed by design.

2. Shortest sampling time can be determined in the application by multiple iterations.

## 6.3.23 Embedded reference voltage

The parameters given in *Table 74* are derived from tests performed under ambient temperature and  $V_{DD}$  supply voltage conditions summarized in *Table 14*.

| Symbol                                | Parameter                                                        | Conditions                          | Min  | Тур  | Max  | Unit   |

|---------------------------------------|------------------------------------------------------------------|-------------------------------------|------|------|------|--------|

| V <sub>REFINT</sub>                   | Internal reference voltage                                       | - 40 °C < T <sub>A</sub> < + 125 °C | 1.18 | 1.21 | 1.24 | V      |

| T <sub>S_vrefint</sub> <sup>(1)</sup> | ADC sampling time when reading the<br>internal reference voltage | -                                   | 10   | -    | -    | μs     |

| V <sub>RERINT_s</sub> <sup>(2)</sup>  | Internal reference voltage spread over the temperature range     | $V_{DD}$ = 3V $\pm$ 10mV            | -    | 3    | 5    | mV     |

| T <sub>Coeff</sub> <sup>(2)</sup>     | Temperature coefficient                                          | -                                   | -    | 30   | 50   | ppm/°C |

| t <sub>START</sub> <sup>(2)</sup>     | Startup time                                                     | -                                   | -    | 6    | 10   | μs     |

#### Table 74. Embedded internal reference voltage

1. Shortest sampling time can be determined in the application by multiple iterations.

2. Guaranteed by design.

#### Table 75. Internal reference voltage calibration values

| Symbol                 | Parameter                                                          | Memory address            |

|------------------------|--------------------------------------------------------------------|---------------------------|

| V <sub>REFIN_CAL</sub> | Raw data acquired at temperature of 30 °C V <sub>DDA</sub> = 3.3 V | 0x1FFF 7A2A - 0x1FFF 7A2B |

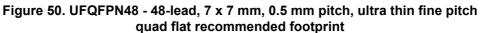

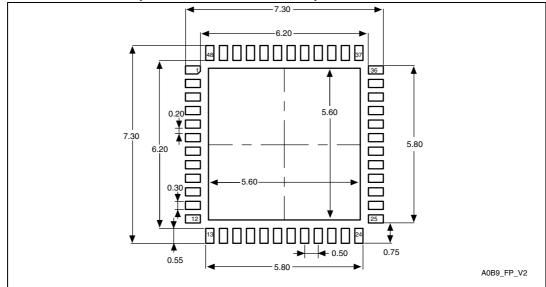

# Table 81. UFQFPN48 - 48-lead, 7 x 7 mm, 0.5 mm pitch, ultra thin fine pitchquad flat package mechanical data (continued)

|        | quad nat puckage moonanoar data (commood) |             |       |        |                       |        |  |

|--------|-------------------------------------------|-------------|-------|--------|-----------------------|--------|--|

| Cumhal |                                           | millimeters |       |        | inches <sup>(1)</sup> |        |  |

| Symbol | Min.                                      | Тур.        | Max.  | Min.   | Тур.                  | Max.   |  |

| E2     | 5.500                                     | 5.600       | 5.700 | 0.2165 | 0.2205                | 0.2244 |  |

| L      | 0.300                                     | 0.400       | 0.500 | 0.0118 | 0.0157                | 0.0197 |  |

| Т      | -                                         | 0.152       | -     | -      | 0.0060                | -      |  |

| b      | 0.200                                     | 0.250       | 0.300 | 0.0079 | 0.0098                | 0.0118 |  |

| е      | -                                         | 0.500       | -     | -      | 0.0197                | -      |  |

| ddd    | -                                         | -           | 0.080 | -      | -                     | 0.0031 |  |

1. Values in inches are converted from mm and rounded to 4 decimal digits.

1. Dimensions are in millimeters.

# 8 Part numbering

## Table 86. Ordering information scheme

| Example:                                                   | STM32 F 411 C E Y 6 TR |

|------------------------------------------------------------|------------------------|

| Device family                                              |                        |

| STM32 = ARM <sup>®</sup> -based 32-bit microcontroller     |                        |

| Product type                                               |                        |

| F = General-purpose                                        |                        |

| Device subfamily                                           |                        |

| 411 = 411 family                                           |                        |

| Pin count                                                  |                        |

| C = 48/49 pins                                             |                        |

| R = 64 pins                                                |                        |

| V = 100 pins                                               |                        |

| Flash memory size                                          |                        |

| C = 256 Kbytes of Flash memory                             |                        |

| E = 512 Kbytes of Flash memory                             |                        |

| Package                                                    |                        |

| H = UFBGA                                                  |                        |

| T = LQFP                                                   |                        |

| U = UFQFPN                                                 |                        |

| Y = WLCSP                                                  |                        |

| Temperature range                                          |                        |

| 6 = Industrial temperature range, - 40 to 85 °C            |                        |

| 7 = Industrial temperature range, - 40 to 105 $^{\circ}$ C |                        |

| 3 = Industrial temperature range, - 40 to 125 °C           |                        |

| Packing                                                    |                        |

| TR = tane and reel                                         |                        |

TR = tape and reel

No character = tray or tube

## Appendix B Application block diagrams

## B.1 USB OTG Full Speed (FS) interface solutions

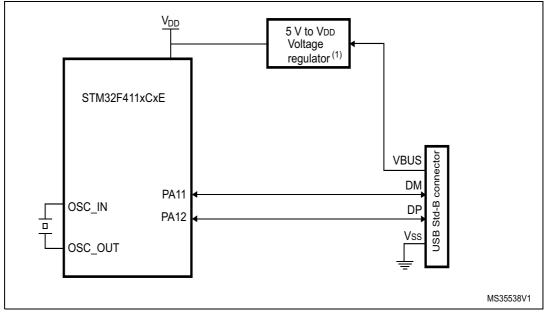

Figure 61. USB controller configured as peripheral-only and used in Full-Speed mode

1. The external voltage regulator is only needed when building a  $\mathrm{V}_{\mathrm{BUS}}$  powered device.

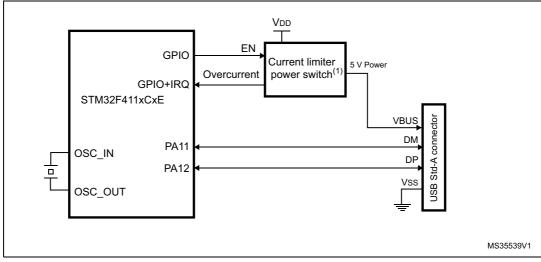

#### Figure 62. USB controller configured as host-only and used in Full-Speed mode

1. The current limiter is required only if the application has to support a  $V_{BUS}$  powered device. A basic power switch can be used if 5V are available on the application board.

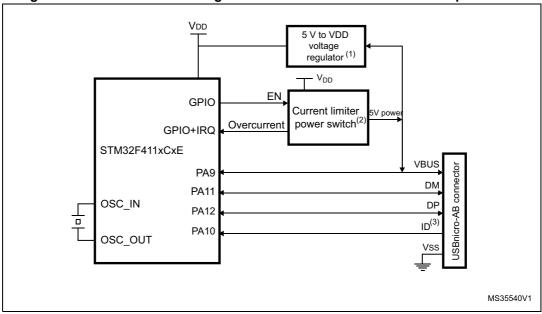

Figure 63. USB controller configured in dual mode and used in Full-Speed mode

- 1. The external voltage regulator is only needed when building a  $\mathrm{V}_{\mathrm{BUS}}$  powered device.

- The current limiter is required only if the application has to support a V<sub>BUS</sub> powered device. A basic power switch can be used if 5 V are available on the application board.

- 3. The ID pin is required in dual role only.

#### IMPORTANT NOTICE - PLEASE READ CAREFULLY

STMicroelectronics NV and its subsidiaries ("ST") reserve the right to make changes, corrections, enhancements, modifications, and improvements to ST products and/or to this document at any time without notice. Purchasers should obtain the latest relevant information on ST products before placing orders. ST products are sold pursuant to ST's terms and conditions of sale in place at the time of order acknowledgement.

Purchasers are solely responsible for the choice, selection, and use of ST products and ST assumes no liability for application assistance or the design of Purchasers' products.

No license, express or implied, to any intellectual property right is granted by ST herein.

Resale of ST products with provisions different from the information set forth herein shall void any warranty granted by ST for such product.

ST and the ST logo are trademarks of ST. All other product or service names are the property of their respective owners.

Information in this document supersedes and replaces information previously supplied in any prior versions of this document.

© 2016 STMicroelectronics – All rights reserved

DocID026289 Rev 6