Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

#### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Product Status             | Active                                                                |

|----------------------------|-----------------------------------------------------------------------|

| Core Processor             | ARM® Cortex®-M4                                                       |

| Core Size                  | 32-Bit Single-Core                                                    |

| Speed                      | 100MHz                                                                |

| Connectivity               | I <sup>2</sup> C, IrDA, LINbus, MMC/SD/SDIO, SPI, UART/USART, USB OTG |

| Peripherals                | Brown-out Detect/Reset, DMA, I <sup>2</sup> S, POR, PWM, WDT          |

| Number of I/O              | 50                                                                    |

| Program Memory Size        | 256KB (256K x 8)                                                      |

| Program Memory Type        | FLASH                                                                 |

| EEPROM Size                | -                                                                     |

| RAM Size                   | 128K x 8                                                              |

| Voltage - Supply (Vcc/Vdd) | 1.7V ~ 3.6V                                                           |

| Data Converters            | A/D 16x12b                                                            |

| Oscillator Type            | Internal                                                              |

| Operating Temperature      | -40°C ~ 105°C (TA)                                                    |

| Mounting Type              | Surface Mount                                                         |

| Package / Case             | 64-LQFP                                                               |

| Supplier Device Package    | 64-LQFP (10x10)                                                       |

| Purchase URL               | https://www.e-xfl.com/product-detail/stmicroelectronics/stm32f411rct7 |

|                            |                                                                       |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

7

8

|          |      | 6.3.5    | Embedded reset and power control block characteristics      | 66       |

|----------|------|----------|-------------------------------------------------------------|----------|

|          |      | 6.3.6    | Supply current characteristics                              | 67       |

|          |      | 6.3.7    | Wakeup time from low-power modes                            | 81       |

|          |      | 6.3.8    | External clock source characteristics                       | 82       |

|          |      | 6.3.9    | Internal clock source characteristics                       | 86       |

|          |      | 6.3.10   | PLL characteristics                                         | 88       |

|          |      | 6.3.11   | PLL spread spectrum clock generation (SSCG) characteristics | 90       |

|          |      | 6.3.12   | Memory characteristics                                      | 91       |

|          |      | 6.3.13   | EMC characteristics                                         | 93       |

|          |      | 6.3.14   | Absolute maximum ratings (electrical sensitivity)           | 95       |

|          |      | 6.3.15   | I/O current injection characteristics                       | 96       |

|          |      | 6.3.16   | I/O port characteristics                                    | 97       |

|          |      | 6.3.17   | NRST pin characteristics                                    | 103      |

|          |      | 6.3.18   | TIM timer characteristics                                   | 104      |

|          |      | 6.3.19   | Communications interfaces                                   | 104      |

|          |      | 6.3.20   | 12-bit ADC characteristics                                  | 113      |

|          |      | 6.3.21   | Temperature sensor characteristics                          | 119      |

|          |      | 6.3.22   | V <sub>BAT</sub> monitoring characteristics                 | 120      |

|          |      | 6.3.23   | Embedded reference voltage                                  | 120      |

|          |      | 6.3.24   | SD/SDIO MMC/eMMC card host interface (SDIO) characteristics | 121      |

|          |      | 6.3.25   | RTC characteristics                                         | 123      |

| 7        | Pack | age info | ormation                                                    | 124      |

|          | 7.1  | -        | P49 package information                                     |          |

|          | 7.2  |          | N48 package information                                     |          |

|          | 7.3  |          | 4 package information                                       |          |

|          |      |          |                                                             |          |

|          | 7.4  |          | 00 package information                                      |          |

|          | 7.5  | UFBGA    | 100 package information                                     | 137      |

|          | 7.6  | Therma   | al characteristics                                          | 140      |

|          |      | 7.6.1    | Reference document                                          | 140      |

| 8        | Part | number   | ing                                                         | 141      |

| Appendix | A R  | lecomm   | endations when using the internal reset OFF                 | 142      |

|          | A.1  | Operati  | ng conditions                                               | 142      |

| Appendix | B A  | pplicati | on block diagrams                                           | 143      |

|          |      |          |                                                             | <b>—</b> |

| 4/149    |      |          | DocID026289 Rev 6                                           | <b>\</b> |

|            | chip scale package outline                                                | 124 |

|------------|---------------------------------------------------------------------------|-----|

| Figure 47. | WLCSP49 - 49-ball, 2.999 x 3.185 mm, 0.4 mm pitch wafer level chip scale  |     |

|            | recommended footprint                                                     | 125 |

| Figure 48. | WLCSP49 marking (package top view)                                        | 126 |

| Figure 49. | UFQFPN48 - 48-lead, 7 x 7 mm, 0.5 mm pitch, ultra thin fine pitch         |     |

|            | quad flat package outline                                                 | 127 |

| Figure 50. | UFQFPN48 - 48-lead, 7 x 7 mm, 0.5 mm pitch, ultra thin fine pitch         |     |

|            | quad flat recommended footprint                                           | 128 |

| Figure 51. | UFQFPN48 marking example (package top view)                               | 129 |

| Figure 52. | LQFP64 - 64-pin, 10 x 10 mm, 64-pin low-profile quad flat package outline | 130 |

| Figure 53. | LQFP64 recommended footprint                                              | 131 |

| Figure 54. | LQFP64 marking example (package top view)                                 | 132 |

| Figure 55. | LQFP100 - 100-pin, 14 x 14 mm, 100-pin low-profile quad flat              |     |

|            | package outline                                                           | 133 |

| Figure 56. | LQFP100 - 100-pin, 14 x 14 mm, 100-pin low-profile quad flat              |     |

|            | recommended footprint                                                     | 135 |

| Figure 57. | LQPF100 marking example (package top view)                                | 136 |

| Figure 58. | UFBGA100 - 100-ball, 7 x 7 mm, 0.50 mm pitch, ultra fine pitch            |     |

|            | ball grid array package outline                                           | 137 |

| Figure 59. | Recommended PCB design rules for pads (0.5 mm-pitch BGA)                  | 138 |

| Figure 60. | UFBGA100 marking example (package top view)                               | 139 |

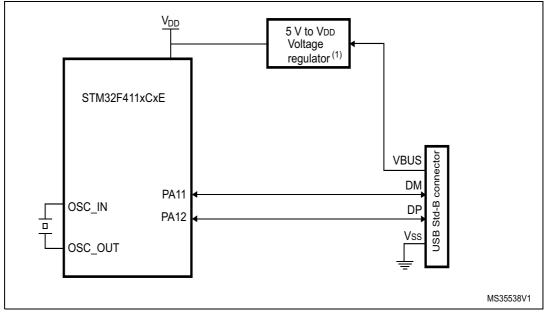

| Figure 61. | USB controller configured as peripheral-only and used in Full-Speed mode  | 143 |

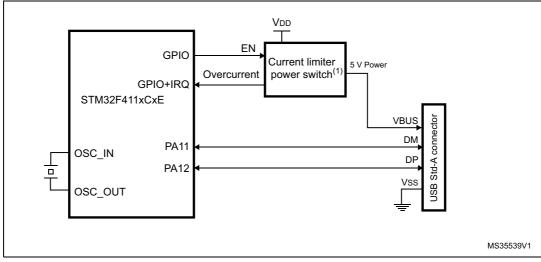

| Figure 62. | USB controller configured as host-only and used in Full-Speed mode        | 143 |

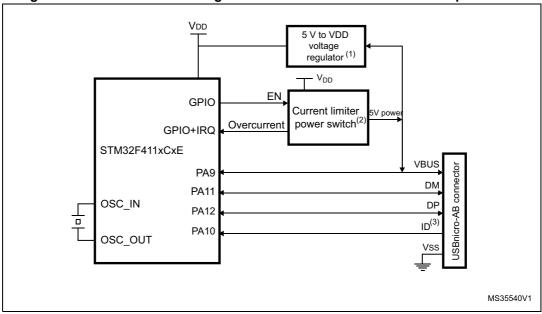

| Figure 63. | USB controller configured in dual mode and used in Full-Speed mode        | 144 |

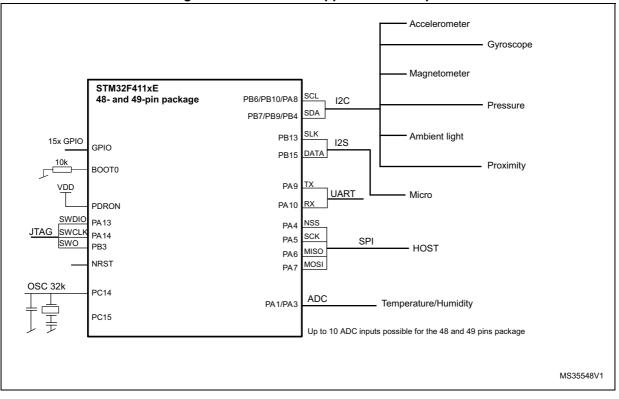

| Figure 64. | Sensor Hub application example                                            | 145 |

| Figure 65. | Batch Acquisition Mode (BAM) example                                      | 146 |

# 2 Description

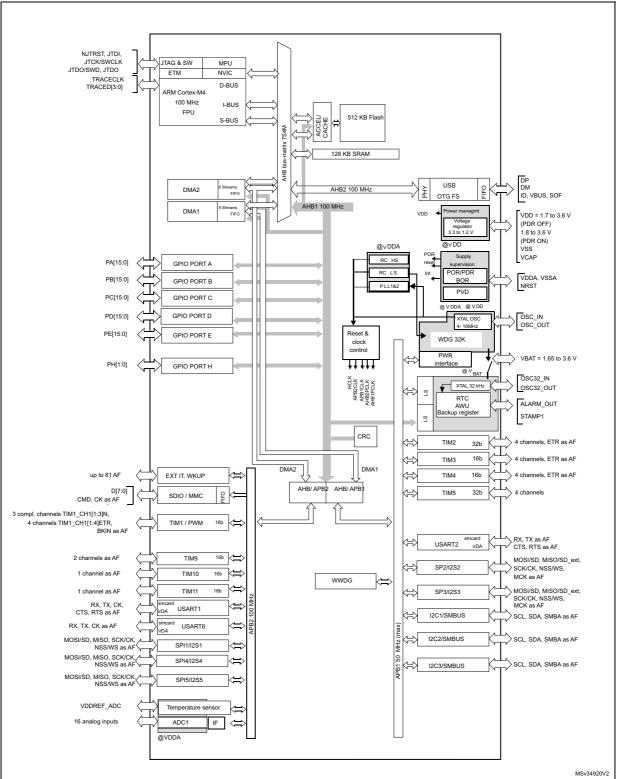

The STM32F411xC/xE devices are based on the high-performance ARM<sup>®</sup> Cortex<sup>®</sup> -M4 32bit RISC core operating at a frequency of up to 100 MHz. The Cortex<sup>®</sup>-M4 core features a Floating point unit (FPU) single precision which supports all ARM single-precision dataprocessing instructions and data types. It also implements a full set of DSP instructions and a memory protection unit (MPU) which enhances application security.

The STM32F411xC/xE belongs to the STM32 Dynamic Efficiency<sup>™</sup> product line (with products combining power efficiency, performance and integration) while adding a new innovative feature called Batch Acquisition Mode (BAM) allowing to save even more power consumption during data batching.

The STM32F411xC/xE incorporate high-speed embedded memories (up to 512 Kbytes of Flash memory, 128 Kbytes of SRAM), and an extensive range of enhanced I/Os and peripherals connected to two APB buses, two AHB bus and a 32-bit multi-AHB bus matrix.

All devices offer one 12-bit ADC, a low-power RTC, six general-purpose 16-bit timers including one PWM timer for motor control, two general-purpose 32-bit timers. They also feature standard and advanced communication interfaces.

- Up to three I<sup>2</sup>Cs

- Five SPIs

- Five I<sup>2</sup>Ss out of which two are full duplex. To achieve audio class accuracy, the I<sup>2</sup>S peripherals can be clocked via a dedicated internal audio PLL or via an external clock to allow synchronization.

- Three USARTs

- SDIO interface

- USB 2.0 OTG full speed interface

Refer to *Table 2: STM32F411xC/xE features and peripheral counts* for the peripherals available for each part number.

The STM32F411xC/xE operate in the - 40 to + 125 °C temperature range from a 1.7 (PDR OFF) to 3.6 V power supply. A comprehensive set of power-saving mode allows the design of low-power applications.

These features make the STM32F411xC/xE microcontrollers suitable for a wide range of applications:

- Motor drive and application control

- Medical equipment

- Industrial applications: PLC, inverters, circuit breakers

- Printers, and scanners

- Alarm systems, video intercom, and HVAC

- Home audio appliances

- Mobile phone sensor hub

Figure 3 shows the general block diagram of the devices.

#### STM32F411xC STM32F411xE

#### Figure 3. STM32F411xC/xE block diagram

1. The timers connected to APB2 are clocked from TIMxCLK up to 100 MHz, while the timers connected to APB1 are clocked from TIMxCLK up to 100 MHz.

DocID026289 Rev 6

### 3.16.3 Regulator ON/OFF and internal power supply supervisor availability

| Package  | Regulator ON                    | Regulator OFF                   | Power supply supervisor ON | Power supply supervisor OFF                      |

|----------|---------------------------------|---------------------------------|----------------------------|--------------------------------------------------|

| UFQFPN48 | Yes                             | No                              | Yes                        | No                                               |

| WLCSP49  | Yes                             | No                              | Yes<br>PDR_ON set to VDD   | Yes<br>PDR_ON external<br>control <sup>(1)</sup> |

| LQFP64   | Yes                             | No                              | Yes                        | No                                               |

| LQFP100  | Yes                             | No                              | Yes                        | No                                               |

| UFBGA100 | Yes<br>BYPASS_REG set to<br>VSS | Yes<br>BYPASS_REG set to<br>VDD | Yes<br>PDR_ON set to VDD   | Yes<br>PDR_ON external<br>control <sup>(1)</sup> |

Table 3. Regulator ON/OFF and internal power supply supervisor availability

1. Refer to Section 3.15: Power supply supervisor

# 3.17 Real-time clock (RTC) and backup registers

The backup domain includes:

- The real-time clock (RTC)

- 20 backup registers

The real-time clock (RTC) is an independent BCD timer/counter. Dedicated registers contain the second, minute, hour (in 12/24 hour), week day, date, month, year, in BCD (binary-coded decimal) format. Correction for 28, 29 (leap year), 30, and 31 day of the month are performed automatically. The RTC features a reference clock detection, a more precise second source clock (50 or 60 Hz) can be used to enhance the calendar precision. The RTC provides a programmable alarm and programmable periodic interrupts with wakeup from Stop and Standby modes. The sub-seconds value is also available in binary format.

It is clocked by a 32.768 kHz external crystal, resonator or oscillator, the internal low-power RC oscillator or the high-speed external clock divided by 128. The internal low-speed RC has a typical frequency of 32 kHz. The RTC can be calibrated using an external 512 Hz output to compensate for any natural quartz deviation.

Two alarm registers are used to generate an alarm at a specific time and calendar fields can be independently masked for alarm comparison. To generate a periodic interrupt, a 16-bit programmable binary auto-reload downcounter with programmable resolution is available and allows automatic wakeup and periodic alarms from every 120 µs to every 36 hours.

A 20-bit prescaler is used for the time base clock. It is by default configured to generate a time base of 1 second from a clock at 32.768 kHz.

The backup registers are 32-bit registers used to store 80 bytes of user application data when  $V_{DD}$  power is not present. Backup registers are not reset by a system, a power reset, or when the device wakes up from the Standby mode (see Section 3.18: Low-power modes).

Additional 32-bit registers contain the programmable alarm subseconds, seconds, minutes, hours, day, and date.

DocID026289 Rev 6

In addition to the audio PLL, a master clock input pin can be used to synchronize the I2S flow with an external PLL (or Codec output).

## 3.26 Secure digital input/output interface (SDIO)

An SD/SDIO/MMC/eMMC host interface is available, that supports MultiMediaCard System Specification Version 4.2 in three different databus modes: 1-bit (default), 4-bit and 8-bit.

The interface allows data transfer at up to 50 MHz, and is compliant with the SD Memory Card Specification Version 2.0.

The SDIO Card Specification Version 2.0 is also supported with two different databus modes: 1-bit (default) and 4-bit.

The current version supports only one SD/SDIO/MMC4.2 card at any one time and a stack of MMC4.1 or previous.

In addition to SD/SDIO/MMC/eMMC, this interface is fully compliant with the CE-ATA digital protocol Rev1.1.

## 3.27 Universal serial bus on-the-go full-speed (OTG\_FS)

The devices embed an USB OTG full-speed device/host/OTG peripheral with integrated transceivers. The USB OTG FS peripheral is compliant with the USB 2.0 specification and with the OTG 1.0 specification. It has software-configurable endpoint setting and supports suspend/resume. The USB OTG full-speed controller requires a dedicated 48 MHz clock that is generated by a PLL connected to the HSE oscillator. The major features are:

- Combined Rx and Tx FIFO size of 320 × 35 bits with dynamic FIFO sizing

- Supports the session request protocol (SRP) and host negotiation protocol (HNP)

- 4 bidirectional endpoints

- 8 host channels with periodic OUT support

- HNP/SNP/IP inside (no need for any external resistor)

- For OTG/Host modes, a power switch is needed in case bus-powered devices are connected

## 3.28 General-purpose input/outputs (GPIOs)

Each of the GPIO pins can be configured by software as output (push-pull or open-drain, with or without pull-up or pull-down), as input (floating, with or without pull-up or pull-down) or as peripheral alternate function. Most of the GPIO pins are shared with digital or analog alternate functions. All GPIOs are high-current-capable and have speed selection to better manage internal noise, power consumption and electromagnetic emission.

The I/O configuration can be locked if needed by following a specific sequence in order to avoid spurious writing to the I/Os registers.

Fast I/O handling allowing maximum I/O toggling up to 100 MHz.

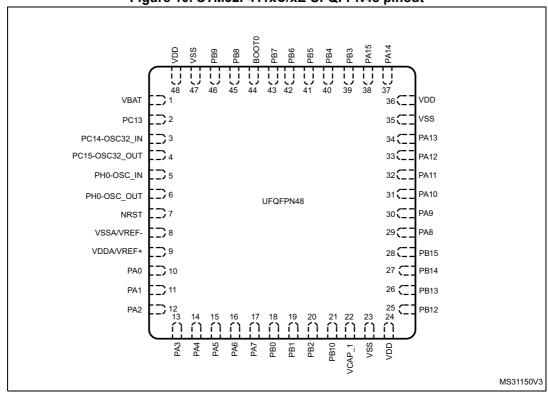

Figure 10. STM32F411xC/xE UFQFPN48 pinout

1. The above figure shows the package top view.

|          | Pir    | n numt  | ber     |          |                                                      |          |               |       |                                                                             |                      |

|----------|--------|---------|---------|----------|------------------------------------------------------|----------|---------------|-------|-----------------------------------------------------------------------------|----------------------|

| UFQFPN48 | LQFP64 | WLCSP49 | LQFP100 | UFBGA100 | Pin name<br>(function after<br>reset) <sup>(1)</sup> | Pin type | I/O structure | Notes | Alternate functions                                                         | Additional functions |

| 10       | 14     | F6      | 23      | L2       | PA0-WKUP                                             | I/O      | тс            | (5)   | TIM2_CH1/TIM2_ET,<br>TIM5_CH1,<br>USART2_CTS,<br>EVENTOUT                   | ADC1_0, WKUP1        |

| 11       | 15     | G7      | 24      | M2       | PA1                                                  | I/O      | FT            | -     | TIM2_CH2,<br>TIM5_CH2,<br>SPI4_MOSI/I2S4_SD,<br>USART2_RTS,<br>EVENTOUT     | ADC1_1               |

| 12       | 16     | E5      | 25      | K3       | PA2                                                  | I/O      | FT            | -     | TIM2_CH3,<br>TIM5_CH3,<br>TIM9_CH1,<br>I2S2_CKIN,<br>USART2_TX,<br>EVENTOUT | ADC1_2               |

| 13       | 17     | E4      | 26      | L3       | PA3                                                  | I/O      | FT            | -     | TIM2_CH4,<br>TIM5_CH4,<br>TIM9_CH2,<br>I2S2_MCK,<br>USART2_RX,<br>EVENTOUT  | ADC1_3               |

| -        | 18     | -       | 27      | -        | VSS                                                  | S        | -             | -     | -                                                                           | -                    |

| -        | -      | -       | -       | E3       | BYPASS_REG                                           | S        | -             | -     | -                                                                           | -                    |

| -        | 19     | 1       | 28      | -        | VDD                                                  | Ι        | FT            | I     | EVENTOUT                                                                    | -                    |

| 14       | 20     | G6      | 29      | М3       | PA4                                                  | I/O      | FT            | -     | SPI1_NSS/I2S1_WS,<br>SPI3_NSS/I2S3_WS,<br>USART2_CK,<br>EVENTOUT            | ADC1_4               |

| 15       | 21     | F5      | 30      | K4       | PA5                                                  | I/O      | FT            | -     | TIM2_CH1/TIM2_ET,<br>SPI1_SCK/I2S1_CK,<br>EVENTOUT                          | ADC1_5               |

| 16       | 22     | F4      | 31      | L4       | PA6                                                  | I/O      | FT            | -     | TIM1_BKIN,<br>TIM3_CH1,<br>SPI1_MISO,<br>I2S2_MCK,<br>SDIO_CMD,<br>EVENTOUT | ADC1_6               |

| 17       | 23     | F3      | 32      | M4       | PA7                                                  | I/O      | FT            | -     | TIM1_CH1N,<br>TIM3_CH2,<br>SPI1_MOSI/I2S1_SD,<br>EVENTOUT                   | ADC1_7               |

Table 8. STM32F411xC/xE pin definitions (continued)

|          | Pir    | n numt  | ber     |          |                                                      |          |               |       |                                                                   |                      |

|----------|--------|---------|---------|----------|------------------------------------------------------|----------|---------------|-------|-------------------------------------------------------------------|----------------------|

| UFQFPN48 | LQFP64 | WLCSP49 | LQFP100 | UFBGA100 | Pin name<br>(function after<br>reset) <sup>(1)</sup> | Pin type | I/O structure | Notes | Alternate functions                                               | Additional functions |

| -        | 24     | -       | 33      | K5       | PC4                                                  | I/O      | FT            | -     | EVENTOUT                                                          | ADC1_14              |

| -        | 25     | -       | 34      | L5       | PC5                                                  | I/O      | FT            | I     | EVENTOUT                                                          | ADC1_15              |

| 18       | 26     | G5      | 35      | M5       | PB0                                                  | I/O      | FT            | -     | TIM1_CH2N,<br>TIM3_CH3,<br>SPI5_SCK/I2S5_CK,<br>EVENTOUT          | ADC1_8               |

| 19       | 27     | G4      | 36      | M6       | PB1                                                  | I/O      | FT            | -     | TIM1_CH3N,<br>TIM3_CH4,<br>SPI5_NSS/I2S5_WS,<br>EVENTOUT          | ADC1_9               |

| 20       | 28     | G3      | 37      | L6       | PB2                                                  | I/O      | FT            | -     | EVENTOUT                                                          | BOOT1                |

| -        | -      | -       | 38      | M7       | PE7                                                  | I/O      | FT            | -     | TIM1_ETR,<br>EVENTOUT                                             | -                    |

| -        | -      | -       | 39      | L7       | PE8                                                  | I/O      | FT            | -     | TIM1_CH1N,<br>EVENTOUT                                            | -                    |

| -        | -      | -       | 40      | M8       | PE9                                                  | I/O      | FT            | -     | TIM1_CH1,<br>EVENTOUT                                             | -                    |

| -        | -      | -       | 41      | L8       | PE10                                                 | I/O      | FT            | -     | TIM1_CH2N,<br>EVENTOUT                                            | -                    |

| -        | -      | -       | 42      | M9       | PE11                                                 | I/O      | FT            | -     | TIM1_CH2,<br>SPI4_NSS/I2S4_WS,<br>SPI5_NSS/I2S5_WS,<br>EVENTOUT   | -                    |

| -        | -      | -       | 43      | L9       | PE12                                                 | I/O      | FT            | -     | TIM1_CH3N,<br>SPI4_SCK/I2S4_CK,<br>SPI5_SCK/I2S5_CK,<br>EVENTOUT  | -                    |

| -        | -      | -       | 44      | M10      | PE13                                                 | I/O      | FT            | -     | TIM1_CH3,<br>SPI4_MISO,<br>SPI5_MISO,<br>EVENTOUT                 | -                    |

| -        | -      | -       | 45      | M11      | PE14                                                 | I/O      | FT            | -     | TIM1_CH4,<br>SPI4_MOSI/I2S4_SD,<br>SPI5_MOSI/I2S5_SD,<br>EVENTOUT | -                    |

| -        | -      | -       | 46      | M12      | PE15                                                 | I/O      | FT            | -     | TIM1_BKIN,<br>EVENTOUT                                            | -                    |

Table 8. STM32F411xC/xE pin definitions (continued)

|          | Pir    | n numl  | ber     |          |                                                      |          |               |       |                                                                                              |                      |

|----------|--------|---------|---------|----------|------------------------------------------------------|----------|---------------|-------|----------------------------------------------------------------------------------------------|----------------------|

| UFQFPN48 | LQFP64 | WLCSP49 | LQFP100 | UFBGA100 | Pin name<br>(function after<br>reset) <sup>(1)</sup> | Pin type | I/O structure | Notes | Alternate functions                                                                          | Additional functions |

| 43       | 59     | D4      | 93      | B4       | PB7                                                  | I/O      | FT            | -     | TIM4_CH2,<br>I2C1_SDA,<br>USART1_RX,<br>SDIO_D0,<br>EVENTOUT                                 | -                    |

| 44       | 60     | A5      | 94      | A4       | BOOT0                                                | I        | В             | -     | -                                                                                            | VPP                  |

| 45       | 61     | В5      | 95      | A3       | PB8                                                  | I/O      | FT            | -     | TIM4_CH3,<br>TIM10_CH1,<br>I2C1_SCL,<br>SPI5_MOSI/I2S5_SD,<br>I2C3_SDA, SDIO_D4,<br>EVENTOUT | -                    |

| 46       | 62     | C5      | 96      | В3       | PB9                                                  | I/O      | FT            | -     | TIM4_CH4,<br>TIM11_CH1,<br>I2C1_SDA,<br>SPI2_NSS/I2S2_WS,<br>I2C2_SDA, SDIO_D5,<br>EVENTOUT  | -                    |

| -        | -      | -       | 97      | C3       | PE0                                                  | I/O      | FT            | -     | TIM4_ETR,<br>EVENTOUT                                                                        | -                    |

| -        | -      | -       | 98      | A2       | PE1                                                  | I/O      | FT            | -     | EVENTOUT                                                                                     | -                    |

| 47       | 63     | A6      | 99      | -        | VSS                                                  | S        | -             | -     | -                                                                                            | -                    |

| -        | -      | B6      | -       | H3       | PDR_ON                                               | Ι        | FT            | -     | -                                                                                            | -                    |

| 48       | 64     | A7      | 100     | -        | VDD                                                  | S        | -             | -     | -                                                                                            | -                    |

Table 8. STM32F411xC/xE pin definitions (continued)

1. Function availability depends on the chosen device.

PC13, PC14 and PC15 are supplied through the power switch. Since the switch only sinks a limited amount of current (3 mA), the use of GPIOs PC13 to PC15 in output mode is limited:

The speed should not exceed 2 MHz with a maximum load of 30 pF.

These I/Os must not be used as a current source (e.g. to drive an LED).

3. Main function after the first backup domain power-up. Later on, it depends on the contents of the RTC registers even after reset (because these registers are not reset by the main reset). For details on how to manage these I/Os, refer to the RTC register description sections in the STM32F411xx reference manual.

4. FT = 5 V tolerant except when in analog mode or oscillator mode (for PC14, PC15, PH0 and PH1).

If the device is delivered in an UFBGA100 and the BYPASS\_REG pin is set to VDD (Regulator off/internal reset ON mode), then PA0 is used as an internal Reset (active low) 5.

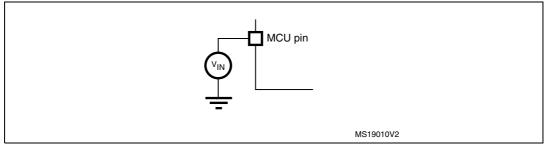

## 6.1.5 Pin input voltage

The input voltage measurement on a pin of the device is described in *Figure 16*.

## 6.3.5 Embedded reset and power control block characteristics

The parameters given in *Table 19* are derived from tests performed under ambient temperature and  $V_{DD}$  supply voltage @ 3.3V.

| Symbol                              | Parameter                | Conditions                  | Min                 | Тур  | Мах  | Unit |  |  |  |  |

|-------------------------------------|--------------------------|-----------------------------|---------------------|------|------|------|--|--|--|--|

|                                     |                          | PLS[2:0]=000 (rising edge)  | 2.09                | 2.14 | 2.19 |      |  |  |  |  |

|                                     |                          | PLS[2:0]=000 (falling edge) | 1.98                | 2.04 | 2.08 |      |  |  |  |  |

|                                     |                          | PLS[2:0]=001 (rising edge)  | 2.23                | 2.30 | 2.37 |      |  |  |  |  |

|                                     |                          | PLS[2:0]=001 (falling edge) | 2.13                | 2.19 | 2.25 |      |  |  |  |  |

|                                     |                          | PLS[2:0]=010 (rising edge)  | 2.39                | 2.45 | 2.51 |      |  |  |  |  |

|                                     |                          | PLS[2:0]=010 (falling edge) | 2.29                | 2.35 | 2.39 |      |  |  |  |  |

|                                     |                          | PLS[2:0]=011 (rising edge)  | 2.54                | 2.60 | 2.65 |      |  |  |  |  |

| N/                                  | Programmable voltage     | PLS[2:0]=011 (falling edge) | 2.44                | 2.51 | 2.56 | V    |  |  |  |  |

| V <sub>PVD</sub>                    | detector level selection | PLS[2:0]=100 (rising edge)  | 2.70                | 2.76 | 2.82 | V    |  |  |  |  |

|                                     |                          | PLS[2:0]=100 (falling edge) | 2.59                | 2.66 | 2.71 |      |  |  |  |  |

|                                     |                          | PLS[2:0]=101 (rising edge)  | 2.86                | 2.93 | 2.99 |      |  |  |  |  |

|                                     |                          | PLS[2:0]=101 (falling edge) | 2.77                | 2.82 | 2.89 |      |  |  |  |  |

|                                     |                          | PLS[2:0]=110 (rising edge)  | 2.96                | 3.03 | 3.10 |      |  |  |  |  |

|                                     |                          | PLS[2:0]=110 (falling edge) | 2.85                | 2.93 | 2.99 |      |  |  |  |  |

|                                     |                          | PLS[2:0]=111 (rising edge)  | 3.07                | 3.14 | 3.21 |      |  |  |  |  |

|                                     |                          | PLS[2:0]=111 (falling edge) | 2.95                | 3.03 | 3.09 |      |  |  |  |  |

| V <sub>PVDhyst</sub> <sup>(2)</sup> | PVD hysteresis           | -                           | -                   | 100  | -    | mV   |  |  |  |  |

|                                     | Power-on/power-down      | Falling edge                | 1.60 <sup>(1)</sup> | 1.68 | 1.76 | V    |  |  |  |  |

| V <sub>POR/PDR</sub>                | reset threshold          | Rising edge                 | 1.64                | 1.72 | 1.80 | v    |  |  |  |  |

| V <sub>PDRhyst</sub> <sup>(2)</sup> | PDR hysteresis           | -                           | -                   | 40   | -    | mV   |  |  |  |  |

| V                                   | Brownout level 1         | Falling edge                | 2.13                | 2.19 | 2.24 |      |  |  |  |  |

| V <sub>BOR1</sub>                   | threshold                | Rising edge                 | 2.23                | 2.29 | 2.33 | 1    |  |  |  |  |

| V                                   | Brownout level 2         | Falling edge                | 2.44                | 2.50 | 2.56 | V    |  |  |  |  |

| V <sub>BOR2</sub>                   | threshold                | Rising edge                 | 2.53                | 2.59 | 2.63 | v    |  |  |  |  |

| V                                   | Brownout level 3         | Falling edge                | 2.75                | 2.83 | 2.88 |      |  |  |  |  |

| V <sub>BOR3</sub>                   | threshold                | Rising edge                 | 2.85                | 2.92 | 2.97 |      |  |  |  |  |

| V <sub>BORhyst</sub> <sup>(2)</sup> | BOR hysteresis           | -                           | -                   | 100  | -    | mV   |  |  |  |  |

| T <sub>RSTTEMPO</sub>               | POR reset timing         | -                           | 0.5                 | 1.5  | 3.0  | ms   |  |  |  |  |

|                 |                |                                                                               |                            |      | Max <sup>(1)</sup>        |                           |                            |                            |      |

|-----------------|----------------|-------------------------------------------------------------------------------|----------------------------|------|---------------------------|---------------------------|----------------------------|----------------------------|------|

| Symbol          | Parameter      | Conditions                                                                    | f <sub>HCLK</sub><br>(MHz) | Тур  | T <sub>A</sub> =<br>25 °C | T <sub>A</sub> =<br>85 °C | T <sub>A</sub> =<br>105 °C | T <sub>A</sub> =<br>125 °C | Unit |

|                 |                |                                                                               | 100                        | 12.2 | 13.2                      | 13.4                      | 14.1                       | 15.3                       |      |

|                 |                | External clock, PLL                                                           | 84                         | 9.8  | 10.6                      | 10.9                      | 11.6                       | 12.8                       |      |

|                 |                | ON <sup>(2)</sup> ,<br>all peripherals                                        | 64                         | 6.9  | 7.4                       | 7.7                       | 8.3                        | 9.5                        |      |

|                 |                | enabled <sup>(3)(4)</sup>                                                     | 50                         | 5.4  | 5.9                       | 6.2                       | 6.8                        | 8.0                        | mA   |

|                 |                |                                                                               | 20                         | 2.8  | 3.2                       | 3.5                       | 4.1                        | 5.3                        |      |

|                 |                | HSI, PLL OFF <sup>(2)</sup> , all peripherals enabled <sup>(3)</sup>          | 16                         | 1.3  | 1.7                       | 2.2                       | 2.8                        | 4.0                        |      |

| I <sub>DD</sub> | Supply current |                                                                               | 1                          | 0.4  | 0.5                       | 0.9                       | 1.6                        | 2.8                        |      |

| 'DD             | in Sleep mode  |                                                                               | 100                        | 3.0  | 3.6                       | 3.9                       | 4.5                        | 5.7                        |      |

|                 |                | $\mathbf{F}$ (and $\mathbf{h}$ ) $\mathbf{D}$ (2)                             | 84                         | 2.5  | 3.0                       | 3.2                       | 3.9                        | 5.1                        | -    |

|                 |                | External clock, PLL ON <sup>(2)</sup> all peripherals disabled <sup>(3)</sup> | 64                         | 1.9  | 2.2                       | 2.5                       | 3.0                        | 4.2                        |      |

|                 |                |                                                                               | 50                         | 1.6  | 1.9                       | 2.1                       | 2.7                        | 3.9                        |      |

|                 |                |                                                                               | 20                         | 1.1  | 1.4                       | 1.7                       | 2.3                        | 3.5                        |      |

|                 |                | HSI, PLL OFF <sup>(2)</sup> , all                                             | 16                         | 0.4  | 0.5                       | 0.9                       | 1.6                        | 2.8                        |      |

|                 |                | peripherals disabled <sup>(3)</sup>                                           | 1                          | 0.3  | 0.4                       | 0.8                       | 1.5                        | 2.7                        |      |

| Table 26. Typical and maximum | current consumption | n in Sleep mode    | - V <sub>DD</sub> = 3.6 V |

|-------------------------------|---------------------|--------------------|---------------------------|

| Table 20. Typical and maximum | ourrent consumption | i ili oleep illout | · • DD • • • •            |

1. Guaranteed by characterization results.

2. Refer to *Table 41* and RM0383 for the possible PLL VCO setting.

3. Add an additional power consumption of 1.6 mA per ADC for the analog part. In applications, this consumption occurs only while the ADC is ON (ADON bit is set in the ADC\_CR2 register).

4. When the ADC is ON (ADON bit set in the ADC\_CR2), add an additional power consumption of 1.6mA per ADC for the analog part.

|          |                                             |                                       | Typ <sup>(1)</sup>        |                           | Max <sup>(1</sup>        |                            |                            |      |  |

|----------|---------------------------------------------|---------------------------------------|---------------------------|---------------------------|--------------------------|----------------------------|----------------------------|------|--|

| Symbol   | Conditions                                  | Parameter                             | T <sub>A</sub> =<br>25 °C | T <sub>A</sub> =<br>25 °C | T <sub>A</sub> =<br>85 ℃ | T <sub>A</sub> =<br>105 °C | T <sub>A</sub> =<br>125 °C | Unit |  |

|          | •                                           | Main regulator usage                  | 112                       | 142 <sup>(2)</sup>        | 400                      | 710 <sup>(2)</sup>         | 1200                       |      |  |

|          | oscillators OFF, no<br>independent watchdog | Low power regulator usage             | 42.6                      | 67 <sup>(2)</sup>         | 300                      | 580 <sup>(2)</sup>         | 1044                       |      |  |

| IDD STOP | Flash in Deep power                         | Main regulator usage                  | 75                        | 99 <sup>(2)</sup>         | 310                      | 580 <sup>(2)</sup>         | 993                        | μA   |  |

|          | down mode, all                              | Low power regulator usage             | 13.6                      | 37 <sup>(2)</sup>         | 265                      | 550 <sup>(2)</sup>         | 1007                       |      |  |

|          | oscillators OFF, no<br>independent watchdog | Low power low voltage regulator usage | 9                         | 28 <sup>(2)</sup>         | 230                      | 500 <sup>(2)</sup>         | 910                        |      |  |

| Table 27. Typical and maximum | current consumptions in Stop mode - V <sub>DD</sub> = 1.7 V |

|-------------------------------|-------------------------------------------------------------|

1. Guaranteed by characterization results.

2. Guaranteed by test in production.

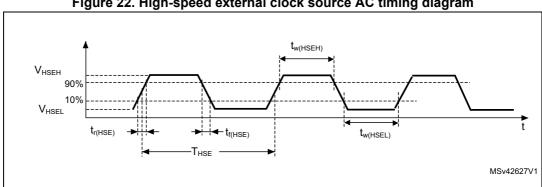

Figure 22. High-speed external clock source AC timing diagram

#### Low-speed external user clock generated from an external source

In bypass mode the LSE oscillator is switched off and the input pin is a standard I/O. The external clock signal has to respect the Table 53. However, the recommended clock input waveform is shown in Figure 23.

The characteristics given in Table 36 result from tests performed using an low-speed external clock source, and under ambient temperature and supply voltage conditions summarized in Table 14.

| Symbol                                       | Parameter                                              | Conditions                       | Min                | Тур    | Max                | Unit |  |

|----------------------------------------------|--------------------------------------------------------|----------------------------------|--------------------|--------|--------------------|------|--|

| f <sub>LSE_ext</sub>                         | User External clock source<br>frequency <sup>(1)</sup> |                                  | -                  | 32.768 | 1000               | kHz  |  |

| V <sub>LSEH</sub>                            | OSC32_IN input pin high level voltage                  |                                  | 0.7V <sub>DD</sub> | -      | V <sub>DD</sub>    | V    |  |

| V <sub>LSEL</sub>                            | OSC32_IN input pin low level voltage                   | -                                | V <sub>SS</sub>    | -      | 0.3V <sub>DD</sub> |      |  |

| t <sub>w(LSEH)</sub><br>t <sub>w(LSEL)</sub> | OSC32_IN high or low time <sup>(1)</sup>               |                                  | 450                | -      | -                  | ns   |  |

| $t_{r(LSE)} \\ t_{f(LSE)}$                   | OSC32_IN rise or fall time <sup>(1)</sup>              |                                  | -                  | -      | 50                 | 113  |  |

| C <sub>in(LSE)</sub>                         | OSC32_IN input capacitance <sup>(1)</sup>              | -                                | -                  | 5      | -                  | pF   |  |

| DuCy <sub>(LSE)</sub>                        | Duty cycle                                             | -                                | 30                 | -      | 70                 | %    |  |

| ١L                                           | OSC32_IN Input leakage current                         | $V_{SS} \leq V_{IN} \leq V_{DD}$ | -                  | -      | ±1                 | μA   |  |

Table 36. Low-speed external user clock characteristics

1. Guaranteed by design.

| Symbol                               | Parameter                     | Conditions                               | Min          | Тур | Max          | Unit |

|--------------------------------------|-------------------------------|------------------------------------------|--------------|-----|--------------|------|

| I <sub>DD(PLL)</sub> <sup>(4)</sup>  | PLL power consumption on VDD  | VCO freq = 100 MHz<br>VCO freq = 432 MHz | 0.15<br>0.45 | -   | 0.40<br>0.75 | mA   |

| I <sub>DDA(PLL)</sub> <sup>(4)</sup> | PLL power consumption on VDDA | VCO freq = 100 MHz<br>VCO freq = 432 MHz | 0.30<br>0.55 | -   | 0.40<br>0.85 |      |

#### Table 41. Main PLL characteristics (continued)

1. Take care of using the appropriate division factor M to obtain the specified PLL input clock values. The M factor is shared between PLL and PLLI2S.

2. Guaranteed by design.

3. The use of two PLLs in parallel could degraded the Jitter up to +30%.

4. Guaranteed by characterization results.

| Symbol                                  | Parameter                             | Conditions                                                              |                    | Min                 | Тур  | Max          | Unit |

|-----------------------------------------|---------------------------------------|-------------------------------------------------------------------------|--------------------|---------------------|------|--------------|------|

| f <sub>PLLI2S_IN</sub>                  | PLLI2S input clock <sup>(1)</sup>     | -                                                                       |                    | 0.95 <sup>(2)</sup> | 1    | 2.10         |      |

| f <sub>PLLI2S_OUT</sub>                 | PLLI2S multiplier output clock        | -                                                                       |                    | -                   | -    | 216          | MHz  |

| f <sub>VCO_OUT</sub>                    | PLLI2S VCO output                     | -                                                                       |                    | 100                 | -    | 432          |      |

| t <sub>LOCK</sub>                       | PLLI2S lock time                      | VCO freq = 100 MHz                                                      |                    | 75                  | -    | 200          | μs   |

|                                         |                                       | VCO freq = 432 MHz                                                      |                    | 100                 | -    | 300          |      |

| Jitter <sup>(3)</sup>                   | Master I2S clock jitter               | Cycle to cycle at<br>12.288 MHz on<br>48 kHz period,<br>N=432, R=5      | RMS                | -                   | 90   | -            |      |

|                                         |                                       |                                                                         | peak<br>to<br>peak | -                   | ±280 | -            |      |

|                                         |                                       | Average frequency of<br>12.288 MHz<br>N = 432, R = 5<br>on 1000 samples |                    | -                   | 90   | -            | ps   |

|                                         | WS I2S clock jitter                   | Cycle to cycle at 48 KHz<br>on 1000 samples                             |                    | -                   | 400  | -            |      |

| I <sub>DD(PLLI2S)</sub> <sup>(4)</sup>  | PLLI2S power consumption on $V_{DD}$  | VCO freq = 100 MHz<br>VCO freq = 432 MHz                                |                    | 0.15<br>0.45        | -    | 0.40<br>0.75 | mA   |

| I <sub>DDA(PLLI2S)</sub> <sup>(4)</sup> | PLLI2S power consumption on $V_{DDA}$ | VCO freq = 100 MHz<br>VCO freq = 432 MHz                                |                    | 0.30<br>0.55        | -    | 0.40<br>0.85 |      |

#### Table 42. PLLI2S (audio PLL) characteristics

1. Take care of using the appropriate division factor M to have the specified PLL input clock values.

2. Guaranteed by design.

3. Value given with main PLL running.

4. Guaranteed by characterization results.

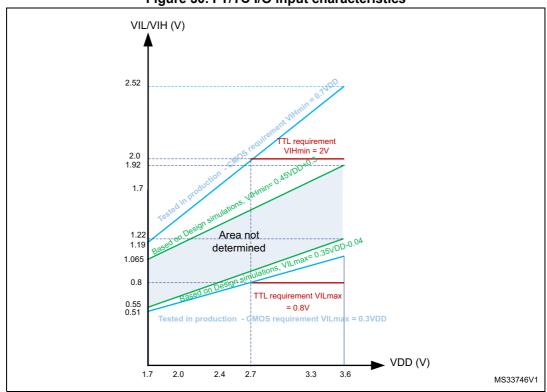

#### Figure 30. FT/TC I/O input characteristics

### **Output driving current**

The GPIOs (general purpose input/outputs) can sink or source up to  $\pm 8$  mA, and sink or source up to  $\pm 20$  mA (with a relaxed V<sub>OL</sub>/V<sub>OH</sub>) except PC13, PC14 and PC15 which can sink or source up to  $\pm 3$ mA. When using the PC13 to PC15 GPIOs in output mode, the speed should not exceed 2 MHz with a maximum load of 30 pF.

In the user application, the number of I/O pins which can drive current must be limited to respect the absolute maximum rating specified in *Section 6.2*. In particular:

- The sum of the currents sourced by all the I/Os on V<sub>DD</sub>, plus the maximum Run consumption of the MCU sourced on V<sub>DD</sub>, cannot exceed the absolute maximum rating ΣI<sub>VDD</sub> (see *Table 12*).

- The sum of the currents sunk by all the I/Os on V<sub>SS</sub> plus the maximum Run consumption of the MCU sunk on V<sub>SS</sub> cannot exceed the absolute maximum rating ΣI<sub>VSS</sub> (see *Table 12*).

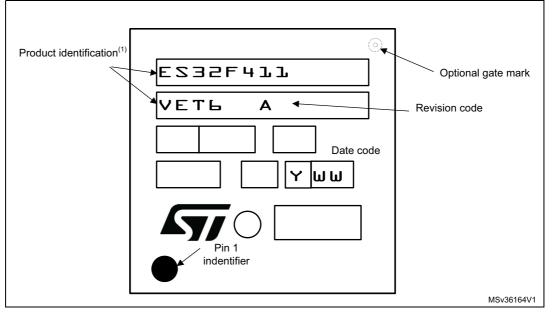

### **Device marking for LQFP100**

The following figure gives an example of topside marking orientation versus pin 1 identifier location.

Other optional marking or inset/upset marks, which depend on supply chain operations, are not indicated below.

Parts marked as "ES", "E" or accompanied by an Engineering Sample notification letter, are not yet qualified and therefore not yet ready to be used in production and any consequences deriving from such usage will not be at ST charge. In no event, ST will be liable for any customer usage of these engineering samples in production. ST Quality has to be contacted prior to any decision to use these Engineering samples to run qualification activity.

# Appendix B Application block diagrams

## B.1 USB OTG Full Speed (FS) interface solutions

Figure 61. USB controller configured as peripheral-only and used in Full-Speed mode

1. The external voltage regulator is only needed when building a  $\mathrm{V}_{\mathrm{BUS}}$  powered device.

### Figure 62. USB controller configured as host-only and used in Full-Speed mode

1. The current limiter is required only if the application has to support a  $V_{BUS}$  powered device. A basic power switch can be used if 5V are available on the application board.

Figure 63. USB controller configured in dual mode and used in Full-Speed mode

- 1. The external voltage regulator is only needed when building a  $\mathrm{V}_{\mathrm{BUS}}$  powered device.

- The current limiter is required only if the application has to support a V<sub>BUS</sub> powered device. A basic power switch can be used if 5 V are available on the application board.

- 3. The ID pin is required in dual role only.

# B.2 Sensor Hub application example

### Figure 64. Sensor Hub application example