Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

#### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Details                    |                                                                         |

|----------------------------|-------------------------------------------------------------------------|

| Product Status             | Active                                                                  |

| Core Processor             | ARM® Cortex®-M4                                                         |

| Core Size                  | 32-Bit Single-Core                                                      |

| Speed                      | 100MHz                                                                  |

| Connectivity               | I <sup>2</sup> C, IrDA, LINbus, MMC/SD/SDIO, SPI, UART/USART, USB OTG   |

| Peripherals                | Brown-out Detect/Reset, DMA, I <sup>2</sup> S, POR, PWM, WDT            |

| Number of I/O              | 50                                                                      |

| Program Memory Size        | 256KB (256K x 8)                                                        |

| Program Memory Type        | FLASH                                                                   |

| EEPROM Size                | -                                                                       |

| RAM Size                   | 128K x 8                                                                |

| Voltage - Supply (Vcc/Vdd) | 1.7V ~ 3.6V                                                             |

| Data Converters            | A/D 16x12b                                                              |

| Oscillator Type            | Internal                                                                |

| Operating Temperature      | -40°C ~ 105°C (TA)                                                      |

| Mounting Type              | Surface Mount                                                           |

| Package / Case             | 64-LQFP                                                                 |

| Supplier Device Package    | 64-LQFP (10x10)                                                         |

| Purchase URL               | https://www.e-xfl.com/product-detail/stmicroelectronics/stm32f411rct7tr |

|                            |                                                                         |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

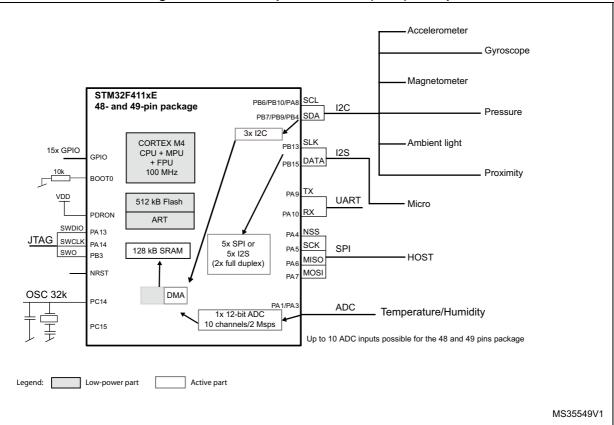

# 1 Introduction

This datasheet provides the description of the STM32F411xC/xE line of microcontrollers.

The STM32F411xC/xE datasheet should be read in conjunction with RM0383 reference manual which is available from the STMicroelectronics website *www.st.com*. It includes all information concerning Flash memory programming.

For information on the Cortex<sup>®</sup>-M4 core, please refer to the Cortex<sup>®</sup>-M4 programming manual (PM0214) available from *www.st.com*.

buses is 100 MHz while the maximum frequency of the high-speed APB domains is 100 MHz. The maximum allowed frequency of the low-speed APB domain is 50 MHz.

The devices embed a dedicated PLL (PLLI2S) which allows to achieve audio class performance. In this case, the  $I^2S$  master clock can generate all standard sampling frequencies from 8 kHz to 192 kHz.

## 3.13 Boot modes

At startup, boot pins are used to select one out of three boot options:

- Boot from user Flash

- Boot from system memory

- Boot from embedded SRAM

The bootloader is located in system memory. It is used to reprogram the Flash memory by using USART1(PA9/10), USART2(PD5/6), USB OTG FS in device mode (PA11/12) through DFU (device firmware upgrade), I2C1(PB6/7), I2C2(PB10/3), I2C3(PA8/PB4), SPI1(PA4/5/6/7), SPI2(PB12/13/14/15) or SPI3(PA15, PC10/11/12).

For more detailed information on the bootloader, refer to Application Note: AN2606, *STM32™ microcontroller system memory boot mode*.

# 3.14 Power supply schemes

- VDD = 1.7 to 3.6 V: external power supply for I/Os with the internal supervisor (POR/PDR) disabled, provided externally through VDD pins. Requires the use of an external power supply supervisor connected to the VDD and NRST pins.

- V<sub>SSA</sub>, V<sub>DDA</sub> = 1.7 to 3.6 V: external analog power supplies for ADC, Reset blocks, RCs and PLL. V<sub>DDA</sub> and V<sub>SSA</sub> must be connected to V<sub>DD</sub> and V<sub>SS</sub>, respectively, with decoupling technique.

- V<sub>BAT</sub> = 1.65 to 3.6 V: power supply for RTC, external clock 32 kHz oscillator and backup registers (through power switch) when V<sub>DD</sub> is not present.

Refer to Figure 17: Power supply scheme for more details.

A comprehensive set of power-saving mode allows to design low-power applications.

When the internal reset is OFF, the following integrated features are no longer supported:

- The integrated power-on reset (POR) / power-down reset (PDR) circuitry is disabled.

- The brownout reset (BOR) circuitry must be disabled.

- The embedded programmable voltage detector (PVD) is disabled.

- V<sub>BAT</sub> functionality is no more available and VBAT pin should be connected to V<sub>DD</sub>.

## 3.16 Voltage regulator

The regulator has four operating modes:

- Regulator ON

- Main regulator mode (MR)

- Low power regulator (LPR)

- Power-down

- Regulator OFF

## 3.16.1 Regulator ON

On packages embedding the BYPASS\_REG pin, the regulator is enabled by holding BYPASS\_REG low. On all other packages, the regulator is always enabled.

There are three power modes configured by software when the regulator is ON:

- MR is used in the nominal regulation mode (With different voltage scaling in Run) In Main regulator mode (MR mode), different voltage scaling are provided to reach the best compromise between maximum frequency and dynamic power consumption.

- LPR is used in the Stop modes

- The LP regulator mode is configured by software when entering Stop mode.

- Power-down is used in Standby mode.

The Power-down mode is activated only when entering in Standby mode. The regulator output is in high impedance and the kernel circuitry is powered down, inducing zero consumption. The contents of the registers and SRAM are lost.

Depending on the package, one or two external ceramic capacitors should be connected on the V<sub>CAP\_1</sub> and V<sub>CAP\_2</sub> pins. The V<sub>CAP\_2</sub> pin is only available for the LQFP100 and UFBGA100 packages.

All packages have the regulator ON feature.

## 3.16.2 Regulator OFF

The Regulator OFF is available only on the UFBGA100, which features the BYPASS\_REG pin. The regulator is disabled by holding BYPASS\_REG high. The regulator OFF mode allows to supply externally a V12 voltage source through  $V_{CAP}$  1 and  $V_{CAP}$  2 pins.

Since the internal voltage scaling is not managed internally, the external voltage value must be aligned with the targeted maximum frequency. Refer to *Table 14: General operating conditions*.

The two 2.2  $\mu$ F V<sub>CAP</sub> ceramic capacitors should be replaced by two 100 nF decoupling capacitors. Refer to *Figure 17: Power supply scheme*.

### 3.20.5 SysTick timer

This timer is dedicated to real-time operating systems, but could also be used as a standard downcounter. It features:

- A 24-bit downcounter

- Autoreload capability

- Maskable system interrupt generation when the counter reaches 0

- Programmable clock source.

# 3.21 Inter-integrated circuit interface (I<sup>2</sup>C)

Up to three I<sup>2</sup>C bus interfaces can operate in multimaster and slave modes. They can support the standard (up to 100 kHz) and fast (up to 400 kHz) modes. The I2C bus frequency can be increased up to 1 MHz. For more details about the complete solution, please contact your local ST sales representative. They also support the 7/10-bit addressing mode and the 7-bit dual addressing mode (as slave). A hardware CRC generation/verification is embedded.

They can be served by DMA and they support SMBus 2.0/PMBus.

The devices also include programmable analog and digital noise filters (see Table 5).

|                                     | Analog filter | Digital filter                                         |

|-------------------------------------|---------------|--------------------------------------------------------|

| Pulse width of<br>suppressed spikes | ≥ 50 ns       | Programmable length from 1 to 15 I2C peripheral clocks |

# 3.22 Universal synchronous/asynchronous receiver transmitters (USART)

The devices embed three universal synchronous/asynchronous receiver transmitters (USART1, USART2 and USART6).

These three interfaces provide asynchronous communication, IrDA SIR ENDEC support, multiprocessor communication mode, single-wire half-duplex communication mode and have LIN Master/Slave capability. The USART1 and USART6 interfaces are able to communicate at speeds of up to 12.5 Mbit/s. The USART2 interface communicates at up to 6.25 bit/s.

USART1 and USART2 also provide hardware management of the CTS and RTS signals, Smart Card mode (ISO 7816 compliant) and SPI-like communication capability. All interfaces can be served by the DMA controller.

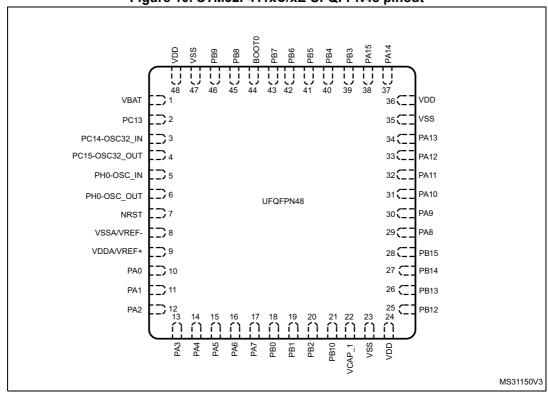

Figure 10. STM32F411xC/xE UFQFPN48 pinout

1. The above figure shows the package top view.

| Pin number |        |         |         |          |                                                      |          |               |       |                                                                                    |                      |

|------------|--------|---------|---------|----------|------------------------------------------------------|----------|---------------|-------|------------------------------------------------------------------------------------|----------------------|

| UFQFPN48   | LQFP64 | WLCSP49 | LQFP100 | UFBGA100 | Pin name<br>(function after<br>reset) <sup>(1)</sup> | Pin type | I/O structure | Notes | Alternate functions                                                                | Additional functions |

| -          | -      | -       | 60      | H12      | PD13                                                 | I/O      | FT            | -     | TIM4_CH2,<br>EVENTOUT                                                              | -                    |

| -          | -      | -       | 61      | H11      | PD14                                                 | I/O      | FT            | -     | TIM4_CH3,<br>EVENTOUT                                                              | -                    |

| -          | -      | -       | 62      | H10      | PD15                                                 | I/O      | FT            | -     | TIM4_CH4,<br>EVENTOUT                                                              | -                    |

| -          | 37     | -       | 63      | E12      | PC6                                                  | I/O      | FT            | -     | TIM3_CH1,<br>I2S2_MCK,<br>USART6_TX,<br>SDIO_D6,<br>EVENTOUT                       | -                    |

| -          | 38     | -       | 64      | E11      | PC7                                                  | I/O      | FT            | -     | TIM3_CH2,<br>SPI2_SCK/I2S2_CK,<br>I2S3_MCK,<br>USART6_RX,<br>SDIO_D7,<br>EVENTOUT  | -                    |

| -          | 39     | -       | 65      | E10      | PC8                                                  | I/O      | FT            | -     | TIM3_CH3,<br>USART6_CK,<br>SDIO_D0,<br>EVENTOUT                                    | -                    |

| -          | 40     | -       | 66      | D12      | PC9                                                  | I/O      | FT            | -     | MCO_2, TIM3_CH4,<br>I2C3_SDA,<br>I2S2_CKIN,<br>SDIO_D1,<br>EVENTOUT                | -                    |

| 29         | 41     | D1      | 67      | D11      | PA8                                                  | I/O      | FT            | -     | MCO_1, TIM1_CH1,<br>I2C3_SCL,<br>USART1_CK,<br>USB_FS_SOF,<br>SDIO_D1,<br>EVENTOUT | -                    |

| 30         | 42     | D2      | 68      | D10      | PA9                                                  | I/O      | FT            | -     | TIM1_CH2,<br>I2C3_SMBA,<br>USART1_TX,<br>USB_FS_VBUS,<br>SDIO_D2,<br>EVENTOUT      | OTG_FS_VBUS          |

Table 8. STM32F411xC/xE pin definitions (continued)

| Bus  | Boundary address          | Peripheral          |

|------|---------------------------|---------------------|

|      | 0x4000 7000 - 0x4000 73FF | PWR                 |

|      | 0x4000 6000 - 0x4000 6FFF | Reserved            |

|      | 0x4000 5C00 - 0x4000 5FFF | I2C3                |

|      | 0x4000 5800 - 0x4000 5BFF | I2C2                |

|      | 0x4000 5400 - 0x4000 57FF | I2C1                |

|      | 0x4000 4800 - 0x4000 53FF | Reserved            |

|      | 0x4000 4400 - 0x4000 47FF | USART2              |

|      | 0x4000 4000 - 0x4000 43FF | I2S3ext             |

|      | 0x4000 3C00 - 0x4000 3FFF | SPI3 / I2S3         |

| APB1 | 0x4000 3800 - 0x4000 3BFF | SPI2 / I2S2         |

|      | 0x4000 3400 - 0x4000 37FF | I2S2ext             |

|      | 0x4000 3000 - 0x4000 33FF | IWDG                |

|      | 0x4000 2C00 - 0x4000 2FFF | WWDG                |

|      | 0x4000 2800 - 0x4000 2BFF | RTC & BKP Registers |

|      | 0x4000 1000 - 0x4000 27FF | Reserved            |

|      | 0x4000 0C00 - 0x4000 0FFF | TIM5                |

|      | 0x4000 0800 - 0x4000 0BFF | TIM4                |

|      | 0x4000 0400 - 0x4000 07FF | TIM3                |

|      | 0x4000 0000 - 0x4000 03FF | TIM2                |

# Table 10. STM32F411xC/xE register boundary addresses (continued)

## 6.3.5 Embedded reset and power control block characteristics

The parameters given in *Table 19* are derived from tests performed under ambient temperature and  $V_{DD}$  supply voltage @ 3.3V.

| Symbol                              | Parameter                | Conditions                  | Min                 | Тур  | Мах  | Unit |  |  |  |

|-------------------------------------|--------------------------|-----------------------------|---------------------|------|------|------|--|--|--|

|                                     |                          | PLS[2:0]=000 (rising edge)  | 2.09                | 2.14 | 2.19 |      |  |  |  |

| V <sub>PVD</sub>                    |                          | PLS[2:0]=000 (falling edge) | 1.98                | 2.04 | 2.08 |      |  |  |  |

|                                     |                          | PLS[2:0]=001 (rising edge)  | 2.23                | 2.30 | 2.37 |      |  |  |  |

|                                     |                          | PLS[2:0]=001 (falling edge) | 2.13                | 2.19 | 2.25 |      |  |  |  |

|                                     |                          | PLS[2:0]=010 (rising edge)  | 2.39                | 2.45 | 2.51 |      |  |  |  |

|                                     |                          | PLS[2:0]=010 (falling edge) | 2.29                | 2.35 | 2.39 |      |  |  |  |

|                                     |                          | PLS[2:0]=011 (rising edge)  | 2.54                | 2.60 | 2.65 |      |  |  |  |

|                                     | Programmable voltage     | PLS[2:0]=011 (falling edge) | 2.44                | 2.51 | 2.56 | V    |  |  |  |

|                                     | detector level selection | PLS[2:0]=100 (rising edge)  | 2.70                | 2.76 | 2.82 | V    |  |  |  |

|                                     |                          | PLS[2:0]=100 (falling edge) | 2.59                | 2.66 | 2.71 |      |  |  |  |

|                                     |                          | PLS[2:0]=101 (rising edge)  | 2.86                | 2.93 | 2.99 |      |  |  |  |

|                                     |                          | PLS[2:0]=101 (falling edge) | 2.77                | 2.82 | 2.89 |      |  |  |  |

|                                     |                          | PLS[2:0]=110 (rising edge)  | 2.96                | 3.03 | 3.10 |      |  |  |  |

|                                     |                          | PLS[2:0]=110 (falling edge) | 2.85                | 2.93 | 2.99 |      |  |  |  |

|                                     |                          | PLS[2:0]=111 (rising edge)  | 3.07                | 3.14 | 3.21 |      |  |  |  |

|                                     |                          | PLS[2:0]=111 (falling edge) | 2.95                | 3.03 | 3.09 |      |  |  |  |

| V <sub>PVDhyst</sub> <sup>(2)</sup> | PVD hysteresis           | -                           | -                   | 100  | -    | mV   |  |  |  |

|                                     | Power-on/power-down      | Falling edge                | 1.60 <sup>(1)</sup> | 1.68 | 1.76 | V    |  |  |  |

| V <sub>POR/PDR</sub>                | reset threshold          | Rising edge                 | 1.64                | 1.72 | 1.80 |      |  |  |  |

| V <sub>PDRhyst</sub> <sup>(2)</sup> | PDR hysteresis           | -                           | -                   | 40   | -    | mV   |  |  |  |

| V                                   | Brownout level 1         | Falling edge                | 2.13                | 2.19 | 2.24 |      |  |  |  |

| V <sub>BOR1</sub>                   | threshold                | Rising edge                 | 2.23                | 2.29 | 2.33 |      |  |  |  |

| V                                   | Brownout level 2         | Falling edge                | 2.44                | 2.50 | 2.56 | V    |  |  |  |

| V <sub>BOR2</sub>                   | threshold                | Rising edge                 | 2.53                | 2.59 | 2.63 | v    |  |  |  |

| M                                   | Brownout level 3         | Falling edge                | 2.75                | 2.83 | 2.88 |      |  |  |  |

| V <sub>BOR3</sub>                   | threshold                | Rising edge                 | 2.85                | 2.92 | 2.97 |      |  |  |  |

| V <sub>BORhyst</sub> <sup>(2)</sup> | BOR hysteresis           | -                           | -                   | 100  | -    | mV   |  |  |  |

| T <sub>RSTTEMPO</sub>               | POR reset timing         | -                           | 0.5                 | 1.5  | 3.0  | ms   |  |  |  |

|                 |                                      | Conditions                                                                    | £                          |      | Max <sup>(1)</sup>        |                           |                            |                            |      |

|-----------------|--------------------------------------|-------------------------------------------------------------------------------|----------------------------|------|---------------------------|---------------------------|----------------------------|----------------------------|------|

| Symbol          | Parameter                            |                                                                               | f <sub>HCLK</sub><br>(MHz) | Тур  | T <sub>A</sub> =<br>25 °C | T <sub>A</sub> =<br>85 °C | T <sub>A</sub> =<br>105 °C | T <sub>A</sub> =<br>125 °C | Unit |

|                 |                                      |                                                                               | 100                        | 29.5 | 31.5                      | 32.3                      | 33.3                       | 34.7                       |      |

|                 |                                      | External clock, PLL                                                           | 84                         | 25.5 | 27.1                      | 27.9                      | 28.9                       | 30.2                       |      |

|                 |                                      | ON <sup>(2)</sup> ,<br>all peripherals                                        | 64                         | 18.6 | 19.8                      | 20.4                      | 21.2                       | 22.4                       |      |

|                 | Supply current<br>in <b>Run mode</b> | enabled <sup>(3)(4)</sup>                                                     | 50                         | 15.2 | 16.4                      | 16.9                      | 17.7                       | 18.7                       | - mA |

|                 |                                      |                                                                               | 20                         | 7.6  | 8.4                       | 8.8                       | 9.5                        | 10.5                       |      |

|                 |                                      | HSI, PLL OFF <sup>(2)</sup> , all peripherals enabled <sup>(3)</sup>          | 16                         | 4.8  | 5.2                       | 5.7                       | 6.5                        | 7.5                        |      |

|                 |                                      |                                                                               | 1                          | 0.9  | 1.3                       | 1.6                       | 2.4                        | 3.4                        |      |

| I <sub>DD</sub> |                                      | External clock, PLL ON <sup>(2)</sup> all peripherals disabled <sup>(3)</sup> | 100                        | 20.4 | 21.8                      | 22.7                      | 23.8                       | 25.1                       |      |

|                 |                                      |                                                                               | 84                         | 18.4 | 19.2 <sup>(5)</sup>       | 20.9                      | 21.1                       | 22.4                       |      |

|                 |                                      |                                                                               | 64                         | 13.5 | 14.5                      | 15.2                      | 15.9                       | 17.2                       |      |

|                 |                                      |                                                                               | 50                         | 11.3 | 12.2                      | 12.8                      | 13.6                       | 14.7                       |      |

|                 |                                      |                                                                               | 20                         | 5.6  | 6.4                       | 6.7                       | 7.4                        | 8.5                        |      |

|                 |                                      | HSI, PLL OFF <sup>(2)</sup> , all                                             | 16                         | 3.6  | 4.1                       | 4.5                       | 5.2                        | 6.3                        |      |

|                 |                                      | peripherals disabled <sup>(3)</sup>                                           | 1                          | 0.9  | 1.2                       | 1.6                       | 2.3                        | 3.4                        |      |

# Table 24. Typical and maximum current consumption in run mode, code with data processing<br/>(ART accelerator disabled) running from Flash memory - $V_{DD}$ = 3.6 V

1. Guaranteed by characterization results.

2. Refer to Table 41 and RM0383 for the possible PLL VCO setting

3. Add an additional power consumption of 1.6 mA per ADC for the analog part. In applications, this consumption occurs only while the ADC is ON (ADON bit is set in the ADC\_CR2 register).

4. When the ADC is ON (ADON bit set in the ADC\_CR2), add an additional power consumption of 1.6mA per ADC for the analog part.

5. Guaranteed by test in production.

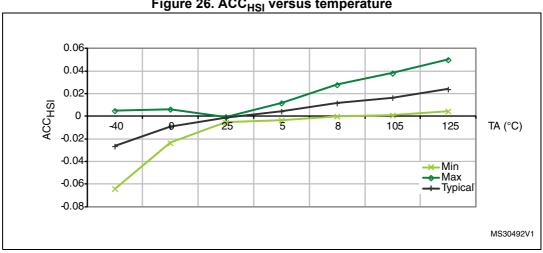

Figure 26. ACC<sub>HSI</sub> versus temperature

1. Guaranteed by characterization results.

### Low-speed internal (LSI) RC oscillator

| Table 40. LSI oscillator characteristic | cs <sup>(1)</sup> |

|-----------------------------------------|-------------------|

|-----------------------------------------|-------------------|

| Symbol                              | Parameter                        | Min | Тур | Мах | Unit |

|-------------------------------------|----------------------------------|-----|-----|-----|------|

| f <sub>LSI</sub> <sup>(2)</sup>     | Frequency                        | 17  | 32  | 47  | kHz  |

| t <sub>su(LSI)</sub> <sup>(3)</sup> | LSI oscillator startup time      | -   | 15  | 40  | μs   |

| I <sub>DD(LSI)</sub> <sup>(3)</sup> | LSI oscillator power consumption | -   | 0.4 | 0.6 | μA   |

1.  $V_{DD}$  = 3 V, T<sub>A</sub> = -40 to 125 °C unless otherwise specified.

2. Guaranteed by characterization results.

3. Guaranteed by design.

| Symbol                               | Parameter                     | Conditions                               | Min          | Тур | Max          | Unit |  |

|--------------------------------------|-------------------------------|------------------------------------------|--------------|-----|--------------|------|--|

| I <sub>DD(PLL)</sub> <sup>(4)</sup>  | PLL power consumption on VDD  | VCO freq = 100 MHz<br>VCO freq = 432 MHz | 0.15<br>0.45 | -   | 0.40<br>0.75 | mA   |  |

| I <sub>DDA(PLL)</sub> <sup>(4)</sup> | PLL power consumption on VDDA | VCO freq = 100 MHz<br>VCO freq = 432 MHz | 0.30<br>0.55 | -   | 0.40<br>0.85 |      |  |

#### Table 41. Main PLL characteristics (continued)

1. Take care of using the appropriate division factor M to obtain the specified PLL input clock values. The M factor is shared between PLL and PLLI2S.

2. Guaranteed by design.

3. The use of two PLLs in parallel could degraded the Jitter up to +30%.

4. Guaranteed by characterization results.

| Symbol                                  | Parameter                             | Conditions                                                              |                    | Min                 | Тур  | Max          | Unit |

|-----------------------------------------|---------------------------------------|-------------------------------------------------------------------------|--------------------|---------------------|------|--------------|------|

| f <sub>PLLI2S_IN</sub>                  | PLLI2S input clock <sup>(1)</sup>     | -                                                                       |                    | 0.95 <sup>(2)</sup> | 1    | 2.10         | MHz  |

| f <sub>PLLI2S_OUT</sub>                 | PLLI2S multiplier output clock        | -                                                                       |                    | -                   | -    | 216          |      |

| f <sub>VCO_OUT</sub>                    | PLLI2S VCO output                     | -                                                                       |                    | 100                 | -    | 432          |      |

| t <sub>LOCK</sub>                       | DLL12S look time                      | VCO freq = 100 MHz                                                      |                    | 75                  | -    | 200          |      |

| LOCK                                    | PLLI2S lock time VCO freq = 432 MHz   |                                                                         | 100                | -                   | 300  | μs           |      |

|                                         |                                       | Cycle to cycle at                                                       | RMS                | -                   | 90   | -            |      |

|                                         | Master I2S clock jitter               | 48 kHz period,                                                          | peak<br>to<br>peak | -                   | ±280 | -            |      |

| Jitter <sup>(3)</sup>                   |                                       | Average frequency of<br>12.288 MHz<br>N = 432, R = 5<br>on 1000 samples |                    | -                   | 90   | -            | ps   |

|                                         | WS I2S clock jitter                   | Cycle to cycle at 48 I<br>on 1000 samples                               | -                  | 400                 | -    |              |      |

| I <sub>DD(PLLI2S)</sub> <sup>(4)</sup>  | PLLI2S power consumption on $V_{DD}$  | VCO freq = 100 MHz<br>VCO freq = 432 MHz                                |                    | 0.15<br>0.45        | -    | 0.40<br>0.75 | mA   |

| I <sub>DDA(PLLI2S)</sub> <sup>(4)</sup> | PLLI2S power consumption on $V_{DDA}$ | VCO freq = 100 MHz<br>VCO freq = 432 MHz                                |                    | 0.30<br>0.55        | -    | 0.40<br>0.85 |      |

#### Table 42. PLLI2S (audio PLL) characteristics

1. Take care of using the appropriate division factor M to have the specified PLL input clock values.

2. Guaranteed by design.

3. Value given with main PLL running.

4. Guaranteed by characterization results.

| Symbol                          | Parameter                                        | Conditions | Min <sup>(1)</sup> | Тур | Max <sup>(1)</sup> | Unit |

|---------------------------------|--------------------------------------------------|------------|--------------------|-----|--------------------|------|

| V <sub>prog</sub>               | Programming voltage                              |            | 2.7                | -   | 3.6                | V    |

| V <sub>PP</sub>                 | V <sub>PP</sub> voltage range                    |            | 7                  | -   | 9                  | V    |

| I <sub>PP</sub>                 | Minimum current sunk on the $V_{\rm PP}$ pin     |            | 10                 | -   | -                  | mA   |

| t <sub>VPP</sub> <sup>(3)</sup> | Cumulative time during which $V_{PP}$ is applied |            | -                  | -   | 1                  | hour |

Table 46. Flash memory programming with V<sub>PP</sub> voltage (continued)

1. Guaranteed by design.

2. The maximum programming time is measured after 100K erase operations.

3.  $V_{PP}$  should only be connected during programming/erasing.

| Symbol           | Parameter      | Conditions                                                                                                                                                                                              | Value<br>Min <sup>(1)</sup> | Unit    |

|------------------|----------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------|---------|

| N <sub>END</sub> | Endurance      | $T_A = -40 \text{ to } + 85 \text{ °C} \text{ (temp. range 6)}$<br>$T_A = -40 \text{ to } + 105 \text{ °C} \text{ (temp. range 7)}$<br>$T_A = -40 \text{ to } + 125 \text{ °C} \text{ (temp. range 3)}$ | 10                          | kcycles |

|                  |                | 1 kcycle <sup>(2)</sup> at T <sub>A</sub> = 85 °C                                                                                                                                                       | 30                          |         |

| t                | Data retention | 1 kcycle <sup>(2)</sup> at T <sub>A</sub> = 105 °C                                                                                                                                                      | 10                          | Years   |

| t <sub>RET</sub> | Data retention | 1 kcycle <sup>(2)</sup> at T <sub>A</sub> = 125 °C                                                                                                                                                      | 3                           | Tears   |

|                  |                | 10 kcycle <sup>(2)</sup> at T <sub>A</sub> = 55 °C                                                                                                                                                      | 20                          |         |

| Table 47. Flash memory | endurance and data retention |

|------------------------|------------------------------|

|------------------------|------------------------------|

1. Guaranteed by characterization results.

2. Cycling performed over the whole temperature range.

## 6.3.13 EMC characteristics

Susceptibility tests are performed on a sample basis during device characterization.

### Functional EMS (electromagnetic susceptibility)

While a simple application is executed on the device (toggling 2 LEDs through I/O ports). the device is stressed by two electromagnetic events until a failure occurs. The failure is indicated by the LEDs:

- Electrostatic discharge (ESD) (positive and negative) is applied to all device pins until a functional disturbance occurs. This test is compliant with the IEC 61000-4-2 standard.

- FTB: A burst of fast transient voltage (positive and negative) is applied to V<sub>DD</sub> and V<sub>SS</sub> through a 100 pF capacitor, until a functional disturbance occurs. This test is compliant with the IEC 61000-4-4 standard.

A device reset allows normal operations to be resumed.

The test results are given in *Table 49*. They are based on the EMS levels and classes defined in application note AN1709.

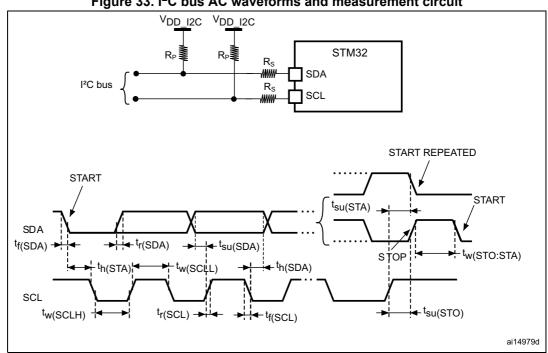

- 1. R<sub>S</sub> = series protection resistor.

- 2. R<sub>P</sub> = external pull-up resistor.

- 3.  $V_{DD \ I2C}$  is the I2C bus power supply.

|                        | I2C_CCR value                  |

|------------------------|--------------------------------|

| f <sub>SCL</sub> (kHz) | <b>R<sub>P</sub> = 4.7 k</b> Ω |

| 400                    | 0x8019                         |

| 300                    | 0x8021                         |

| 200                    | 0x8032                         |

| 100                    | 0x0096                         |

| 50                     | 0x012C                         |

| 20                     | 0x02EE                         |

# Table 59. SCL frequency ( $f_{PCLK1}$ = 50 MHz, $V_{DD} = V_{DD_{-12C}} = 3.3 V$ )<sup>(1)(2)</sup>

1.  $R_P$  = External pull-up resistance,  $f_{SCL}$  = I<sup>2</sup>C speed

2. For speeds around 200 kHz, the tolerance on the achieved speed is of ±5%. For other speed ranges, the tolerance on the achieved speed is  $\pm 2\%$ . These variations depend on the accuracy of the external components used to design the application.

## I<sup>2</sup>S interface characteristics

Unless otherwise specified, the parameters given in *Table 61* for the I<sup>2</sup>S interface are derived from tests performed under the ambient temperature,  $f_{PCLKx}$  frequency and  $V_{DD}$  supply voltage conditions summarized in *Table 14*, with the following configuration:

- Output speed is set to OSPEEDRy[1:0] = 10

- Capacitive load C = 30 pF

- Measurement points are done at CMOS levels: 0.5V<sub>DD</sub>

Refer to Section 6.3.16: I/O port characteristics for more details on the input/output alternate function characteristics (CK, SD, WS).

| Symbol                 | Parameter                      | Conditions                             | Min    | Мах                   | Unit |

|------------------------|--------------------------------|----------------------------------------|--------|-----------------------|------|

| f <sub>MCK</sub>       | I2S Main clock output          | -                                      | 256x8K | 256xFs <sup>(2)</sup> | MHz  |

| f                      | 125 clock froguonov            | Master data: 32 bits                   | -      | 64xFs                 | MHz  |

| f <sub>CK</sub>        | I2S clock frequency            | Slave data: 32 bits                    | -      | 64xFs                 |      |

| D <sub>CK</sub>        | I2S clock frequency duty cycle | Slave receiver                         | 30     | 70                    | %    |

| t <sub>v(WS)</sub>     | WS valid time                  | Master mode                            | 0      | 7                     |      |

| t <sub>h(WS)</sub>     | WS hold time                   | Master mode                            | 1.5    | -                     |      |

| t <sub>su(WS)</sub>    | WS setup time                  | Slave mode                             | 1.5    | -                     |      |

| t <sub>h(WS)</sub>     | WS hold time                   | Slave mode                             | 3      | -                     |      |

| t <sub>su(SD_MR)</sub> | Data input setup time          | Master receiver                        | 1      | -                     |      |

| $t_{su(SD\_SR)}$       |                                | Slave receiver                         | 2.5    | -                     | ns   |

| t <sub>h(SD_MR)</sub>  | Data input hold time           | Master receiver                        | 7      | -                     |      |

| t <sub>h(SD_SR)</sub>  | Data input noid time           | Slave receiver                         | 2.5    | -                     |      |

| t <sub>v(SD_ST)</sub>  | Data output valid time         | Slave transmitter (after enable edge)  | -      | 20                    |      |

| t <sub>v(SD_MT)</sub>  |                                | Master transmitter (after enable edge) | -      | 6                     |      |

| t <sub>h(SD_ST)</sub>  |                                | Slave transmitter (after enable edge)  | 8      | -                     |      |

| t <sub>h(SD_MT)</sub>  | Data output hold time          | Master transmitter (after enable edge) | 2      | -                     |      |

| Table 61. I <sup>2</sup> S dynamic characteristics <sup>(1</sup> | I) |  |

|------------------------------------------------------------------|----|--|

|------------------------------------------------------------------|----|--|

1. Guaranteed by characterization results.

2. The maximum value of 256xFs is 50 MHz (APB1 maximum frequency).

Note: Refer to the I2S section of RM0383 reference manual for more details on the sampling frequency ( $F_{S}$ ).

$f_{MCK}$ ,  $f_{CK}$ , and  $D_{CK}$  values reflect only the digital peripheral behavior. The values of these parameters might be slightly impacted by the source clock precision.  $D_{CK}$  depends mainly on the value of ODD bit. The digital contribution leads to a minimum value of (I2SDIV/(2\*I2SDIV+ODD) and a maximum value of (I2SDIV+ODD)/(2\*I2SDIV+ODD).  $F_S$  maximum value is supported for each mode/condition.

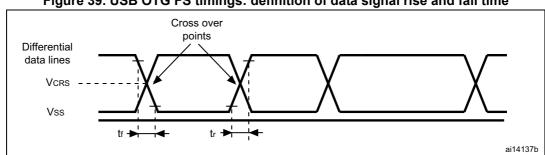

#### Figure 39. USB OTG FS timings: definition of data signal rise and fall time

#### Table 64. USB OTG FS electrical characteristics<sup>(1)</sup>

|                  | Driver characteristics          |                                |     |     |      |  |  |

|------------------|---------------------------------|--------------------------------|-----|-----|------|--|--|

| Symbol           | Parameter                       | Conditions                     | Min | Max | Unit |  |  |

| t <sub>r</sub>   | Rise time <sup>(2)</sup>        | C <sub>L</sub> = 50 pF         | 4   | 20  | ns   |  |  |

| t <sub>f</sub>   | Fall time <sup>(2)</sup>        | C <sub>L</sub> = 50 pF         | 4   | 20  | ns   |  |  |

| t <sub>rfm</sub> | Rise/ fall time matching        | t <sub>r</sub> /t <sub>f</sub> | 90  | 110 | %    |  |  |

| V <sub>CRS</sub> | Output signal crossover voltage |                                | 1.3 | 2.0 | V    |  |  |

1. Guaranteed by design.

2. Measured from 10% to 90% of the data signal. For more detailed informations, please refer to USB Specification - Chapter 7 (version 2.0).

#### 6.3.20 12-bit ADC characteristics

Unless otherwise specified, the parameters given in *Table 65* are derived from tests performed under the ambient temperature,  $f_{PCLK2}$  frequency and  $V_{DDA}$  supply voltage conditions summarized in *Table 14*.

| Symbol                             | Parameter                               | Conditions                                      | Min                                                         | Тур | Max               | Unit               |

|------------------------------------|-----------------------------------------|-------------------------------------------------|-------------------------------------------------------------|-----|-------------------|--------------------|

| V <sub>DDA</sub>                   | Power supply                            | V <sub>DDA</sub> –V <sub>REF+</sub> < 1.2 V     | 1.7 <sup>(1)</sup>                                          | -   | 3.6               | V                  |

| V <sub>REF+</sub>                  | Positive reference voltage              | VDDA - VREF+ < 1.2 V                            | 1.7 <sup>(1)</sup>                                          | -   | V <sub>DDA</sub>  | V                  |

| f                                  | ADC clock frequency                     | V <sub>DDA</sub> = 1.7 <sup>(1)</sup> to 2.4 V  | 0.6                                                         | 15  | 18                | MHz                |

| f <sub>ADC</sub>                   | ADC Clock frequency                     | V <sub>DDA</sub> = 2.4 to 3.6 V                 | 0.6                                                         | 30  | 36                | MHz                |

| f <sub>TRIG</sub> <sup>(2)</sup>   | External trigger frequency              | f <sub>ADC</sub> = 30 MHz,<br>12-bit resolution | -                                                           | -   | 1764              | kHz                |

|                                    |                                         |                                                 | -                                                           | -   | 17                | 1/f <sub>ADC</sub> |

| V <sub>AIN</sub>                   | Conversion voltage range <sup>(3)</sup> |                                                 | 0 (V <sub>SSA</sub> or V <sub>REF-</sub><br>tied to ground) | -   | V <sub>REF+</sub> | V                  |

| R <sub>AIN</sub> <sup>(2)</sup>    | External input impedance                | See <i>Equation 1</i> for details               | -                                                           | -   | 50                | kΩ                 |

| R <sub>ADC</sub> <sup>(2)(4)</sup> | Sampling switch resistance              |                                                 | -                                                           | -   | 6                 | kΩ                 |

| C <sub>ADC</sub> <sup>(2)</sup>    | Internal sample and hold capacitor      |                                                 | -                                                           | 4   | 7                 | pF                 |

Table 65. ADC characteristics

## General PCB design guidelines

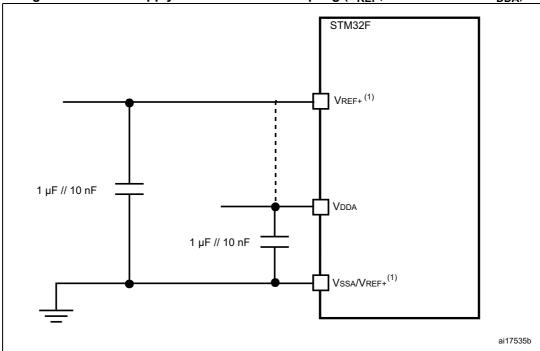

Power supply decoupling should be performed as shown in *Figure 42* or *Figure 43*, depending on whether  $V_{REF+}$  is connected to  $V_{DDA}$  or not. The 10 nF capacitors should be ceramic (good quality). They should be placed them as close as possible to the chip.

1.  $V_{REF+}$  and  $V_{REF-}$  inputs are both available on UFBGA100.  $V_{REF+}$  is also available on LQFP100. When  $V_{REF+}$  and  $V_{REF-}$  are not available, they are internally connected to  $V_{DDA}$  and  $V_{SSA}$ .

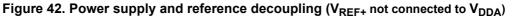

# 7.2 UFQFPN48 package information

Figure 49. UFQFPN48 - 48-lead, 7 x 7 mm, 0.5 mm pitch, ultra thin fine pitch quad flat package outline

1. Drawing is not to scale.

- 2. All leads/pads should also be soldered to the PCB to improve the lead/pad solder joint life.

- 3. There is an exposed die pad on the underside of the UFQFPN package. It is recommended to connect and solder this back-side pad to PCB ground.

# Table 81. UFQFPN48 - 48-lead, 7 x 7 mm, 0.5 mm pitch, ultra thin fine pitch quad flat package mechanical data

| Symbol |       | millimeters |       |        | inches <sup>(1)</sup> |        |

|--------|-------|-------------|-------|--------|-----------------------|--------|

| Symbol | Min.  | Тур.        | Max.  | Min.   | Тур.                  | Max.   |

| A      | 0.500 | 0.550       | 0.600 | 0.0197 | 0.0217                | 0.0236 |

| A1     | 0.000 | 0.020       | 0.050 | 0.0000 | 0.0008                | 0.0020 |

| D      | 6.900 | 7.000       | 7.100 | 0.2717 | 0.2756                | 0.2795 |

| E      | 6.900 | 7.000       | 7.100 | 0.2717 | 0.2756                | 0.2795 |

| D2     | 5.500 | 5.600       | 5.700 | 0.2165 | 0.2205                | 0.2244 |

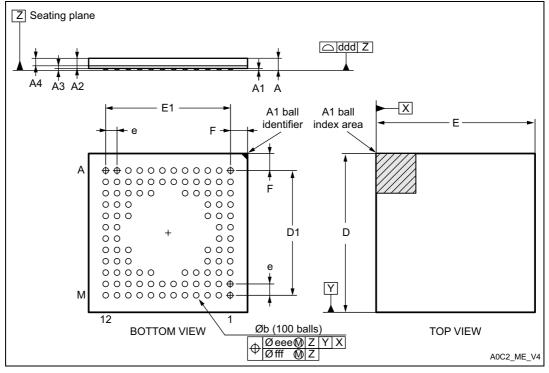

# 7.5 UFBGA100 package information

Figure 58. UFBGA100 - 100-ball, 7 x 7 mm, 0.50 mm pitch, ultra fine pitch ball grid array package outline

1. Drawing is not to scale.

| Table 84. UFBGA100, 7 x 7 mm, 0.50 mm pitch, ultra fine pitch ball grid array package |

|---------------------------------------------------------------------------------------|

| mechanical data                                                                       |

| Cumhal |       |       |       | inches <sup>(1)</sup> |        |        |

|--------|-------|-------|-------|-----------------------|--------|--------|

| Symbol | Min.  | Тур.  | Max.  | Min.                  | Тур.   | Max.   |

| А      | 0.460 | 0.530 | 0.600 | 0.0181                | 0.0209 | 0.0236 |

| A1     | 0.050 | 0.080 | 0.110 | 0.0020                | 0.0031 | 0.0043 |

| A2     | 0.400 | 0.450 | 0.500 | 0.0157                | 0.0177 | 0.0197 |

| A3     | -     | 0.130 | -     | -                     | 0.0051 | -      |

| A4     | 0.270 | 0.320 | 0.370 | 0.0106                | 0.0126 | 0.0146 |

| b      | 0.200 | 0.250 | 0.300 | 0.0079                | 0.0098 | 0.0118 |

| D      | 6.950 | 7.000 | 7.050 | 0.2736                | 0.2756 | 0.2776 |

| D1     | 5.450 | 5.500 | 5.550 | 0.2146                | 0.2165 | 0.2185 |

| E      | 6.950 | 7.000 | 7.050 | 0.2736                | 0.2756 | 0.2776 |

| E1     | 5.450 | 5.500 | 5.550 | 0.2146                | 0.2165 | 0.2185 |

| е      | -     | 0.500 | -     | -                     | 0.0197 | -      |

| F      | 0.700 | 0.750 | 0.800 | 0.0276                | 0.0295 | 0.0315 |

# 7.6 Thermal characteristics

The maximum chip junction temperature (T<sub>J</sub>max) must never exceed the values given in *Table 14: General operating conditions on page 59.*

The maximum chip-junction temperature,  $T_J$  max., in degrees Celsius, may be calculated using the following equation:

$T_J \max = T_A \max + (PD \max x \Theta_{JA})$

Where:

- T<sub>A</sub> max is the maximum ambient temperature in °C,

- $\Theta_{JA}$  is the package junction-to-ambient thermal resistance, in ° C/W,

- PD max is the sum of P<sub>INT</sub> max and P<sub>I/O</sub> max (PD max = P<sub>INT</sub> max + P<sub>I/O</sub>max),

- P<sub>INT</sub> max is the product of I<sub>DD</sub> and V<sub>DD</sub>, expressed in Watts. This is the maximum chip internal power.

$\mathsf{P}_{\mathsf{I}\!/\!\mathsf{O}}$  max represents the maximum power dissipation on output pins where:

$\mathsf{P}_{\mathsf{I/O}} \max = \Sigma \; (\mathsf{V}_{\mathsf{OL}} \times \mathsf{I}_{\mathsf{OL}}) + \Sigma ((\mathsf{V}_{\mathsf{DD}} - \mathsf{V}_{\mathsf{OH}}) \times \mathsf{I}_{\mathsf{OH}}),$

taking into account the actual V\_{OL} / I\_{OL} and V\_{OH} / I\_{OH} of the I/Os at low and high level in the application.

| Symbol          | Parameter                                       | Value | Unit |

|-----------------|-------------------------------------------------|-------|------|

|                 | Thermal resistance junction-ambient<br>UFQFPN48 | 32    |      |

| Θ <sub>JA</sub> | Thermal resistance junction-ambient<br>WLCSP49  | 51    |      |

|                 | Thermal resistance junction-ambient<br>LQFP64   | 47    | °C/W |

|                 | Thermal resistance junction-ambient<br>LQFP100  | 43    |      |

|                 | Thermal resistance junction-ambient<br>UFBGA100 | 62    |      |

#### Table 85. Package thermal characteristics

### 7.6.1 Reference document

JESD51-2 Integrated Circuits Thermal Test Method Environment Conditions - Natural Convection (Still Air). Available from www.jedec.org.

# **B.3** Batch Acquisition Mode (BAM) example

Data is transferred through the DMA from interfaces into the internal SRAM while the rest of the MCU is set in low power mode.

- Code execution from RAM before switching off the Flash.

- Flash is set in power down and flash interface (ART<sup>™</sup> accelerator) clock is stopped.

- The clocks are enabled only for the required interfaces.

- MCU core is set in sleep mode (core clock stopped waiting for interrupt).

- Only the needed DMA channels are enabled and running.

### Figure 65. Batch Acquisition Mode (BAM) example