Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

#### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Product Status             | Active                                                                  |

|----------------------------|-------------------------------------------------------------------------|

| Core Processor             | ARM® Cortex®-M4                                                         |

| Core Size                  | 32-Bit Single-Core                                                      |

| Speed                      | 100MHz                                                                  |

| Connectivity               | I <sup>2</sup> C, IrDA, LINbus, MMC/SD/SDIO, SPI, UART/USART, USB OTG   |

| Peripherals                | Brown-out Detect/Reset, DMA, I <sup>2</sup> S, POR, PWM, WDT            |

| Number of I/O              | 50                                                                      |

| Program Memory Size        | 512KB (512K x 8)                                                        |

| Program Memory Type        | FLASH                                                                   |

| EEPROM Size                | -                                                                       |

| RAM Size                   | 128K x 8                                                                |

| Voltage - Supply (Vcc/Vdd) | 1.7V ~ 3.6V                                                             |

| Data Converters            | A/D 16x12b                                                              |

| Oscillator Type            | Internal                                                                |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                       |

| Mounting Type              | Surface Mount                                                           |

| Package / Case             | 64-LQFP                                                                 |

| Supplier Device Package    | 64-LQFP (10x10)                                                         |

| Purchase URL               | https://www.e-xfl.com/product-detail/stmicroelectronics/stm32f411ret6tr |

|                            |                                                                         |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

7

8

|          |      | 6.3.5    | Embedded reset and power control block characteristics      | 66       |

|----------|------|----------|-------------------------------------------------------------|----------|

|          |      | 6.3.6    | Supply current characteristics                              | 67       |

|          |      | 6.3.7    | Wakeup time from low-power modes                            | 81       |

|          |      | 6.3.8    | External clock source characteristics                       | 82       |

|          |      | 6.3.9    | Internal clock source characteristics                       | 86       |

|          |      | 6.3.10   | PLL characteristics                                         | 88       |

|          |      | 6.3.11   | PLL spread spectrum clock generation (SSCG) characteristics | 90       |

|          |      | 6.3.12   | Memory characteristics                                      | 91       |

|          |      | 6.3.13   | EMC characteristics                                         | 93       |

|          |      | 6.3.14   | Absolute maximum ratings (electrical sensitivity)           | 95       |

|          |      | 6.3.15   | I/O current injection characteristics                       | 96       |

|          |      | 6.3.16   | I/O port characteristics                                    | 97       |

|          |      | 6.3.17   | NRST pin characteristics                                    | 103      |

|          |      | 6.3.18   | TIM timer characteristics                                   | 104      |

|          |      | 6.3.19   | Communications interfaces                                   | 104      |

|          |      | 6.3.20   | 12-bit ADC characteristics                                  | 113      |

|          |      | 6.3.21   | Temperature sensor characteristics                          | 119      |

|          |      | 6.3.22   | V <sub>BAT</sub> monitoring characteristics                 | 120      |

|          |      | 6.3.23   | Embedded reference voltage                                  | 120      |

|          |      | 6.3.24   | SD/SDIO MMC/eMMC card host interface (SDIO) characteristics | 121      |

|          |      | 6.3.25   | RTC characteristics                                         | 123      |

| 7        | Pack | age info | ormation                                                    | 124      |

|          | 7.1  | -        | P49 package information                                     |          |

|          | 7.2  |          | N48 package information                                     |          |

|          | 7.3  |          | 4 package information                                       |          |

|          |      |          |                                                             |          |

|          | 7.4  |          | 00 package information                                      |          |

|          | 7.5  | UFBGA    | 100 package information                                     | 137      |

|          | 7.6  | Therma   | al characteristics                                          | 140      |

|          |      | 7.6.1    | Reference document                                          | 140      |

| 8        | Part | number   | ing                                                         | 141      |

| Appendix | A R  | lecomm   | endations when using the internal reset OFF                 | 142      |

|          | A.1  | Operati  | ng conditions                                               | 142      |

| Appendix | B A  | pplicati | on block diagrams                                           | 143      |

|          |      |          |                                                             | <b>—</b> |

| 4/149    |      |          | DocID026289 Rev 6                                           | <b>\</b> |

# 3.4 Memory protection unit

The memory protection unit (MPU) is used to manage the CPU accesses to memory to prevent one task to accidentally corrupt the memory or resources used by any other active task. This memory area is organized into up to 8 protected areas that can in turn be divided up into 8 subareas. The protection area sizes are between 32 bytes and the whole 4 gigabytes of addressable memory.

The MPU is especially helpful for applications where some critical or certified code has to be protected against the misbehavior of other tasks. It is usually managed by an RTOS (real-time operating system). If a program accesses a memory location that is prohibited by the MPU, the RTOS can detect it and take action. In an RTOS environment, the kernel can dynamically update the MPU area setting, based on the process to be executed.

The MPU is optional and can be bypassed for applications that do not need it.

# 3.5 Embedded Flash memory

The devices embed up to 512 Kbytes of Flash memory available for storing programs and data.

To optimize the power consumption the Flash memory can also be switched off in Run or in Sleep mode (see Section 3.18: Low-power modes). Two modes are available: Flash in Stop mode or in DeepSleep mode (trade off between power saving and startup time, see Table 34: Low-power mode wakeup timings(1)). Before disabling the Flash memory, the code must be executed from the internal RAM.

### One-time programmable bytes

A one-time programmable area is available with 16 OTP blocks of 32 bytes. Each block can be individually locked.

(Additional information can be found in the product reference manual.)

# 3.6 CRC (cyclic redundancy check) calculation unit

The CRC (cyclic redundancy check) calculation unit is used to get a CRC code from a 32-bit data word and a fixed generator polynomial.

Among other applications, CRC-based techniques are used to verify data transmission or storage integrity. In the scope of the EN/IEC 60335-1 standard, they offer a means of verifying the Flash memory integrity. The CRC calculation unit helps compute a software signature during runtime, to be compared with a reference signature generated at link-time and stored at a given memory location.

# 3.7 Embedded SRAM

All devices embed:

128 Kbytes of system SRAM which can be accessed (read/write) at CPU clock speed with 0 wait states

DocID026289 Rev 6

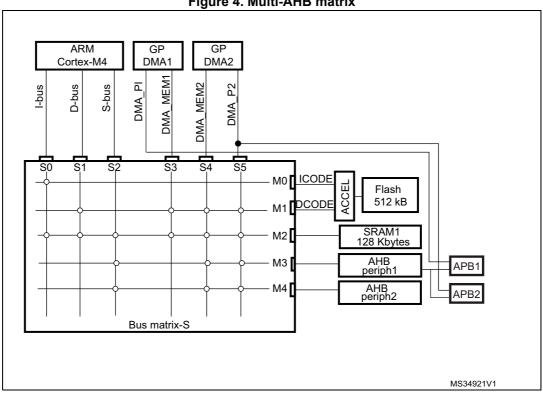

# 3.8 Multi-AHB bus matrix

The 32-bit multi-AHB bus matrix interconnects all the masters (CPU, DMAs) and the slaves (Flash memory, RAM, AHB and APB peripherals) and ensures a seamless and efficient operation even when several high-speed peripherals work simultaneously.

# 3.9 DMA controller (DMA)

The devices feature two general-purpose dual-port DMAs (DMA1 and DMA2) with 8 streams each. They are able to manage memory-to-memory, peripheral-to-memory and memory-to-peripheral transfers. They feature dedicated FIFOs for APB/AHB peripherals, support burst transfer and are designed to provide the maximum peripheral bandwidth (AHB/APB).

The two DMA controllers support circular buffer management, so that no specific code is needed when the controller reaches the end of the buffer. The two DMA controllers also have a double buffering feature, which automates the use and switching of two memory buffers without requiring any special code.

Each stream is connected to dedicated hardware DMA requests, with support for software trigger on each stream. Configuration is made by software and transfer sizes between source and destination are independent.

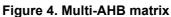

Figure 7. Startup in regulator OFF: slow V<sub>DD</sub> slope - power-down reset risen after V<sub>CAP 1</sub>/V<sub>CAP 2</sub> stabilization

1. This figure is valid whatever the internal reset mode (ON or OFF).

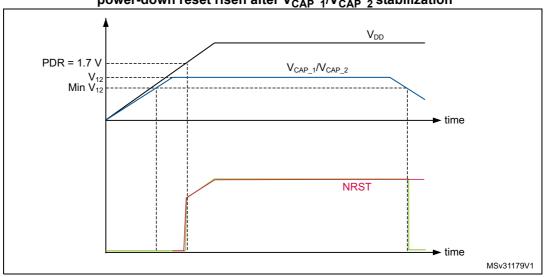

# Figure 8. Startup in regulator OFF mode: fast $V_{DD}$ slope - power-down reset risen before $V_{CAP\_1}/V_{CAP\_2}$ stabilization

1. This figure is valid whatever the internal reset mode (ON or OFF).

## STM32F411xC STM32F411xE

|   |                  |        |       |        |       |       |            |       | -      |        |           |        |

|---|------------------|--------|-------|--------|-------|-------|------------|-------|--------|--------|-----------|--------|

|   | 1                | 2      | 3     | 4      | 5     | 6     | 7          | 8     | 9      | 10     | 11        | 12     |

| A | (PE3)            | (PE1)  | (РВ8) | (BOO)0 | (PD7) | (PD5) | РВ4        | (РВЗ) | (PA15) | (PA14) | PA13      | (PA12) |

| в | PE4              | (PE2)  | (PB9) | (PB7)  | (PB6) | (PD6) |            | (PD3) | (PD1)  | C12    | PC10      | (PA11) |

| с |                  | MP PE5 | (PE0) | VDD    | (PB5) |       | <br>       | (PD2) | PD0    | C11    | (CAP<br>2 | PA10   |

| D | FC14<br>OSC32_IN | PE6    | VSS   |        |       |       | <br>       |       |        | (PA9)  | (PA8)     | PC9    |

| E | PC15)<br>05C32_0 | VBAT   | BYPAS | S_REG  |       |       |            |       |        | PC8    | PC7       | PC6    |

| F | PH0<br>SC N      | VSS    |       |        |       |       | <br> <br>+ |       |        |        | VSS       | vss    |

| G | PH1<br>OSCOL     |        |       |        |       |       | <br>       |       |        |        | VDD       | VDD    |

| н | PCO              | NRS    |       | DN     |       |       | <br>       |       |        | D15    | PD14      | PD13   |

| J | VSSA             | PC1    | PC2   |        |       |       |            |       |        | ©D12   | PD11      | PD10   |

| к | VRET-            | PC3    | (PA2) | (PA5)  | (PC4) |       | <br>       | (PD9) | (PB11) | PB15   | PB14      | PB13   |

| L | VREF+            | PAO    | (PA3) | (PA6)  | PC5   | (PB2) | (PE8)      | PE10  | PE12   | PB10   | (VCAP)    | PB12   |

| м | VDDA             | (PA1)  | (PA4) | (PA7)  | (PB0) | (PB1) | PE7        | (PE9) | (PE11) | PE13   | PE14      | PE15   |

## Figure 13. STM32F411xC/xE UFBGA100 pinout

1. This figure shows the package top view

|          | Pir    | n numt  | ber     |          |                                                      |          |               |       |                                                                                                     |                      |

|----------|--------|---------|---------|----------|------------------------------------------------------|----------|---------------|-------|-----------------------------------------------------------------------------------------------------|----------------------|

| UFQFPN48 | LQFP64 | WLCSP49 | LQFP100 | UFBGA100 | Pin name<br>(function after<br>reset) <sup>(1)</sup> | Pin type | I/O structure | Notes | Alternate functions                                                                                 | Additional functions |

| 31       | 43     | C2      | 69      | C12      | PA10                                                 | I/O      | FT            | -     | TIM1_CH3,<br>SPI5_MOSI/I2S5_SD,<br>USART1_RX,<br>USB_FS_ID,<br>EVENTOUT                             | -                    |

| 32       | 44     | C1      | 70      | B12      | PA11                                                 | I/O      | FT            | -     | TIM1_CH4,<br>SPI4_MISO,<br>USART1_CTS,<br>USART6_TX,<br>USB_FS_DM,<br>EVENTOUT                      | -                    |

| 33       | 45     | C3      | 71      | A12      | PA12                                                 | I/O      | FT            | -     | TIM1_ETR,<br>SPI5_MISO,<br>USART1_RTS,<br>USART6_RX,<br>USB_FS_DP,<br>EVENTOUT                      | -                    |

| 34       | 46     | B3      | 72      | A11      | PA13                                                 | I/O      | FT            | -     | JTMS-SWDIO,<br>EVENTOUT                                                                             | -                    |

| -        | -      | -       | 73      | C11      | VCAP_2                                               | S        | -             | -     | -                                                                                                   | -                    |

| 35       | 47     | B1      | 74      | F11      | VSS                                                  | S        | -             | -     | -                                                                                                   | -                    |

| 36       | 48     | B2      | 75      | G11      | VDD                                                  | S        | -             | -     | -                                                                                                   | -                    |

| 37       | 49     | A1      | 76      | A10      | PA14                                                 | I/O      | FT            | -     | JTCK-SWCLK,<br>EVENTOUT                                                                             | -                    |

| 38       | 50     | A2      | 77      | A9       | PA15                                                 | I/O      | FT            | -     | JTDI,<br>TIM2_CH1/TIM2_ETR<br>,<br>SPI1_NSS/I2S1_WS,<br>SPI3_NSS/I2S3_WS,<br>USART1_TX,<br>EVENTOUT | -                    |

| -        | 51     | -       | 78      | B11      | PC10                                                 | I/O      | FT            | -     | SPI3_SCK/I2S3_CK,<br>SDIO_D2,<br>EVENTOUT                                                           | -                    |

| -        | 52     | -       | 79      | C10      | PC11                                                 | I/O      | FT            | -     | I2S3ext_SD,<br>SPI3_MISO,<br>SDIO_D3,<br>EVENTOUT                                                   | -                    |

| -        | 53     | -       | 80      | B10      | PC12                                                 | I/O      | FT            | -     | SPI3_MOSI/I2S3_SD,<br>SDIO_CK,<br>EVENTOUT                                                          | -                    |

| Operating<br>power<br>supply<br>range            | ADC<br>operation                     | Maximum<br>Flash<br>memory<br>access<br>frequency<br>with no wait<br>states<br>(f <sub>Flashmax</sub> ) | Maximum Flash<br>memory access<br>frequency with<br>wait states <sup>(1)(2)</sup> | I/O operation                                      | Clock output<br>frequency on<br>I/O pins <sup>(3)</sup>                                                       | Possible<br>Flash<br>memory<br>operations |

|--------------------------------------------------|--------------------------------------|---------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------|----------------------------------------------------|---------------------------------------------------------------------------------------------------------------|-------------------------------------------|

| V <sub>DD</sub> = 2.4 to<br>2.7 V                | Conversion<br>time up to<br>2.4 Msps | 24 MHz                                                                                                  | 100 MHz with 4<br>wait states                                                     | <ul> <li>I/O compensation works</li> </ul>         | up to 50 MHz                                                                                                  | 16-bit erase<br>and program<br>operations |

| V <sub>DD</sub> = 2.7 to<br>3.6 V <sup>(6)</sup> | Conversion<br>time up to<br>2.4 Msps | 30 MHz                                                                                                  | 100 MHz with 3<br>wait states                                                     | <ul> <li>I/O<br/>compensation<br/>works</li> </ul> | - up to<br>100 MHz<br>when $V_{DD}$ =<br>3.0 to 3.6 V<br>- up to<br>50 MHz<br>when $V_{DD}$ =<br>2.7 to 3.0 V | 32-bit erase<br>and program<br>operations |

### Table 15. Features depending on the operating power supply range (continued)

1. Applicable only when the code is executed from Flash memory. When the code is executed from RAM, no wait state is required.

- 2. Thanks to the ART accelerator and the 128-bit Flash memory, the number of wait states given here does not impact the execution speed from Flash memory since the ART accelerator allows to achieve a performance equivalent to 0 wait state program execution.

- 3. Refer to Table 55: I/O AC characteristics for frequencies vs. external load.

- V<sub>DD</sub>/V<sub>DDA</sub> minimum value of 1.7 V, with the use of an external power supply supervisor (refer to Section 3.15.2: Internal reset OFF).

- 5. Prefetch is not available. Refer to AN3430 application note for details on how to adjust performance and power.

- The voltage range for the USB full speed embedded PHY can drop down to 2.7 V. However the electrical characteristics of D- and D+ pins will be degraded between 2.7 and 3 V.

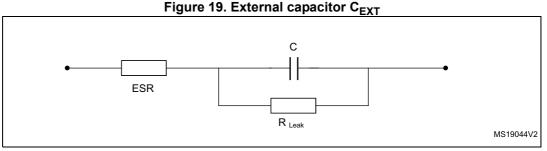

# 6.3.2 VCAP\_1/VCAP\_2 external capacitors

Stabilization for the main regulator is achieved by connecting the external capacitor  $C_{EXT}$  to the VCAP\_1 and VCAP\_2 pins. For packages supporting only 1 VCAP pin, the 2 CEXT capacitors are replaced by a single capacitor.

C<sub>EXT</sub> is specified in *Table 16*.

1. Legend: ESR is the equivalent series resistance.

DocID026289 Rev 6

| Symbol | Parameter                                                          | Conditions |  |  |  |  |  |  |  |

|--------|--------------------------------------------------------------------|------------|--|--|--|--|--|--|--|

| CEXT   | Capacitance of external capacitor with a single VCAP pin available | 4.7 µF     |  |  |  |  |  |  |  |

| ESR    | ESR of external capacitor with a single VCAP pin available         | <1Ω        |  |  |  |  |  |  |  |

### Table 16. VCAP\_1/VCAP\_2 operating conditions<sup>(1)</sup>

When bypassing the voltage regulator, the two 2.2 μF V<sub>CAP</sub> capacitors are not required and should be replaced by two 100 nF decoupling capacitors.

## 6.3.3 Operating conditions at power-up/power-down (regulator ON)

Subject to general operating conditions for  $T_A$ .

### Table 17. Operating conditions at power-up / power-down (regulator ON)

| Symbol           | Parameter                      | Min | Мах | Unit  |

|------------------|--------------------------------|-----|-----|-------|

| 1                | V <sub>DD</sub> rise time rate | 20  | ∞   | us/V  |

| <sup>L</sup> VDD | V <sub>DD</sub> fall time rate | 20  | ∞   | μ5/ ν |

## 6.3.4 Operating conditions at power-up / power-down (regulator OFF)

Subject to general operating conditions for T<sub>A</sub>.

### Table 18. Operating conditions at power-up / power-down (regulator OFF)<sup>(1)</sup>

| Symbol            | Parameter                                    | Conditions | Min | Max | Unit |

|-------------------|----------------------------------------------|------------|-----|-----|------|

| +                 | V <sub>DD</sub> rise time rate               | Power-up   | 20  | ~   |      |

| t <sub>VDD</sub>  | V <sub>DD</sub> fall time rate               | Power-down | 20  | ~   | us/V |

| +                 | $V_{CAP\_1}$ and $V_{CAP\_2}$ rise time rate | Power-up   | 20  | ~   | μ5/ν |

| <sup>I</sup> VCAP | $V_{CAP\_1}$ and $V_{CAP\_2}$ fall time rate | Power-down | 20  | ~   |      |

1. To reset the internal logic at power-down, a reset must be applied on pin PA0 when  $V_{\text{DD}}$  reach below 1.08 V.

Note: This feature is only available for UFBGA100 package.

| (ART accelerator enabled except prefetch) running from Flash memory - $V_{DD}$ = 3.6 V |                |                                                                               |                           |                           |                           |                            |                            |      |      |  |

|----------------------------------------------------------------------------------------|----------------|-------------------------------------------------------------------------------|---------------------------|---------------------------|---------------------------|----------------------------|----------------------------|------|------|--|

|                                                                                        |                |                                                                               | £                         |                           |                           | Ma                         | x <sup>(1)</sup>           |      |      |  |

| Symbol Parameter                                                                       | Conditions     | f <sub>HCLK</sub><br>(MHz)                                                    | Тур                       | T <sub>A</sub> =<br>25 °C | T <sub>A</sub> =<br>85 °C | T <sub>A</sub> =<br>105 °C | T <sub>A</sub> =<br>125 °C | Unit |      |  |

|                                                                                        |                |                                                                               | 100                       | 20.7                      | 22.2                      | 22.5                       | 23.2                       | 24.4 |      |  |

|                                                                                        |                | External clock, PLL                                                           | 84                        | 16.8                      | 18.0                      | 18.3                       | 19.0                       | 20.1 |      |  |

|                                                                                        |                | ON <sup>(2)</sup> ,<br>all peripherals                                        | 64                        | 11.8                      | 12.7                      | 12.9                       | 13.6                       | 14.6 |      |  |

|                                                                                        |                | enabled <sup>(3)(4)</sup>                                                     | enabled <sup>(3)(4)</sup> | 50                        | 9.3                       | 10.2                       | 10.4                       | 11.1 | 12.0 |  |

|                                                                                        |                |                                                                               | 20                        | 4.8                       | 5.5                       | 5.8                        | 6.5                        | 7.4  | mA   |  |

|                                                                                        |                | HSI, PLL OFF <sup>(2)</sup> , all peripherals enabled <sup>(3)</sup>          | 16                        | 3.0                       | 3.3                       | 3.8                        | 4.5                        | 5.4  |      |  |

|                                                                                        | Supply current |                                                                               | 1                         | 0.7                       | 1.0                       | 1.4                        | 2.1                        | 3.0  |      |  |

| I <sub>DD</sub>                                                                        | in Run mode    |                                                                               | 100                       | 11.6                      | 12.6                      | 12.9                       | 13.6                       | 14.8 | ШA   |  |

|                                                                                        |                |                                                                               | 84                        | 9.7                       | 10.2 <sup>(5)</sup>       | 11.1                       | 11.3                       | 12.5 | -    |  |

|                                                                                        |                | External clock, PLL ON <sup>(2)</sup> all peripherals disabled <sup>(3)</sup> | 64                        | 6.7                       | 7.4                       | 7.7                        | 8.3                        | 9.4  |      |  |

|                                                                                        |                |                                                                               | 50                        | 5.4                       | 6.0                       | 6.3                        | 7.0                        | 8.0  |      |  |

|                                                                                        |                |                                                                               | 20                        | 2.9                       | 3.4                       | 3.7                        | 4.4                        | 5.4  |      |  |

|                                                                                        |                | HSI, PLL OFF <sup>(2)</sup> , all                                             | 16                        | 1.9                       | 2.2                       | 2.6                        | 3.3                        | 4.3  |      |  |

|                                                                                        |                | peripherals disabled <sup>(3)</sup>                                           | 1                         | 0.7                       | 0.9                       | 1.3                        | 2.1                        | 3.1  |      |  |

# Table 23. Typical and maximum current consumption in run mode, code with data processing(ART accelerator enabled except prefetch) running from Flash memory - V<sub>DD</sub> = 3.6 V

1. Guaranteed by characterization results.

2. Refer to Table 41 and RM0383 for the possible PLL VCO setting

3. Add an additional power consumption of 1.6 mA per ADC for the analog part. In applications, this consumption occurs only while the ADC is ON (ADON bit is set in the ADC\_CR2 register).

4. When the ADC is ON (ADON bit set in the ADC\_CR2), add an additional power consumption of 1.6mA per ADC for the analog part.

5. Guaranteed by test in production.

|                 |                |                                                                               |                            |      |                           | Ма                        | x <sup>(1)</sup>           |                            |      |

|-----------------|----------------|-------------------------------------------------------------------------------|----------------------------|------|---------------------------|---------------------------|----------------------------|----------------------------|------|

| Symbol Param    | Parameter      | Conditions                                                                    | f <sub>HCLK</sub><br>(MHz) | Тур  | T <sub>A</sub> =<br>25 °C | T <sub>A</sub> =<br>85 °C | T <sub>A</sub> =<br>105 °C | T <sub>A</sub> =<br>125 °C | Unit |

|                 |                |                                                                               | 100                        | 29.5 | 31.5                      | 32.3                      | 33.3                       | 34.7                       |      |

|                 |                | External clock, PLL                                                           | 84                         | 25.5 | 27.1                      | 27.9                      | 28.9                       | 30.2                       |      |

|                 |                | ON <sup>(2)</sup> ,<br>all peripherals                                        | 64                         | 18.6 | 19.8                      | 20.4                      | 21.2                       | 22.4                       |      |

|                 |                | enabled <sup>(3)(4)</sup>                                                     | 50                         | 15.2 | 16.4                      | 16.9                      | 17.7                       | 18.7                       | mA   |

|                 |                |                                                                               | 20                         | 7.6  | 8.4                       | 8.8                       | 9.5                        | 10.5                       |      |

|                 |                | HSI, PLL OFF <sup>(2)</sup> , all peripherals enabled <sup>(3)</sup>          | 16                         | 4.8  | 5.2                       | 5.7                       | 6.5                        | 7.5                        |      |

|                 | Supply current |                                                                               | 1                          | 0.9  | 1.3                       | 1.6                       | 2.4                        | 3.4                        |      |

| I <sub>DD</sub> | in Run mode    | External clock, PLL ON <sup>(2)</sup> all peripherals disabled <sup>(3)</sup> | 100                        | 20.4 | 21.8                      | 22.7                      | 23.8                       | 25.1                       | mA   |

|                 |                |                                                                               | 84                         | 18.4 | 19.2 <sup>(5)</sup>       | 20.9                      | 21.1                       | 22.4                       | -    |

|                 |                |                                                                               | 64                         | 13.5 | 14.5                      | 15.2                      | 15.9                       | 17.2                       |      |

|                 |                |                                                                               | 50                         | 11.3 | 12.2                      | 12.8                      | 13.6                       | 14.7                       |      |

|                 |                |                                                                               | 20                         | 5.6  | 6.4                       | 6.7                       | 7.4                        | 8.5                        |      |

|                 |                | HSI, PLL OFF <sup>(2)</sup> , all                                             | 16                         | 3.6  | 4.1                       | 4.5                       | 5.2                        | 6.3                        |      |

|                 |                | peripherals disabled <sup>(3)</sup>                                           | 1                          | 0.9  | 1.2                       | 1.6                       | 2.3                        | 3.4                        |      |

# Table 24. Typical and maximum current consumption in run mode, code with data processing<br/>(ART accelerator disabled) running from Flash memory - $V_{DD}$ = 3.6 V

1. Guaranteed by characterization results.

2. Refer to Table 41 and RM0383 for the possible PLL VCO setting

3. Add an additional power consumption of 1.6 mA per ADC for the analog part. In applications, this consumption occurs only while the ADC is ON (ADON bit is set in the ADC\_CR2 register).

4. When the ADC is ON (ADON bit set in the ADC\_CR2), add an additional power consumption of 1.6mA per ADC for the analog part.

5. Guaranteed by test in production.

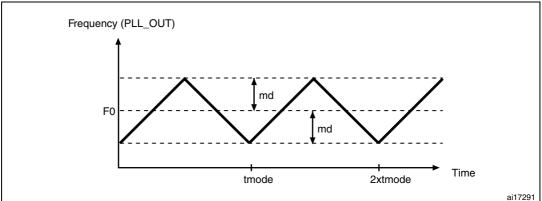

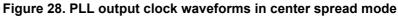

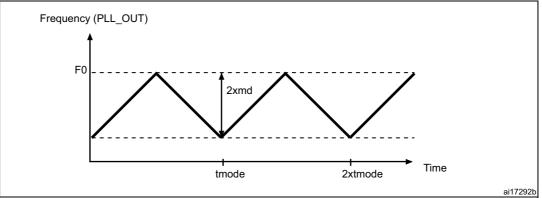

*Figure 28* and *Figure 29* show the main PLL output clock waveforms in center spread and down spread modes, where:

F0 is  $f_{PLL_OUT}$  nominal.

$T_{mode}$  is the modulation period.

md is the modulation depth.

## 6.3.12 Memory characteristics

### **Flash memory**

The characteristics are given at  $T_A$  = - 40 to 125 °C unless otherwise specified.

The devices are shipped to customers with the Flash memory erased.

| Symbol                         | Parameter | Conditions                                  | Min | Тур | Мах | Unit |

|--------------------------------|-----------|---------------------------------------------|-----|-----|-----|------|

|                                |           | Write / Erase 8-bit mode, $V_{DD}$ = 1.7 V  | -   | 5   | -   |      |

| I <sub>DD</sub> Supply current |           | Write / Erase 16-bit mode, $V_{DD}$ = 2.1 V | -   | 8   | -   | mA   |

|                                |           | Write / Erase 32-bit mode, $V_{DD}$ = 3.3 V | -   | 12  | -   |      |

| Symbol                         | Parameter                                               |                                               | Conditions        | Min | Тур | Мах | Unit |

|--------------------------------|---------------------------------------------------------|-----------------------------------------------|-------------------|-----|-----|-----|------|

| R <sub>PU</sub>                | Weak pull-up<br>equivalent<br>resistor <sup>(6)</sup>   | All pins<br>except for<br>PA10<br>(OTG_FS_ID) | $V_{IN} = V_{SS}$ | 30  | 40  | 50  |      |

|                                |                                                         | PA10<br>(OTG_FS_ID)                           | -                 | 7   | 10  | 14  | kΩ   |

| R <sub>PD</sub>                | Weak pull-down<br>equivalent<br>resistor <sup>(7)</sup> | All pins<br>except for<br>PA10<br>(OTG_FS_ID) | $V_{IN} = V_{DD}$ | 30  | 40  | 50  | N22  |

|                                |                                                         | PA10<br>(OTG_FS_ID)                           | -                 | 7   | 10  | 14  |      |

| C <sub>IO</sub> <sup>(8)</sup> | I/O pin capacitance                                     |                                               | _                 | -   | 5   | -   | pF   |

Table 53. I/O static characteristics (continued)

1. Guaranteed by test in production.

2. Guaranteed by design.

3. With a minimum of 200 mV.

- 4. Leakage could be higher than the maximum value, if negative current is injected on adjacent pins, Refer to Table 52: I/O current injection susceptibility

- To sustain a voltage higher than VDD +0.3 V, the internal pull-up/pull-down resistors must be disabled. Leakage could be higher than the maximum value, if negative current is injected on adjacent pins.Refer to Table 52: I/O current injection susceptibility

- 6. Pull-up resistors are designed with a true resistance in series with a switchable PMOS. This PMOS contribution to the series resistance is minimum (~10% order).

- Pull-down resistors are designed with a true resistance in series with a switchable NMOS. This NMOS contribution to the series resistance is minimum (~10% order).

- 8. Hysteresis voltage between Schmitt trigger switching levels. Guaranteed by characterization results.

All I/Os are CMOS and TTL compliant (no software configuration required). Their characteristics cover more than the strict CMOS-technology or TTL parameters. The coverage of these requirements for FT and TC I/Os is shown in *Figure 30*.

| OSPEEDRy<br>[1:0] bit<br>value <sup>(1)</sup> | Symbol                                           | Parameter                                                       | Conditions                                       | Min | Тур | Мах                | Unit |

|-----------------------------------------------|--------------------------------------------------|-----------------------------------------------------------------|--------------------------------------------------|-----|-----|--------------------|------|

|                                               |                                                  |                                                                 | C <sub>L</sub> = 30 pF, V <sub>DD</sub> ≥ 2.70 V | -   | -   | 100 <sup>(4)</sup> |      |

|                                               | F <sub>max(IO)out</sub>                          | Maximum frequency <sup>(3)</sup>                                | C <sub>L</sub> = 30 pF, V <sub>DD</sub> ≥ 1.7 V  | -   | -   | 50 <sup>(4)</sup>  | MHz  |

|                                               |                                                  |                                                                 | C <sub>L</sub> = 30 pF, V <sub>DD</sub> ≥ 2.70 V | -   | -   | 4                  |      |

| 11                                            | t <sub>f(IO)out</sub> /<br>t <sub>r(IO)out</sub> | time and output low to high                                     | C <sub>L</sub> = 30 pF, V <sub>DD</sub> ≥ 1.7 V  | -   | -   | 6                  | ns   |

|                                               |                                                  |                                                                 | C <sub>L</sub> = 10 pF, V <sub>DD</sub> ≥ 2.70 V | -   | -   | 2.5                | 115  |

|                                               |                                                  |                                                                 | C <sub>L</sub> = 10 pF, V <sub>DD</sub> ≥ 1.7 V  | -   | -   | 4                  |      |

| -                                             | t <sub>EXTIpw</sub>                              | Pulse width of external signals detected by the EXTI controller |                                                  | 10  | -   | -                  | ns   |

Table 55. I/O AC characteristics<sup>(1)(2)</sup> (continued)

1. Guaranteed by characterization results.

2. The I/O speed is configured using the OSPEEDRy[1:0] bits. Refer to the STM32F4xx reference manual for a description of the GPIOx\_SPEEDR GPIO port output speed register.

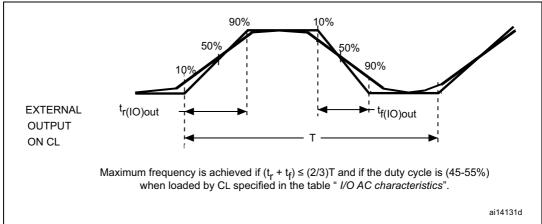

3. The maximum frequency is defined in *Figure 31*.

4. For maximum frequencies above 50 MHz and  $V_{DD}$  > 2.4 V, the compensation cell should be used.

#### Figure 31. I/O AC characteristics definition

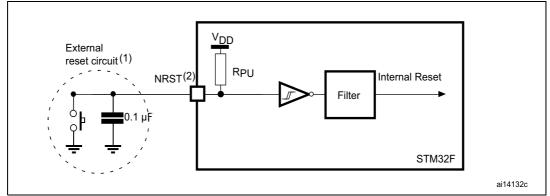

## 6.3.17 NRST pin characteristics

The NRST pin input driver uses CMOS technology. It is connected to a permanent pull-up resistor,  $R_{PU}$  (see *Table 53*).

Unless otherwise specified, the parameters given in *Table 56* are derived from tests performed under the ambient temperature and V<sub>DD</sub> supply voltage conditions summarized in *Table 14*. Refer to *Table 53: I/O static characteristics* for the values of VIH and VIL for NRST pin.

| Symbol                               | Parameter                                       | Conditions               | Min | Тур | Мах | Unit |

|--------------------------------------|-------------------------------------------------|--------------------------|-----|-----|-----|------|

| R <sub>PU</sub>                      | Weak pull-up equivalent resistor <sup>(1)</sup> | $V_{IN} = V_{SS}$        | 30  | 40  | 50  | kΩ   |

| V <sub>F(NRST)</sub> <sup>(2)</sup>  | NRST Input filtered pulse                       |                          | -   | -   | 100 | ns   |

| V <sub>NF(NRST)</sub> <sup>(2)</sup> | NRST Input not filtered pulse                   | V <sub>DD</sub> > 2.7 V  | 300 | -   | -   | ns   |

| T <sub>NRST_OUT</sub>                | Generated reset pulse duration                  | Internal Reset<br>source | 20  | -   | -   | μs   |

1. The pull-up is designed with a true resistance in series with a switchable PMOS. This PMOS contribution to the series resistance must be minimum (~10% order).

2. Guaranteed by design.

#### Figure 32. Recommended NRST pin protection

1. The reset network protects the device against parasitic resets.

The user must ensure that the level on the NRST pin can go below the V<sub>IL(NRST)</sub> max level specified in Table 56. Otherwise the reset is not taken into account by the device.

### SPI interface characteristics

Unless otherwise specified, the parameters given in *Table 60* for the SPI interface are derived from tests performed under the ambient temperature,  $f_{PCLKx}$  frequency and  $V_{DD}$  supply voltage conditions summarized in *Table 14*, with the following configuration:

- Output speed is set to OSPEEDRy[1:0] = 10

- Capacitive load C = 30 pF

- Measurement points are done at CMOS levels: 0.5V<sub>DD</sub>

Refer to Section 6.3.16: I/O port characteristics for more details on the input/output alternate function characteristics (NSS, SCK, MOSI, MISO for SPI).

| Symbol                                       | Parameter                            | Conditions                                                                | Min                    | Тур               | Мах                       | Unit |  |

|----------------------------------------------|--------------------------------------|---------------------------------------------------------------------------|------------------------|-------------------|---------------------------|------|--|

|                                              |                                      | Master full duplex/receiver mode,<br>2.7 V < $V_{DD}$ < 3.6 V<br>SPI1/4/5 | -                      | -                 | 42                        |      |  |

|                                              |                                      | Master full duplex/receiver mode,<br>3.0 V < $V_{DD}$ < 3.6 V<br>SPI1/4/5 | -                      | -                 | 50                        |      |  |

|                                              |                                      | Master transmitter mode<br>1.7 V < V <sub>DD</sub> < 3.6 V<br>SPI1/4/5    | -                      | -                 | 50                        |      |  |

| <sup>f</sup> scк<br>1/t <sub>c(SCK)</sub>    | SPI clock frequency                  | Master mode<br>1.7 V < V <sub>DD</sub> < 3.6 V<br>SPI1/2/3/4/5            | -                      | -                 | 25                        | MHz  |  |

|                                              |                                      | Slave transmitter/full duplex mode $2.7 V < V_{DD} < 3.6 V$ SPI1/4/5      |                        | -                 | 38 <sup>(2)</sup>         |      |  |

|                                              |                                      | Slave receiver mode,<br>1.8 V < V <sub>DD</sub> < 3.6 V<br>SPI1/4/5       | -                      | -                 | 50                        |      |  |

|                                              |                                      | Slave mode,<br>1.8 V < V <sub>DD</sub> < 3.6 V<br>SPI1/2/3/4/5            | -                      | -                 | 25                        |      |  |

| Duty(SCK)                                    | Duty cycle of SPI clock<br>frequency | Slave mode                                                                | 30                     | 50                | 70                        | %    |  |

| t <sub>w(SCKH)</sub><br>t <sub>w(SCKL)</sub> | SCK high and low time                | Master mode, SPI presc = 2                                                | T <sub>PCLK</sub> -1.5 | T <sub>PCLK</sub> | Т <sub>РСLК</sub><br>+1.5 | ns   |  |

| t <sub>su(NSS)</sub>                         | NSS setup time                       | Slave mode, SPI presc = 2                                                 | 3T <sub>PCLK</sub>     | -                 | -                         | ns   |  |

| t <sub>h(NSS)</sub>                          | NSS hold time                        | Slave mode, SPI presc = 2                                                 | 2T <sub>PCLK</sub>     | -                 | -                         | ns   |  |

| t <sub>su(MI)</sub>                          | Data input setup time                | Master mode                                                               | 4                      | -                 | -                         | ns   |  |

| t <sub>su(SI)</sub>                          |                                      | Slave mode                                                                | 2.5                    | -                 | -                         | ns   |  |

| t <sub>h(MI)</sub>                           | Data input hold time                 | Master mode                                                               | 7.5                    | -                 | -                         | ns   |  |

| t <sub>h(SI)</sub>                           |                                      | Slave mode                                                                | 3.5                    | -                 | -                         | ns   |  |

| Table 60. SPI dynamic characteristics <sup>(</sup> |

|----------------------------------------------------|

|----------------------------------------------------|

# 6.3.25 RTC characteristics

# Table 77. Dynamic characteristics: eMMC characteristics $V_{DD} = 1.7 V$ to 1.9 $V^{(1)(2)}$

| Symbol                                         | Parameter                                     | Conditions   | Min | Тур  | Max | Unit |  |  |  |  |  |

|------------------------------------------------|-----------------------------------------------|--------------|-----|------|-----|------|--|--|--|--|--|

| f <sub>PP</sub>                                | Clock frequency in data transfer mode         | -            | 0   | -    | 50  | MHz  |  |  |  |  |  |

| -                                              | SDIO_CK/fPCLK2 frequency ratio                | -            | -   | -    | 8/3 | -    |  |  |  |  |  |

| t <sub>W(CKL)</sub>                            | Clock low time                                | fpp = 50 MHz | 10  | 10.5 | -   | 200  |  |  |  |  |  |

| t <sub>W(CKH)</sub>                            | Clock high time                               | fpp = 50 MHz | 9   | 9.5  | -   | – ns |  |  |  |  |  |

| CMD, D in                                      | CMD, D inputs (referenced to CK) in eMMC mode |              |     |      |     |      |  |  |  |  |  |

| t <sub>ISU</sub>                               | Input setup time HS                           | fpp = 50 MHz | 0   | -    | -   | ns   |  |  |  |  |  |

| t <sub>IH</sub>                                | Input hold time HS                            | fpp = 50 MHz | 6   | -    | -   |      |  |  |  |  |  |

| CMD, D outputs (referenced to CK) in eMMC mode |                                               |              |     |      |     |      |  |  |  |  |  |

| t <sub>OV</sub>                                | Output valid time HS                          | fpp = 50 MHz | -   | 3.5  | 5   | 20   |  |  |  |  |  |

| t <sub>OH</sub>                                | Output hold time HS                           | fpp = 50 MHz | 2   | -    | -   | – ns |  |  |  |  |  |

1. Guaranteed by characterization results.

2. C<sub>load</sub> = 20 pF

### Table 78. RTC characteristics

| Symbol | Parameter                                  | Conditions                                          | Min | Max |

|--------|--------------------------------------------|-----------------------------------------------------|-----|-----|

| -      | f <sub>PCLK1</sub> /RTCCLK frequency ratio | Any read/write operation<br>from/to an RTC register | 4   | -   |

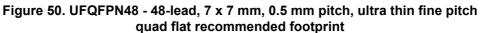

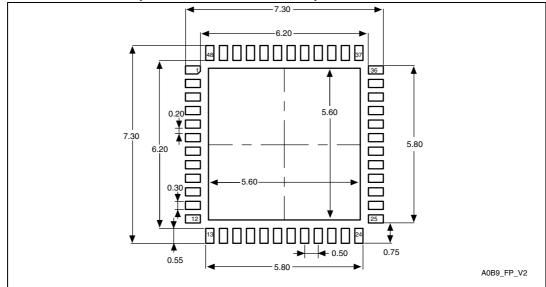

# Table 81. UFQFPN48 - 48-lead, 7 x 7 mm, 0.5 mm pitch, ultra thin fine pitchquad flat package mechanical data (continued)

|        | quad nat puckage meenaned, and (commune) |       |       |                       |        |        |  |  |  |

|--------|------------------------------------------|-------|-------|-----------------------|--------|--------|--|--|--|

| Cumhal | millimeters                              |       |       | inches <sup>(1)</sup> |        |        |  |  |  |

| Symbol | Min.                                     | Тур.  | Max.  | Min.                  | Тур.   | Max.   |  |  |  |

| E2     | 5.500                                    | 5.600 | 5.700 | 0.2165                | 0.2205 | 0.2244 |  |  |  |

| L      | 0.300                                    | 0.400 | 0.500 | 0.0118                | 0.0157 | 0.0197 |  |  |  |

| Т      | -                                        | 0.152 | -     | -                     | 0.0060 | -      |  |  |  |

| b      | 0.200                                    | 0.250 | 0.300 | 0.0079                | 0.0098 | 0.0118 |  |  |  |

| е      | -                                        | 0.500 | -     | -                     | 0.0197 | -      |  |  |  |

| ddd    | -                                        | -     | 0.080 | -                     | -      | 0.0031 |  |  |  |

1. Values in inches are converted from mm and rounded to 4 decimal digits.

1. Dimensions are in millimeters.

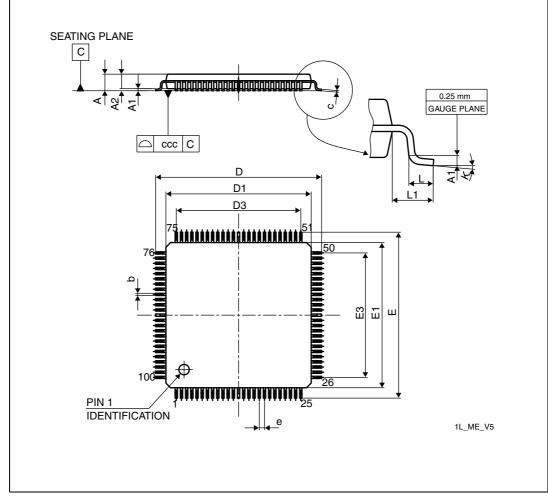

# 7.4 LQFP100 package information

Figure 55. LQFP100 - 100-pin, 14 x 14 mm, 100-pin low-profile quad flat package outline

<sup>1.</sup> Drawing is not to scale.

# Table 84. UFBGA100, 7 x 7 mm, 0.50 mm pitch, ultra fine pitch ball grid array packagemechanical data (continued)

| Symbol |      | millimeters |       |      | inches <sup>(1)</sup> |        |  |

|--------|------|-------------|-------|------|-----------------------|--------|--|

| Symbol | Min. | Тур.        | Max.  | Min. | Тур.                  | Max.   |  |

| ddd    | -    | -           | 0.100 | -    | -                     | 0.0039 |  |

| eee    | -    | -           | 0.150 | -    | -                     | 0.0059 |  |

| fff    | -    | -           | 0.050 | -    | -                     | 0.0020 |  |

1. Values in inches are converted from mm and rounded to 4 decimal digits.

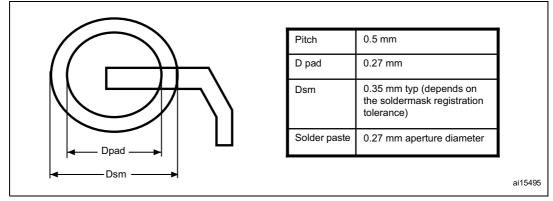

### Figure 59. Recommended PCB design rules for pads (0.5 mm-pitch BGA)

1. Non solder mask defined (NSMD) pads are recommended.

2. 4 to 6 mils solder paste screen printing process.

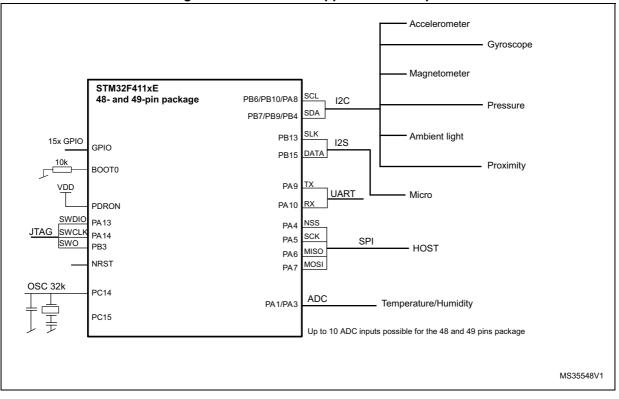

# B.2 Sensor Hub application example

### Figure 64. Sensor Hub application example