Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

#### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| 2 0 0 0 0 0                |                                                                       |

|----------------------------|-----------------------------------------------------------------------|

| Product Status             | Active                                                                |

| Core Processor             | ARM® Cortex®-M4                                                       |

| Core Size                  | 32-Bit Single-Core                                                    |

| Speed                      | 100MHz                                                                |

| Connectivity               | I <sup>2</sup> C, IrDA, LINbus, MMC/SD/SDIO, SPI, UART/USART, USB OTG |

| Peripherals                | Brown-out Detect/Reset, DMA, I <sup>2</sup> S, POR, PWM, WDT          |

| Number of I/O              | 50                                                                    |

| Program Memory Size        | 512KB (512K x 8)                                                      |

| Program Memory Type        | FLASH                                                                 |

| EEPROM Size                | -                                                                     |

| RAM Size                   | 128K x 8                                                              |

| Voltage - Supply (Vcc/Vdd) | 1.7V ~ 3.6V                                                           |

| Data Converters            | A/D 16x12b                                                            |

| Oscillator Type            | Internal                                                              |

| Operating Temperature      | -40°C ~ 105°C (TA)                                                    |

| Mounting Type              | Surface Mount                                                         |

| Package / Case             | 64-LQFP                                                               |

| Supplier Device Package    | 64-LQFP (10x10)                                                       |

| Purchase URL               | https://www.e-xfl.com/product-detail/stmicroelectronics/stm32f411ret7 |

|                            |                                                                       |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

|            | chip scale package outline                                                | 124 |

|------------|---------------------------------------------------------------------------|-----|

| Figure 47. | WLCSP49 - 49-ball, 2.999 x 3.185 mm, 0.4 mm pitch wafer level chip scale  |     |

|            | recommended footprint                                                     | 125 |

| Figure 48. | WLCSP49 marking (package top view)                                        | 126 |

| Figure 49. | UFQFPN48 - 48-lead, 7 x 7 mm, 0.5 mm pitch, ultra thin fine pitch         |     |

|            | quad flat package outline                                                 | 127 |

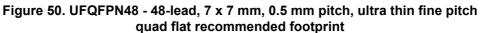

| Figure 50. | UFQFPN48 - 48-lead, 7 x 7 mm, 0.5 mm pitch, ultra thin fine pitch         |     |

|            | quad flat recommended footprint                                           | 128 |

| Figure 51. | UFQFPN48 marking example (package top view)                               | 129 |

| Figure 52. | LQFP64 - 64-pin, 10 x 10 mm, 64-pin low-profile quad flat package outline | 130 |

| Figure 53. | LQFP64 recommended footprint                                              | 131 |

| Figure 54. | LQFP64 marking example (package top view)                                 | 132 |

| Figure 55. | LQFP100 - 100-pin, 14 x 14 mm, 100-pin low-profile quad flat              |     |

|            | package outline                                                           | 133 |

| Figure 56. | LQFP100 - 100-pin, 14 x 14 mm, 100-pin low-profile quad flat              |     |

|            | recommended footprint                                                     | 135 |

| Figure 57. | LQPF100 marking example (package top view)                                | 136 |

| Figure 58. | UFBGA100 - 100-ball, 7 x 7 mm, 0.50 mm pitch, ultra fine pitch            |     |

|            | ball grid array package outline                                           | 137 |

| Figure 59. | Recommended PCB design rules for pads (0.5 mm-pitch BGA)                  | 138 |

| Figure 60. | UFBGA100 marking example (package top view)                               | 139 |

| Figure 61. | USB controller configured as peripheral-only and used in Full-Speed mode  | 143 |

| Figure 62. | USB controller configured as host-only and used in Full-Speed mode        | 143 |

| Figure 63. | USB controller configured in dual mode and used in Full-Speed mode        | 144 |

| Figure 64. | Sensor Hub application example                                            | 145 |

| Figure 65. | Batch Acquisition Mode (BAM) example                                      | 146 |

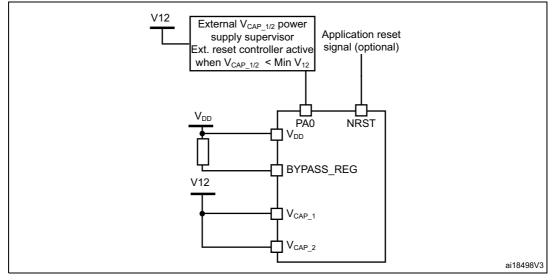

When the regulator is OFF, there is no more internal monitoring on V12. An external power supply supervisor should be used to monitor the V12 of the logic power domain. PA0 pin should be used for this purpose, and act as power-on reset on V12 power domain.

In regulator OFF mode, the following features are no more supported:

- PA0 cannot be used as a GPIO pin since it allows to reset a part of the V12 logic power domain which is not reset by the NRST pin.

- As long as PA0 is kept low, the debug mode cannot be used under power-on reset. As a consequence, PA0 and NRST pins must be managed separately if the debug connection under reset or pre-reset is required.

#### Figure 6. Regulator OFF

The following conditions must be respected:

- V<sub>DD</sub> should always be higher than V<sub>CAP\_1</sub> and V<sub>CAP\_2</sub> to avoid current injection between power domains.

- If the time for V<sub>CAP\_1</sub> and V<sub>CAP\_2</sub> to reach V<sub>12</sub> minimum value is faster than the time for V<sub>DD</sub> to reach 1.7 V, then PA0 should be kept low to cover both conditions: until V<sub>CAP\_1</sub> and V<sub>CAP\_2</sub> reach V<sub>12</sub> minimum value and until V<sub>DD</sub> reaches 1.7 V (see *Figure 7*).

- Otherwise, if the time for V<sub>CAP\_1</sub> and V<sub>CAP\_2</sub> to reach V<sub>12</sub> minimum value is slower than the time for V<sub>DD</sub> to reach 1.7 V, then PA0 could be asserted low externally (see *Figure 8*).

- If  $V_{CAP_1}$  and  $V_{CAP_2}$  go below  $V_{12}$  minimum value and  $V_{DD}$  is higher than 1.7 V, then a reset must be asserted on PA0 pin.

Note:

The minimum value of  $V_{12}$  depends on the maximum frequency targeted in the application

## 3.29 Analog-to-digital converter (ADC)

One 12-bit analog-to-digital converter is embedded and shares up to 16 external channels, performing conversions in the single-shot or scan mode. In scan mode, automatic conversion is performed on a selected group of analog inputs.

The ADC can be served by the DMA controller. An analog watchdog feature allows very precise monitoring of the converted voltage of one, some or all selected channels. An interrupt is generated when the converted voltage is outside the programmed thresholds.

To synchronize A/D conversion and timers, the ADCs could be triggered by any of TIM1, TIM2, TIM3, TIM4 or TIM5 timer.

## 3.30 Temperature sensor

The temperature sensor has to generate a voltage that varies linearly with temperature. The conversion range is between 1.7 V and 3.6 V. The temperature sensor is internally connected to the ADC\_IN18 input channel which is used to convert the sensor output voltage into a digital value. Refer to the reference manual for additional information.

As the offset of the temperature sensor varies from chip to chip due to process variation, the internal temperature sensor is mainly suitable for applications that detect temperature changes instead of absolute temperatures. If an accurate temperature reading is needed, then an external temperature sensor part should be used.

# 3.31 Serial wire JTAG debug port (SWJ-DP)

The ARM SWJ-DP interface is embedded, and is a combined JTAG and serial wire debug port that enables either a serial wire debug or a JTAG probe to be connected to the target.

Debug is performed using 2 pins only instead of 5 required by the JTAG (JTAG pins could be re-use as GPIO with alternate function): the JTAG TMS and TCK pins are shared with SWDIO and SWCLK, respectively, and a specific sequence on the TMS pin is used to switch between JTAG-DP and SW-DP.

# 3.32 Embedded Trace Macrocell™

The ARM Embedded Trace Macrocell provides a greater visibility of the instruction and data flow inside the CPU core by streaming compressed data at a very high rate from the STM32F411xC/xE through a small number of ETM pins to an external hardware trace port analyzer (TPA) device. The TPA is connected to a host computer using any high-speed channel available. Real-time instruction and data flow activity can be recorded and then formatted for display on the host computer that runs the debugger software. TPA hardware is commercially available from common development tool vendors.

The Embedded Trace Macrocell operates with third party debugger software tools.

|          | Pir    | n numt  | ber     |          |                                                      |          |               |       |                                                                                                     |                      |

|----------|--------|---------|---------|----------|------------------------------------------------------|----------|---------------|-------|-----------------------------------------------------------------------------------------------------|----------------------|

| UFQFPN48 | LQFP64 | WLCSP49 | LQFP100 | UFBGA100 | Pin name<br>(function after<br>reset) <sup>(1)</sup> | Pin type | I/O structure | Notes | Alternate functions                                                                                 | Additional functions |

| 21       | 29     | E3      | 47      | L10      | PB10                                                 | I/O      | FT            | -     | TIM2_CH3,<br>I2C2_SCL,<br>SPI2_SCK/I2S2_CK,<br>I2S3_MCK, SDIO_D7,<br>EVENTOUT                       | -                    |

| -        | -      | -       | -       | К9       | PB11                                                 | I/O      | FT            | -     | TIM2_CH4,<br>I2C2_SDA,<br>I2S2_CKIN,<br>EVENTOUT                                                    | -                    |

| 22       | 30     | G2      | 48      | L11      | VCAP_1                                               | S        | -             | -     | -                                                                                                   | -                    |

| 23       | 31     | D3      | 49      | F12      | VSS                                                  | S        | -             | -     | -                                                                                                   | -                    |

| 24       | 32     | F2      | 50      | G12      | VDD                                                  | S        | -             | -     | -                                                                                                   | -                    |

| 25       | 33     | E2      | 51      | L12      | PB12                                                 | I/O      | FT            | -     | TIM1_BKIN,<br>I2C2_SMBA,<br>SPI2_NSS/I2S2_WS,<br>SPI4_NSS/I2S4_WS,<br>SPI3_SCK/I2S3_CK,<br>EVENTOUT | -                    |

| 26       | 34     | G1      | 52      | K12      | PB13                                                 | I/O      | FT            | -     | TIM1_CH1N,<br>SPI2_SCK/I2S2_CK,<br>SPI4_SCK/I2S4_CK,<br>EVENTOUT                                    | -                    |

| 27       | 35     | F1      | 53      | K11      | PB14                                                 | I/O      | FT            | -     | TIM1_CH2N,<br>SPI2_MISO,<br>I2S2ext_SD,<br>SDIO_D6,<br>EVENTOUT                                     | -                    |

| 28       | 36     | E1      | 54      | K10      | PB15                                                 | I/O      | FT            | -     | RTC_50Hz,<br>TIM1_CH3N,<br>SPI2_MOSI/I2S2_SD,<br>SDIO_CK,<br>EVENTOUT                               | RTC_REFIN            |

| -        | -      | -       | 55      | -        | PD8                                                  | I/O      | FT            | -     | -                                                                                                   | -                    |

| -        | -      | -       | 56      | K8       | PD9                                                  | I/O      | FT            | -     | -                                                                                                   | -                    |

| -        | -      | -       | 57      | J12      | PD10                                                 | I/O      | FT            | -     | -                                                                                                   | -                    |

| -        | -      | -       | 58      | J11      | PD11                                                 | I/O      | FT            | -     | -                                                                                                   | -                    |

| -        | -      | -       | 59      | J10      | PD12                                                 | I/O      | FT            | -     | TIM4_CH1,<br>EVENTOUT                                                                               | -                    |

|          | Pir    | n numl  | ber     |          |                                                      |          |               |       |                                                                                              |                      |

|----------|--------|---------|---------|----------|------------------------------------------------------|----------|---------------|-------|----------------------------------------------------------------------------------------------|----------------------|

| UFQFPN48 | LQFP64 | WLCSP49 | LQFP100 | UFBGA100 | Pin name<br>(function after<br>reset) <sup>(1)</sup> | Pin type | I/O structure | Notes | Alternate functions                                                                          | Additional functions |

| 43       | 59     | D4      | 93      | B4       | PB7                                                  | I/O      | FT            | -     | TIM4_CH2,<br>I2C1_SDA,<br>USART1_RX,<br>SDIO_D0,<br>EVENTOUT                                 | -                    |

| 44       | 60     | A5      | 94      | A4       | BOOT0                                                | I        | В             | -     | -                                                                                            | VPP                  |

| 45       | 61     | В5      | 95      | A3       | PB8                                                  | I/O      | FT            | -     | TIM4_CH3,<br>TIM10_CH1,<br>I2C1_SCL,<br>SPI5_MOSI/I2S5_SD,<br>I2C3_SDA, SDIO_D4,<br>EVENTOUT | -                    |

| 46       | 62     | C5      | 96      | В3       | PB9                                                  | I/O      | FT            | -     | TIM4_CH4,<br>TIM11_CH1,<br>I2C1_SDA,<br>SPI2_NSS/I2S2_WS,<br>I2C2_SDA, SDIO_D5,<br>EVENTOUT  | -                    |

| -        | -      | -       | 97      | C3       | PE0                                                  | I/O      | FT            | -     | TIM4_ETR,<br>EVENTOUT                                                                        | -                    |

| -        | -      | -       | 98      | A2       | PE1                                                  | I/O      | FT            | -     | EVENTOUT                                                                                     | -                    |

| 47       | 63     | A6      | 99      | -        | VSS                                                  | S        | -             | -     | -                                                                                            | -                    |

| -        | -      | B6      | -       | H3       | PDR_ON                                               | Ι        | FT            | -     | -                                                                                            | -                    |

| 48       | 64     | A7      | 100     | -        | VDD                                                  | S        | -             | -     | -                                                                                            | -                    |

Table 8. STM32F411xC/xE pin definitions (continued)

1. Function availability depends on the chosen device.

PC13, PC14 and PC15 are supplied through the power switch. Since the switch only sinks a limited amount of current (3 mA), the use of GPIOs PC13 to PC15 in output mode is limited:

The speed should not exceed 2 MHz with a maximum load of 30 pF.

These I/Os must not be used as a current source (e.g. to drive an LED).

3. Main function after the first backup domain power-up. Later on, it depends on the contents of the RTC registers even after reset (because these registers are not reset by the main reset). For details on how to manage these I/Os, refer to the RTC register description sections in the STM32F411xx reference manual.

4. FT = 5 V tolerant except when in analog mode or oscillator mode (for PC14, PC15, PH0 and PH1).

If the device is delivered in an UFBGA100 and the BYPASS\_REG pin is set to VDD (Regulator off/internal reset ON mode), then PA0 is used as an internal Reset (active low) 5.

STM32F411xC STM32F411xE

Pinouts and pin description

|   |      | AF00         | AF01      | AF02                | AF03                     | AF04               | AF05                                     | AF06                                                    | AF07                            | AF08   | AF09          | AF10    | AF11 | AF12 | AF13 | AF14 | AF1       |

|---|------|--------------|-----------|---------------------|--------------------------|--------------------|------------------------------------------|---------------------------------------------------------|---------------------------------|--------|---------------|---------|------|------|------|------|-----------|

|   | Port | SYS_AF       | TIM1/TIM2 | TIM3/<br>TIM4/ TIM5 | TIM9/<br>TIM10/<br>TIM11 | I2C1/I2C2/<br>I2C3 | SPI1/I2S1S<br>PI2/<br>I2S2/SPI3/<br>I2S3 | SPI2/I2S2/<br>SPI3/<br>I2S3/SPI4/<br>I2S4/SPI5/<br>I2S5 | SPI3/I2S3/<br>USART1/<br>USART2 | USART6 | 12C2/<br>12C3 | OTG1_FS |      | SDIO |      |      |           |

|   | PE0  | -            | -         | TIM4_ETR            | -                        | -                  | -                                        | -                                                       | -                               | -      | -             | -       | -    | -    | -    | -    | EVE<br>OU |

|   | PE1  | -            | -         |                     | -                        | -                  | -                                        | -                                                       | -                               | -      | -             | -       | -    | -    | -    | -    | EVE<br>OU |

|   | PE2  | TRACECL<br>K | -         | -                   | -                        | -                  | SPI4_SCK/I<br>2S4_CK                     | SPI5_SCK/I2<br>S5_CK                                    | -                               | -      | -             | -       | -    | -    | -    | -    | EVE<br>OU |

|   | PE3  | TRACED0      | -         | -                   | -                        | -                  | -                                        | -                                                       | -                               | -      | -             | -       | -    | -    | -    | -    | EVE<br>OU |

|   | PE4  | TRACED1      | -         | -                   | -                        | -                  | SPI4_NSS/I<br>2S4_WS                     | SPI5_NSS/I2<br>S5_WS                                    | -                               | -      | -             | -       | -    | -    | -    | -    | EVE<br>OU |

|   | PE5  | TRACED2      | -         | -                   | TIM9_CH1                 | -                  | SPI4_MISO                                | SPI5_MISO                                               | -                               | -      | -             | -       | -    | -    | -    | -    | EVE<br>OL |

|   | PE6  | TRACED3      | -         | -                   | TIM9_CH2                 | -                  | SPI4_MOSI<br>/I2S4_SD                    | SPI5_MOSI/I<br>2S5_SD                                   | -                               | -      | -             | -       | -    | -    | -    | -    | EVE<br>OL |

| L | PE7  | -            | TIM1_ETR  | -                   | -                        | -                  | -                                        | -                                                       | -                               | -      | -             | -       | -    | -    | -    | -    | EVE<br>OL |

|   | PE8  | -            | TIM1_CH1N | -                   | -                        | -                  | -                                        | -                                                       | -                               | -      | -             | -       | -    | -    | -    | -    | EVE<br>OL |

|   | PE9  | -            | TIM1_CH1  | -                   | -                        | -                  | -                                        | -                                                       | -                               | -      | -             | -       | -    | -    | -    | -    | EVE<br>OU |

|   | PE10 | -            | TIM1_CH2N | -                   | -                        | -                  | -                                        | -                                                       | -                               | -      | -             | -       | -    | -    | -    | -    | EVE<br>OU |

|   | PE11 | -            | TIM1_CH2  | -                   | -                        | -                  | SPI4_NSS/I<br>2S4_WS                     | SPI5_NSS/I2<br>S5_WS                                    | -                               | -      | -             | -       | -    | -    | -    | -    | EVE<br>OL |

|   | PE12 | -            | TIM1_CH3N | -                   | -                        | -                  | SPI4_SCK/I<br>2S4_CK                     | SPI5_SCK/I2<br>S5_CK                                    | -                               | -      | -             | -       | -    | -    | -    | -    | EVE<br>OL |

|   | PE13 | -            | TIM1_CH3  | -                   | -                        | -                  | SPI4_MISO                                | SPI5_MISO                                               | -                               | -      | -             | -       | -    | -    | -    | -    | EVE<br>Ol |

|   | PE14 | -            | TIM1_CH4  | -                   | -                        | -                  | SPI4_MOSI<br>/I2S4_SD                    | SPI5_MOSI/I<br>2S5_SD                                   | -                               | -      | -             | -       | -    | -    | -    | -    | EVE<br>Ol |

|   | PE15 | -            | TIM1_BKIN | -                   | -                        | -                  | -                                        | -                                                       | _                               | -      | -             | -       | -    | _    | -    | -    | EVE       |

## STM32F411xC STM32F411xE

| Bus  | Boundary address           | Peripheral |

|------|----------------------------|------------|

|      | 0x4001 5400- 0x4001 FFFF   | Reserved   |

|      | 0x4001 5000 - 0x4001 53FFF | SPI5/I2S5  |

|      | 0x4001 4800 - 0x4001 4BFF  | TIM11      |

|      | 0x4001 4400 - 0x4001 47FF  | TIM10      |

|      | 0x4001 4000 - 0x4001 43FF  | ТІМ9       |

|      | 0x4001 3C00 - 0x4001 3FFF  | EXTI       |

|      | 0x4001 3800 - 0x4001 3BFF  | SYSCFG     |

|      | 0x4001 3400 - 0x4001 37FF  | SPI4/I2S4  |

| APB2 | 0x4001 3000 - 0x4001 33FF  | SPI1/I2S1  |

| APDZ | 0x4001 2C00 - 0x4001 2FFF  | SDIO       |

|      | 0x4001 2400 - 0x4001 2BFF  | Reserved   |

|      | 0x4001 2000 - 0x4001 23FF  | ADC1       |

|      | 0x4001 1800 - 0x4001 1FFF  | Reserved   |

|      | 0x4001 1400 - 0x4001 17FF  | USART6     |

|      | 0x4001 1000 - 0x4001 13FF  | USART1     |

|      | 0x4001 0400 - 0x4001 0FFF  | Reserved   |

|      | 0x4001 0000 - 0x4001 03FF  | TIM1       |

|      | 0x4000 7400 - 0x4000 FFFF  | Reserved   |

Table 10. STM32F411xC/xE register boundary addresses (continued)

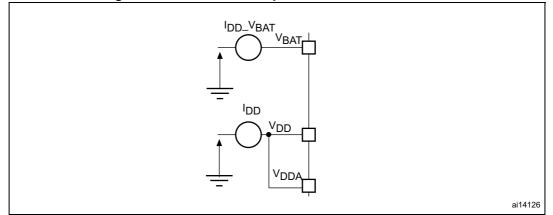

## 6.1.7 Current consumption measurement

#### Figure 18. Current consumption measurement scheme

## 6.2 Absolute maximum ratings

Stresses above the absolute maximum ratings listed in *Table 11: Voltage characteristics*, *Table 12: Current characteristics*, and *Table 13: Thermal characteristics* may cause permanent damage to the device. These are stress ratings only and functional operation of the device at these conditions is not implied. Exposure to maximum rating conditions for extended periods may affect device reliability.

| Symbol                | Ratings                                                                        | Min                                                      | Max                  | Unit |

|-----------------------|--------------------------------------------------------------------------------|----------------------------------------------------------|----------------------|------|

| $V_{DD} - V_{SS}$     | External main supply voltage (including $V_{DDA}, V_{DD}$ and $V_{BAT})^{(1)}$ | -0.3                                                     | 4.0                  |      |

|                       | Input voltage on FT and TC pins <sup>(2)</sup>                                 | V <sub>SS</sub> -0.3                                     | V <sub>DD</sub> +4.0 | v    |

| V <sub>IN</sub>       | Input voltage on any other pin                                                 | V <sub>SS</sub> -0.3                                     | 4.0                  |      |

|                       | Input voltage for BOOT0                                                        | V <sub>SS</sub> 9.0                                      |                      |      |

| $ \Delta V_{DDx} $    | Variations between different $V_{DD}$ power pins                               | -                                                        | 50                   | mV   |

| $ V_{SSX} - V_{SS} $  | Variations between all the different ground pins                               | -                                                        | 50                   | IIIV |

| V <sub>ESD(HBM)</sub> | Electrostatic discharge voltage (human body model)                             | see Sectio<br>Absolute n<br>ratings (ele<br>sensitivity) | naximum<br>ectrical  |      |

#### Table 11. Voltage characteristics

1. All main power ( $V_{DD}$ ,  $V_{DDA}$ ) and ground ( $V_{SS}$ ,  $V_{SSA}$ ) pins must always be connected to the external power supply, in the permitted range.

2. V<sub>IN</sub> maximum value must always be respected. Refer to *Table 12* for the values of the maximum allowed injected current.

| Symbol | Parameter                                                      | Conditions                           | Min  | Тур | Max | Unit |  |  |

|--------|----------------------------------------------------------------|--------------------------------------|------|-----|-----|------|--|--|

|        |                                                                | UFQFPN48                             | -    | -   | 156 |      |  |  |

|        |                                                                | WLCSP49                              | -    | -   | 98  |      |  |  |

| PD     | Power dissipation at $T_A = 125 \ ^{\circ}C \ (range 3)^{(7)}$ | LQFP64                               | -    | -   | 106 | mW   |  |  |

|        |                                                                | LQFP100                              | -    | -   | 116 |      |  |  |

|        |                                                                | UFBGA100                             | -    | -   | 81  |      |  |  |

|        | Ambient temperature for                                        | Maximum power dissipation            | - 40 | -   | 85  |      |  |  |

|        | range 6                                                        | Low power dissipation <sup>(8)</sup> | - 40 | -   | 105 |      |  |  |

| Та     | Ambient temperature for                                        | Maximum power dissipation            | - 40 | -   | 105 |      |  |  |

| IA     | range 7                                                        | Low power dissipation <sup>(8)</sup> | - 40 | -   | 125 |      |  |  |

|        | Ambient temperature for                                        | Maximum power dissipation            | - 40 | -   | 110 | °C   |  |  |

|        | range 3                                                        | Low power dissipation <sup>(8)</sup> | - 40 | -   | 130 |      |  |  |

|        |                                                                | Range 6                              | - 40 | -   | 105 |      |  |  |

| TJ     | Junction temperature range                                     | Range 7                              | - 40 | -   | 125 |      |  |  |

|        |                                                                | Range 3                              | - 40 | -   | 130 |      |  |  |

Table 14. General operating conditions (continued)

V<sub>DD</sub>/V<sub>DDA</sub> minimum value of 1.7 V with the use of an external power supply supervisor (refer to Section 3.15.2: Internal reset OFF).

2. When the ADC is used, refer to Table 65: ADC characteristics.

- 3. If VREF+ pin is present, it must respect the following condition: VDDA-VREF+ < 1.2 V.

- 4. It is recommended to power V<sub>DD</sub> and V<sub>DDA</sub> from the same source. A maximum difference of 300 mV between V<sub>DD</sub> and V<sub>DDA</sub> can be tolerated during power-up and power-down operation.

- 5. Guaranteed by test in production.

- 6. To sustain a voltage higher than VDD+0.3, the internal Pull-up and Pull-Down resistors must be disabled

- 7. If  $T_A$  is lower, higher  $P_D$  values are allowed as long as  $T_J$  does not exceed  $T_{Jmax}$ .

- 8. In low power dissipation state, T<sub>A</sub> can be extended to this range as long as T<sub>J</sub> does not exceed T<sub>Jmax</sub>.

| Operating<br>power<br>supply<br>range           | ADC<br>operation                     | Maximum<br>Flash<br>memory<br>access<br>frequency<br>with no wait<br>states<br>(f <sub>Flashmax</sub> ) | Maximum Flash<br>memory access<br>frequency with<br>wait states <sup>(1)(2)</sup> | I/O operation                               | Clock output<br>frequency on<br>I/O pins <sup>(3)</sup> | Possible<br>Flash<br>memory<br>operations        |

|-------------------------------------------------|--------------------------------------|---------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------|---------------------------------------------|---------------------------------------------------------|--------------------------------------------------|

| V <sub>DD</sub> =1.7 to<br>2.1 V <sup>(4)</sup> | Conversion<br>time up to<br>1.2 Msps | 16 MHz <sup>(5)</sup>                                                                                   | 100 MHz with 6<br>wait states                                                     | <ul> <li>No I/O compensation</li> </ul>     | up to 30 MHz                                            | 8-bit erase<br>and program<br>operations<br>only |

| V <sub>DD</sub> = 2.1 to<br>2.4 V               | Conversion<br>time up to<br>1.2 Msps | 18 MHz                                                                                                  | 100 MHz with 5<br>wait states                                                     | <ul> <li>No I/O<br/>compensation</li> </ul> | up to 30 MHz                                            | 16-bit erase<br>and program<br>operations        |

Table 15. Features depending on the operating power supply range

| Symbol                           | Parameter                                                                            | Conditions                                                                                | Min | Тур | Max | Unit |

|----------------------------------|--------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------|-----|-----|-----|------|

| I <sub>RUSH</sub> <sup>(2)</sup> | In-Rush current on<br>voltage regulator power-<br>on (POR or wakeup from<br>Standby) | -                                                                                         | -   | 160 | 200 | mA   |

| E <sub>RUSH</sub> <sup>(2)</sup> | In-Rush energy on<br>voltage regulator power-<br>on (POR or wakeup from<br>Standby)  | V <sub>DD</sub> = 1.7 V, T <sub>A</sub> = 125 °C,<br>I <sub>RUSH</sub> = 171 mA for 31 µs | -   | -   | 5.4 | μC   |

Table 19. Embedded reset and power control block characteristics (continued)

1. The product behavior is guaranteed by design down to the minimum V<sub>POR/PDR</sub> value.

2. Guaranteed by design.

3. The reset timing is measured from the power-on (POR reset or wakeup from V<sub>BAT</sub>) to the instant when first instruction is fetched by the user application code.

## 6.3.6 Supply current characteristics

The current consumption is a function of several parameters and factors such as the operating voltage, ambient temperature, I/O pin loading, device software configuration, operating frequencies, I/O pin switching rate, program location in memory and executed binary code.

The current consumption is measured as described in *Figure 18: Current consumption measurement scheme*.

All the run-mode current consumption measurements given in this section are performed with a reduced code that gives a consumption equivalent to CoreMark code.

#### Typical and maximum current consumption

The MCU is placed under the following conditions:

- All I/O pins are in input mode with a static value at VDD or VSS (no load).

- All peripherals are disabled except if it is explicitly mentioned.

- The Flash memory access time is adjusted to both f<sub>HCLK</sub> frequency and VDD ranges (refer to *Table 15: Features depending on the operating power supply range*).

- The voltage scaling is adjusted to f<sub>HCLK</sub> frequency as follows:

- Scale 3 for  $f_{HCLK} \le 64$  MHz

- Scale 2 for 64 MHz <  $f_{HCLK} \le 84$  MHz

- Scale 1 for 84 MHz < f<sub>HCLK</sub> ≤ 100 MHz

- The system clock is HCLK, f<sub>PCLK1</sub> = f<sub>HCLK</sub>/2, and f<sub>PCLK2</sub> = f<sub>HCLK</sub>.

- External clock is 4 MHz and PLL is ON except if it is explicitly mentioned.

- The maximum values are obtained for V<sub>DD</sub> = 3.6 V and a maximum ambient temperature (T<sub>A</sub>), and the typical values for T<sub>A</sub>= 25 °C and V<sub>DD</sub> = 3.3 V unless otherwise specified.

| Symbol                              | Parameter                                                                                   | Min <sup>(1)</sup> | Typ <sup>(1)</sup> | Max <sup>(1)</sup> | Unit                  |  |

|-------------------------------------|---------------------------------------------------------------------------------------------|--------------------|--------------------|--------------------|-----------------------|--|

| t <sub>WUSLEEP</sub> <sup>(2)</sup> | Wakeup from Sleep mode                                                                      | -                  | 4                  | 6                  | CPU<br>clock<br>cycle |  |

|                                     | Wakeup from Stop mode, usage of main regulator                                              | -                  | 13.5               | 14.5               |                       |  |

| + (2)                               | Wakeup from Stop mode, usage of main regulator, Flash memory in Deep power down mode        | -                  | 105                | 111                | 116                   |  |

| twustop <sup>(2)</sup>              | Wakeup from Stop mode, regulator in low power mode                                          | -                  | 21                 | 33                 | μs                    |  |

|                                     | Wakeup from Stop mode, regulator in low power mode,<br>Flash memory in Deep power down mode | -                  | 113                | 130                |                       |  |

| twustdby <sup>(2)(3)</sup>          | Wakeup from Standby mode                                                                    | -                  | 314                | 407                | μs                    |  |

| turu=                               | Wakeup of Flash from Flash_Stop mode                                                        | -                  | -                  | 8                  | 116                   |  |

| <sup>t</sup> WUFLASH                | Wakeup of Flash from Flash Deep power down mode                                             | -                  | -                  | 100                | μs                    |  |

Table 34. Low-power mode wakeup timings<sup>(1)</sup>

1. Guaranteed by characterization results.

2. The wakeup times are measured from the wakeup event to the point in which the application code reads the first instruction.

3.  $t_{WUSTDBY}$  maximum value is given at -40 °C.

## 6.3.8 External clock source characteristics

#### High-speed external user clock generated from an external source

In bypass mode the HSE oscillator is switched off and the input pin is a standard I/O. The external clock signal has to respect the *Table 53*. However, the recommended clock input waveform is shown in *Figure 22*.

The characteristics given in *Table 35* result from tests performed using an high-speed external clock source, and under ambient temperature and supply voltage conditions summarized in *Table 14*.

| Symbol                                       | Parameter                                           | Conditions                       | Min             | Тур | Max                | Unit |

|----------------------------------------------|-----------------------------------------------------|----------------------------------|-----------------|-----|--------------------|------|

| f <sub>HSE_ext</sub>                         | External user clock source frequency <sup>(1)</sup> |                                  | 1               | -   | 50                 | MHz  |

| V <sub>HSEH</sub>                            | OSC_IN input pin high level voltage                 |                                  | $0.7V_{DD}$     | -   | V <sub>DD</sub>    | v    |

| V <sub>HSEL</sub>                            | OSC_IN input pin low level voltage                  |                                  | V <sub>SS</sub> | -   | $0.3V_{\text{DD}}$ | v    |

| t <sub>w(HSEH)</sub><br>t <sub>w(HSEL)</sub> | OSC_IN high or low time <sup>(1)</sup>              |                                  | 5               | -   | -                  | ns   |

| t <sub>r(HSE)</sub><br>t <sub>f(HSE)</sub>   | OSC_IN rise or fall time <sup>(1)</sup>             |                                  | -               | -   | 10                 | 115  |

| C <sub>in(HSE)</sub>                         | OSC_IN input capacitance <sup>(1)</sup>             | -                                | -               | 5   | -                  | pF   |

| DuCy <sub>(HSE)</sub>                        | Duty cycle                                          | -                                | 45              | -   | 55                 | %    |

| ١L                                           | OSC_IN Input leakage current                        | $V_{SS} \leq V_{IN} \leq V_{DD}$ | -               | -   | ±1                 | μA   |

Table 35. High-speed external user clock characteristics

1. Guaranteed by design.

## Static latchup

Two complementary static tests are required on six parts to assess the latchup performance:

- A supply overvoltage is applied to each power supply pin

- A current injection is applied to each input, output and configurable I/O pin

These tests are compliant with EIA/JESD 78A IC latchup standard.

| Table 51. I | Electrical | sensitivities |

|-------------|------------|---------------|

|-------------|------------|---------------|

| Symbol | Parameter             | Conditions                                     | Class      |

|--------|-----------------------|------------------------------------------------|------------|

| LU     | Static latch-up class | $T_A = + 125 \text{ °C conforming to JESD78A}$ | II level A |

## 6.3.15 I/O current injection characteristics

As a general rule, current injection to the I/O pins, due to external voltage below  $V_{SS}$  or above  $V_{DD}$  (for standard, 3 V-capable I/O pins) should be avoided during normal product operation. However, in order to give an indication of the robustness of the microcontroller in cases when abnormal injection accidentally happens, susceptibility tests are performed on a sample basis during device characterization.

### Functional susceptibility to I/O current injection

While a simple application is executed on the device, the device is stressed by injecting current into the I/O pins programmed in floating input mode. While current is injected into the I/O pin, one at a time, the device is checked for functional failures.

The failure is indicated by an out of range parameter: ADC error above a certain limit (>5 LSB TUE), out of conventional limits of induced leakage current on adjacent pins (out of  $-5 \mu$ A/+0  $\mu$ A range), or other functional failure (for example reset, oscillator frequency deviation).

Negative induced leakage current is caused by negative injection and positive induced leakage current by positive injection.

The test results are given in Table 52.

|                  |                                                                                                                                                                    | Functional susceptibility |                    |      |

|------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------|--------------------|------|

| Symbol           | Description                                                                                                                                                        | Negative injection        | Positive injection | Unit |

|                  | Injected current on BOOT0 pin                                                                                                                                      | -0                        | NA                 |      |

|                  | Injected current on NRST pin                                                                                                                                       | -0                        | NA                 |      |

| I <sub>INJ</sub> | Injected current on PB3, PB4, PB5, PB6, PB7,<br>PB8, PB9, PC13, PC14, PC15, PH1, PDR_ON,<br>PC0, PC1,PC2, PC3, PD1, PD5, PD6, PD7, PE0,<br>PE2, PE3, PE4, PE5, PE6 | -0                        | NA                 | mA   |

|                  | Injected current on any other FT pin                                                                                                                               | -5                        | NA                 |      |

|                  | Injected current on any other pins                                                                                                                                 | -5                        | +5                 |      |

## Table 52. I/O current injection susceptibility<sup>(1)</sup>

1. NA = not applicable.

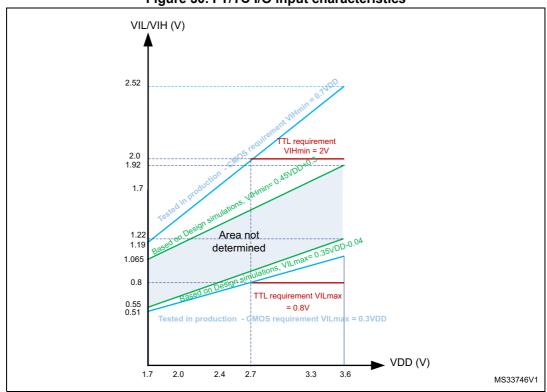

#### Figure 30. FT/TC I/O input characteristics

## **Output driving current**

The GPIOs (general purpose input/outputs) can sink or source up to  $\pm 8$  mA, and sink or source up to  $\pm 20$  mA (with a relaxed V<sub>OL</sub>/V<sub>OH</sub>) except PC13, PC14 and PC15 which can sink or source up to  $\pm 3$ mA. When using the PC13 to PC15 GPIOs in output mode, the speed should not exceed 2 MHz with a maximum load of 30 pF.

In the user application, the number of I/O pins which can drive current must be limited to respect the absolute maximum rating specified in *Section 6.2*. In particular:

- The sum of the currents sourced by all the I/Os on V<sub>DD</sub>, plus the maximum Run consumption of the MCU sourced on V<sub>DD</sub>, cannot exceed the absolute maximum rating ΣI<sub>VDD</sub> (see *Table 12*).

- The sum of the currents sunk by all the I/Os on V<sub>SS</sub> plus the maximum Run consumption of the MCU sunk on V<sub>SS</sub> cannot exceed the absolute maximum rating ΣI<sub>VSS</sub> (see *Table 12*).

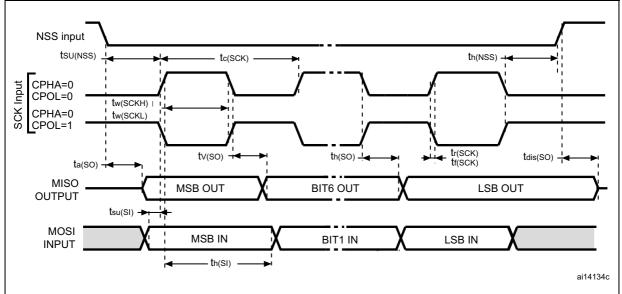

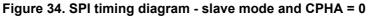

| Symbol                                    | Parameter                | Conditions                                                         | Min | Тур | Мах  | Unit |

|-------------------------------------------|--------------------------|--------------------------------------------------------------------|-----|-----|------|------|

| t <sub>a(SO</sub> )                       | Data output access time  | Slave mode                                                         | 7   | -   | 21   | ns   |

| t <sub>dis(SO)</sub>                      | Data output disable time | Slave mode                                                         | 5   | -   | 12   | ns   |

| +                                         | Data output valid timo   | Slave mode (after enable edge),<br>2.7 V < $V_{DD}$ < 3.6 V        | -   | 11  | 13   | ns   |

| t <sub>v(SO)</sub> Data output valid time |                          | Slave mode (after enable edge),<br>1.7 V < $V_{DD}$ < 3.6 V        | -   | 11  | 18.5 | ns   |

| t <sub>h(SO)</sub>                        | Data output hold time    | Slave mode (after enable edge),<br>1.7 V < V <sub>DD</sub> < 3.6 V | 8   | -   | -    | ns   |

| t <sub>v(MO)</sub>                        | Data output valid time   | Master mode (after enable edge)                                    | -   | 4   | 6    | ns   |

| t <sub>h(MO)</sub>                        | Data output hold time    | Master mode (after enable edge)                                    | 0   | -   | -    | ns   |

| Table 60. SPI | dynamic | characteristics <sup>(1)</sup> | (continued) |

|---------------|---------|--------------------------------|-------------|

|---------------|---------|--------------------------------|-------------|

1. Guaranteed by characterization results.

2. Maximum frequency in Slave transmitter mode is determined by the sum of  $t_{v(SO)}$  and  $t_{su(MI)}$  which has to fit into SCK low or high phase preceding the SCK sampling edge. This value can be achieved when the SPI communicates with a master having  $t_{su(MI)} = 0$  while Duty(SCK) = 50%

## I<sup>2</sup>S interface characteristics

Unless otherwise specified, the parameters given in *Table 61* for the I<sup>2</sup>S interface are derived from tests performed under the ambient temperature,  $f_{PCLKx}$  frequency and  $V_{DD}$  supply voltage conditions summarized in *Table 14*, with the following configuration:

- Output speed is set to OSPEEDRy[1:0] = 10

- Capacitive load C = 30 pF

- Measurement points are done at CMOS levels: 0.5V<sub>DD</sub>

Refer to Section 6.3.16: I/O port characteristics for more details on the input/output alternate function characteristics (CK, SD, WS).

| Symbol                 | Parameter                      | Conditions                             | Min    | Мах                   | Unit |

|------------------------|--------------------------------|----------------------------------------|--------|-----------------------|------|

| f <sub>MCK</sub>       | I2S Main clock output          | -                                      | 256x8K | 256xFs <sup>(2)</sup> | MHz  |

| f                      | 125 clock froguonov            | Master data: 32 bits                   | -      | 64xFs                 | MHz  |

| f <sub>CK</sub>        | I2S clock frequency            | Slave data: 32 bits                    | -      | 64xFs                 |      |

| D <sub>CK</sub>        | I2S clock frequency duty cycle | Slave receiver                         | 30     | 70                    | %    |

| t <sub>v(WS)</sub>     | WS valid time                  | Master mode                            | 0      | 7                     |      |

| t <sub>h(WS)</sub>     | WS hold time                   | Master mode                            | 1.5    | -                     |      |

| t <sub>su(WS)</sub>    | WS setup time                  | Slave mode                             | 1.5    | -                     |      |

| t <sub>h(WS)</sub>     | WS hold time                   | Slave mode                             | 3      | -                     |      |

| t <sub>su(SD_MR)</sub> | Data input setup time          | Master receiver                        | 1      | -                     |      |

| $t_{su(SD\_SR)}$       |                                | Slave receiver                         | 2.5    | -                     | ns   |

| t <sub>h(SD_MR)</sub>  | Data input hold time           | Master receiver                        | 7      | -                     |      |

| t <sub>h(SD_SR)</sub>  | Data input noid time           | Slave receiver                         | 2.5    | -                     |      |

| t <sub>v(SD_ST)</sub>  | Data output valid time         | Slave transmitter (after enable edge)  | -      | 20                    |      |

| t <sub>v(SD_MT)</sub>  |                                | Master transmitter (after enable edge) | -      | 6                     |      |

| t <sub>h(SD_ST)</sub>  |                                | Slave transmitter (after enable edge)  | 8      | -                     |      |

| t <sub>h(SD_MT)</sub>  | Data output hold time          | Master transmitter (after enable edge) | 2      | -                     |      |

| Table 61. I <sup>2</sup> S dynamic characteristics <sup>(1</sup> | I) |  |

|------------------------------------------------------------------|----|--|

|------------------------------------------------------------------|----|--|

1. Guaranteed by characterization results.

2. The maximum value of 256xFs is 50 MHz (APB1 maximum frequency).

Note: Refer to the I2S section of RM0383 reference manual for more details on the sampling frequency ( $F_{S}$ ).

$f_{MCK}$ ,  $f_{CK}$ , and  $D_{CK}$  values reflect only the digital peripheral behavior. The values of these parameters might be slightly impacted by the source clock precision.  $D_{CK}$  depends mainly on the value of ODD bit. The digital contribution leads to a minimum value of (I2SDIV/(2\*I2SDIV+ODD) and a maximum value of (I2SDIV+ODD)/(2\*I2SDIV+ODD).  $F_S$  maximum value is supported for each mode/condition.

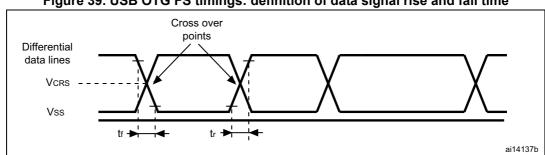

#### Figure 39. USB OTG FS timings: definition of data signal rise and fall time

#### Table 64. USB OTG FS electrical characteristics<sup>(1)</sup>

|                  | Driver characteristics          |                                |     |     |      |  |

|------------------|---------------------------------|--------------------------------|-----|-----|------|--|

| Symbol           | Parameter                       | Conditions                     | Min | Max | Unit |  |

| t <sub>r</sub>   | Rise time <sup>(2)</sup>        | C <sub>L</sub> = 50 pF         | 4   | 20  | ns   |  |

| t <sub>f</sub>   | Fall time <sup>(2)</sup>        | C <sub>L</sub> = 50 pF         | 4   | 20  | ns   |  |

| t <sub>rfm</sub> | Rise/ fall time matching        | t <sub>r</sub> /t <sub>f</sub> | 90  | 110 | %    |  |

| V <sub>CRS</sub> | Output signal crossover voltage |                                | 1.3 | 2.0 | V    |  |

1. Guaranteed by design.

2. Measured from 10% to 90% of the data signal. For more detailed informations, please refer to USB Specification - Chapter 7 (version 2.0).

## 6.3.20 12-bit ADC characteristics

Unless otherwise specified, the parameters given in *Table 65* are derived from tests performed under the ambient temperature,  $f_{PCLK2}$  frequency and  $V_{DDA}$  supply voltage conditions summarized in *Table 14*.

| Symbol                             | Parameter                               | Conditions                                      | Min                                                         | Тур | Max               | Unit               |

|------------------------------------|-----------------------------------------|-------------------------------------------------|-------------------------------------------------------------|-----|-------------------|--------------------|

| V <sub>DDA</sub>                   | Power supply                            | V <sub>DDA</sub> –V <sub>REF+</sub> < 1.2 V     | 1.7 <sup>(1)</sup>                                          | -   | 3.6               | V                  |

| V <sub>REF+</sub>                  | Positive reference voltage              | $V_{DDA} - V_{REF+} < 1.2 V$                    | 1.7 <sup>(1)</sup>                                          | -   | V <sub>DDA</sub>  | V                  |

| f                                  | ADC clock frequency                     | $V_{DDA}$ = 1.7 <sup>(1)</sup> to 2.4 V         | 0.6                                                         | 15  | 18                | MHz                |

| f <sub>ADC</sub>                   | ADC Clock frequency                     | V <sub>DDA</sub> = 2.4 to 3.6 V                 | 0.6                                                         | 30  | 36                | MHz                |

| f <sub>TRIG</sub> <sup>(2)</sup>   | External trigger frequency              | f <sub>ADC</sub> = 30 MHz,<br>12-bit resolution | -                                                           | -   | 1764              | kHz                |

|                                    |                                         |                                                 | -                                                           | -   | 17                | 1/f <sub>ADC</sub> |

| V <sub>AIN</sub>                   | Conversion voltage range <sup>(3)</sup> |                                                 | 0 (V <sub>SSA</sub> or V <sub>REF-</sub><br>tied to ground) | -   | V <sub>REF+</sub> | V                  |

| R <sub>AIN</sub> <sup>(2)</sup>    | External input impedance                | See <i>Equation 1</i> for details               | -                                                           | -   | 50                | kΩ                 |

| R <sub>ADC</sub> <sup>(2)(4)</sup> | Sampling switch resistance              |                                                 | -                                                           | -   | 6                 | kΩ                 |

| C <sub>ADC</sub> <sup>(2)</sup>    | Internal sample and hold capacitor      |                                                 | -                                                           | 4   | 7                 | pF                 |

Table 65. ADC characteristics

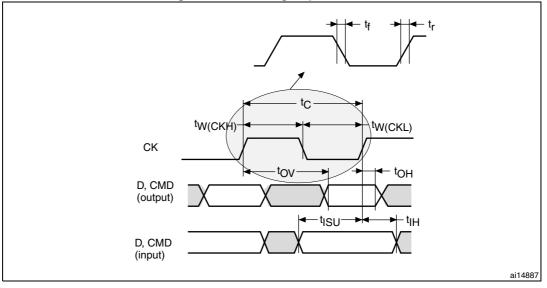

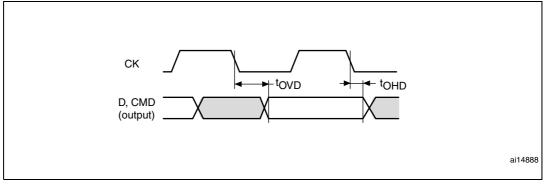

## 6.3.24 SD/SDIO MMC/eMMC card host interface (SDIO) characteristics

Unless otherwise specified, the parameters given in *Table 76* for the SDIO/MMC/eMMC interface are derived from tests performed under the ambient temperature,  $f_{PCLK2}$  frequency and  $V_{DD}$  supply voltage conditions summarized in *Table 14*, with the following configuration:

- Output speed is set to OSPEEDRy[1:0] = 10

- Capacitive load C = 30 pF (for eMMC C = 20 pF)

- Measurement points are done at CMOS levels: 0.5V<sub>DD</sub>

Refer to Section 6.3.16: I/O port characteristics for more details on the input/output characteristics.

#### Figure 44. SDIO high-speed mode

Figure 45. SD default mode

| package mechanical data |       |             |       |        |                       |        |

|-------------------------|-------|-------------|-------|--------|-----------------------|--------|

| Symbol                  |       | millimeters |       |        | inches <sup>(1)</sup> |        |

| Symbol                  | Min   | Тур         | Мах   | Min    | Тур                   | Max    |

| А                       | 0.525 | 0.555       | 0.585 | 0.0207 | 0.0219                | 0.0230 |

| A1                      | -     | 0.175       | -     | -      | 0.0069                | -      |

| A2                      | -     | 0.380       | -     | -      | 0.0150                | -      |

| A3 <sup>(2)</sup>       | -     | 0.025       | -     | -      | 0.0010                | -      |

| b <sup>(3)</sup>        | 0.220 | 0.250       | 0.280 | 0.0087 | 0.0098                | 0.0110 |

| D                       | 2.964 | 2.999       | 3.034 | 0.1167 | 0.1181                | 0.1194 |

| E                       | 3.150 | 3.185       | 3.220 | 0.1240 | 0.1254                | 0.1268 |

| е                       | -     | 0.400       | -     | -      | 0.0157                | -      |

| e1                      | -     | 2.400       | -     | -      | 0.0945                | -      |

| e2                      | -     | 2.400       | -     | -      | 0.0945                | -      |

| F                       | -     | 0.2995      | -     | -      | 0.0118                | -      |

| G                       | -     | 0.3925      | -     | -      | 0.0155                | -      |

| aaa                     | -     | 0.100       | -     | -      | 0.0039                | -      |

| bbb                     | -     | 0.100       | -     | -      | 0.0039                | -      |

| ccc                     | -     | 0.100       | -     | -      | 0.0039                | -      |

| ddd                     | -     | 0.050       | -     | -      | 0.0020                | -      |

| eee                     | -     | 0.050       | -     | -      | 0.0020                | -      |

# Table 79. WLCSP49 - 49-ball, 2.999 x 3.185 mm, 0.4 mm pitch wafer level chip scalepackage mechanical data

1. Values in inches are converted from mm and rounded to 4 decimal digits.

2. Back side coating

3. Dimension is measured at the maximum bump diameter parallel to primary datum Z.

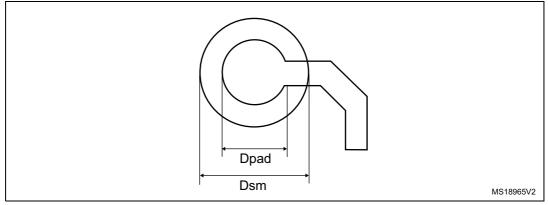

# Figure 47. WLCSP49 - 49-ball, 2.999 x 3.185 mm, 0.4 mm pitch wafer level chip scale recommended footprint

| ······································ |                                               |  |  |

|----------------------------------------|-----------------------------------------------|--|--|

| Dimension                              | Recommended values                            |  |  |

| Pitch                                  | 0.4 mm                                        |  |  |

| Dpad                                   | 260 μm max. (circular)<br>220 μm recommended  |  |  |

| Dsm                                    | 300 μm min. (for 260 μm diameter pad)         |  |  |

| PCB pad design                         | Non-solder mask defined via underbump allowed |  |  |

Table 80. WLCSP49 recommended PCB design rules (0.4 mm pitch)

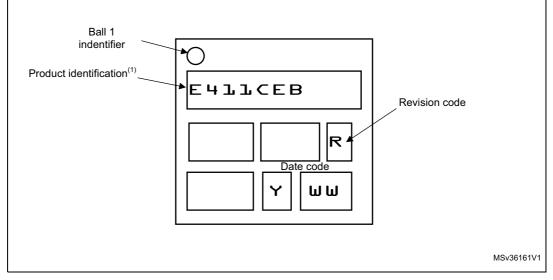

## **Device marking for WLCSP49**

The following figure gives an example of topside marking orientation versus ball A1 identifier location.

Other optional marking or inset/upset marks, which depend on supply chain operations, are not indicated below.

Figure 48. WLCSP49 marking (package top view)

Parts marked as "ES", "E" or accompanied by an Engineering Sample notification letter, are not yet qualified and therefore not yet ready to be used in production and any consequences deriving from such usage will not be at ST charge. In no event, ST will be liable for any customer usage of these engineering samples in production. ST Quality has to be contacted prior to any decision to use these Engineering samples to run qualification activity.

# Table 81. UFQFPN48 - 48-lead, 7 x 7 mm, 0.5 mm pitch, ultra thin fine pitchquad flat package mechanical data (continued)

| Symbol | millimeters |       |       | inches <sup>(1)</sup> |        |        |

|--------|-------------|-------|-------|-----------------------|--------|--------|

|        | Min.        | Тур.  | Max.  | Min.                  | Тур.   | Max.   |

| E2     | 5.500       | 5.600 | 5.700 | 0.2165                | 0.2205 | 0.2244 |

| L      | 0.300       | 0.400 | 0.500 | 0.0118                | 0.0157 | 0.0197 |

| Т      | -           | 0.152 | -     | -                     | 0.0060 | -      |

| b      | 0.200       | 0.250 | 0.300 | 0.0079                | 0.0098 | 0.0118 |

| е      | -           | 0.500 | -     | -                     | 0.0197 | -      |

| ddd    | -           | -     | 0.080 | -                     | -      | 0.0031 |

1. Values in inches are converted from mm and rounded to 4 decimal digits.

1. Dimensions are in millimeters.