# E·XFL

#### Welcome to E-XFL.COM

### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

### Details

| Product Status             | Active                                                                |

|----------------------------|-----------------------------------------------------------------------|

| Core Processor             | ARM® Cortex®-M4                                                       |

| Core Size                  | 32-Bit Single-Core                                                    |

| Speed                      | 100MHz                                                                |

| Connectivity               | I <sup>2</sup> C, IrDA, LINbus, MMC/SD/SDIO, SPI, UART/USART, USB OTG |

| Peripherals                | Brown-out Detect/Reset, DMA, I <sup>2</sup> S, POR, PWM, WDT          |

| Number of I/O              | 81                                                                    |

| Program Memory Size        | 256KB (256K x 8)                                                      |

| Program Memory Type        | FLASH                                                                 |

| EEPROM Size                | -                                                                     |

| RAM Size                   | 128K x 8                                                              |

| Voltage - Supply (Vcc/Vdd) | 1.7V ~ 3.6V                                                           |

| Data Converters            | A/D 16x12b                                                            |

| Oscillator Type            | Internal                                                              |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                     |

| Mounting Type              | Surface Mount                                                         |

| Package / Case             | 100-LQFP                                                              |

| Supplier Device Package    | 100-LQFP (14x14)                                                      |

| Purchase URL               | https://www.e-xfl.com/product-detail/stmicroelectronics/stm32f411vct6 |

|                            |                                                                       |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

## Contents

| 1 | Intro | duction                                                                                         | 10 |

|---|-------|-------------------------------------------------------------------------------------------------|----|

| 2 | Desc  | ription                                                                                         | 11 |

|   | 2.1   | Compatibility with STM32F4 series                                                               | 13 |

| 3 | Func  | tional overview                                                                                 | 16 |

|   | 3.1   | $ARM^{	extsf{R}}$ Cortex $^{	extsf{R}}$ -M4 with FPU core with embedded Flash and SRAM $\ldots$ | 16 |

|   | 3.2   | Adaptive real-time memory accelerator (ART Accelerator™)                                        | 16 |

|   | 3.3   | Batch Acquisition mode (BAM)                                                                    | 16 |

|   | 3.4   | Memory protection unit                                                                          | 17 |

|   | 3.5   | Embedded Flash memory                                                                           | 17 |

|   | 3.6   | CRC (cyclic redundancy check) calculation unit                                                  | 17 |

|   | 3.7   | Embedded SRAM                                                                                   | 17 |

|   | 3.8   | Multi-AHB bus matrix                                                                            | 18 |

|   | 3.9   | DMA controller (DMA)                                                                            | 18 |

|   | 3.10  | Nested vectored interrupt controller (NVIC)                                                     | 19 |

|   | 3.11  | External interrupt/event controller (EXTI)                                                      | 19 |

|   | 3.12  | Clocks and startup                                                                              | 19 |

|   | 3.13  | Boot modes                                                                                      | 20 |

|   | 3.14  | Power supply schemes                                                                            | 20 |

|   | 3.15  | Power supply supervisor                                                                         | 21 |

|   |       | 3.15.1 Internal reset ON                                                                        | 21 |

|   |       | 3.15.2 Internal reset OFF                                                                       | 21 |

|   | 3.16  | Voltage regulator                                                                               | 22 |

|   |       | 3.16.1 Regulator ON                                                                             | 22 |

|   |       | 3.16.2 Regulator OFF                                                                            |    |

|   |       | 3.16.3 Regulator ON/OFF and internal power supply supervisor availability                       |    |

|   | 3.17  | Real-time clock (RTC) and backup registers                                                      |    |

|   | 3.18  | Low-power modes                                                                                 |    |

|   | 3.19  | V <sub>BAT</sub> operation                                                                      | 26 |

|   | 3.20  | Timers and watchdogs                                                                            | 27 |

|   |       | 3.20.1 Advanced-control timers (TIM1)                                                           | 27 |

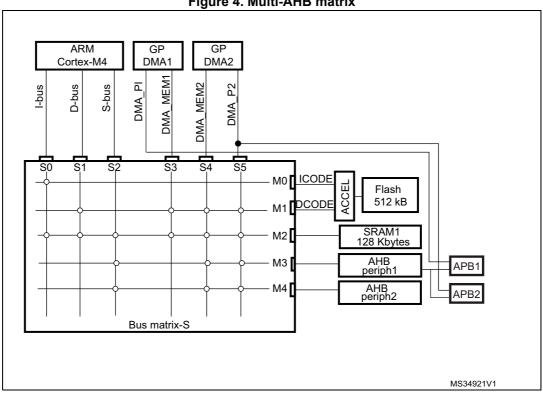

## 3.8 Multi-AHB bus matrix

The 32-bit multi-AHB bus matrix interconnects all the masters (CPU, DMAs) and the slaves (Flash memory, RAM, AHB and APB peripherals) and ensures a seamless and efficient operation even when several high-speed peripherals work simultaneously.

## 3.9 DMA controller (DMA)

The devices feature two general-purpose dual-port DMAs (DMA1 and DMA2) with 8 streams each. They are able to manage memory-to-memory, peripheral-to-memory and memory-to-peripheral transfers. They feature dedicated FIFOs for APB/AHB peripherals, support burst transfer and are designed to provide the maximum peripheral bandwidth (AHB/APB).

The two DMA controllers support circular buffer management, so that no specific code is needed when the controller reaches the end of the buffer. The two DMA controllers also have a double buffering feature, which automates the use and switching of two memory buffers without requiring any special code.

Each stream is connected to dedicated hardware DMA requests, with support for software trigger on each stream. Configuration is made by software and transfer sizes between source and destination are independent.

| USART<br>name | Standard<br>features | Modem<br>(RTS/CTS) | LIN | SPI<br>master | irDA | Smartcard<br>(ISO 7816) | Max. baud<br>rate in Mbit/s<br>(oversampling<br>by 16) | Max. baud<br>rate in Mbit/s<br>(oversampling<br>by 8) | APB<br>mapping            |

|---------------|----------------------|--------------------|-----|---------------|------|-------------------------|--------------------------------------------------------|-------------------------------------------------------|---------------------------|

| USART1        | х                    | х                  | х   | х             | х    | х                       | 6.25                                                   | 12.5                                                  | APB2<br>(max.<br>100 MHz) |

| USART2        | х                    | х                  | х   | х             | х    | х                       | 3.12                                                   | 6.25                                                  | APB1<br>(max.<br>50 MHz)  |

| USART6        | х                    | N.A                | х   | Х             | Х    | х                       | 6.25                                                   | 12.5                                                  | APB2<br>(max.<br>100 MHz) |

Table 6. USART feature comparison

## 3.23 Serial peripheral interface (SPI)

The devices feature five SPIs in slave and master modes in full-duplex and simplex communication modes. SPI1, SPI4 and SPI5 can communicate at up to 50 Mbit/s, SPI2 and SPI3 can communicate at up to 25 Mbit/s. The 3-bit prescaler gives 8 master mode frequencies and the frame is configurable to 8 bits or 16 bits. The hardware CRC generation/verification supports basic SD Card/MMC modes. All SPIs can be served by the DMA controller.

The SPI interface can be configured to operate in TI mode for communications in master mode and slave mode.

## 3.24 Inter-integrated sound (I<sup>2</sup>S)

Five standard I<sup>2</sup>S interfaces (multiplexed with SPI1 to SPI5) are available. They can be operated in master or slave mode, in simplex communication modes and full duplex for I2S2 and I2S3 and can be configured to operate with a 16-/32-bit resolution as an input or output channel. All the I2Sx audio sampling frequencies from 8 kHz up to 192 kHz are supported. When either or both of the I<sup>2</sup>S interfaces is/are configured in master mode, the master clock can be output to the external DAC/CODEC at 256 times the sampling frequency.

All  $I^2Sx$  can be served by the DMA controller.

## 3.25 Audio PLL (PLLI2S)

The devices feature an additional dedicated PLL for audio I<sup>2</sup>S application. It allows to achieve error-free I<sup>2</sup>S sampling clock accuracy without compromising on the CPU performance.

The PLLI2S configuration can be modified to manage an  $I^2S$  sample rate change without disabling the main PLL (PLL) used for the CPU.

The audio PLL can be programmed with very low error to obtain sampling rates ranging from 8 kHz to 192 kHz.

|          | Pir    | n numt  | ber     |          |                                                      |          |               |       |                                                                   |                      |

|----------|--------|---------|---------|----------|------------------------------------------------------|----------|---------------|-------|-------------------------------------------------------------------|----------------------|

| UFQFPN48 | LQFP64 | WLCSP49 | LQFP100 | UFBGA100 | Pin name<br>(function after<br>reset) <sup>(1)</sup> | Pin type | I/O structure | Notes | Alternate functions                                               | Additional functions |

| -        | 24     | -       | 33      | K5       | PC4                                                  | I/O      | FT            | -     | EVENTOUT                                                          | ADC1_14              |

| -        | 25     | -       | 34      | L5       | PC5                                                  | I/O      | FT            | I     | EVENTOUT                                                          | ADC1_15              |

| 18       | 26     | G5      | 35      | M5       | PB0                                                  | I/O      | FT            | -     | TIM1_CH2N,<br>TIM3_CH3,<br>SPI5_SCK/I2S5_CK,<br>EVENTOUT          | ADC1_8               |

| 19       | 27     | G4      | 36      | M6       | PB1                                                  | I/O      | FT            | -     | TIM1_CH3N,<br>TIM3_CH4,<br>SPI5_NSS/I2S5_WS,<br>EVENTOUT          | ADC1_9               |

| 20       | 28     | G3      | 37      | L6       | PB2                                                  | I/O      | FT            | -     | EVENTOUT                                                          | BOOT1                |

| -        | -      | -       | 38      | M7       | PE7                                                  | I/O      | FT            | -     | TIM1_ETR,<br>EVENTOUT                                             | -                    |

| -        | -      | -       | 39      | L7       | PE8                                                  | I/O      | FT            | -     | TIM1_CH1N,<br>EVENTOUT                                            | -                    |

| -        | -      | -       | 40      | M8       | PE9                                                  | I/O      | FT            | -     | TIM1_CH1,<br>EVENTOUT                                             | -                    |

| -        | -      | -       | 41      | L8       | PE10                                                 | I/O      | FT            | -     | TIM1_CH2N,<br>EVENTOUT                                            | -                    |

| -        | -      | -       | 42      | M9       | PE11                                                 | I/O      | FT            | -     | TIM1_CH2,<br>SPI4_NSS/I2S4_WS,<br>SPI5_NSS/I2S5_WS,<br>EVENTOUT   | -                    |

| -        | -      | -       | 43      | L9       | PE12                                                 | I/O      | FT            | -     | TIM1_CH3N,<br>SPI4_SCK/I2S4_CK,<br>SPI5_SCK/I2S5_CK,<br>EVENTOUT  | -                    |

| -        | -      | -       | 44      | M10      | PE13                                                 | I/O      | FT            | -     | TIM1_CH3,<br>SPI4_MISO,<br>SPI5_MISO,<br>EVENTOUT                 | -                    |

| -        | -      | -       | 45      | M11      | PE14                                                 | I/O      | FT            | -     | TIM1_CH4,<br>SPI4_MOSI/I2S4_SD,<br>SPI5_MOSI/I2S5_SD,<br>EVENTOUT | -                    |

| -        | -      | -       | 46      | M12      | PE15                                                 | I/O      | FT            | -     | TIM1_BKIN,<br>EVENTOUT                                            | -                    |

Table 8. STM32F411xC/xE pin definitions (continued)

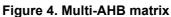

### 6.1.7 Current consumption measurement

### Figure 18. Current consumption measurement scheme

### 6.2 Absolute maximum ratings

Stresses above the absolute maximum ratings listed in *Table 11: Voltage characteristics*, *Table 12: Current characteristics*, and *Table 13: Thermal characteristics* may cause permanent damage to the device. These are stress ratings only and functional operation of the device at these conditions is not implied. Exposure to maximum rating conditions for extended periods may affect device reliability.

| Symbol                | Ratings                                                                        | Min                                                      | Max                  | Unit |

|-----------------------|--------------------------------------------------------------------------------|----------------------------------------------------------|----------------------|------|

| $V_{DD} - V_{SS}$     | External main supply voltage (including $V_{DDA}, V_{DD}$ and $V_{BAT})^{(1)}$ | -0.3                                                     | 4.0                  |      |

|                       | Input voltage on FT and TC pins <sup>(2)</sup>                                 | V <sub>SS</sub> -0.3                                     | V <sub>DD</sub> +4.0 | V    |

| V <sub>IN</sub>       | Input voltage on any other pin                                                 | V <sub>SS</sub> -0.3                                     | 4.0                  |      |

|                       | Input voltage for BOOT0                                                        | V <sub>SS</sub>                                          | 9.0                  |      |

| $ \Delta V_{DDx} $    | Variations between different $V_{DD}$ power pins                               | -                                                        | 50                   | mV   |

| $ V_{SSX} - V_{SS} $  | Variations between all the different ground pins                               | -                                                        | 50                   | IIIV |

| V <sub>ESD(HBM)</sub> | Electrostatic discharge voltage (human body model)                             | see Sectio<br>Absolute n<br>ratings (ele<br>sensitivity) | naximum<br>ectrical  |      |

### Table 11. Voltage characteristics

1. All main power ( $V_{DD}$ ,  $V_{DDA}$ ) and ground ( $V_{SS}$ ,  $V_{SSA}$ ) pins must always be connected to the external power supply, in the permitted range.

2. V<sub>IN</sub> maximum value must always be respected. Refer to *Table 12* for the values of the maximum allowed injected current.

| Symbol | Parameter                                                      | Conditions                           | Min  | Тур | Max | Unit |

|--------|----------------------------------------------------------------|--------------------------------------|------|-----|-----|------|

|        |                                                                | UFQFPN48                             | -    | -   | 156 |      |

|        |                                                                | WLCSP49                              | -    | -   | 98  |      |

| PD     | Power dissipation at $T_A = 125 \ ^{\circ}C \ (range 3)^{(7)}$ | LQFP64                               | -    | -   | 106 | mW   |

|        |                                                                | LQFP100                              | -    | -   | 116 |      |

|        |                                                                | UFBGA100                             | -    | -   | 81  |      |

|        | Ambient temperature for                                        | Maximum power dissipation            | - 40 | -   | 85  |      |

|        | range 6                                                        | Low power dissipation <sup>(8)</sup> | - 40 | -   | 105 |      |

| Та     | Ambient temperature for                                        | Maximum power dissipation            | - 40 | -   | 105 |      |

| IA     | range 7                                                        | Low power dissipation <sup>(8)</sup> | - 40 | -   | 125 |      |

|        | Ambient temperature for                                        | Maximum power dissipation            | - 40 | -   | 110 | °C   |

|        | range 3                                                        | Low power dissipation <sup>(8)</sup> | - 40 | -   | 130 |      |

|        |                                                                | Range 6                              | - 40 | -   | 105 |      |

| TJ     | Junction temperature range                                     | Range 7                              | - 40 | -   | 125 |      |

|        |                                                                | Range 3                              | - 40 | -   | 130 |      |

Table 14. General operating conditions (continued)

V<sub>DD</sub>/V<sub>DDA</sub> minimum value of 1.7 V with the use of an external power supply supervisor (refer to Section 3.15.2: Internal reset OFF).

2. When the ADC is used, refer to Table 65: ADC characteristics.

- 3. If VREF+ pin is present, it must respect the following condition: VDDA-VREF+ < 1.2 V.

- 4. It is recommended to power V<sub>DD</sub> and V<sub>DDA</sub> from the same source. A maximum difference of 300 mV between V<sub>DD</sub> and V<sub>DDA</sub> can be tolerated during power-up and power-down operation.

- 5. Guaranteed by test in production.

- 6. To sustain a voltage higher than VDD+0.3, the internal Pull-up and Pull-Down resistors must be disabled

- 7. If  $T_A$  is lower, higher  $P_D$  values are allowed as long as  $T_J$  does not exceed  $T_{Jmax}$ .

- 8. In low power dissipation state, T<sub>A</sub> can be extended to this range as long as T<sub>J</sub> does not exceed T<sub>Jmax</sub>.

| Operating<br>power<br>supply<br>range           | ADC<br>operation                     | Maximum<br>Flash<br>memory<br>access<br>frequency<br>with no wait<br>states<br>(f <sub>Flashmax</sub> ) | Maximum Flash<br>memory access<br>frequency with<br>wait states <sup>(1)(2)</sup> | I/O operation                               | Clock output<br>frequency on<br>I/O pins <sup>(3)</sup> | Possible<br>Flash<br>memory<br>operations        |

|-------------------------------------------------|--------------------------------------|---------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------|---------------------------------------------|---------------------------------------------------------|--------------------------------------------------|

| V <sub>DD</sub> =1.7 to<br>2.1 V <sup>(4)</sup> | Conversion<br>time up to<br>1.2 Msps | 16 MHz <sup>(5)</sup>                                                                                   | 100 MHz with 6<br>wait states                                                     | <ul> <li>No I/O<br/>compensation</li> </ul> | up to 30 MHz                                            | 8-bit erase<br>and program<br>operations<br>only |

| V <sub>DD</sub> = 2.1 to<br>2.4 V               | Conversion<br>time up to<br>1.2 Msps | 18 MHz                                                                                                  | 100 MHz with 5<br>wait states                                                     | <ul> <li>No I/O<br/>compensation</li> </ul> | up to 30 MHz                                            | 16-bit erase<br>and program<br>operations        |

Table 15. Features depending on the operating power supply range

| Operating<br>power<br>supply<br>range            | ADC<br>operation                     | Maximum<br>Flash<br>memory<br>access<br>frequency<br>with no wait<br>states<br>(f <sub>Flashmax</sub> ) | Maximum Flash<br>memory access<br>frequency with<br>wait states <sup>(1)(2)</sup> | I/O operation                                      | Clock output<br>frequency on<br>I/O pins <sup>(3)</sup>                                                       | Possible<br>Flash<br>memory<br>operations |

|--------------------------------------------------|--------------------------------------|---------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------|----------------------------------------------------|---------------------------------------------------------------------------------------------------------------|-------------------------------------------|

| V <sub>DD</sub> = 2.4 to<br>2.7 V                | Conversion<br>time up to<br>2.4 Msps | 24 MHz                                                                                                  | 100 MHz with 4<br>wait states                                                     | <ul> <li>I/O compensation works</li> </ul>         | up to 50 MHz                                                                                                  | 16-bit erase<br>and program<br>operations |

| V <sub>DD</sub> = 2.7 to<br>3.6 V <sup>(6)</sup> | Conversion<br>time up to<br>2.4 Msps | 30 MHz                                                                                                  | 100 MHz with 3<br>wait states                                                     | <ul> <li>I/O<br/>compensation<br/>works</li> </ul> | - up to<br>100 MHz<br>when $V_{DD}$ =<br>3.0 to 3.6 V<br>- up to<br>50 MHz<br>when $V_{DD}$ =<br>2.7 to 3.0 V | 32-bit erase<br>and program<br>operations |

### Table 15. Features depending on the operating power supply range (continued)

1. Applicable only when the code is executed from Flash memory. When the code is executed from RAM, no wait state is required.

- 2. Thanks to the ART accelerator and the 128-bit Flash memory, the number of wait states given here does not impact the execution speed from Flash memory since the ART accelerator allows to achieve a performance equivalent to 0 wait state program execution.

- 3. Refer to Table 55: I/O AC characteristics for frequencies vs. external load.

- V<sub>DD</sub>/V<sub>DDA</sub> minimum value of 1.7 V, with the use of an external power supply supervisor (refer to Section 3.15.2: Internal reset OFF).

- 5. Prefetch is not available. Refer to AN3430 application note for details on how to adjust performance and power.

- The voltage range for the USB full speed embedded PHY can drop down to 2.7 V. However the electrical characteristics of D- and D+ pins will be degraded between 2.7 and 3 V.

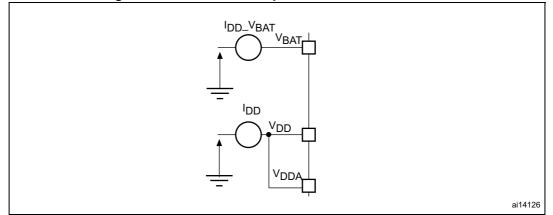

### 6.3.2 VCAP\_1/VCAP\_2 external capacitors

Stabilization for the main regulator is achieved by connecting the external capacitor  $C_{EXT}$  to the VCAP\_1 and VCAP\_2 pins. For packages supporting only 1 VCAP pin, the 2 CEXT capacitors are replaced by a single capacitor.

C<sub>EXT</sub> is specified in *Table 16*.

1. Legend: ESR is the equivalent series resistance.

|                  |                           |                                                                               |      |                           | Max <sup>(1)</sup>        |                            |                            |      |    |

|------------------|---------------------------|-------------------------------------------------------------------------------|------|---------------------------|---------------------------|----------------------------|----------------------------|------|----|

| Symbol Parameter | Conditions                | f <sub>HCLK</sub><br>(MHz)                                                    | Тур  | T <sub>A</sub> =<br>25 °C | T <sub>A</sub> =<br>85 °C | T <sub>A</sub> =<br>105 °C | T <sub>A</sub> =<br>125 °C | Unit |    |

|                  |                           |                                                                               | 100  | 29.5                      | 31.5                      | 32.3                       | 33.3                       | 34.7 |    |

|                  |                           | External clock, PLL<br>ON <sup>(2)</sup> ,<br>all peripherals                 | 84   | 25.5                      | 27.1                      | 27.9                       | 28.9                       | 30.2 |    |

|                  |                           |                                                                               | 64   | 18.6                      | 19.8                      | 20.4                       | 21.2                       | 22.4 |    |

|                  | enabled <sup>(3)(4)</sup> | 50                                                                            | 15.2 | 16.4                      | 16.9                      | 17.7                       | 18.7                       |      |    |

|                  |                           |                                                                               | 20   | 7.6                       | 8.4                       | 8.8                        | 9.5                        | 10.5 | mA |

|                  |                           | HSI, PLL OFF <sup>(2)</sup> , all peripherals enabled <sup>(3)</sup>          | 16   | 4.8                       | 5.2                       | 5.7                        | 6.5                        | 7.5  |    |

|                  | Supply current            |                                                                               | 1    | 0.9                       | 1.3                       | 1.6                        | 2.4                        | 3.4  |    |

| I <sub>DD</sub>  | in Run mode               |                                                                               | 100  | 20.4                      | 21.8                      | 22.7                       | 23.8                       | 25.1 | mA |

|                  |                           |                                                                               | 84   | 18.4                      | 19.2 <sup>(5)</sup>       | 20.9                       | 21.1                       | 22.4 |    |

|                  |                           | External clock, PLL ON <sup>(2)</sup> all peripherals disabled <sup>(3)</sup> | 64   | 13.5                      | 14.5                      | 15.2                       | 15.9                       | 17.2 |    |

|                  |                           | 50                                                                            | 11.3 | 12.2                      | 12.8                      | 13.6                       | 14.7                       | -    |    |

|                  |                           | 20                                                                            | 5.6  | 6.4                       | 6.7                       | 7.4                        | 8.5                        |      |    |

|                  |                           | HSI, PLL OFF <sup>(2)</sup> , all                                             | 16   | 3.6                       | 4.1                       | 4.5                        | 5.2                        | 6.3  | 1  |

|                  |                           | peripherals disabled <sup>(3)</sup>                                           | 1    | 0.9                       | 1.2                       | 1.6                        | 2.3                        | 3.4  |    |

## Table 24. Typical and maximum current consumption in run mode, code with data processing<br/>(ART accelerator disabled) running from Flash memory - $V_{DD}$ = 3.6 V

1. Guaranteed by characterization results.

2. Refer to Table 41 and RM0383 for the possible PLL VCO setting

3. Add an additional power consumption of 1.6 mA per ADC for the analog part. In applications, this consumption occurs only while the ADC is ON (ADON bit is set in the ADC\_CR2 register).

4. When the ADC is ON (ADON bit set in the ADC\_CR2), add an additional power consumption of 1.6mA per ADC for the analog part.

5. Guaranteed by test in production.

| Perip           | bheral              | I <sub>DD</sub> (Тур) | Unit   |

|-----------------|---------------------|-----------------------|--------|

|                 | TIM1                | 5.71                  |        |

|                 | TIM9                | 2.86                  |        |

|                 | TIM10               | 1.79                  |        |

|                 | TIM11               | 2.02                  |        |

|                 | OTG_FS              | 23.93                 |        |

| APB2            | ADC1 <sup>(4)</sup> | 2.98                  |        |

| (up to 100 MHz) | SPI1                | 1.19                  | μA/MHz |

|                 | USART1              | 3.10                  |        |

|                 | USART6              | 2.86                  |        |

|                 | SDIO                | 5.95                  |        |

|                 | SPI4                | 1.31                  |        |

|                 | SYSCFG              | 0.71                  |        |

Table 33. Peripheral current consumption (continued)

1. Valid if all the DMA streams are activated (please refer to the reference manual RM0383).

2. For N DMA streams activated (up to 8 activated streams, refer to the reference manual RM0383).

3. I2SMOD bit set in SPI\_I2SCFGR register, and then the I2SE bit set to enable I2S peripheral.

4. When the ADC is ON (ADON bit set in the ADC\_CR2 register), add an additional power consumption of 1.6 mA for the analog part.

|                                 | Table 461 Habi monory programming that tip volage (continuou) |            |                    |     |                    |      |  |  |  |

|---------------------------------|---------------------------------------------------------------|------------|--------------------|-----|--------------------|------|--|--|--|

| Symbol                          | Parameter                                                     | Conditions | Min <sup>(1)</sup> | Тур | Max <sup>(1)</sup> | Unit |  |  |  |

| V <sub>prog</sub>               | Programming voltage                                           |            | 2.7                | -   | 3.6                | V    |  |  |  |

| V <sub>PP</sub>                 | V <sub>PP</sub> voltage range                                 |            | 7                  | -   | 9                  | V    |  |  |  |

| I <sub>PP</sub>                 | Minimum current sunk on the $V_{\rm PP}$ pin                  |            | 10                 | -   | -                  | mA   |  |  |  |

| t <sub>VPP</sub> <sup>(3)</sup> | Cumulative time during which $V_{PP}$ is applied              |            | -                  | -   | 1                  | hour |  |  |  |

Table 46. Flash memory programming with V<sub>PP</sub> voltage (continued)

1. Guaranteed by design.

2. The maximum programming time is measured after 100K erase operations.

3.  $V_{PP}$  should only be connected during programming/erasing.

| Symbol           | Parameter      | Conditions                                                                                                                                                                                              | Value<br>Min <sup>(1)</sup> | Unit    |

|------------------|----------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------|---------|

| N <sub>END</sub> | Endurance      | $T_A = -40 \text{ to } + 85 \text{ °C} \text{ (temp. range 6)}$<br>$T_A = -40 \text{ to } + 105 \text{ °C} \text{ (temp. range 7)}$<br>$T_A = -40 \text{ to } + 125 \text{ °C} \text{ (temp. range 3)}$ | 10                          | kcycles |

|                  |                | 1 kcycle <sup>(2)</sup> at T <sub>A</sub> = 85 °C                                                                                                                                                       | 30                          |         |

| t                | Data retention | 1 kcycle <sup>(2)</sup> at T <sub>A</sub> = 105 °C                                                                                                                                                      | 10                          | Years   |

| t <sub>RET</sub> |                | 1 kcycle <sup>(2)</sup> at T <sub>A</sub> = 125 °C                                                                                                                                                      | 3                           | Tears   |

|                  |                | 10 kcycle <sup>(2)</sup> at T <sub>A</sub> = 55 °C                                                                                                                                                      | 20                          |         |

| Table 47. Flash memory | endurance and data retention |

|------------------------|------------------------------|

|------------------------|------------------------------|

1. Guaranteed by characterization results.

2. Cycling performed over the whole temperature range.

### 6.3.13 EMC characteristics

Susceptibility tests are performed on a sample basis during device characterization.

### Functional EMS (electromagnetic susceptibility)

While a simple application is executed on the device (toggling 2 LEDs through I/O ports). the device is stressed by two electromagnetic events until a failure occurs. The failure is indicated by the LEDs:

- Electrostatic discharge (ESD) (positive and negative) is applied to all device pins until a functional disturbance occurs. This test is compliant with the IEC 61000-4-2 standard.

- FTB: A burst of fast transient voltage (positive and negative) is applied to V<sub>DD</sub> and V<sub>SS</sub> through a 100 pF capacitor, until a functional disturbance occurs. This test is compliant with the IEC 61000-4-4 standard.

A device reset allows normal operations to be resumed.

The test results are given in *Table 49*. They are based on the EMS levels and classes defined in application note AN1709.

### Input/output AC characteristics

The definition and values of input/output AC characteristics are given in *Figure 31* and *Table 55*, respectively.

Unless otherwise specified, the parameters given in *Table 55* are derived from tests performed under the ambient temperature and  $V_{DD}$  supply voltage conditions summarized in *Table 14*.

| OSPEEDRy<br>[1:0] bit<br>value <sup>(1)</sup> | Symbol                                           | Parameter                                                                       | Conditions                                                  | Min | Тур | Мах                | Unit  |

|-----------------------------------------------|--------------------------------------------------|---------------------------------------------------------------------------------|-------------------------------------------------------------|-----|-----|--------------------|-------|

|                                               |                                                  | Maximum frequency <sup>(3)</sup>                                                | C <sub>L</sub> = 50 pF, V <sub>DD</sub> ≥ 2.70 V            | -   | -   | 4                  |       |

|                                               | f                                                |                                                                                 | C <sub>L</sub> = 50 pF, V <sub>DD</sub> ≥ 1.7 V             | -   | -   | 2                  | MHz   |

|                                               | f <sub>max(IO)out</sub>                          |                                                                                 | C <sub>L</sub> = 10 pF, V <sub>DD</sub> ≥ 2.70 V            | -   | -   | 8                  | MHZ   |

| 00                                            |                                                  |                                                                                 | C <sub>L</sub> = 10 pF, V <sub>DD</sub> ≥ 1.7 V             | -   | -   | 4                  |       |

|                                               | t <sub>f(IO)out</sub> /<br>t <sub>r(IO)out</sub> | Output high to low level fall<br>time and output low to high<br>level rise time | C <sub>L</sub> = 50 pF, V <sub>DD</sub> = 1.7 V to<br>3.6 V | -   | -   | 100                | ns    |

|                                               |                                                  | ax(IO)out Maximum frequency <sup>(3)</sup>                                      | C <sub>L</sub> = 50 pF, V <sub>DD</sub> ≥ 2.70 V            | -   | -   | 25                 |       |

|                                               | f <sub>max(IO)out</sub>                          |                                                                                 | C <sub>L</sub> = 50 pF, V <sub>DD</sub> ≥ 1.7 V             | -   | -   | 12.5               | MHz   |

|                                               |                                                  |                                                                                 | C <sub>L</sub> = 10 pF, V <sub>DD</sub> ≥ 2.70 V            | -   | -   | 50                 |       |

| 01                                            |                                                  |                                                                                 | C <sub>L</sub> = 10 pF, V <sub>DD</sub> ≥ 1.7 V             | -   | -   | 20                 |       |

| 01                                            | t <sub>f(IO)out</sub> /<br>t <sub>r(IO)out</sub> | Output high to low level fall<br>time and output low to high<br>level rise time | C <sub>L</sub> = 50 pF, V <sub>DD</sub> ≥2.7 V              | -   | -   | 10                 | - ns  |

|                                               |                                                  |                                                                                 | C <sub>L</sub> = 50 pF, V <sub>DD</sub> ≥ 1.7 V             | -   | -   | 20                 |       |

|                                               |                                                  |                                                                                 | C <sub>L</sub> = 10 pF, V <sub>DD</sub> ≥ 2.70 V            | -   | -   | 6                  |       |

|                                               |                                                  |                                                                                 | C <sub>L</sub> = 10 pF, V <sub>DD</sub> ≥ 1.7 V             | -   | -   | 10                 |       |

|                                               |                                                  |                                                                                 | C <sub>L</sub> = 40 pF, V <sub>DD</sub> ≥ 2.70 V            | -   | -   | 50 <sup>(4)</sup>  |       |

|                                               | f <sub>max(IO)out</sub>                          | <sub>lout</sub> Maximum frequency <sup>(3)</sup>                                | C <sub>L</sub> = 40 pF, V <sub>DD</sub> ≥ 1.7 V             | -   | -   | 25                 | - MHz |

| 10 -                                          |                                                  |                                                                                 | C <sub>L</sub> = 10 pF, V <sub>DD</sub> ≥ 2.70 V            | -   | -   | 100 <sup>(4)</sup> |       |

|                                               |                                                  |                                                                                 | C <sub>L</sub> = 10 pF, V <sub>DD</sub> ≥ 1.7 V             | -   | -   | 50 <sup>(4)</sup>  |       |

|                                               |                                                  |                                                                                 | C <sub>L</sub> = 40 pF, V <sub>DD</sub> ≥ 2.70 V            | -   | -   | 6                  | – ns  |

|                                               | t <sub>f(IO)out</sub> /<br>t <sub>r(IO)out</sub> | Output high to low level fall<br>time and output low to high<br>level rise time | C <sub>L</sub> = 40 pF, V <sub>DD</sub> ≥ 1.7 V             | -   | -   | 10                 |       |

|                                               |                                                  |                                                                                 | C <sub>L</sub> = 10 pF, V <sub>DD</sub> ≥ 2.70 V            | -   | -   | 4                  |       |

|                                               |                                                  |                                                                                 | C <sub>L</sub> = 10 pF, V <sub>DD</sub> ≥ 1.7 V             | -   | -   | 6                  |       |

Table 55. I/O AC characteristics<sup>(1)(2)</sup>

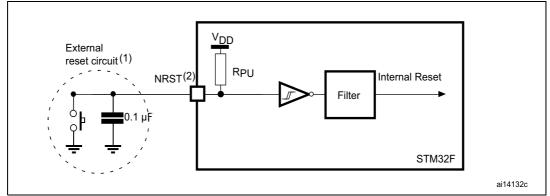

### 6.3.17 NRST pin characteristics

The NRST pin input driver uses CMOS technology. It is connected to a permanent pull-up resistor,  $R_{PU}$  (see *Table 53*).

Unless otherwise specified, the parameters given in *Table 56* are derived from tests performed under the ambient temperature and V<sub>DD</sub> supply voltage conditions summarized in *Table 14*. Refer to *Table 53: I/O static characteristics* for the values of VIH and VIL for NRST pin.

| Symbol                               | Parameter                                                                   | Min                     | Тур | Мах | Unit |    |

|--------------------------------------|-----------------------------------------------------------------------------|-------------------------|-----|-----|------|----|

| R <sub>PU</sub>                      | Weak pull-up equivalent<br>resistor <sup>(1)</sup> $V_{IN} = V_{SS}$ 304050 |                         |     |     | kΩ   |    |

| V <sub>F(NRST)</sub> <sup>(2)</sup>  | NRST Input filtered pulse                                                   |                         | -   | -   | 100  | ns |

| V <sub>NF(NRST)</sub> <sup>(2)</sup> | NRST Input not filtered pulse                                               | V <sub>DD</sub> > 2.7 V | 300 | -   | -    | ns |

| T <sub>NRST_OUT</sub>                | AST_OUT Generated reset pulse duration Internal Reset source 20 -           |                         | -   | -   | μs   |    |

1. The pull-up is designed with a true resistance in series with a switchable PMOS. This PMOS contribution to the series resistance must be minimum (~10% order).

2. Guaranteed by design.

### Figure 32. Recommended NRST pin protection

1. The reset network protects the device against parasitic resets.

The user must ensure that the level on the NRST pin can go below the V<sub>IL(NRST)</sub> max level specified in Table 56. Otherwise the reset is not taken into account by the device.

### 6.3.18 TIM timer characteristics

The parameters given in Table 57 are guaranteed by design.

Refer to Section 6.3.16: I/O port characteristics for details on the input/output alternate function characteristics (output compare, input capture, external clock, PWM output).

| Symbol                 | Parameter                                                         | Conditions <sup>(3)</sup>                    | Min    | Max                     | Unit                 |

|------------------------|-------------------------------------------------------------------|----------------------------------------------|--------|-------------------------|----------------------|

| -                      |                                                                   | AHB/APBx prescaler=1                         | 1      | -                       | t <sub>TIMxCLK</sub> |

| t <sub>res(TIM)</sub>  | <b>_</b>                                                          | or 2 or 4, f <sub>TIMxCLK</sub> =<br>100 MHz | 11.9   | -                       | ns                   |

|                        | Timer resolution time                                             | AHB/APBx prescaler>4,                        | 1      | -                       | t <sub>TIMxCLK</sub> |

|                        |                                                                   | f <sub>TIMxCLK</sub> = 100 MHz               | 11.9   | -                       | ns                   |

| f <sub>EXT</sub>       | Timer external clock<br>frequency on CH1 to CH4                   |                                              | 0      | f <sub>TIMxCLK</sub> /2 | MHz                  |

|                        |                                                                   | f <sub>TIMxCLK</sub> = 100 MHz               | 0      | 50                      | MHz                  |

| Res <sub>TIM</sub>     | Timer resolution                                                  |                                              | -      | 16/32                   | bit                  |

| t <sub>COUNTER</sub>   | 16-bit counter clock<br>period when internal clock<br>is selected | f <sub>TIMxCLK</sub> = 100 MHz               | 0.0119 | 780                     | μs                   |

| t <sub>MAX_COUNT</sub> | Maximum possible count                                            |                                              | -      | 65536 ×<br>65536        | t <sub>TIMxCLK</sub> |

|                        | with 32-bit counter                                               | f <sub>TIMxCLK</sub> = 100 MHz               | -      | 51.1                    | S                    |

Table 57. TIMx characteristics<sup>(1)(2)</sup>

1. TIMx is used as a general term to refer to the TIM1 to TIM11 timers.

2. Guaranteed by design.

The maximum timer frequency on APB1 is 50 MHz and on APB2 is up to 100 MHz, by setting the TIMPRE bit in the RCC\_DCKCFGR register, if APBx prescaler is 1 or 2 or 4, then TIMxCLK = HCKL, otherwise TIMxCLK >= 4x PCLKx.

### 6.3.19 Communications interfaces

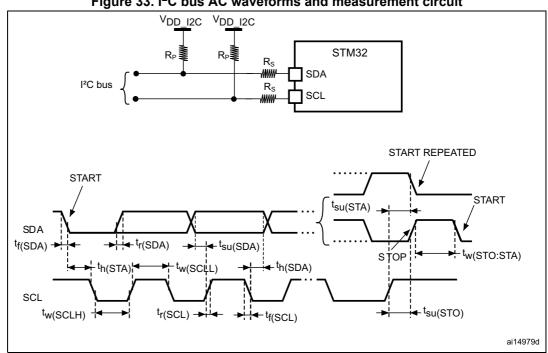

### I<sup>2</sup>C interface characteristics

The I<sup>2</sup>C interface meets the requirements of the standard I<sup>2</sup>C communication protocol with the following restrictions: the I/O pins SDA and SCL are mapped to are not "true" opendrain. When configured as open-drain, the PMOS connected between the I/O pin and V<sub>DD</sub> is disabled, but is still present.

The I<sup>2</sup>C characteristics are described in *Table 58*. Refer also to *Section 6.3.16*: I/O port *characteristics* for more details on the input/output alternate function characteristics (SDA and SCL).

The I<sup>2</sup>C bus interface supports standard mode (up to 100 kHz) and fast mode (up to 400 kHz). The I<sup>2</sup>C bus frequency can be increased up to 1 MHz. For more details about the complete solution, please contact your local ST sales representative.

- 1. R<sub>S</sub> = series protection resistor.

- 2. R<sub>P</sub> = external pull-up resistor.

- 3.  $V_{DD \ I2C}$  is the I2C bus power supply.

|                        | I2C_CCR value                  |

|------------------------|--------------------------------|

| f <sub>SCL</sub> (kHz) | <b>R<sub>P</sub> = 4.7 k</b> Ω |

| 400                    | 0x8019                         |

| 300                    | 0x8021                         |

| 200                    | 0x8032                         |

| 100                    | 0x0096                         |

| 50                     | 0x012C                         |

| 20                     | 0x02EE                         |

## Table 59. SCL frequency ( $f_{PCLK1}$ = 50 MHz, $V_{DD} = V_{DD_{-12C}} = 3.3 V$ )<sup>(1)(2)</sup>

1.  $R_P$  = External pull-up resistance,  $f_{SCL}$  = I<sup>2</sup>C speed

2. For speeds around 200 kHz, the tolerance on the achieved speed is of ±5%. For other speed ranges, the tolerance on the achieved speed is  $\pm 2\%$ . These variations depend on the accuracy of the external components used to design the application.

### **Electrical characteristics**

| Symbol                            | Parameter                                                                       | Conditions                                           | Min                 | Тур       | Max              | Unit               |

|-----------------------------------|---------------------------------------------------------------------------------|------------------------------------------------------|---------------------|-----------|------------------|--------------------|

| t <sub>lat</sub> (2)              | Injection trigger conversion                                                    | f <sub>ADC</sub> = 30 MHz                            | -                   | -         | 0.100            | μs                 |

| 'lat` '                           | latency                                                                         |                                                      | -                   | -         | 3 <sup>(5)</sup> | 1/f <sub>ADC</sub> |

| t <sub>latr</sub> (2)             | Regular trigger conversion                                                      | f <sub>ADC</sub> = 30 MHz                            | -                   | -         | 0.067            | μs                 |

| 'latr'                            | latency                                                                         |                                                      | -                   | -         | 2 <sup>(5)</sup> | 1/f <sub>ADC</sub> |

| t <sub>S</sub> <sup>(2)</sup>     | Sampling time                                                                   | f <sub>ADC</sub> = 30 MHz                            | 0.100               | -         | 16               | μs                 |

|                                   |                                                                                 |                                                      | 3                   | -         | 480              | 1/f <sub>ADC</sub> |

| t <sub>STAB</sub> <sup>(2)</sup>  | Power-up time                                                                   |                                                      | -                   | 2         | 3                | μs                 |

|                                   |                                                                                 | f <sub>ADC</sub> = 30 MHz<br>12-bit resolution       | 0.50                | -         | 16.40            | μs                 |

|                                   | Total conversion time (including sampling time)                                 | f <sub>ADC</sub> = 30 MHz<br>10-bit resolution       | 0.43                | -         | 16.34            | μs                 |

| t <sub>CONV</sub> <sup>(2)</sup>  |                                                                                 | f <sub>ADC</sub> = 30 MHz<br>8-bit resolution        | 0.37                | -         | 16.27            | μs                 |

|                                   |                                                                                 | f <sub>ADC</sub> = 30 MHz<br>6-bit resolution        | 0.30                | -         | 16.20            | μs                 |

|                                   |                                                                                 | 9 to 492 (t <sub>S</sub> for sampling approximation) | +n-bit resolution f | or succes | ssive            | 1/f <sub>ADC</sub> |

|                                   | $f_S^{(2)}$ Sampling rate<br>( $f_{ADC}$ = 30 MHz, and<br>$t_S$ = 3 ADC cycles) | 12-bit resolution<br>Single ADC                      | -                   | -         | 2                | Msps               |

| f <sub>S</sub> <sup>(2)</sup>     |                                                                                 | 12-bit resolution<br>Interleave Dual ADC<br>mode     | -                   | -         | 3.75             | Msps               |

|                                   |                                                                                 | 12-bit resolution<br>Interleave Triple ADC<br>mode   | -                   | -         | 6                | Msps               |

| I <sub>VREF+</sub> <sup>(2)</sup> | ADC V <sub>REF</sub> DC current<br>consumption in conversion<br>mode            |                                                      | -                   | 300       | 500              | μA                 |

| I <sub>VDDA</sub> <sup>(2)</sup>  | ADC V <sub>DDA</sub> DC current<br>consumption in conversion<br>mode            |                                                      | -                   | 1.6       | 1.8              | mA                 |

### Table 65. ADC characteristics (continued)

1. V<sub>DDA</sub> minimum value of 1.7 V is possible with the use of an external power supply supervisor (refer to Section 3.15.2: Internal reset OFF).

2. Guaranteed by characterization results.

3.  $V_{REF+}$  is internally connected to  $V_{DDA}$  and  $V_{REF-}$  is internally connected to  $V_{SSA}$ .

4.  $R_{ADC}$  maximum value is given for V<sub>DD</sub>=1.7 V, and minimum value for V<sub>DD</sub>=3.3 V.

5. For external triggers, a delay of  $1/f_{PCLK2}$  must be added to the latency specified in *Table 65*.

| Symbol              | Parameter                             | Conditions                                       | Min  | Тур | Max | Unit |  |

|---------------------|---------------------------------------|--------------------------------------------------|------|-----|-----|------|--|

| f <sub>PP</sub>     | Clock frequency in data transfer mode | -                                                | 0    | -   | 50  | MHz  |  |

| -                   | SDIO_CK/fPCLK2 frequency ratio        | -                                                | -    | -   | 8/3 | -    |  |

| t <sub>W(CKL)</sub> | Clock low time                        | fpp = 50 MHz                                     | 10.5 | 11  | -   |      |  |

| t <sub>W(CKH)</sub> | Clock high time                       | fpp = 50 MHz                                     | 8.5  | 9   | -   | ns   |  |

| CMD, D ir           | puts (referenced to CK) in MMC and    | d SD HS mode                                     |      |     |     |      |  |

| t <sub>ISU</sub>    | Input setup time HS                   | fpp = 50 MHz                                     | 2.5  | -   | -   |      |  |

| t <sub>iH</sub>     | Input hold time HS                    | fpp = 50 MHz<br>-40°C <t<sub>A&lt; 125°C</t<sub> | 5    | -   | -   | ns   |  |

|                     |                                       | fpp = 50 MHz<br>-40°C <t<sub>A&lt;+85°C</t<sub>  | 2.5  | -   | -   |      |  |

| CMD, D o            | utputs (referenced to CK) in MMC a    | nd SD HS mode                                    |      |     |     |      |  |

| t <sub>OV</sub>     | Output valid time HS                  | fpp = 50 MHz                                     | -    | 3.5 | 4   |      |  |

| t <sub>OH</sub>     | Output hold time HS                   | fpp = 50 MHz                                     | 2    | -   | -   | – ns |  |

| CMD, D ir           | nputs (referenced to CK) in SD defau  | ılt mode                                         |      |     |     |      |  |

| t <sub>ISUD</sub>   | Input setup time SD                   | fpp = 25 MHz                                     | 3    | -   | -   | ns   |  |

| t <sub>IHD</sub>    | Input hold time SD                    | fpp = 25 MHz                                     | 4    | -   | -   |      |  |

| CMD, D o            | utputs (referenced to CK) in SD defa  | ault mode                                        |      |     |     | -    |  |

| t <sub>OVD</sub>    | Output valid default time SD          | fpp =25 MHz                                      | -    | 5   | 5.5 |      |  |

| t <sub>OHD</sub>    | Output hold default time SD           | fpp =25 MHz                                      | 4.5  | -   | -   | ns   |  |

1. Guaranteed by characterization results.

2.  $V_{DD}$  = 2.7 to 3.6 V.

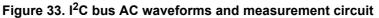

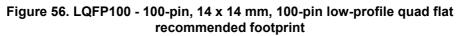

1. Dimensions are in millimeters.

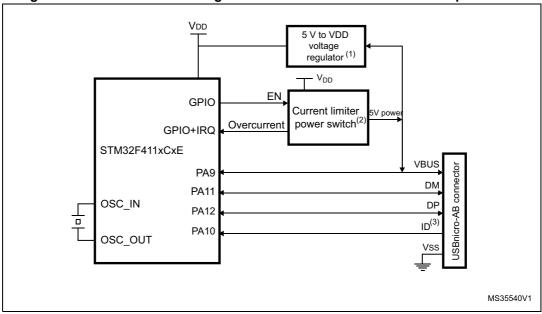

Figure 63. USB controller configured in dual mode and used in Full-Speed mode

- 1. The external voltage regulator is only needed when building a  $\mathrm{V}_{\mathrm{BUS}}$  powered device.

- The current limiter is required only if the application has to support a V<sub>BUS</sub> powered device. A basic power switch can be used if 5 V are available on the application board.

- 3. The ID pin is required in dual role only.

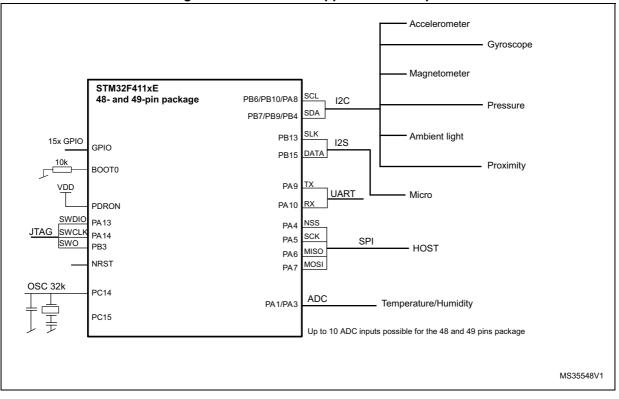

## B.2 Sensor Hub application example

### Figure 64. Sensor Hub application example

| Date        | Revision | Changes                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

|-------------|----------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 21-Nov-2016 | 5        | Updated:<br>- Features<br>- Figure 1: Compatible board design for LQFP100 package<br>- Figure 2: Compatible board design for LQFP64 package<br>- Figure 3: STM32F411xC/xE block diagram<br>- Figure 22: High-speed external clock source AC timing diagram<br>- Figure 23: Low-speed external clock source AC timing diagram<br>- Figure 23: Low-speed external clock source AC timing diagram<br>- Figure 33: I2C bus AC waveforms and measurement circuit<br>- Figure 58: UFBGA100 - 100-ball, 7 x 7 mm, 0.50 mm pitch, ultra fine pitch ball grid<br>array package outline<br>- Table 2: STM32F411xC/xE features and peripheral counts<br>- Table 8: STM32F411xC/xE pin definitions<br>- Table 8: STM32F411xC/xE pin definitions<br>- Table 13: Thermal characteristics<br>- Table 14: General operating conditions<br>- From Table 20: Typical and maximum current consumption, code with data processing<br>(ART accelerator disabled) running from SRAM - VDD = 1.7 V to Table 31: Typical<br>and maximum current consumptions in VBAT mode<br>- Table 35: High-speed external user clock characteristics<br>- Table 36: Low-speed external user clock characteristics<br>- Table 36: Low-speed external user clock characteristics<br>- Table 39: HSI oscillator characteristics<br>- Table 39: HSI oscillator characteristics<br>- Table 51: Electrical sensitivities<br>- Table 51: Electrical sensitivities<br>- Table 51: Lectrical sensitivities<br>- Table 51: Lectrical sensitivities<br>- Table 51: Lectrical sensitivities<br>- Table 51: Lectrical sensitivities<br>- Table 86: Ordering information scheme<br>Added:<br>- One-time programmable bytes<br>- Table 85: Package thermal characteristics |

| 05-Dec-2016 | 6        | Updated:<br>– Table 27: Typical and maximum current consumptions in Stop mode - VDD = 1.7 V<br>– Table 28: Typical and maximum current consumption in Stop mode - VDD=3.6 V<br>– Table 29: Typical and maximum current consumption in Standby mode - VDD= 1.7 V<br>– Table 30: Typical and maximum current consumption in Standby mode - VDD= 3.6 V                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |