Welcome to **E-XFL.COM**

What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded - Microcontrollers</u>"

| Details                    |                                                                         |

|----------------------------|-------------------------------------------------------------------------|

| Product Status             | Active                                                                  |

| Core Processor             | ARM® Cortex®-M4                                                         |

| Core Size                  | 32-Bit Single-Core                                                      |

| Speed                      | 100MHz                                                                  |

| Connectivity               | I <sup>2</sup> C, IrDA, LINbus, MMC/SD/SDIO, SPI, UART/USART, USB OTG   |

| Peripherals                | Brown-out Detect/Reset, DMA, I <sup>2</sup> S, POR, PWM, WDT            |

| Number of I/O              | 81                                                                      |

| Program Memory Size        | 512KB (512K x 8)                                                        |

| Program Memory Type        | FLASH                                                                   |

| EEPROM Size                | -                                                                       |

| RAM Size                   | 128K x 8                                                                |

| Voltage - Supply (Vcc/Vdd) | 1.7V ~ 3.6V                                                             |

| Data Converters            | A/D 16x12b                                                              |

| Oscillator Type            | Internal                                                                |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                       |

| Mounting Type              | Surface Mount                                                           |

| Package / Case             | 100-UFBGA                                                               |

| Supplier Device Package    | 100-UFBGA (7x7)                                                         |

| Purchase URL               | https://www.e-xfl.com/product-detail/stmicroelectronics/stm32f411veh6tr |

| Table 42. | PLLI2S (audio PLL) characteristics                                                         | 89    |

|-----------|--------------------------------------------------------------------------------------------|-------|

| Table 43. | SSCG parameter constraints                                                                 |       |

| Table 44. | Flash memory characteristics                                                               |       |

| Table 45. | Flash memory programming                                                                   |       |

| Table 46. | Flash memory programming with V <sub>PP</sub> voltage                                      |       |

| Table 47. | Flash memory endurance and data retention                                                  |       |

| Table 48. | EMS characteristics for LQFP100 package                                                    | 94    |

| Table 49. | EMI characteristics for LQFP100                                                            |       |

| Table 50. | ESD absolute maximum ratings                                                               | 95    |

| Table 51. | Electrical sensitivities                                                                   | 96    |

| Table 52. | I/O current injection susceptibility                                                       | 96    |

| Table 53. | I/O static characteristics                                                                 | 97    |

| Table 54. | Output voltage characteristics                                                             | . 100 |

| Table 55. | I/O AC characteristics                                                                     | . 101 |

| Table 56. | NRST pin characteristics                                                                   | . 103 |

| Table 57. | TIMx characteristics                                                                       | . 104 |

| Table 58. | I <sup>2</sup> C characteristics                                                           | . 105 |

| Table 59. | SCL frequency (f <sub>PCLK1</sub> = 50 MHz, V <sub>DD</sub> = V <sub>DD_I2C</sub> = 3.3 V) | . 106 |

| Table 60. | SPI dynamic characteristics                                                                |       |

| Table 61. | I <sup>2</sup> S dynamic characteristics                                                   | . 110 |

| Table 62. | USB OTG FS startup time                                                                    | . 112 |

| Table 63. | USB OTG FS DC electrical characteristics                                                   | . 112 |

| Table 64. | USB OTG FS electrical characteristics                                                      | . 113 |

| Table 65. | ADC characteristics                                                                        | . 113 |

| Table 66. | ADC accuracy at f <sub>ADC</sub> = 18 MHz                                                  | . 115 |

| Table 67. | ADC accuracy at f <sub>ADC</sub> = 30 MHz                                                  | . 115 |

| Table 68. | ADC accuracy at f <sub>ADC</sub> = 36 MHz                                                  |       |

| Table 69. | ADC dynamic accuracy at f <sub>ADC</sub> = 18 MHz - limited test conditions                |       |

| Table 70. | ADC dynamic accuracy at f <sub>ADC</sub> = 36 MHz - limited test conditions                |       |

| Table 71. | Temperature sensor characteristics                                                         |       |

| Table 72. | Temperature sensor calibration values                                                      | . 119 |

| Table 73. | V <sub>BAT</sub> monitoring characteristics                                                |       |

| Table 74. | Embedded internal reference voltage                                                        |       |

| Table 75. | Internal reference voltage calibration values                                              |       |

| Table 76. | Dynamic characteristics: SD / MMC characteristics                                          |       |

| Table 77. | Dynamic characteristics: eMMC characteristics V <sub>DD</sub> = 1.7 V to 1.9 V             |       |

| Table 78. | RTC characteristics                                                                        | . 123 |

| Table 79. | WLCSP49 - 49-ball, 2.999 x 3.185 mm, 0.4 mm pitch wafer level chip scale                   |       |

|           | package mechanical data                                                                    | . 125 |

| Table 80. | WLCSP49 recommended PCB design rules (0.4 mm pitch)                                        | . 126 |

| Table 81. | UFQFPN48 - 48-lead, 7 x 7 mm, 0.5 mm pitch, ultra thin fine pitch                          |       |

|           | quad flat package mechanical data                                                          |       |

| Table 82. | LQFP64 - 64-pin, 10 x 10 mm, 64-pin low-profile quad flat package mechanical data          |       |

| Table 83. | LQPF100 - 100-pin, 14 x 14 mm, 100-pin low-profile quad flat package mechanical data       | a134  |

| Table 84. | UFBGA100, 7 x 7 mm, 0.50 mm pitch, ultra fine pitch ball grid array package                |       |

| <b>-</b>  | mechanical data                                                                            |       |

| Table 85. | Package thermal characteristics                                                            |       |

| Table 86. | Ordering information scheme                                                                |       |

| Table 87. | Limitations depending on the operating power supply range                                  |       |

| Table 88. | Document revision history                                                                  | . 147 |

## List of figures

| Figure 1.  | Compatible board design for LQFP100 package                                                  | 13  |

|------------|----------------------------------------------------------------------------------------------|-----|

| Figure 2.  | Compatible board design for LQFP64 package                                                   |     |

| Figure 3.  | STM32F411xC/xE block diagram                                                                 |     |

| Figure 4.  | Multi-AHB matrix                                                                             |     |

| Figure 5.  | Power supply supervisor interconnection with internal reset OFF                              | 21  |

| Figure 6.  | Regulator OFF                                                                                |     |

| Figure 7.  | Startup in regulator OFF: slow V <sub>DD</sub> slope -                                       |     |

| Ü          | power-down reset risen after V <sub>CAP 1</sub> /V <sub>CAP 2</sub> stabilization            | 24  |

| Figure 8.  | Startup in regulator OFF mode: fast V <sub>DD</sub> slope -                                  |     |

| J          | power-down reset risen before V <sub>CAP_1</sub> /V <sub>CAP_2</sub> stabilization           | 24  |

| Figure 9.  | STM32F411xC/xE WLCSP49 pinout                                                                | 33  |

| Figure 10. | STM32F411xC/xE UFQFPN48 pinout                                                               |     |

| Figure 11. | STM32F411xC/xE LQFP64 pinout                                                                 |     |

| Figure 12. | STM32F411xC/xE LQFP100 pinout                                                                |     |

| Figure 13. | STM32F411xC/xE UFBGA100 pinout                                                               |     |

| Figure 14. | Memory map                                                                                   |     |

| Figure 15. | Pin loading conditions                                                                       |     |

| Figure 16. | Input voltage measurement                                                                    |     |

| Figure 17. | Power supply scheme                                                                          |     |

| Figure 18. | Current consumption measurement scheme                                                       |     |

| Figure 19. | External capacitor C <sub>EXT</sub>                                                          |     |

| Figure 20. | Typical V <sub>BAT</sub> current consumption (LSE in low-drive mode and RTC ON)              |     |

| Figure 21. | Low-power mode wakeup                                                                        |     |

| Figure 22. | High-speed external clock source AC timing diagram                                           |     |

| Figure 23. | Low-speed external clock source AC timing diagram                                            |     |

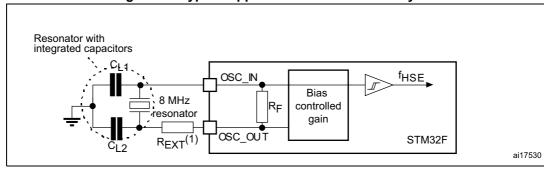

| Figure 24. | Typical application with an 8 MHz crystal                                                    |     |

| Figure 25. | Typical application with a 32.768 kHz crystal                                                |     |

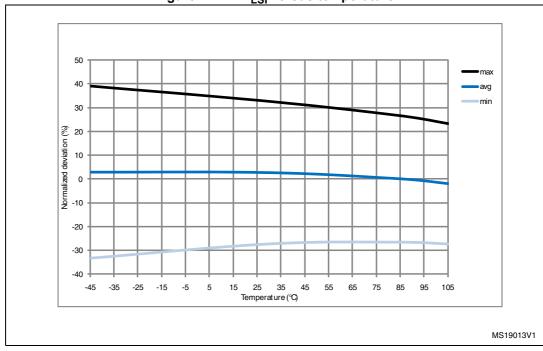

| Figure 26. | ACC <sub>HSI</sub> versus temperature                                                        |     |

| Figure 27. | ACC <sub>I SI</sub> versus temperature                                                       |     |

| Figure 28. | PLL output clock waveforms in center spread mode                                             |     |

| Figure 29. | PLL output clock waveforms in down spread mode                                               |     |

| Figure 30. | FT/TC I/O input characteristics                                                              |     |

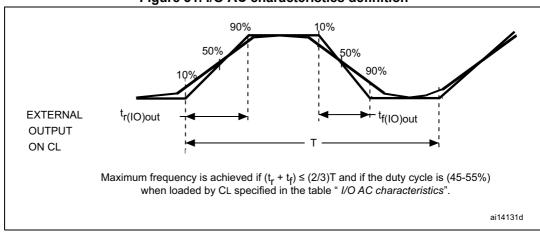

| Figure 31. | I/O AC characteristics definition                                                            |     |

| Figure 32. | Recommended NRST pin protection                                                              |     |

| Figure 33. | I <sup>2</sup> C bus AC waveforms and measurement circuit                                    |     |

| Figure 34. | SPI timing diagram - slave mode and CPHA = 0                                                 |     |

| Figure 35. | SPI timing diagram - slave mode and CPHA = 1 <sup>(1)</sup>                                  |     |

| Figure 36. | SPI timing diagram - master mode <sup>(1)</sup>                                              | 109 |

| Figure 37. | SPI timing diagram - master mode <sup>(1)</sup>                                              | 111 |

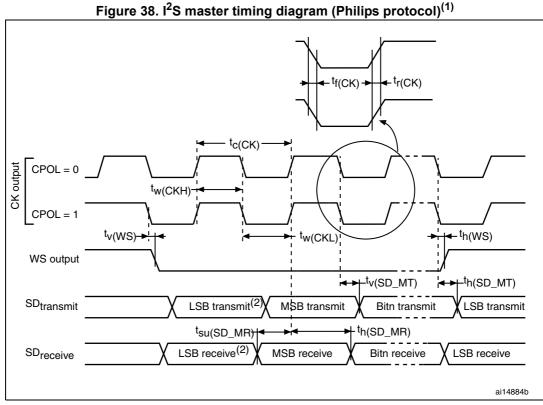

| Figure 38. | I <sup>2</sup> S master timing diagram (Philips protocol) <sup>(1)</sup>                     | 111 |

| Figure 39. | USB OTG FS timings: definition of data signal rise and fall time                             |     |

| Figure 40. | ADC accuracy characteristics                                                                 |     |

| Figure 41. | Typical connection diagram using the ADC                                                     | 117 |

| Figure 42. | Power supply and reference decoupling (V <sub>REF+</sub> not connected to V <sub>DDA</sub> ) |     |

| Figure 43. | Power supply and reference decoupling ( $V_{REF+}$ connected to $V_{DDA}$ )                  | 119 |

| Figure 44. | SDIO high-speed mode                                                                         |     |

| Figure 45. | SD default mode                                                                              |     |

| Figure 46  | WI CSP49 - 49-ball 2 999 x 3 185 mm 0 4 mm pitch wafer level                                 |     |

buses is 100 MHz while the maximum frequency of the high-speed APB domains is 100 MHz. The maximum allowed frequency of the low-speed APB domain is 50 MHz.

The devices embed a dedicated PLL (PLLI2S) which allows to achieve audio class performance. In this case, the I<sup>2</sup>S master clock can generate all standard sampling frequencies from 8 kHz to 192 kHz.

#### 3.13 Boot modes

At startup, boot pins are used to select one out of three boot options:

- · Boot from user Flash

- Boot from system memory

- Boot from embedded SRAM

The bootloader is located in system memory. It is used to reprogram the Flash memory by using USART1(PA9/10), USART2(PD5/6), USB OTG FS in device mode (PA11/12) through DFU (device firmware upgrade), I2C1(PB6/7), I2C2(PB10/3), I2C3(PA8/PB4), SPI1(PA4/5/6/7), SPI2(PB12/13/14/15) or SPI3(PA15, PC10/11/12).

For more detailed information on the bootloader, refer to Application Note: AN2606, STM32™ microcontroller system memory boot mode.

## 3.14 Power supply schemes

- VDD = 1.7 to 3.6 V: external power supply for I/Os with the internal supervisor (POR/PDR) disabled, provided externally through VDD pins. Requires the use of an external power supply supervisor connected to the VDD and NRST pins.

- V<sub>SSA</sub>, V<sub>DDA</sub> = 1.7 to 3.6 V: external analog power supplies for ADC, Reset blocks, RCs and PLL. V<sub>DDA</sub> and V<sub>SSA</sub> must be connected to V<sub>DD</sub> and V<sub>SS</sub>, respectively, with decoupling technique.

- $V_{BAT}$  = 1.65 to 3.6 V: power supply for RTC, external clock 32 kHz oscillator and backup registers (through power switch) when  $V_{DD}$  is not present.

Refer to Figure 17: Power supply scheme for more details.

## 3.15 Power supply supervisor

#### 3.15.1 Internal reset ON

This feature is available for  $V_{DD}$  operating voltage range 1.8 V to 3.6 V.

The internal power supply supervisor is enabled by holding PDR\_ON high.

The devices have an integrated power-on reset (POR) / power-down reset (PDR) circuitry coupled with a Brownout reset (BOR) circuitry. At power-on, POR is always active, and ensures proper operation starting from 1.8 V. After the 1.8 V POR threshold level is reached, the option byte loading process starts, either to confirm or modify default thresholds, or to disable BOR permanently. Three BOR thresholds are available through option bytes.

The devices remain in reset mode when  $V_{DD}$  is below a specified threshold,  $V_{POR/PDR}$  or  $V_{BOR}$ , without the need for an external reset circuit.

The devices also feature an embedded programmable voltage detector (PVD) that monitors the  $V_{DD}/V_{DDA}$  power supply and compares it to the  $V_{PVD}$  threshold. An interrupt can be generated when  $V_{DD}/V_{DDA}$  drops below the  $V_{PVD}$  threshold and/or when  $V_{DD}/V_{DDA}$  is higher than the  $V_{PVD}$  threshold. The interrupt service routine can then generate a warning message and/or put the MCU into a safe state. The PVD is enabled by software.

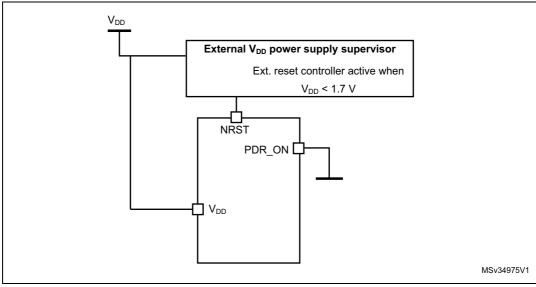

#### 3.15.2 Internal reset OFF

This feature is available only on packages featuring the PDR\_ON pin. The internal power-on reset (POR) / power-down reset (PDR) circuitry is disabled by setting the PDR\_ON pin to low.

An external power supply supervisor should monitor  $V_{DD}$  and should set the device in reset mode when  $V_{DD}$  is below 1.7 V. NRST should be connected to this external power supply supervisor. Refer to *Figure 5: Power supply supervisor interconnection with internal reset OFF*.

Figure 5. Power supply supervisor interconnection with internal reset OFF<sup>(1)</sup>

1. The PRD\_ON pin is only available on the WLCSP49 and UFBGA100 packages.

In addition to the audio PLL, a master clock input pin can be used to synchronize the I2S flow with an external PLL (or Codec output).

## 3.26 Secure digital input/output interface (SDIO)

An SD/SDIO/MMC/eMMC host interface is available, that supports MultiMediaCard System Specification Version 4.2 in three different databus modes: 1-bit (default), 4-bit and 8-bit.

The interface allows data transfer at up to 50 MHz, and is compliant with the SD Memory Card Specification Version 2.0.

The SDIO Card Specification Version 2.0 is also supported with two different databus modes: 1-bit (default) and 4-bit.

The current version supports only one SD/SDIO/MMC4.2 card at any one time and a stack of MMC4.1 or previous.

In addition to SD/SDIO/MMC/eMMC, this interface is fully compliant with the CE-ATA digital protocol Rev1.1.

## 3.27 Universal serial bus on-the-go full-speed (OTG FS)

The devices embed an USB OTG full-speed device/host/OTG peripheral with integrated transceivers. The USB OTG FS peripheral is compliant with the USB 2.0 specification and with the OTG 1.0 specification. It has software-configurable endpoint setting and supports suspend/resume. The USB OTG full-speed controller requires a dedicated 48 MHz clock that is generated by a PLL connected to the HSE oscillator. The major features are:

- Combined Rx and Tx FIFO size of 320 × 35 bits with dynamic FIFO sizing

- Supports the session request protocol (SRP) and host negotiation protocol (HNP)

- 4 bidirectional endpoints

- 8 host channels with periodic OUT support

- HNP/SNP/IP inside (no need for any external resistor)

- For OTG/Host modes, a power switch is needed in case bus-powered devices are connected

## 3.28 General-purpose input/outputs (GPIOs)

Each of the GPIO pins can be configured by software as output (push-pull or open-drain, with or without pull-up or pull-down), as input (floating, with or without pull-up or pull-down) or as peripheral alternate function. Most of the GPIO pins are shared with digital or analog alternate functions. All GPIOs are high-current-capable and have speed selection to better manage internal noise, power consumption and electromagnetic emission.

The I/O configuration can be locked if needed by following a specific sequence in order to avoid spurious writing to the I/Os registers.

Fast I/O handling allowing maximum I/O toggling up to 100 MHz.

Figure 13. STM32F411xC/xE UFBGA100 pinout

|     |                  |             | iguie | 13. 31 | WIJZF | 111xC/x | L OFB          | GAIU  | o pino | ut   |           |        |

|-----|------------------|-------------|-------|--------|-------|---------|----------------|-------|--------|------|-----------|--------|

|     | 1                | 2           | 3     | 4      | 5     | 6       | 7              | 8     | 9      | 10   | 11        | 12     |

| A   | (PE3)            | (PE1)       | (PB8) | B0070  | (PD7) | PD5     | <br> <br>  PB4 | (PB3) | (PA15) | PA14 | PA13      | (PA12) |

| В   | PE4              | PE2         | (PB9) | (PB7)  | PB6   | (PD6)   | PD4            | (PD3) | (PD1)  | C12  | PC10      | (PA11) |

| С   | C13<br>NTLTA     | MP PE5      | (PE0) | VDD    | PB5   |         | <br>           | PD2   | PD0    | C11  | VCAP<br>2 | PA10   |

| D   | FC14<br>OSC32_IN | PE6         | VSS   |        |       |         | <br>           |       |        | PA9  | PA8       | PC9    |

| E   | OSC32_0          | VBAT        | BYPAS | SS_REG |       |         | <br>           |       |        | PC8  | PC7       | PC6    |

| F _ | PHO<br>SC N      | VSS         |       |        |       |         | <br> <br>      |       |        |      | vss       | (vss)  |

| G   | PH1<br>OSC OI    | JT (VDD)    |       |        |       |         | <br>           |       |        |      | (VDD)     | (VDD)  |

| н   | PCO              | NRS         | PDR   | ON     |       |         | <br>           |       |        | PD15 | PD14      | PD13   |

| J   | VSSA             | PC1         | PC2   |        |       |         |                |       |        | PD12 | (PD11)    | (PD10) |

| К   | VREIT-           | PC3         | PA2   | PA5    | PC4   |         | <br>           | PD9   | (PB11) | PB15 | PB14      | (PB13) |

| L   | VREP+            | PA0<br>WKUP | (PA3) | PA6    | PC5   | PB2     | PE8            | PE10  | PE12   | PB10 | (VCAP)    | (PB12) |

| М   | (VDDA)           | (PA1)       | PA4   | PA7    | (PB0) | (PB1)   | PE7            | PE9   | (PE11) | PE13 | PE14      | PE15   |

| L   |                  |             |       |        |       |         |                |       |        |      |           |        |

|     |                  |             |       |        |       |         |                |       |        |      |           |        |

<sup>1.</sup> This figure shows the package top view

Table 8. STM32F411xC/xE pin definitions (continued)

|          | Pir    | n numb  | oer     |          |                                                      |          |               |       |                                                                   |                      |

|----------|--------|---------|---------|----------|------------------------------------------------------|----------|---------------|-------|-------------------------------------------------------------------|----------------------|

| UFQFPN48 | LQFP64 | WLCSP49 | LQFP100 | UFBGA100 | Pin name<br>(function after<br>reset) <sup>(1)</sup> | Pin type | I/O structure | Notes | Alternate functions                                               | Additional functions |

| -        | 24     | -       | 33      | K5       | PC4                                                  | I/O      | FT            | ı     | EVENTOUT                                                          | ADC1_14              |

| -        | 25     | -       | 34      | L5       | PC5                                                  | I/O      | FT            | ı     | EVENTOUT                                                          | ADC1_15              |

| 18       | 26     | G5      | 35      | M5       | PB0                                                  | I/O      | FT            | -     | TIM1_CH2N,<br>TIM3_CH3,<br>SPI5_SCK/I2S5_CK,<br>EVENTOUT          | ADC1_8               |

| 19       | 27     | G4      | 36      | M6       | PB1                                                  | I/O      | FT            | ı     | TIM1_CH3N,<br>TIM3_CH4,<br>SPI5_NSS/I2S5_WS,<br>EVENTOUT          | ADC1_9               |

| 20       | 28     | G3      | 37      | L6       | PB2                                                  | I/O      | FT            | ı     | EVENTOUT                                                          | BOOT1                |

| -        | -      | -       | 38      | M7       | PE7                                                  | I/O      | FT            | -     | TIM1_ETR,<br>EVENTOUT                                             | -                    |

| -        | -      | -       | 39      | L7       | PE8                                                  | I/O      | FT            | -     | TIM1_CH1N,<br>EVENTOUT                                            | -                    |

| -        | -      | -       | 40      | M8       | PE9                                                  | I/O      | FT            | -     | TIM1_CH1,<br>EVENTOUT                                             | -                    |

| -        | -      | -       | 41      | L8       | PE10                                                 | I/O      | FT            | -     | TIM1_CH2N,<br>EVENTOUT                                            | -                    |

| -        | -      | -       | 42      | M9       | PE11                                                 | I/O      | FT            | -     | TIM1_CH2,<br>SPI4_NSS/I2S4_WS,<br>SPI5_NSS/I2S5_WS,<br>EVENTOUT   | -                    |

| -        | -      | -       | 43      | L9       | PE12                                                 | I/O      | FT            | -     | TIM1_CH3N,<br>SPI4_SCK/I2S4_CK,<br>SPI5_SCK/I2S5_CK,<br>EVENTOUT  | -                    |

| -        | -      | -       | 44      | M10      | PE13                                                 | I/O      | FT            | -     | TIM1_CH3,<br>SPI4_MISO,<br>SPI5_MISO,<br>EVENTOUT                 | -                    |

| -        | -      | -       | 45      | M11      | PE14                                                 | I/O      | FT            | -     | TIM1_CH4,<br>SPI4_MOSI/I2S4_SD,<br>SPI5_MOSI/I2S5_SD,<br>EVENTOUT | -                    |

| -        | -      | -       | 46      | M12      | PE15                                                 | I/O      | FT            | -     | TIM1_BKIN,<br>EVENTOUT                                            | -                    |

Figure 24. Typical application with an 8 MHz crystal

1. R<sub>EXT</sub> value depends on the crystal characteristics.

#### Low-speed external clock generated from a crystal/ceramic resonator

The low-speed external (LSE) clock can be supplied with a 32.768 kHz crystal/ceramic resonator oscillator. All the information given in this paragraph are based on characterization results obtained with typical external components specified in *Table 38*. In the application, the resonator and the load capacitors have to be placed as close as possible to the oscillator pins in order to minimize output distortion and startup stabilization time. Refer to the crystal resonator manufacturer for more details on the resonator characteristics (frequency, package, accuracy).

The LSE high-power mode allows to cover a wider range of possible crystals but with a cost of higher power consumption.

|                                     |                          | CITAL MOTORITOR (ILSE         |     | · · · · · · · · · · · · · · · · · · · |      |      |

|-------------------------------------|--------------------------|-------------------------------|-----|---------------------------------------|------|------|

| Symbol                              | Parameter                | Conditions                    | Min | Тур                                   | Max  | Unit |

| $R_{F}$                             | Feedback resistor        | -                             | -   | 18.4                                  | -    | МΩ   |

| I <sub>DD</sub>                     | LSE current consumption  | Low-power mode (default)      | -   | -                                     | 1    | μA   |

|                                     | Consumption              | High-drive mode               | -   | -                                     | 3    |      |

| G <sub>m</sub> _crit_max            | Maximum critical crystal | Startup, low-power mode       | -   | -                                     | 0.56 | µA/V |

| G <sub>m_</sub> GIIL_IIIax          | g <sub>m</sub>           | Startup, high-drive mode      | -   | -                                     | 1.50 | μν ν |

| t <sub>SU(LSE)</sub> <sup>(2)</sup> | startup time             | V <sub>DD</sub> is stabilized | -   | 2                                     | -    | S    |

Table 38. LSE oscillator characteristics ( $f_{LSE}$  = 32.768 kHz) <sup>(1)</sup>

Note:

For information on selecting the crystal, refer to the application note AN2867 "Oscillator design guide for ST microcontrollers" available from the ST website www.st.com. For information about the LSE high-power mode, refer to the reference manual RM0383.

<sup>1.</sup> Guaranteed by design.

t<sub>SU(LSE)</sub> is the startup time measured from the moment it is enabled (by software) to a stabilized 32.768 kHz oscillation is reached. This value is guaranteed by characterization. It is measured for a standard crystal resonator and it can vary significantly with the crystal manufacturer.

Figure 27. ACC<sub>LSI</sub> versus temperature

## 6.3.10 PLL characteristics

The parameters given in *Table 41* and *Table 42* are derived from tests performed under temperature and  $V_{DD}$  supply voltage conditions summarized in *Table 14*.

| Symbol                 | Parameter                          | Conditio       | Conditions         |                     | Тур  | Max  | Unit |

|------------------------|------------------------------------|----------------|--------------------|---------------------|------|------|------|

| f <sub>PLL_IN</sub>    | PLL input clock <sup>(1)</sup>     |                |                    | 0.95 <sup>(2)</sup> | 1    | 2.10 | MHz  |

| f <sub>PLL_OUT</sub>   | PLL multiplier output clock        |                |                    | 24                  | -    | 100  | MHz  |

| f <sub>PLL48_OUT</sub> | 48 MHz PLL multiplier output clock |                |                    | -                   | 48   | 75   | MHz  |

| f <sub>VCO_OUT</sub>   | PLL VCO output                     |                |                    | 100                 | -    | 432  | MHz  |

| +                      | PLL lock time                      | VCO freq = 100 | 75                 | -                   | 200  | 116  |      |

| t <sub>LOCK</sub>      | PLL IOCK UITIE                     | VCO freq = 432 | 100                | -                   | 300  | μs   |      |

|                        |                                    |                | RMS                | -                   | 25   | -    |      |

| Jitter <sup>(3)</sup>  | Cycle-to-cycle jitter              | System clock   | peak<br>to<br>peak | -                   | ±150 | -    |      |

| Jitter(3)              |                                    | 100 MHz        | RMS                | -                   | 15   | -    | ps   |

|                        | Period Jitter                      |                | peak<br>to<br>peak | -                   | ±200 | -    | 1    |

**Table 41. Main PLL characteristics**

|                      | ore recruitment memory pro                              | J FF       | <u> </u>           | 1   | · · · /            |      |

|----------------------|---------------------------------------------------------|------------|--------------------|-----|--------------------|------|

| Symbol               | Parameter                                               | Conditions | Min <sup>(1)</sup> | Тур | Max <sup>(1)</sup> | Unit |

| $V_{prog}$           | Programming voltage                                     |            | 2.7                | -   | 3.6                | V    |

| $V_{PP}$             | V <sub>PP</sub> voltage range                           |            | 7                  | -   | 9                  | V    |

| I <sub>PP</sub>      | Minimum current sunk on the V <sub>PP</sub> pin         |            | 10                 | -   | -                  | mA   |

| t <sub>VPP</sub> (3) | Cumulative time during which V <sub>PP</sub> is applied |            | -                  | -   | 1                  | hour |

Table 46. Flash memory programming with V<sub>PP</sub> voltage (continued)

- 1. Guaranteed by design.

- 2. The maximum programming time is measured after 100K erase operations.

- 3. V<sub>PP</sub> should only be connected during programming/erasing.

Table 47. Flash memory endurance and data retention

| Ob. a.l.         | D              | O a malistia ma                                                                                                                 | Value              | 1114    |

|------------------|----------------|---------------------------------------------------------------------------------------------------------------------------------|--------------------|---------|

| Symbol           | Parameter      | Conditions                                                                                                                      | Min <sup>(1)</sup> | Unit    |

| N <sub>END</sub> | Endurance      | $T_A$ = - 40 to + 85 °C (temp. range 6)<br>$T_A$ = - 40 to + 105 °C (temp. range 7)<br>$T_A$ = - 40 to + 125 °C (temp. range 3) | 10                 | kcycles |

|                  |                | 1 kcycle <sup>(2)</sup> at T <sub>A</sub> = 85 °C                                                                               | 30                 |         |

|                  | Data retention | 1 kcycle <sup>(2)</sup> at T <sub>A</sub> = 105 °C                                                                              | 10                 | Years   |

| t <sub>RET</sub> | Data retention | 1 kcycle <sup>(2)</sup> at T <sub>A</sub> = 125 °C                                                                              | 3                  | Teals   |

|                  |                | 10 kcycle <sup>(2)</sup> at T <sub>A</sub> = 55 °C                                                                              | 20                 |         |

- 1. Guaranteed by characterization results.

- 2. Cycling performed over the whole temperature range.

#### 6.3.13 EMC characteristics

Susceptibility tests are performed on a sample basis during device characterization.

#### Functional EMS (electromagnetic susceptibility)

While a simple application is executed on the device (toggling 2 LEDs through I/O ports). the device is stressed by two electromagnetic events until a failure occurs. The failure is indicated by the LEDs:

- **Electrostatic discharge (ESD)** (positive and negative) is applied to all device pins until a functional disturbance occurs. This test is compliant with the IEC 61000-4-2 standard.

- FTB: A burst of fast transient voltage (positive and negative) is applied to V<sub>DD</sub> and V<sub>SS</sub> through a 100 pF capacitor, until a functional disturbance occurs. This test is compliant with the IEC 61000-4-4 standard.

A device reset allows normal operations to be resumed.

The test results are given in *Table 49*. They are based on the EMS levels and classes defined in application note AN1709.

#### Static latchup

Two complementary static tests are required on six parts to assess the latchup performance:

- A supply overvoltage is applied to each power supply pin

- A current injection is applied to each input, output and configurable I/O pin

These tests are compliant with EIA/JESD 78A IC latchup standard.

Table 51. Electrical sensitivities

| Symbol | Parameter             | Conditions                                      | Class      |

|--------|-----------------------|-------------------------------------------------|------------|

| LU     | Static latch-up class | T <sub>A</sub> = + 125 °C conforming to JESD78A | II level A |

#### 6.3.15 I/O current injection characteristics

As a general rule, current injection to the I/O pins, due to external voltage below  $V_{SS}$  or above  $V_{DD}$  (for standard, 3 V-capable I/O pins) should be avoided during normal product operation. However, in order to give an indication of the robustness of the microcontroller in cases when abnormal injection accidentally happens, susceptibility tests are performed on a sample basis during device characterization.

#### Functional susceptibility to I/O current injection

While a simple application is executed on the device, the device is stressed by injecting current into the I/O pins programmed in floating input mode. While current is injected into the I/O pin, one at a time, the device is checked for functional failures.

The failure is indicated by an out of range parameter: ADC error above a certain limit (>5 LSB TUE), out of conventional limits of induced leakage current on adjacent pins (out of  $-5 \,\mu\text{A/+0}\,\mu\text{A}$  range), or other functional failure (for example reset, oscillator frequency deviation).

Negative induced leakage current is caused by negative injection and positive induced leakage current by positive injection.

The test results are given in Table 52.

Table 52. I/O current injection susceptibility<sup>(1)</sup>

|                  |                                                                                                                                                           | Functional s       |                    |      |

|------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------|--------------------|------|

| Symbol           | Description                                                                                                                                               | Negative injection | Positive injection | Unit |

|                  | Injected current on BOOT0 pin                                                                                                                             | -0                 | NA                 |      |

|                  | Injected current on NRST pin                                                                                                                              | -0                 | NA                 |      |

| I <sub>INJ</sub> | Injected current on PB3, PB4, PB5, PB6, PB7, PB8, PB9, PC13, PC14, PC15, PH1, PDR_ON, PC0, PC1,PC2, PC3, PD1, PD5, PD6, PD7, PE0, PE2, PE3, PE4, PE5, PE6 | -0                 | NA                 | mA   |

|                  | Injected current on any other FT pin                                                                                                                      | <b>–</b> 5         | NA                 |      |

|                  | Injected current on any other pins                                                                                                                        | <b>-</b> 5         | +5                 |      |

<sup>1.</sup> NA = not applicable.

| Symbol                                                          | Param                                             | eter                                          | Conditions        | Min | Тур | Max | Unit |

|-----------------------------------------------------------------|---------------------------------------------------|-----------------------------------------------|-------------------|-----|-----|-----|------|

| R <sub>PU</sub> Weak pull-up equivalent resistor <sup>(6)</sup> | equivalent                                        | All pins<br>except for<br>PA10<br>(OTG_FS_ID) | $V_{IN} = V_{SS}$ | 30  | 40  | 50  |      |

|                                                                 | resistor                                          | PA10<br>(OTG_FS_ID)                           | -                 | 7   | 10  | 14  | kΩ   |

| R <sub>PD</sub>                                                 | Weak pull-down equivalent resistor <sup>(7)</sup> | All pins<br>except for<br>PA10<br>(OTG_FS_ID) | $V_{IN} = V_{DD}$ | 30  | 40  | 50  | KS2  |

| . 5                                                             | resistor                                          | PA10<br>(OTG_FS_ID)                           | -                 | 7   | 10  | 14  |      |

| C <sub>IO</sub> (8)                                             | I/O pin capacitano                                | е                                             | -                 | -   | 5   | -   | pF   |

Table 53. I/O static characteristics (continued)

- 1. Guaranteed by test in production.

- 2. Guaranteed by design.

- 3. With a minimum of 200 mV.

- Leakage could be higher than the maximum value, if negative current is injected on adjacent pins, Refer to Table 52: I/O current injection susceptibility

- To sustain a voltage higher than VDD +0.3 V, the internal pull-up/pull-down resistors must be disabled. Leakage could be higher than the maximum value, if negative current is injected on adjacent pins. Refer to *Table 52: I/O current injection* susceptibility

- 6. Pull-up resistors are designed with a true resistance in series with a switchable PMOS. This PMOS contribution to the series resistance is minimum (~10% order).

- Pull-down resistors are designed with a true resistance in series with a switchable NMOS. This NMOS contribution to the series resistance is minimum (~10% order).

- 8. Hysteresis voltage between Schmitt trigger switching levels. Guaranteed by characterization results.

All I/Os are CMOS and TTL compliant (no software configuration required). Their characteristics cover more than the strict CMOS-technology or TTL parameters. The coverage of these requirements for FT and TC I/Os is shown in *Figure 30*.

| OSPEEDRy<br>[1:0] bit<br>value <sup>(1)</sup> | Symbol                  | Parameter                                                       | Conditions                                       | Min | Тур | Max                | Unit |

|-----------------------------------------------|-------------------------|-----------------------------------------------------------------|--------------------------------------------------|-----|-----|--------------------|------|

|                                               |                         |                                                                 | C <sub>L</sub> = 30 pF, V <sub>DD</sub> ≥ 2.70 V | -   | -   | 100 <sup>(4)</sup> |      |

|                                               | F <sub>max(IO)out</sub> | Maximum frequency <sup>(3)</sup>                                | C <sub>L</sub> = 30 pF, V <sub>DD</sub> ≥ 1.7 V  | -   | -   | 50 <sup>(4)</sup>  | MHz  |

|                                               |                         |                                                                 | C <sub>L</sub> = 30 pF, V <sub>DD</sub> ≥ 2.70 V | -   | -   | 4                  |      |

| 11                                            | time and                | Output high to low level fall time and output low to high       | C <sub>L</sub> = 30 pF, V <sub>DD</sub> ≥ 1.7 V  | -   | -   | 6                  | ns   |

|                                               |                         | level rise time                                                 | C <sub>L</sub> = 10 pF, V <sub>DD</sub> ≥ 2.70 V | -   | -   | 2.5                |      |

|                                               |                         |                                                                 | C <sub>L</sub> = 10 pF, V <sub>DD</sub> ≥ 1.7 V  | -   | -   | 4                  |      |

| -                                             | t <sub>EXTIpw</sub>     | Pulse width of external signals detected by the EXTI controller |                                                  | 10  | -   | -                  | ns   |

Table 55. I/O AC characteristics<sup>(1)(2)</sup> (continued)

- 1. Guaranteed by characterization results.

- 2. The I/O speed is configured using the OSPEEDRy[1:0] bits. Refer to the STM32F4xx reference manual for a description of the GPIOx\_SPEEDR GPIO port output speed register.

- 3. The maximum frequency is defined in Figure 31.

- 4. For maximum frequencies above 50 MHz and  $V_{DD}$  > 2.4 V, the compensation cell should be used.

Figure 31. I/O AC characteristics definition

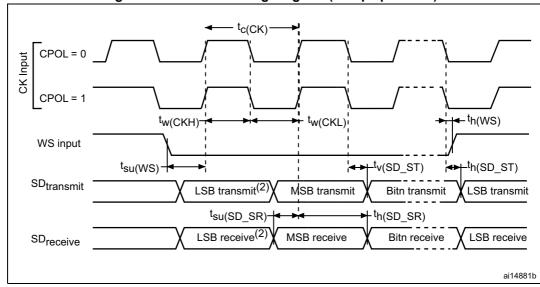

#### I<sup>2</sup>S interface characteristics

Unless otherwise specified, the parameters given in *Table 61* for the  $I^2S$  interface are derived from tests performed under the ambient temperature,  $f_{PCLKx}$  frequency and  $V_{DD}$  supply voltage conditions summarized in *Table 14*, with the following configuration:

- Output speed is set to OSPEEDRy[1:0] = 10

- Capacitive load C = 30 pF

- Measurement points are done at CMOS levels: 0.5V<sub>DD</sub>

Refer to Section 6.3.16: I/O port characteristics for more details on the input/output alternate function characteristics (CK, SD, WS).

**Symbol Parameter Conditions** Min Max Unit 256xFs<sup>(2)</sup> I2S Main clock output 256x8K MHz  $f_{MCK}$ Master data: 32 bits 64xFs I2S clock frequency MHz  $f_{CK}$ Slave data: 32 bits 64xFs I2S clock frequency duty cycle Slave receiver 30 70 %  $D_{CK}$ WS valid time Master mode 0 7  $t_{v(WS)}$ WS hold time Master mode 1.5 t<sub>h(WS)</sub> WS setup time Slave mode 1.5 t<sub>su(WS)</sub> WS hold time Slave mode 3 t<sub>h(WS)</sub> Master receiver 1 t<sub>su(SD MR)</sub> Data input setup time Slave receiver 2.5 ns t<sub>su(SD\_SR)</sub> 7 Master receiver \_ t<sub>h(SD MR)</sub> Data input hold time 2.5 Slave receiver th(SD SR) Slave transmitter (after enable edge) \_ 20  $t_{v(SD\_ST)}$ Data output valid time Master transmitter (after enable edge) 6 t<sub>v(SD MT)</sub>

Table 61. I<sup>2</sup>S dynamic characteristics<sup>(1)</sup>

Data output hold time

Note:

t<sub>h(SD ST)</sub>

t<sub>h(SD MT)</sub>

Refer to the I2S section of RM0383 reference manual for more details on the sampling frequency ( $F_S$ ).

Slave transmitter (after enable edge)

Master transmitter (after enable edge)

8

2

$f_{MCK}$ ,  $f_{CK}$ , and  $D_{CK}$  values reflect only the digital peripheral behavior. The values of these parameters might be slightly impacted by the source clock precision.  $D_{CK}$  depends mainly on the value of ODD bit. The digital contribution leads to a minimum value of (I2SDIV/(2\*I2SDIV+ODD) and a maximum value of (I2SDIV+ODD)/(2\*I2SDIV+ODD).  $F_S$  maximum value is supported for each mode/condition.

<sup>1.</sup> Guaranteed by characterization results.

<sup>2.</sup> The maximum value of 256xFs is 50 MHz (APB1 maximum frequency).

Figure 37. I<sup>2</sup>S slave timing diagram (Philips protocol)<sup>(1)</sup>

LSB transmit/receive of the previously transmitted byte. No LSB transmit/receive is sent before the first byte.

LSB transmit/receive of the previously transmitted byte. No LSB transmit/receive is sent before the first byte.

Table 76. Dynamic characteristics: SD / MMC characteristics<sup>(1)(2)</sup>

| Symbol                                                 | Parameter                                               | Conditions                                       | Min            | Тур | Max | Unit |  |  |  |  |

|--------------------------------------------------------|---------------------------------------------------------|--------------------------------------------------|----------------|-----|-----|------|--|--|--|--|

| f <sub>PP</sub>                                        | Clock frequency in data transfer mode                   | -                                                | 0 -            |     | 50  | MHz  |  |  |  |  |

| -                                                      | SDIO_CK/fPCLK2 frequency ratio                          | -                                                | -              | -   | 8/3 | -    |  |  |  |  |

| t <sub>W(CKL)</sub>                                    | Clock low time                                          | fpp = 50 MHz                                     | 50 MHz 10.5 11 |     | -   | ns   |  |  |  |  |

| t <sub>W(CKH)</sub>                                    | Clock high time                                         | fpp = 50 MHz                                     | 8.5            | 9   | -   | 113  |  |  |  |  |

| CMD, D inputs (referenced to CK) in MMC and SD HS mode |                                                         |                                                  |                |     |     |      |  |  |  |  |

| t <sub>ISU</sub>                                       | Input setup time HS                                     | fpp = 50 MHz                                     | 2.5            | -   | -   |      |  |  |  |  |

| t <sub>IH</sub>                                        | Input hold time HS                                      | fpp = 50 MHz<br>-40°C <t<sub>A&lt; 125°C</t<sub> | 5              | -   | -   | ns   |  |  |  |  |

|                                                        |                                                         | fpp = 50 MHz<br>-40°C <t<sub>A&lt;+85°C</t<sub>  | 2.5            | -   | -   |      |  |  |  |  |

| CMD, D o                                               | CMD, D outputs (referenced to CK) in MMC and SD HS mode |                                                  |                |     |     |      |  |  |  |  |

| t <sub>OV</sub>                                        | Output valid time HS                                    | fpp = 50 MHz                                     | -              | 3.5 | 4   |      |  |  |  |  |

| t <sub>OH</sub>                                        | Output hold time HS                                     | fpp = 50 MHz                                     | 2              | -   | -   | ns   |  |  |  |  |

| CMD, D in                                              | CMD, D inputs (referenced to CK) in SD default mode     |                                                  |                |     |     |      |  |  |  |  |

| t <sub>ISUD</sub>                                      | Input setup time SD                                     | fpp = 25 MHz                                     | 3              | -   | -   |      |  |  |  |  |

| t <sub>IHD</sub>                                       | Input hold time SD                                      | fpp = 25 MHz                                     | 4 -            |     | -   | ns   |  |  |  |  |

| CMD, D outputs (referenced to CK) in SD default mode   |                                                         |                                                  |                |     |     |      |  |  |  |  |

| t <sub>OVD</sub>                                       | Output valid default time SD                            | fpp =25 MHz                                      | -              | 5   | 5.5 |      |  |  |  |  |

| t <sub>OHD</sub>                                       | Output hold default time SD                             | fpp =25 MHz                                      | 4.5            | 5 - |     | ns   |  |  |  |  |

<sup>1.</sup> Guaranteed by characterization results.

<sup>2.</sup>  $V_{DD} = 2.7 \text{ to } 3.6 \text{ V}.$

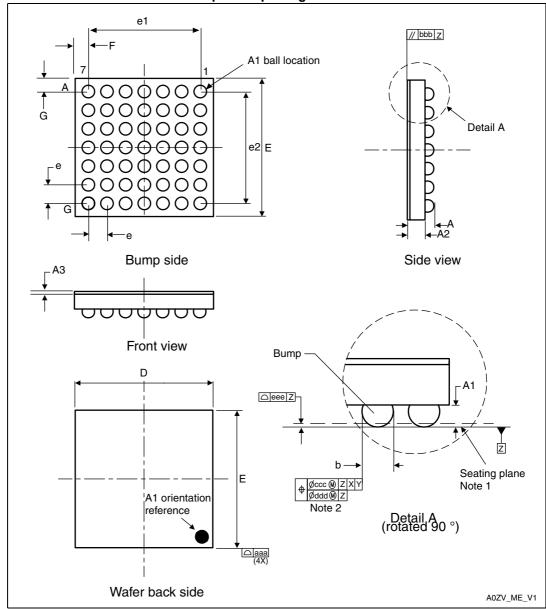

## 7 Package information

In order to meet environmental requirements, ST offers these devices in different grades of ECOPACK<sup>®</sup> packages, depending on their level of environmental compliance. ECOPACK<sup>®</sup> specifications, grade definitions and product status are available at: <a href="https://www.st.com">www.st.com</a>. ECOPACK<sup>®</sup> is an ST trademark.

## 7.1 WLCSP49 package information

Figure 46. WLCSP49 - 49-ball, 2.999 x 3.185 mm, 0.4 mm pitch wafer level chip scale package outline

1. Drawing is not to scale.

57/

Table 79. WLCSP49 - 49-ball, 2.999 x 3.185 mm, 0.4 mm pitch wafer level chip scale package mechanical data

| Min         Typ         Max         Min         Typ           A         0.525         0.555         0.585         0.0207         0.027           A1         -         0.175         -         -         0.006           A2         -         0.380         -         -         0.015           A3 <sup>(2)</sup> -         0.025         -         -         0.007           b <sup>(3)</sup> 0.220         0.250         0.280         0.0087         0.009           D         2.964         2.999         3.034         0.1167         0.118           E         3.150         3.185         3.220         0.1240         0.124 |                       |  |  |  |

|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------|--|--|--|

| Min         Typ         Max         Min         Typ           A         0.525         0.555         0.585         0.0207         0.020           A1         -         0.175         -         -         0.006           A2         -         0.380         -         -         0.015           A3 <sup>(2)</sup> -         0.025         -         -         0.000           b <sup>(3)</sup> 0.220         0.250         0.280         0.0087         0.009           D         2.964         2.999         3.034         0.1167         0.118           E         3.150         3.185         3.220         0.1240         0.129 | inches <sup>(1)</sup> |  |  |  |

| A1       -       0.175       -       -       0.006         A2       -       0.380       -       -       0.015         A3 <sup>(2)</sup> -       0.025       -       -       0.007         b <sup>(3)</sup> 0.220       0.250       0.280       0.0087       0.009         D       2.964       2.999       3.034       0.1167       0.118         E       3.150       3.185       3.220       0.1240       0.128                                                                                                                                                                                                                    | o Max                 |  |  |  |

| A2       -       0.380       -       -       0.018         A3 <sup>(2)</sup> -       0.025       -       -       0.009         b <sup>(3)</sup> 0.220       0.250       0.280       0.0087       0.009         D       2.964       2.999       3.034       0.1167       0.118         E       3.150       3.185       3.220       0.1240       0.128                                                                                                                                                                                                                                                                               | 19 0.0230             |  |  |  |

| A3 <sup>(2)</sup> -       0.025       -       -       0.00         b <sup>(3)</sup> 0.220       0.250       0.280       0.0087       0.008         D       2.964       2.999       3.034       0.1167       0.118         E       3.150       3.185       3.220       0.1240       0.128                                                                                                                                                                                                                                                                                                                                           | 69 -                  |  |  |  |

| b <sup>(3)</sup> 0.220     0.250     0.280     0.0087     0.009       D     2.964     2.999     3.034     0.1167     0.118       E     3.150     3.185     3.220     0.1240     0.128                                                                                                                                                                                                                                                                                                                                                                                                                                              | 50 -                  |  |  |  |

| D     2.964     2.999     3.034     0.1167     0.118       E     3.150     3.185     3.220     0.1240     0.129                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | 10 -                  |  |  |  |

| E 3.150 3.185 3.220 0.1240 0.125                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | 98 0.0110             |  |  |  |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | 81 0.1194             |  |  |  |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | 54 0.1268             |  |  |  |

| e - 0.400 0.015                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | 57 -                  |  |  |  |

| e1 - 2.400 0.094                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | 45 -                  |  |  |  |

| e2 - 2.400 0.094                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | 45 -                  |  |  |  |

| F - 0.2995 0.01                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | 18 -                  |  |  |  |

| G - 0.3925 0.015                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | 55 -                  |  |  |  |

| aaa - 0.100 0.003                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | 39 -                  |  |  |  |

| bbb - 0.100 0.003                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | 39 -                  |  |  |  |

| ccc - 0.100 0.000                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | 39 -                  |  |  |  |

| ddd - 0.050 0.002                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | 20 -                  |  |  |  |

| eee - 0.050 0.002                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | 20 -                  |  |  |  |

- 1. Values in inches are converted from mm and rounded to 4 decimal digits.

- 2. Back side coating

- 3. Dimension is measured at the maximum bump diameter parallel to primary datum Z.

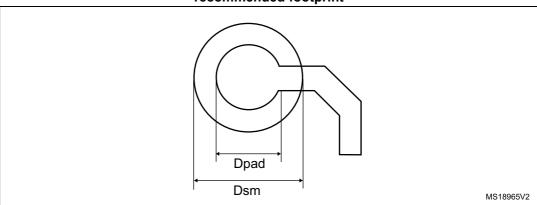

Figure 47. WLCSP49 - 49-ball, 2.999 x 3.185 mm, 0.4 mm pitch wafer level chip scale recommended footprint

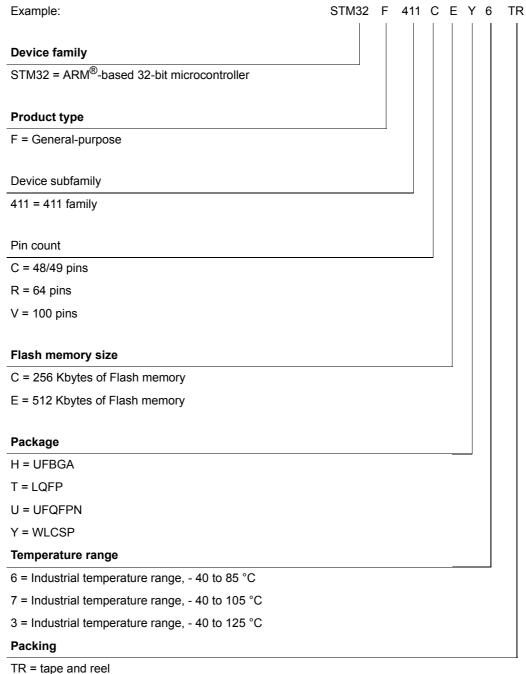

## 8 Part numbering

Table 86. Ordering information scheme

TR - tape and reel

No character = tray or tube

# Appendix A Recommendations when using the internal reset OFF

When the internal reset is OFF, the following integrated features are no longer supported:

- The integrated power-on-reset (POR)/power-down reset (PDR) circuitry is disabled.

- The brownout reset (BRO) circuitry must be disabled. By default BOR is OFF.

- The embedded programmable voltage detector (PVD) is disabled.

- V<sub>BAT</sub> functionality is no more available and VBAT pin should be connected to V<sub>DD</sub>.

## A.1 Operating conditions

Table 87. Limitations depending on the operating power supply range

| Operating power supply range               | ADC<br>operation                        | Maximum Flash memory access frequency with no wait state (f <sub>Flashmax</sub> ) | Maximum Flash memory access frequency with no wait states <sup>(1)</sup> (2) | I/O operation       | Possible<br>Flash memory<br>operations  |

|--------------------------------------------|-----------------------------------------|-----------------------------------------------------------------------------------|------------------------------------------------------------------------------|---------------------|-----------------------------------------|

| $V_{DD} = 1.7 \text{ to}$<br>2.1 $V^{(3)}$ | = 1.7 to Conversion time up to 1.2 Msps |                                                                                   | 100 MHz with<br>6 wait states                                                | No I/O compensation | 8-bit erase and program operations only |

Applicable only when the code is executed from Flash memory. When the code is executed from RAM, no wait state is required.

<sup>2.</sup> Thanks to the ART accelerator and the 128-bit Flash memory, the number of wait states given here does not impact the execution speed from Flash memory since the ART accelerator allows to achieve a performance equivalent to 0 wait state program execution.

V<sub>DD</sub>/V<sub>DDA</sub> minimum value of 1.7 V, with the use of an external power supply supervisor (refer to Section 3.15.1: Internal reset ON).

<sup>4.</sup> Prefetch is not available. Refer to AN3430 application note for details on how to adjust performance and power.