# E·XFL

#### Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

#### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Product Status             | Active                                                                |

|----------------------------|-----------------------------------------------------------------------|

| Core Processor             | ARM® Cortex®-M4                                                       |

| Core Size                  | 32-Bit Single-Core                                                    |

| Speed                      | 100MHz                                                                |

| Connectivity               | I <sup>2</sup> C, IrDA, LINbus, MMC/SD/SDIO, SPI, UART/USART, USB OTG |

| Peripherals                | Brown-out Detect/Reset, DMA, I <sup>2</sup> S, POR, PWM, WDT          |

| Number of I/O              | 81                                                                    |

| Program Memory Size        | 512KB (512K x 8)                                                      |

| Program Memory Type        | FLASH                                                                 |

| EEPROM Size                | -                                                                     |

| RAM Size                   | 128K x 8                                                              |

| Voltage - Supply (Vcc/Vdd) | 1.7V ~ 3.6V                                                           |

| Data Converters            | A/D 16x12b                                                            |

| Oscillator Type            | Internal                                                              |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                     |

| Mounting Type              | Surface Mount                                                         |

| Package / Case             | 100-LQFP                                                              |

| Supplier Device Package    | 100-LQFP (14x14)                                                      |

| Purchase URL               | https://www.e-xfl.com/product-detail/stmicroelectronics/stm32f411vet6 |

|                            |                                                                       |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

## List of tables

| Table 1.  | Device summary                                                                           | 1    |

|-----------|------------------------------------------------------------------------------------------|------|

| Table 2.  | STM32F411xC/xE features and peripheral counts                                            | . 12 |

| Table 3.  | Regulator ON/OFF and internal power supply supervisor availability                       | . 25 |

| Table 4.  | Timer feature comparison.                                                                |      |

| Table 5.  | Comparison of I2C analog and digital filters                                             |      |

| Table 6.  | USART feature comparison                                                                 |      |

| Table 7.  | Legend/abbreviations used in the pinout table                                            |      |

| Table 8.  | STM32F411xC/xE pin definitions                                                           |      |

| Table 9.  | Alternate function mapping.                                                              |      |

| Table 10. | STM32F411xC/xE                                                                           |      |

|           | register boundary addresses                                                              | . 53 |

| Table 11. | Voltage characteristics                                                                  |      |

| Table 12. | Current characteristics                                                                  |      |

| Table 13. | Thermal characteristics.                                                                 |      |

| Table 14. | General operating conditions                                                             |      |

| Table 15. | Features depending on the operating power supply range                                   |      |

| Table 16. | VCAP_1/VCAP_2 operating conditions                                                       |      |

| Table 17. | Operating conditions at power-up / power-down (regulator ON)                             |      |

| Table 18. | Operating conditions at power-up / power-down (regulator OFF).                           |      |

| Table 19. | Embedded reset and power control block characteristics.                                  |      |

| Table 20. | Typical and maximum current consumption, code with data processing (ART                  |      |

|           | accelerator disabled) running from SRAM - $V_{DD}$ = 1.7 V                               | . 68 |

| Table 21. | Typical and maximum current consumption, code with data processing (ART                  |      |

|           | accelerator disabled) running from SRAM - $V_{DD}$ = 3.6 V                               | . 69 |

| Table 22. | Typical and maximum current consumption in run mode, code with data processing           |      |

|           | (ART accelerator enabled except prefetch) running from Flash memory- $V_{DD}$ = 1.7 V.   | . 70 |

| Table 23. | Typical and maximum current consumption in run mode, code with data processing           |      |

|           | (ART accelerator enabled except prefetch) running from Flash memory - $V_{DD}$ = 3.6 V . | . 71 |

| Table 24. | Typical and maximum current consumption in run mode, code with data processing           |      |

|           | (ART accelerator disabled) running from Flash memory - $V_{DD}$ = 3.6 V                  | . 72 |

| Table 25. | Typical and maximum current consumption in run mode, code with data processing           |      |

|           | (ART accelerator enabled with prefetch) running from Flash memory - $V_{DD}$ = 3.6 V     | . 73 |

| Table 26. | Typical and maximum current consumption in Sleep mode - $V_{DD}$ = 3.6 V                 |      |

| Table 27. | Typical and maximum current consumptions in Stop mode - V <sub>DD</sub> = 1.7 V          |      |

| Table 28. | Typical and maximum current consumption in Stop mode - V <sub>DD</sub> =3.6 V            |      |

| Table 29. | Typical and maximum current consumption in Standby mode - V <sub>DD</sub> = 1.7 V        |      |

| Table 30. | Typical and maximum current consumption in Standby mode - V <sub>DD</sub> = 3.6 V        |      |

| Table 31. | Typical and maximum current consumptions in V <sub>BAT</sub> mode                        |      |

| Table 32. | Switching output I/O current consumption                                                 |      |

| Table 33. | Peripheral current consumption                                                           |      |

| Table 34. | Low-power mode wakeup timings <sup>(1)</sup>                                             | . 82 |

| Table 35. | High-speed external user clock characteristics.                                          |      |

| Table 36. | Low-speed external user clock characteristics                                            |      |

| Table 37. | HSE 4-26 MHz oscillator characteristics.                                                 |      |

| Table 38. | LSE oscillator characteristics (f <sub>LSE</sub> = 32.768 kHz)                           | . 85 |

| Table 39. | HSI oscillator characteristics                                                           | . 86 |

| Table 40. | LSI oscillator characteristics                                                           |      |

| Table 41. | Main PLL characteristics.                                                                |      |

|           |                                                                                          |      |

## 2 Description

The STM32F411xC/xE devices are based on the high-performance ARM<sup>®</sup> Cortex<sup>®</sup> -M4 32bit RISC core operating at a frequency of up to 100 MHz. The Cortex<sup>®</sup>-M4 core features a Floating point unit (FPU) single precision which supports all ARM single-precision dataprocessing instructions and data types. It also implements a full set of DSP instructions and a memory protection unit (MPU) which enhances application security.

The STM32F411xC/xE belongs to the STM32 Dynamic Efficiency<sup>™</sup> product line (with products combining power efficiency, performance and integration) while adding a new innovative feature called Batch Acquisition Mode (BAM) allowing to save even more power consumption during data batching.

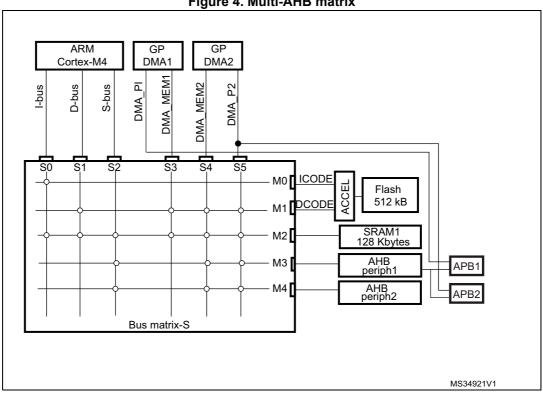

The STM32F411xC/xE incorporate high-speed embedded memories (up to 512 Kbytes of Flash memory, 128 Kbytes of SRAM), and an extensive range of enhanced I/Os and peripherals connected to two APB buses, two AHB bus and a 32-bit multi-AHB bus matrix.

All devices offer one 12-bit ADC, a low-power RTC, six general-purpose 16-bit timers including one PWM timer for motor control, two general-purpose 32-bit timers. They also feature standard and advanced communication interfaces.

- Up to three I<sup>2</sup>Cs

- Five SPIs

- Five I<sup>2</sup>Ss out of which two are full duplex. To achieve audio class accuracy, the I<sup>2</sup>S peripherals can be clocked via a dedicated internal audio PLL or via an external clock to allow synchronization.

- Three USARTs

- SDIO interface

- USB 2.0 OTG full speed interface

Refer to *Table 2: STM32F411xC/xE features and peripheral counts* for the peripherals available for each part number.

The STM32F411xC/xE operate in the - 40 to + 125 °C temperature range from a 1.7 (PDR OFF) to 3.6 V power supply. A comprehensive set of power-saving mode allows the design of low-power applications.

These features make the STM32F411xC/xE microcontrollers suitable for a wide range of applications:

- Motor drive and application control

- Medical equipment

- Industrial applications: PLC, inverters, circuit breakers

- Printers, and scanners

- Alarm systems, video intercom, and HVAC

- Home audio appliances

- Mobile phone sensor hub

Figure 3 shows the general block diagram of the devices.

### 3.8 Multi-AHB bus matrix

The 32-bit multi-AHB bus matrix interconnects all the masters (CPU, DMAs) and the slaves (Flash memory, RAM, AHB and APB peripherals) and ensures a seamless and efficient operation even when several high-speed peripherals work simultaneously.

### 3.9 DMA controller (DMA)

The devices feature two general-purpose dual-port DMAs (DMA1 and DMA2) with 8 streams each. They are able to manage memory-to-memory, peripheral-to-memory and memory-to-peripheral transfers. They feature dedicated FIFOs for APB/AHB peripherals, support burst transfer and are designed to provide the maximum peripheral bandwidth (AHB/APB).

The two DMA controllers support circular buffer management, so that no specific code is needed when the controller reaches the end of the buffer. The two DMA controllers also have a double buffering feature, which automates the use and switching of two memory buffers without requiring any special code.

Each stream is connected to dedicated hardware DMA requests, with support for software trigger on each stream. Configuration is made by software and transfer sizes between source and destination are independent.

#### 3.16.3 Regulator ON/OFF and internal power supply supervisor availability

| Package  |                                 |                                 | Power supply supervisor ON | Power supply supervisor OFF                      |

|----------|---------------------------------|---------------------------------|----------------------------|--------------------------------------------------|

| UFQFPN48 | Yes                             | No                              | Yes                        | No                                               |

| WLCSP49  | Yes                             | No                              | Yes<br>PDR_ON set to VDD   | Yes<br>PDR_ON external<br>control <sup>(1)</sup> |

| LQFP64   | Yes                             | No                              | Yes                        | No                                               |

| LQFP100  | Yes                             | No                              | Yes                        | No                                               |

| UFBGA100 | Yes<br>BYPASS_REG set to<br>VSS | Yes<br>BYPASS_REG set to<br>VDD | Yes<br>PDR_ON set to VDD   | Yes<br>PDR_ON external<br>control <sup>(1)</sup> |

Table 3. Regulator ON/OFF and internal power supply supervisor availability

1. Refer to Section 3.15: Power supply supervisor

## 3.17 Real-time clock (RTC) and backup registers

The backup domain includes:

- The real-time clock (RTC)

- 20 backup registers

The real-time clock (RTC) is an independent BCD timer/counter. Dedicated registers contain the second, minute, hour (in 12/24 hour), week day, date, month, year, in BCD (binary-coded decimal) format. Correction for 28, 29 (leap year), 30, and 31 day of the month are performed automatically. The RTC features a reference clock detection, a more precise second source clock (50 or 60 Hz) can be used to enhance the calendar precision. The RTC provides a programmable alarm and programmable periodic interrupts with wakeup from Stop and Standby modes. The sub-seconds value is also available in binary format.

It is clocked by a 32.768 kHz external crystal, resonator or oscillator, the internal low-power RC oscillator or the high-speed external clock divided by 128. The internal low-speed RC has a typical frequency of 32 kHz. The RTC can be calibrated using an external 512 Hz output to compensate for any natural quartz deviation.

Two alarm registers are used to generate an alarm at a specific time and calendar fields can be independently masked for alarm comparison. To generate a periodic interrupt, a 16-bit programmable binary auto-reload downcounter with programmable resolution is available and allows automatic wakeup and periodic alarms from every 120 µs to every 36 hours.

A 20-bit prescaler is used for the time base clock. It is by default configured to generate a time base of 1 second from a clock at 32.768 kHz.

The backup registers are 32-bit registers used to store 80 bytes of user application data when  $V_{DD}$  power is not present. Backup registers are not reset by a system, a power reset, or when the device wakes up from the Standby mode (see Section 3.18: Low-power modes).

Additional 32-bit registers contain the programmable alarm subseconds, seconds, minutes, hours, day, and date.

DocID026289 Rev 6

The RTC and backup registers are supplied through a switch that is powered either from the  $V_{DD}$  supply when present or from the  $V_{BAT}$  pin.

### 3.18 Low-power modes

The devices support three low-power modes to achieve the best compromise between low power consumption, short startup time and available wakeup sources:

#### Sleep mode

In Sleep mode, only the CPU is stopped. All peripherals continue to operate and can wake up the CPU when an interrupt/event occurs.

To further reduce the power consumption, the Flash memory can be switched off before entering in Sleep mode. Note that this requires a code execution from the RAM.

#### • Stop mode

The Stop mode achieves the lowest power consumption while retaining the contents of SRAM and registers. All clocks in the 1.2 V domain are stopped, the PLL, the HSI RC and the HSE crystal oscillators are disabled. The voltage regulator can also be put either in normal or in low-power mode.

The devices can be woken up from the Stop mode by any of the EXTI line (the EXTI line source can be one of the 16 external lines, the PVD output, the RTC alarm/ wakeup/ tamper/ time stamp events).

#### • Standby mode

The Standby mode is used to achieve the lowest power consumption. The internal voltage regulator is switched off so that the entire 1.2 V domain is powered off. The PLL, the HSI RC and the HSE crystal oscillators are also switched off. After entering Standby mode, the SRAM and register contents are lost except for registers in the backup domain when selected.

The devices exit the Standby mode when an external reset (NRST pin), an IWDG reset, a rising edge on the WKUP pin, or an RTC alarm/ wakeup/ tamper/time stamp event occurs.

Standby mode is not supported when the embedded voltage regulator is bypassed and the 1.2 V domain is controlled by an external power.

### 3.19 V<sub>BAT</sub> operation

The VBAT pin allows to power the device  $V_{BAT}$  domain from an external battery, an external super-capacitor, or from  $V_{DD}$  when no external battery and an external super-capacitor are present.

$V_{\text{BAT}}$  operation is activated when  $V_{\text{DD}}$  is not present.

The VBAT pin supplies the RTC and the backup registers.

Note: When the microcontroller is supplied from VBAT, external interrupts and RTC alarm/events do not exit it from  $V_{BAT}$  operation. When PDR\_ON pin is not connected to  $V_{DD}$  (internal Reset OFF), the  $V_{BAT}$  functionality is no more available and VBAT pin should be connected to  $V_{DD}$ .

STM32F411xC STM32F411xE

Pinouts and pin description

|        |      |        |           |                     | 7                        | able 9. A          | lternate f                               | unction ma                                              | apping (d                       | continue      | a)            |         |      |             |      |      |              |

|--------|------|--------|-----------|---------------------|--------------------------|--------------------|------------------------------------------|---------------------------------------------------------|---------------------------------|---------------|---------------|---------|------|-------------|------|------|--------------|

|        |      | AF00   | AF01      | AF02                | AF03                     | AF04               | AF05                                     | AF06                                                    | AF07                            | AF08          | AF09          | AF10    | AF11 | AF12        | AF13 | AF14 | AF15         |

|        | Port | SYS_AF | TIM1/TIM2 | TIM3/<br>TIM4/ TIM5 | TIM9/<br>TIM10/<br>TIM11 | I2C1/I2C2/<br>I2C3 | SPI1/I2S1S<br>PI2/<br>I2S2/SPI3/<br>I2S3 | SPI2/I2S2/<br>SPI3/<br>I2S3/SPI4/<br>I2S4/SPI5/<br>I2S5 | SPI3/I2S3/<br>USART1/<br>USART2 | USART6        | 12C2/<br>12C3 | OTG1_FS |      | SDIO        |      |      |              |

|        | PC0  | -      | -         | -                   | -                        | -                  | -                                        | -                                                       | -                               | -             | -             | -       | -    | -           | -    | -    | EVENT<br>OUT |

|        | PC1  | -      | -         | -                   | -                        | -                  | -                                        | -                                                       | -                               | -             | -             | -       | -    | -           | -    | -    | EVENT<br>OUT |

|        | PC2  | -      | -         | -                   | -                        | -                  | SPI2_MISO                                | I2S2ext_SD                                              | -                               | -             | -             | -       | -    | -           | -    | -    | EVENT<br>OUT |

|        | PC3  | -      | -         | -                   | -                        | -                  | SPI2_MOSI<br>/I2S2_SD                    | -                                                       | -                               | -             | -             | -       | -    | -           | -    | -    | EVENT<br>OUT |

|        | PC4  | -      | -         | -                   | -                        | -                  |                                          | -                                                       | -                               | -             | -             | -       | -    | -           | -    | -    | EVENT<br>OUT |

|        | PC5  | -      | -         | -                   | -                        | -                  |                                          | -                                                       | -                               | -             | -             | -       | -    | -           | -    | -    | EVENT<br>OUT |

|        | PC6  | -      | -         | TIM3_CH1            | -                        | -                  | I2S2_MCK                                 | -                                                       | -                               | USART6_<br>TX | -             | -       | -    | SDIO_<br>D6 | -    | -    | EVENT<br>OUT |

| Port C | PC7  | -      | -         | TIM3_CH2            | -                        | -                  | SPI2_SCK/I<br>2S2_CK                     | I2S3_MCK                                                | -                               | USART6_<br>RX | -             | -       | -    | SDIO_<br>D7 | -    | -    | EVENT<br>OUT |

|        | PC8  | -      | -         | TIM3_CH3            | -                        | -                  | -                                        | -                                                       | -                               | USART6_<br>CK | -             | -       | -    | SDIO_<br>D0 | -    | -    | EVENT<br>OUT |

|        | PC9  | MCO_2  | -         | TIM3_CH4            | -                        | I2C3_SDA           | I2S2_CKIN                                | -                                                       | -                               |               | -             | -       | -    | SDIO_<br>D1 | -    | -    | EVENT<br>OUT |

|        | PC10 | -      | -         | -                   | -                        | -                  | -                                        | SPI3_SCK/I2<br>S3_CK                                    | -                               | -             | -             | -       | -    | SDIO_<br>D2 | -    | -    | EVENT<br>OUT |

|        | PC11 | -      | -         | -                   | -                        | -                  | I2S3ext_SD                               | SPI3_MISO                                               | -                               | -             | -             | -       | -    | SDIO_<br>D3 | -    | -    | EVENT<br>OUT |

|        | PC12 | -      | -         | -                   | -                        | -                  | -                                        | SPI3_MOSI/I<br>2S3_SD                                   | -                               | -             | -             | -       | -    | SDIO_<br>CK | -    | -    | EVENT<br>OUT |

|        | PC13 | -      | -         | -                   | -                        | -                  | -                                        | -                                                       | -                               | -             | -             | -       | -    | -           | -    | -    | -            |

|        | PC14 | -      | -         | -                   | -                        | -                  | -                                        | -                                                       | -                               | -             | -             | -       | -    | -           | -    | -    | -            |

|        | PC15 | -      | -         | -                   | -                        | -                  | -                                        | -                                                       | -                               | -             | -             | -       | -    | -           | -    | -    | -            |

\_ . . . . .

DocID026289 Rev 6

5

49/149

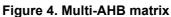

## 5 Memory mapping

The memory map is shown in Figure 14.

Figure 14. Memory map

Table 10. STM32F411xC/xE register boundary addresses

| Bus                     | Boundary address Peripheral |                                |  |  |

|-------------------------|-----------------------------|--------------------------------|--|--|

|                         | 0xE010 0000 - 0xFFFF FFFF   | Reserved                       |  |  |

| Cortex <sup>®</sup> -M4 | 0xE000 0000 - 0xE00F FFFF   | Cortex-M4 internal peripherals |  |  |

|                         | 0x5004 0000 - 0xDFFF FFFF   | Reserved                       |  |  |

|                 |                    |                                                                               | £                          |      | Max <sup>(1)</sup>        |                           |                            |                            |      |

|-----------------|--------------------|-------------------------------------------------------------------------------|----------------------------|------|---------------------------|---------------------------|----------------------------|----------------------------|------|

| Symbol F        | Parameter          | Conditions                                                                    | f <sub>HCLK</sub><br>(MHz) | Тур  | T <sub>A</sub> =<br>25 °C | T <sub>A</sub> =<br>85 °C | T <sub>A</sub> =<br>105 °C | T <sub>A</sub> =<br>125 °C | Unit |

|                 |                    |                                                                               | 100                        | 20.4 | 21.8                      | 22.1                      | 22.8                       | 23.8                       |      |

|                 |                    | External clock, PLL                                                           | 84                         | 16.5 | 17.6                      | 17.8                      | 18.6                       | 19.6                       |      |

|                 |                    | ON <sup>(2)</sup> ,<br>all peripherals                                        | 64                         | 11.4 | 12.3                      | 12.5                      | 13.1                       | 14.1                       |      |

|                 | Supply current     | enabled <sup>(3)(4)</sup>                                                     | 50                         | 9.0  | 9.7                       | 10.0                      | 10.6                       | 11.6                       |      |

|                 |                    |                                                                               | 20                         | 4.6  | 5.0                       | 5.3                       | 6.0                        | 7.0                        |      |

|                 |                    | HSI, PLL OFF <sup>(2)</sup> , all peripherals enabled <sup>(3)</sup>          | 16                         | 2.9  | 3.2                       | 3.6                       | 4.3                        | 5.3                        |      |

|                 |                    |                                                                               | 1                          | 0.7  | 0.8                       | 1.3                       | 1.9                        | 2.9                        | mA   |

| I <sub>DD</sub> | in <b>Run mode</b> |                                                                               | 100                        | 11.2 | 12.2                      | 12.4                      | 13.2                       | 14.2                       | ШA   |

|                 |                    |                                                                               | 84                         | 9.1  | 9.9                       | 10.1                      | 10.9                       | 11.9                       |      |

|                 |                    | External clock, PLL ON <sup>(2)</sup> all peripherals disabled <sup>(3)</sup> | 64                         | 6.4  | 7.0                       | 7.3                       | 7.9                        | 8.9                        |      |

|                 |                    |                                                                               | 50                         | 5.1  | 5.6                       | 5.9                       | 6.6                        | 7.6                        |      |

|                 |                    |                                                                               | 20                         | 2.6  | 3.0                       | 3.3                       | 4.0                        | 5.0                        |      |

|                 |                    | HSI, PLL OFF <sup>(2)</sup> , all                                             | 16                         | 1.8  | 2.0                       | 2.4                       | 3.0                        | 4.0                        |      |

|                 |                    | peripherals disabled <sup>(3)</sup>                                           | 1                          | 0.6  | 0.7                       | 1.2                       | 1.9                        | 2.9                        |      |

## Table 22. Typical and maximum current consumption in run mode, code with data processing (ART accelerator enabled except prefetch) running from Flash memory- V<sub>DD</sub> = 1.7 V

1. Guaranteed by characterization results.

2. Refer to Table 41 and RM0383 for the possible PLL VCO setting

3. Add an additional power consumption of 1.6 mA per ADC for the analog part. In applications, this consumption occurs only while the ADC is ON (ADON bit is set in the ADC\_CR2 register).

4. When the ADC is ON (ADON bit set in the ADC\_CR2), add an additional power consumption of 1.6mA per ADC for the analog part.

| Symbol | Parameter                | Conditions <sup>(1)</sup>                                         | I/O toggling<br>frequency (f <sub>SW</sub> ) | Тур   | Unit |

|--------|--------------------------|-------------------------------------------------------------------|----------------------------------------------|-------|------|

|        |                          |                                                                   | 2 MHz                                        | 0.05  |      |

|        |                          |                                                                   | 8 MHz                                        | 0.15  |      |

|        |                          |                                                                   | 25 MHz                                       | 0.45  |      |

|        |                          | V <sub>DD</sub> = 3.3 V<br>C = C <sub>INT</sub>                   | 50 MHz                                       | 0.85  |      |

|        |                          | U = UINT                                                          | 60 MHz                                       | 1.00  |      |

|        |                          |                                                                   | 84 MHz                                       | 1.40  |      |

|        |                          |                                                                   | 90 MHz                                       | 1.67  |      |

|        |                          |                                                                   | 2 MHz                                        | 0.10  |      |

|        |                          |                                                                   | 8 MHz                                        | 0.35  |      |

|        |                          | $V_{DD} = 3.3 V$ $C_{EXT} = 0 pF$ $C = C_{INT} + C_{EXT} + C_{S}$ | 25 MHz                                       | 1.05  |      |

|        | I/O switching<br>current |                                                                   | 50 MHz                                       | 2.20  |      |

|        |                          |                                                                   | 60 MHz                                       | 2.40  |      |

|        |                          |                                                                   | 84 MHz                                       | 3.55  |      |

|        |                          |                                                                   | 90 MHz                                       | 4.23  |      |

| IDDIO  |                          | V <sub>DD</sub> = 3.3 V                                           | 2 MHz                                        | 0.20  |      |

| UDUO   |                          |                                                                   | 8 MHz                                        | 0.65  | mA   |

|        |                          |                                                                   | 25 MHz                                       | 1.85  |      |

|        |                          | C <sub>EXT</sub> =10 pF                                           | 50 MHz                                       | 2.45  |      |

|        |                          | $C = C_{INT} + C_{EXT} + C_S$                                     | 60 MHz                                       | 4.70  |      |

|        |                          |                                                                   | 84 MHz                                       | 8.80  |      |

|        |                          |                                                                   | 90 MHz                                       | 10.47 |      |

|        |                          |                                                                   | 2 MHz                                        | 0.25  |      |

|        |                          | V <sub>DD</sub> = 3.3 V                                           | 8 MHz                                        | 1.00  |      |

|        |                          | C <sub>EXT</sub> = 22 pF                                          | 25 MHz                                       | 3.45  |      |

|        |                          | $C = C_{INT} + C_{EXT} + C_{S}$                                   | 50 MHz                                       | 7.15  |      |

|        |                          |                                                                   | 60 MHz                                       | 11.55 |      |

|        |                          |                                                                   | 2 MHz                                        | 0.32  |      |

|        |                          | $V_{DD} = 3.3 V$                                                  | 8 MHz                                        | 1.27  |      |

|        |                          | $C_{EXT} = 33 \text{ pF}$<br>$C = C_{INT} + C_{EXT} + C_S$        | 25 MHz                                       | 3.88  |      |

|        |                          |                                                                   | 50 MHz                                       | 12.34 |      |

| Table 32. Switching output I/O | current consumption |

|--------------------------------|---------------------|

|--------------------------------|---------------------|

1. CS is the PCB board capacitance including the pad pin. CS = 7 pF (estimated value).

57

#### **On-chip peripheral current consumption**

The MCU is placed under the following conditions:

- At startup, all I/O pins are in analog input configuration.

- All peripherals are disabled unless otherwise mentioned.

- The ART accelerator is ON.

- Voltage Scale 2 mode selected, internal digital voltage V12 = 1.26 V.

- HCLK is the system clock at 84 MHz. f<sub>PCLK1</sub> = f<sub>HCLK</sub>/2, and f<sub>PCLK2</sub> = f<sub>HCLK</sub>.

The given value is calculated by measuring the difference of current consumption

- with all peripherals clocked off

- with only one peripheral clocked on

- Ambient operating temperature is 25 °C and V<sub>DD</sub>=3.3 V.

| Peripheral              |                     | I <sub>DD</sub> (Тур) | Unit   |

|-------------------------|---------------------|-----------------------|--------|

|                         | GPIOA               | 1.55                  |        |

| -                       | GPIOB               | 1.55                  |        |

| -                       | GPIOC               | 1.55                  |        |

| -                       | GPIOD               | 1.55                  |        |

|                         | GPIOE               | 1.55                  |        |

|                         | GPIOH               | 1.55                  |        |

|                         | CRC                 | 0.36                  |        |

| AHB1<br>(up to 100 MHz) | DMA1 <sup>(1)</sup> | 14.96                 | µA/MHz |

|                         | DMA1 <sup>(2)</sup> | 1.54N+2.66            |        |

|                         | DMA2 <sup>(1)</sup> | 14.96                 |        |

|                         | DMA2 <sup>(2)</sup> | 1.54N+2.66            |        |

|                         | TIM2                | 11.19                 |        |

|                         | TIM3                | 8.57                  |        |

| -                       | TIM4                | 8.33                  |        |

| -                       | TIM5                | 11.19                 |        |

| -                       | PWR                 | 0.71                  |        |

| APB1                    | USART2              | 3.33                  |        |

| (up to 50 MHz)          | I2C1/2/3            | 3.10                  | µA/MHz |

|                         | SPI2 <sup>(3)</sup> | 2.62                  |        |

|                         | SPI3 <sup>(3)</sup> | 2.86                  |        |

|                         | I2S2                | 1.90                  |        |

|                         | I2S3                | 1.67                  |        |

|                         | WWDG                | 0.71                  |        |

#### Table 33. Peripheral current consumption

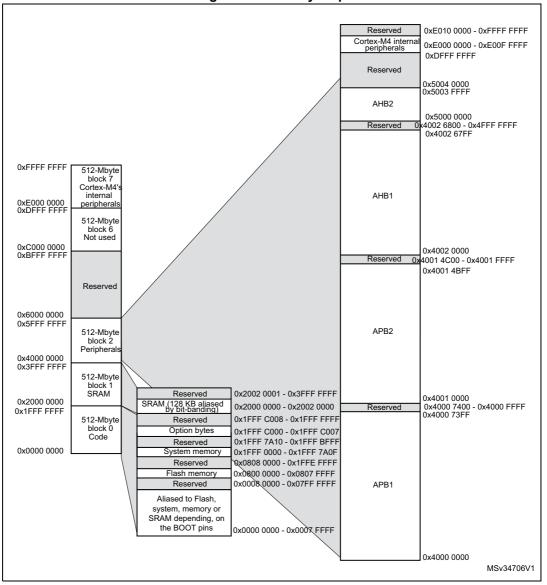

Figure 26. ACC<sub>HSI</sub> versus temperature

1. Guaranteed by characterization results.

#### Low-speed internal (LSI) RC oscillator

| Table 40. LSI oscillator characteristic | cs <sup>(1)</sup> |

|-----------------------------------------|-------------------|

|-----------------------------------------|-------------------|

| Symbol                              | Parameter                        | Min | Тур | Мах | Unit |

|-------------------------------------|----------------------------------|-----|-----|-----|------|

| f <sub>LSI</sub> <sup>(2)</sup>     | Frequency                        | 17  | 32  | 47  | kHz  |

| t <sub>su(LSI)</sub> <sup>(3)</sup> | LSI oscillator startup time      | -   | 15  | 40  | μs   |

| I <sub>DD(LSI)</sub> <sup>(3)</sup> | LSI oscillator power consumption | -   | 0.4 | 0.6 | μA   |

1.  $V_{DD}$  = 3 V, T<sub>A</sub> = -40 to 125 °C unless otherwise specified.

2. Guaranteed by characterization results.

3. Guaranteed by design.

#### 6.3.11 PLL spread spectrum clock generation (SSCG) characteristics

The spread spectrum clock generation (SSCG) feature allows to reduce electromagnetic interferences (see *Table 49: EMI characteristics for LQFP100*). It is available only on the main PLL.

| Symbol            | Parameter                              |      | Тур | Max <sup>(1)</sup> | Unit |

|-------------------|----------------------------------------|------|-----|--------------------|------|

| f <sub>Mod</sub>  | Modulation frequency                   | -    | -   | 10                 | kHz  |

| md                | Peak modulation depth                  | 0.25 | -   | 2                  | %    |

| MODEPER * INCSTEP | (Modulation period) * (Increment Step) | -    | -   | 2 <sup>15</sup> -1 | -    |

| Table 43 | SSCG | parameter | constraints |

|----------|------|-----------|-------------|

|          | 0000 | parameter | constraints |

1. Guaranteed by design.

#### Equation 1

The frequency modulation period (MODEPER) is given by the equation below:

$MODEPER = round[f_{PLL IN} / (4 \times f_{Mod})]$

$f_{\text{PLL}\ \text{IN}}$  and  $f_{\text{Mod}}$  must be expressed in Hz.

As an example:

If  $f_{PLL_IN} = 1$  MHz, and  $f_{MOD} = 1$  kHz, the modulation depth (MODEPER) is given by equation 1:

MODEPER = round  $[10^{6}/(4 \times 10^{3})] = 250$

#### **Equation 2**

Equation 2 allows to calculate the increment step (INCSTEP):

INCSTEP = round[

$$((2^{15} - 1) \times md \times PLLN)/(100 \times 5 \times MODEPER)$$

]

$f_{\text{VCO OUT}}$  must be expressed in MHz.

With a modulation depth (md) =  $\pm 2$  % (4 % peak to peak), and PLLN = 240 (in MHz):

INCSTEP = round[ $((2^{15}-1) \times 2 \times 240)/(100 \times 5 \times 250)$ ] = 126md(quantitazed)%

An amplitude quantization error may be generated because the linear modulation profile is obtained by taking the quantized values (rounded to the nearest integer) of MODPER and INCSTEP. As a result, the achieved modulation depth is quantized. The percentage quantized modulation depth is given by the following formula:

$$md_{quantized}$$

% = (MODEPER×INCSTEP×100×5)/ ((2<sup>15</sup>-1)×PLLN)

As a result:

$$md_{quantized}\% = (250 \times 126 \times 100 \times 5)/ ((2^{15} - 1) \times 240) = 2.002\%$$

(peak)

DocID026289 Rev 6

| Symbol            | Parameter                                                                                                                         | Conditions                                                                                                                                                | Level/<br>Class |

|-------------------|-----------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------|

| V <sub>FESD</sub> | Voltage limits to be applied on any I/O pin to induce a functional disturbance                                                    | $V_{DD}$ = 3.3 V, LQFP100, WLCSP49,<br>T <sub>A</sub> = +25 °C, f <sub>HCLK</sub> = 100 MHz,<br>conforms to IEC 61000-4-2                                 | 2B              |

| V <sub>EFTB</sub> | Fast transient voltage burst limits to be applied through 100 pF on $V_{DD}$ and $V_{SS}$ pins to induce a functional disturbance | $V_{DD} = 3.3 \text{ V}, \text{LQFP100}, \text{WLCSP49}, T_A = +25 ^{\circ}\text{C}, f_{\text{HCLK}} = 100 \text{ MHz}, \text{conforms to IEC 61000-4-4}$ | 4A              |

Table 48. EMS characteristics for LQFP100 package

When the application is exposed to a noisy environment, it is recommended to avoid pin exposition to disturbances. The pins showing a middle range robustness are: PA0, PA1, PA2, on LQFP100 packages and PDR\_ON on WLCSP49.

As a consequence, it is recommended to add a serial resistor (1 k $\Omega$  maximum) located as close as possible to the MCU to the pins exposed to noise (connected to tracks longer than 50 mm on PCB).

#### Designing hardened software to avoid noise problems

EMC characterization and optimization are performed at component level with a typical application environment and simplified MCU software. It should be noted that good EMC performance is highly dependent on the user application and the software in particular.

Therefore it is recommended that the user applies EMC software optimization and prequalification tests in relation with the EMC level requested for his application.

#### Software recommendations

The software flowchart must include the management of runaway conditions such as:

- Corrupted program counter

- Unexpected reset

- Critical Data corruption (control registers...)

#### Prequalification trials

Most of the common failures (unexpected reset and program counter corruption) can be reproduced by manually forcing a low state on the NRST pin or the Oscillator pins for 1 second.

To complete these trials, ESD stress can be applied directly on the device, over the range of specification values. When unexpected behavior is detected, the software can be hardened to prevent unrecoverable errors occurring (see application note AN1015).

| Symbol               | Parameter                | Conditions                                                         | Min | Тур | Мах  | Unit |  |

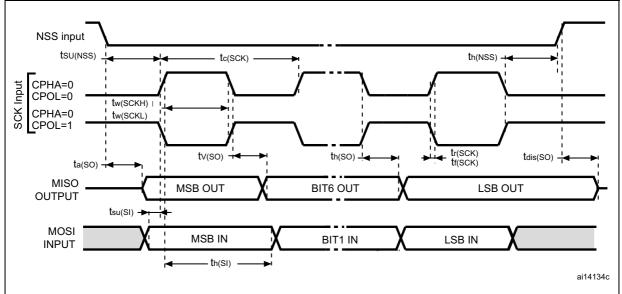

|----------------------|--------------------------|--------------------------------------------------------------------|-----|-----|------|------|--|

| t <sub>a(SO</sub> )  | Data output access time  | Slave mode                                                         | 7   | -   | 21   | ns   |  |

| t <sub>dis(SO)</sub> | Data output disable time | Slave mode                                                         | 5   | -   | 12   | ns   |  |

|                      |                          | Slave mode (after enable edge),<br>2.7 V < $V_{DD}$ < 3.6 V        | -   | 11  | 13   | ns   |  |

| t <sub>v(SO)</sub>   | Data output valid time   | Slave mode (after enable edge),<br>1.7 V < $V_{DD}$ < 3.6 V        | -   | 11  | 18.5 | ns   |  |

| t <sub>h(SO)</sub>   | Data output hold time    | Slave mode (after enable edge),<br>1.7 V < V <sub>DD</sub> < 3.6 V | 8   | -   | -    | ns   |  |

| t <sub>v(MO)</sub>   | Data output valid time   | Master mode (after enable edge)                                    | -   | 4   | 6    | ns   |  |

| t <sub>h(MO)</sub>   | Data output hold time    | Master mode (after enable edge)                                    | 0   | -   | -    | ns   |  |

| Table 60. SPI | dynamic | characteristics <sup>(1)</sup> | (continued) |

|---------------|---------|--------------------------------|-------------|

|---------------|---------|--------------------------------|-------------|

1. Guaranteed by characterization results.

2. Maximum frequency in Slave transmitter mode is determined by the sum of  $t_{v(SO)}$  and  $t_{su(MI)}$  which has to fit into SCK low or high phase preceding the SCK sampling edge. This value can be achieved when the SPI communicates with a master having  $t_{su(MI)} = 0$  while Duty(SCK) = 50%

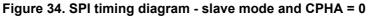

Figure 37. I<sup>2</sup>S slave timing diagram (Philips protocol)<sup>(1)</sup>

1. LSB transmit/receive of the previously transmitted byte. No LSB transmit/receive is sent before the first byte.

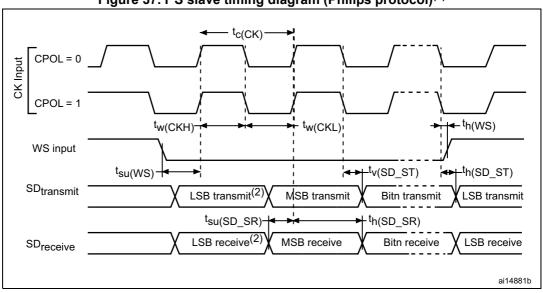

#### Figure 38. I<sup>2</sup>S master timing diagram (Philips protocol)<sup>(1)</sup>

1. LSB transmit/receive of the previously transmitted byte. No LSB transmit/receive is sent before the first byte.

| package mechanical data |       |             |       |                       |        |        |

|-------------------------|-------|-------------|-------|-----------------------|--------|--------|

| Symbol                  |       | millimeters |       | inches <sup>(1)</sup> |        |        |

| Symbol                  | Min   | Тур         | Max   | Min                   | Тур    | Max    |

| А                       | 0.525 | 0.555       | 0.585 | 0.0207                | 0.0219 | 0.0230 |

| A1                      | -     | 0.175       | -     | -                     | 0.0069 | -      |

| A2                      | -     | 0.380       | -     | -                     | 0.0150 | -      |

| A3 <sup>(2)</sup>       | -     | 0.025       | -     | -                     | 0.0010 | -      |

| b <sup>(3)</sup>        | 0.220 | 0.250       | 0.280 | 0.0087                | 0.0098 | 0.0110 |

| D                       | 2.964 | 2.999       | 3.034 | 0.1167                | 0.1181 | 0.1194 |

| E                       | 3.150 | 3.185       | 3.220 | 0.1240                | 0.1254 | 0.1268 |

| е                       | -     | 0.400       | -     | -                     | 0.0157 | -      |

| e1                      | -     | 2.400       | -     | -                     | 0.0945 | -      |

| e2                      | -     | 2.400       | -     | -                     | 0.0945 | -      |

| F                       | -     | 0.2995      | -     | -                     | 0.0118 | -      |

| G                       | -     | 0.3925      | -     | -                     | 0.0155 | -      |

| aaa                     | -     | 0.100       | -     | -                     | 0.0039 | -      |

| bbb                     | -     | 0.100       | -     | -                     | 0.0039 | -      |

| ccc                     | -     | 0.100       | -     | -                     | 0.0039 | -      |

| ddd                     | -     | 0.050       | -     | -                     | 0.0020 | -      |

| eee                     | -     | 0.050       | -     | -                     | 0.0020 | -      |

## Table 79. WLCSP49 - 49-ball, 2.999 x 3.185 mm, 0.4 mm pitch wafer level chip scalepackage mechanical data

1. Values in inches are converted from mm and rounded to 4 decimal digits.

2. Back side coating

3. Dimension is measured at the maximum bump diameter parallel to primary datum Z.

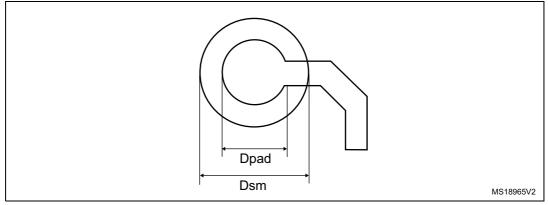

## Figure 47. WLCSP49 - 49-ball, 2.999 x 3.185 mm, 0.4 mm pitch wafer level chip scale recommended footprint

## 7.3 LQFP64 package information

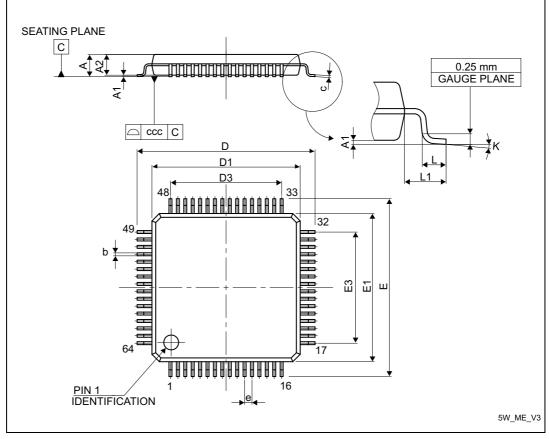

Figure 52. LQFP64 - 64-pin, 10 x 10 mm, 64-pin low-profile quad flat package outline

1. Drawing is not to scale.

## Appendix B Application block diagrams

### B.1 USB OTG Full Speed (FS) interface solutions

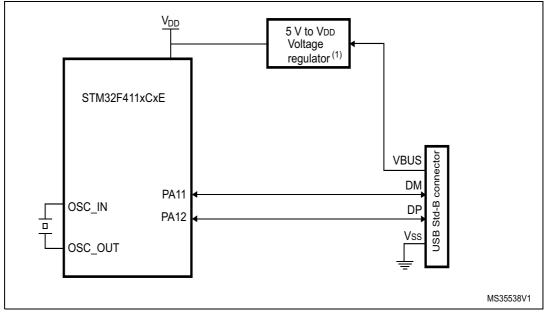

Figure 61. USB controller configured as peripheral-only and used in Full-Speed mode

1. The external voltage regulator is only needed when building a  $\mathrm{V}_{\mathrm{BUS}}$  powered device.

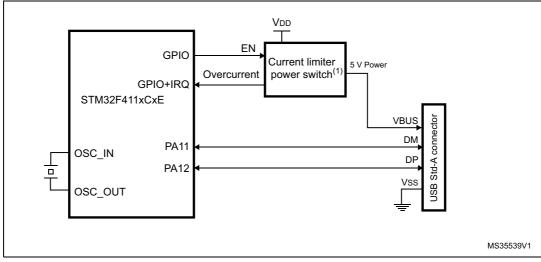

#### Figure 62. USB controller configured as host-only and used in Full-Speed mode

1. The current limiter is required only if the application has to support a  $V_{BUS}$  powered device. A basic power switch can be used if 5V are available on the application board.

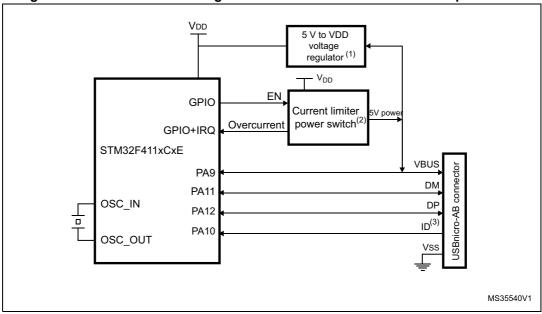

Figure 63. USB controller configured in dual mode and used in Full-Speed mode

- 1. The external voltage regulator is only needed when building a  $\mathrm{V}_{\mathrm{BUS}}$  powered device.

- The current limiter is required only if the application has to support a V<sub>BUS</sub> powered device. A basic power switch can be used if 5 V are available on the application board.

- 3. The ID pin is required in dual role only.

## **Revision history**

| Date          | Date Revision Changes |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |  |  |  |

|---------------|-----------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|

| 19-Jun-2014   | 1                     | Initial release.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |  |  |  |

| 10-Sep-2014 2 |                       | Introduced the BAM feature in <i>Features</i> , <i>Section 2: Description.</i> , and <i>Section 3.3: Batch Acquisition mode (BAM)</i> .<br>Updated Section 3.5: Embedded Flash memory, Section 3.14: Power supply schemes and Section 3.18: Low-power modes, Section 3.20.2: General-purpose timers (TIMx) and Section 3.30: Temperature sensor.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |  |  |  |

|               | 2                     | <ul> <li>Modified Table 8: STM32F411xC/xE pin definitions, Table 9: Alternate function mapping and APB2 in Table 10: STM32F411xC/xE register boundary addresses.</li> <li>Modified Table 34: Low-power mode wakeup timings(1), Table 20: Typical and maximum current consumption, code with data processing (ART accelerator disabled) running from SRAM - VDD = 1.7 V, Table 21: Typical and maximum current consumption, code with data processing (ART accelerator disabled) running from SRAM - VDD = 1.7 V, Table 21: Typical and maximum current consumption, code with data processing (ART accelerator disabled) running from SRAM - VDD = 3.6 V, Table 25: Typical and maximum current consumption in run mode, code with data processing (ART accelerator enabled with prefetch) running from Flash memory - VDD = 3.6 V, Table 26: Typical and maximum current consumption in Sleep mode - VDD = 3.6 V and Table 58: I2C characteristics and Figure 33: I2C bus AC waveforms and measurement circuit.</li> <li>Added Figure 21: Low-power mode wakeup, Section Appendix A: Recommendations when using the internal reset OFF and Section Appendix B: Application block diagrams.</li> </ul>                                                                                                                                                                                                                                                                                                                       |  |  |  |

| 27-Nov-2014   | 3                     | Changed datasheet status to Production Data.<br>Updated <i>Table 31: Typical and maximum current consumptions in VBAT mode.</i><br><i>Section : On-chip peripheral current consumption:</i> changed HCLK frequency and<br>updated DMA1 and DMA2 current consumption in <i>Table 33: Peripheral current</i><br><i>consumption.</i><br>Updated <i>Table 55: I/O AC characteristics.</i><br>Updated THD in <i>Table 69: ADC dynamic accuracy at fADC = 18 MHz - limited test</i><br><i>conditions</i> and <i>Table 70: ADC dynamic accuracy at fADC = 36 MHz - limited test</i><br><i>conditions.</i><br>Updated <i>Table 55: I/O AC characteristics.</i><br>Updated <i>Table 55: I/O AC characteristics.</i><br>Updated <i>Table 55: I/O AC characteristics.</i><br>Updated <i>Figure 46: WLCSP49 - 49-ball, 2.999 x 3.185 mm, 0.4 mm pitch wafer level</i><br><i>chip scale package outline</i> and <i>Figure 48: WLCSP49 marking (package top view).</i><br>Added <i>Figure 47: WLCSP49 - 49-ball, 2.999 x 3.185 mm, 0.4 mm pitch wafer level</i><br><i>chip scale recommended footprint</i> and <i>Table 80: WLCSP49 recommended PCB design</i><br><i>rules (0.4 mm pitch).</i><br>Updated <i>Figure 51: UFQFPN48 marking example (package top view), Figure 54:</i><br><i>LQFP64 marking example (package top view), Figure 57: LQPF100 marking example</i><br>( <i>package top view),</i> and <i>Figure 58: UFBGA100 - 100-ball, 7 x 7 mm, 0.50 mm pitch,</i><br><i>ultra fine pitch ball grid array package outline.</i> |  |  |  |

| 04-Feb-2015   | 4                     | Added VPP alternate function for BOOT0 in <i>Table 8: STM32F411xC/xE pin definitions</i> .<br>Added TC inputs in <i>Table 11: Voltage characteristics</i> , <i>Table 12: Current characteristics</i> ,<br><i>Table 14: General operating conditions</i> , <i>Table 53: I/O static characteristics</i> and<br><i>Figure 30: FT/TC I/O input characteristics</i> .<br>Updated V <sub>ESD(CDM)</sub> in <i>Table 50: ESD absolute maximum ratings</i> .<br>A3 minimum and maximum values removed in <i>Table 83: UFBGA100 - 100-ball</i> , 7 x 7<br><i>mm</i> , 0.50 mm pitch, ultra fine pitch ball grid array package mechanical data.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |  |  |  |

| Table 88. | Document | revision | history |

|-----------|----------|----------|---------|

|-----------|----------|----------|---------|