### Microchip Technology - PIC16F1503-E/MG Datasheet

Welcome to E-XFL.COM

### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

### Details

| Details                    |                                                                           |

|----------------------------|---------------------------------------------------------------------------|

| Product Status             | Active                                                                    |

| Core Processor             | PIC                                                                       |

| Core Size                  | 8-Bit                                                                     |

| Speed                      | 20MHz                                                                     |

| Connectivity               | I <sup>2</sup> C, SPI                                                     |

| Peripherals                | Brown-out Detect/Reset, POR, PWM, WDT                                     |

| Number of I/O              | 11                                                                        |

| Program Memory Size        | 3.5KB (2K x 14)                                                           |

| Program Memory Type        | FLASH                                                                     |

| EEPROM Size                | -                                                                         |

| RAM Size                   | 128 x 8                                                                   |

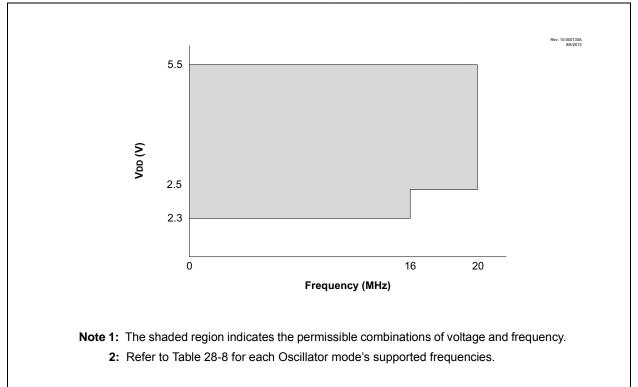

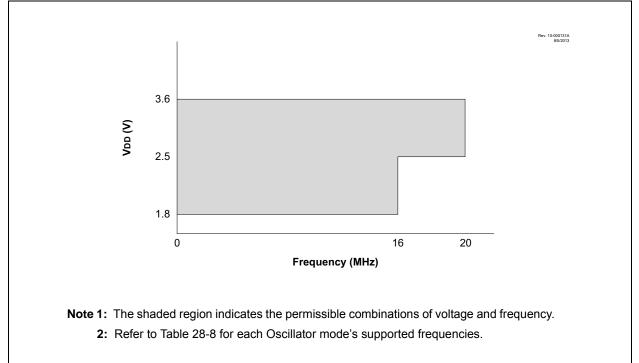

| Voltage - Supply (Vcc/Vdd) | 2.3V ~ 5.5V                                                               |

| Data Converters            | A/D 8x10b                                                                 |

| Oscillator Type            | Internal                                                                  |

| Operating Temperature      | -40°C ~ 125°C (TA)                                                        |

| Mounting Type              | Surface Mount                                                             |

| Package / Case             | 16-VFQFN Exposed Pad                                                      |

| Supplier Device Package    | 16-QFN (3x3)                                                              |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic16f1503-e-mg |

|                            |                                                                           |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

### **Peripheral Features (Continued):**

- Two Configurable Logic Cell (CLC) modules:

- 16 selectable input source signals

- Four inputs per module

- Software control of combinational/sequential logic/state/clock functions

PIC12(L)F1501/PIC16(L)F150X FAMILY TYPES

- AND/OR/XOR/D Flop/D Latch/SR/JK

- Inputs from external and internal sources

- Output available to pins and peripherals

- Operation while in Sleep

- Numerically Controlled Oscillator (NCO):

- 20-bit accumulator

- 16-bit increment

- True linear frequency control

- High-speed clock input

- Selectable Output modes

- Fixed Duty Cycle (FDC) mode

- Pulse Frequency (PF) mode

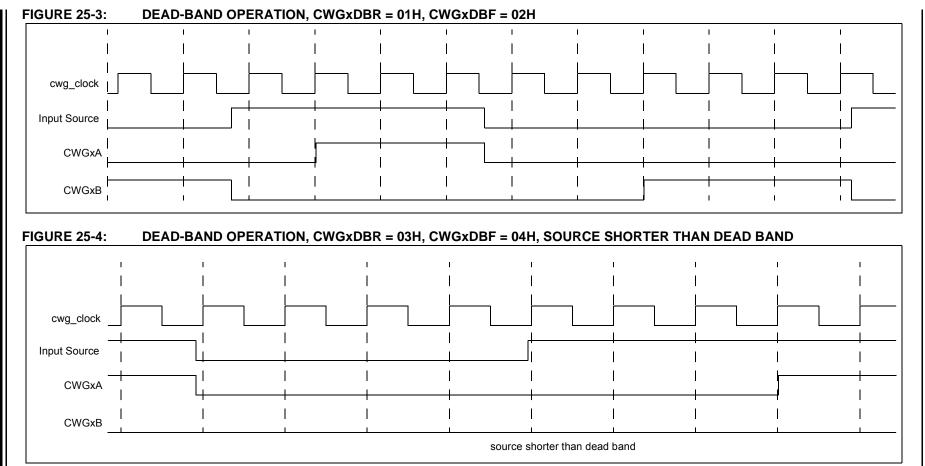

- Complementary Waveform Generator (CWG):

- Eight selectable signal sources

- Selectable falling and rising edge dead-band control

- Polarity control

- Four auto-shutdown sources

- Multiple input sources: PWM, CLC, NCO

| Device        | Data Sheet Index | Program Memory<br>Flash (words) | Data SRAM<br>(bytes) | I/O's <sup>(2)</sup> | 10-bit ADC (ch) | Comparators | DAC | Timers<br>(8/16-bit) | MWd | EUSART | MSSP (I <sup>2</sup> C/SPI) | CWG | CLC | NCO | Debug <sup>(1)</sup> | XLP |

|---------------|------------------|---------------------------------|----------------------|----------------------|-----------------|-------------|-----|----------------------|-----|--------|-----------------------------|-----|-----|-----|----------------------|-----|

| PIC12(L)F1501 | (1)              | 1024                            | 64                   | 6                    | 4               | 1           | 1   | 2/1                  | 4   | —      | -                           | 1   | 2   | 1   | Н                    |     |

| PIC16(L)F1503 | (2)              | 2048                            | 128                  | 12                   | 8               | 2           | 1   | 2/1                  | 4   | _      | 1                           | 1   | 2   | 1   | Н                    | _   |

| PIC16(L)F1507 | (3)              | 2048                            | 128                  | 18                   | 12              |             |     | 2/1                  | 4   | _      |                             | 1   | 2   | 1   | Н                    | _   |

| PIC16(L)F1508 | (4)              | 4096                            | 256                  | 18                   | 12              | 2           | 1   | 2/1                  | 4   | 1      | 1                           | 1   | 4   | 1   | I/H                  | Y   |

| PIC16(L)F1509 | (4)              | 8192                            | 512                  | 18                   | 12              | 2           | 1   | 2/1                  | 4   | 1      | 1                           | 1   | 4   | 1   | I/H                  | Υ   |

Note 1: Debugging Methods: (I) - Integrated on Chip; (H) - using Debug Header; (E) - using Emulation Header.

2: One pin is input-only.

Data Sheet Index: (Unshaded devices are described in this document.)

1: DS40001615 PIC12(L)F1501 Data Sheet, 8-Pin Flash, 8-bit Microcontrollers.

- 2: DS40001607 PIC16(L)F1503 Data Sheet, 14-Pin Flash, 8-bit Microcontrollers.

- 3: DS40001586 PIC16(L)F1507 Data Sheet, 20-Pin Flash, 8-bit Microcontrollers.

- 4: DS40001609 PIC16(L)F1508/9 Data Sheet, 20-Pin Flash, 8-bit Microcontrollers.

**Note:** For other small form-factor package availability and marking information, please visit http://www.microchip.com/packaging or contact your local sales office.

### 6.4 Low-Power Brown-Out Reset (LPBOR)

The Low-Power Brown-out Reset (LPBOR) operates like the BOR to detect low voltage conditions on the VDD pin. When too low of a voltage is detected, the device is held in Reset. When this occurs, a register bit (BOR) is changed to indicate that a BOR Reset has occurred. The BOR bit in PCON is used for both BOR and the LPBOR. Refer to Register 6-2.

The LPBOR voltage threshold (Lapboard) has a wider tolerance than the BOR (Vpor), but requires much less current (LPBOR current) to operate. The LPBOR is intended for use when the BOR is configured as disabled (BOREN = 00) or disabled in Sleep mode (BOREN = 10).

Refer to Figure 6-1 to see how the LPBOR interacts with other modules.

### 6.4.1 ENABLING LPBOR

The LPBOR is controlled by the  $\overline{\text{LPBOR}}$  bit of Configuration Words. When the device is erased, the LPBOR module defaults to disabled.

### 6.5 MCLR

The  $\overline{\text{MCLR}}$  is an optional external input that can reset the device. The  $\overline{\text{MCLR}}$  function is controlled by the MCLRE bit of Configuration Words and the LVP bit of Configuration Words (Table 6-2).

### TABLE 6-2: MCLR CONFIGURATION

| MCLRE | LVP | MCLR     |

|-------|-----|----------|

| 0     | 0   | Disabled |

| 1     | 0   | Enabled  |

| x     | 1   | Enabled  |

### 6.5.1 MCLR ENABLED

When  $\overline{\text{MCLR}}$  is enabled and the pin is held low, the device is held in Reset. The  $\overline{\text{MCLR}}$  pin is connected to VDD through an internal weak pull-up.

The device has a noise filter in the  $\overline{\text{MCLR}}$  Reset path. The filter will detect and ignore small pulses.

### **Note:** A Reset does not drive the MCLR pin low.

### 6.5.2 MCLR DISABLED

When MCLR is disabled, the pin functions as a general purpose input and the internal weak pull-up is under software control. See **Section 11.3 "PORTA Registers"** for more information.

### 6.6 Watchdog Timer (WDT) Reset

The Watchdog Timer generates a Reset if the firmware does not issue a CLRWDT instruction within the time-out period. The TO and PD bits in the STATUS register are changed to indicate the WDT Reset. See **Section 9.0 "Watchdog Timer (WDT)**" for more information.

### 6.7 RESET Instruction

A RESET instruction will cause a device Reset. The  $\overline{RI}$  bit in the PCON register will be set to '0'. See Table 6-4 for default conditions after a RESET instruction has occurred.

### 6.8 Stack Overflow/Underflow Reset

The device can reset when the Stack Overflows or Underflows. The STKOVF or STKUNF bits of the PCON register indicate the Reset condition. These Resets are enabled by setting the STVREN bit in Configuration Words. See **Section 3.5.2 "Overflow/Underflow Reset"** for more information.

### 6.9 Programming Mode Exit

Upon exit of Programming mode, the device will behave as if a POR had just occurred.

### 6.10 Power-Up Timer

The Power-up Timer optionally delays device execution after a BOR or POR event. This timer is typically used to allow VDD to stabilize before allowing the device to start running.

The Power-up Timer is controlled by the  $\overline{\text{PWRTE}}$  bit of Configuration Words.

### 6.11 Start-up Sequence

Upon the release of a POR or BOR, the following must occur before the device will begin executing:

- 1. Power-up Timer runs to completion (if enabled).

- 2. MCLR must be released (if enabled).

The total time-out will vary based on oscillator configuration and Power-up Timer configuration. See **Section 5.0 "Oscillator Module"** for more information.

The Power-up Timer runs independently of MCLR Reset. If MCLR is kept low long enough, the Power-up Timer will expire. Upon bringing MCLR high, the device will begin execution after 10 FOSS cycles (see Figure 6-3). This is useful for testing purposes or to synchronize more than one device operating in parallel.

| U-0                                                                                   | ) U-0                                           | U-0               | U-0            | U-0            | U-0              | R/W-0/0          | R/W-0/0      |

|---------------------------------------------------------------------------------------|-------------------------------------------------|-------------------|----------------|----------------|------------------|------------------|--------------|

| _                                                                                     | —                                               | —                 | _              | _              | —                | CLC2IF           | CLC1IF       |

| bit 7                                                                                 |                                                 |                   |                |                |                  |                  | bit 0        |

|                                                                                       |                                                 |                   |                |                |                  |                  |              |

| Legend:                                                                               |                                                 |                   |                |                |                  |                  |              |

| R = Rea                                                                               | dable bit                                       | W = Writable      | bit            | U = Unimpler   | mented bit, read | as '0'           |              |

| u = Bit is                                                                            | unchanged                                       | x = Bit is unkr   | nown           | -n/n = Value a | at POR and BOI   | R/Value at all c | other Resets |

| '1' = Bit i                                                                           | s set                                           | '0' = Bit is cle  | ared           |                |                  |                  |              |

|                                                                                       |                                                 |                   |                |                |                  |                  |              |

| bit 7-2                                                                               | Unimpleme                                       | ented: Read as '  | 0'             |                |                  |                  |              |

| bit 1                                                                                 | CLC2IF: Co                                      | onfigurable Logic | Block 2 Interr | upt Flag bit   |                  |                  |              |

|                                                                                       |                                                 | ot is pending     |                |                |                  |                  |              |

|                                                                                       | •                                               | ot is not pending |                |                |                  |                  |              |

| bit 0                                                                                 |                                                 | onfigurable Logic | Block 1 Interr | upt Flag bit   |                  |                  |              |

|                                                                                       | 1 = Interrupt is pending                        |                   |                |                |                  |                  |              |

|                                                                                       | 0 = Interrup                                    | ot is not pending |                |                |                  |                  |              |

|                                                                                       |                                                 |                   |                |                |                  |                  |              |

| Note: Interrupt flag bits are set when an interrupt                                   |                                                 |                   |                |                |                  |                  |              |

| condition occurs, regardless of the state of                                          |                                                 |                   |                |                |                  |                  |              |

| its corresponding enable bit or the Global<br>Enable bit, GIE of the INTCON register. |                                                 |                   |                |                |                  |                  |              |

| 1                                                                                     | User software                                   |                   | -              |                |                  |                  |              |

|                                                                                       | appropriate interrupt flag bits are clear prior |                   |                |                |                  |                  |              |

### REGISTER 7-7: PIR3: PERIPHERAL INTERRUPT REQUEST REGISTER 3

appropriate interrupt flag bits are clear prior to enabling an interrupt.

### 9.1 Independent Clock Source

The WDT derives its time base from the 31 kHz LFINTOSC internal oscillator. Time intervals in this chapter are based on a nominal interval of 1 ms. See **Section 28.0 "Electrical Specifications"** for the LFINTOSC tolerances.

### 9.2 WDT Operating Modes

The Watchdog Timer module has four operating modes controlled by the WDTE<1:0> bits in Configuration Words. See Table 9-1.

### 9.2.1 WDT IS ALWAYS ON

When the WDTE bits of Configuration Words are set to '11', the WDT is always on.

WDT protection is active during Sleep.

### 9.2.2 WDT IS OFF IN SLEEP

When the WDTE bits of Configuration Words are set to '10', the WDT is on, except in Sleep.

WDT protection is not active during Sleep.

### 9.2.3 WDT CONTROLLED BY SOFTWARE

When the WDTE bits of Configuration Words are set to '01', the WDT is controlled by the SWDTEN bit of the WDTCON register.

WDT protection is unchanged by Sleep. See Table 9-1 for more details.

| TABLE 9-1: | WDT OPERATING MODES |

|------------|---------------------|

|------------|---------------------|

| WDTE<1:0> | SWDTEN | Device<br>Mode | WDT<br>Mode |

|-----------|--------|----------------|-------------|

| 11        | Х      | Х              | Active      |

| 10        |        | Awake          | Active      |

| 10        | Х      | Sleep          | Disabled    |

| 0.1       | 1      | х              | Active      |

| 01        | 0      | х              | Disabled    |

| 00        | Х      | х              | Disabled    |

### TABLE 9-2: WDT CLEARING CONDITIONS

# ConditionsWDTWDTE<1:0> = 00WDTE<1:0> = 01 and SWDTEN = 0WDTE<1:0> = 10 and enter SleepClearedCLRWDT CommandClearedOscillator Fail DetectedExit Sleep + System Clock = INTOSC, EXTCLKChange INTOSC divider (IRCF bits)Unaffected

### 9.3 Time-Out Period

The WDTPS bits of the WDTCON register set the time-out period from 1 ms to 256 seconds (nominal). After a Reset, the default time-out period is two seconds.

### 9.4 Clearing the WDT

The WDT is cleared when any of the following conditions occur:

- Any Reset

- CLRWDT instruction is executed

- · Device enters Sleep

- Device wakes up from Sleep

- Oscillator fail

- · WDT is disabled

See Table 9-2 for more information.

### 9.5 Operation During Sleep

When the device enters Sleep, the WDT is cleared. If the WDT is enabled during Sleep, the WDT resumes counting. When the device exits Sleep, the WDT is cleared again.

When a WDT time-out occurs while the device is in Sleep, no Reset is generated. Instead, the device wakes up and resumes operation. The TO and PD bits in the STATUS register are changed to indicate the event. The RWDT bit in the PCON register can also be used. See Section 3.0 "Memory Organization" for more information.

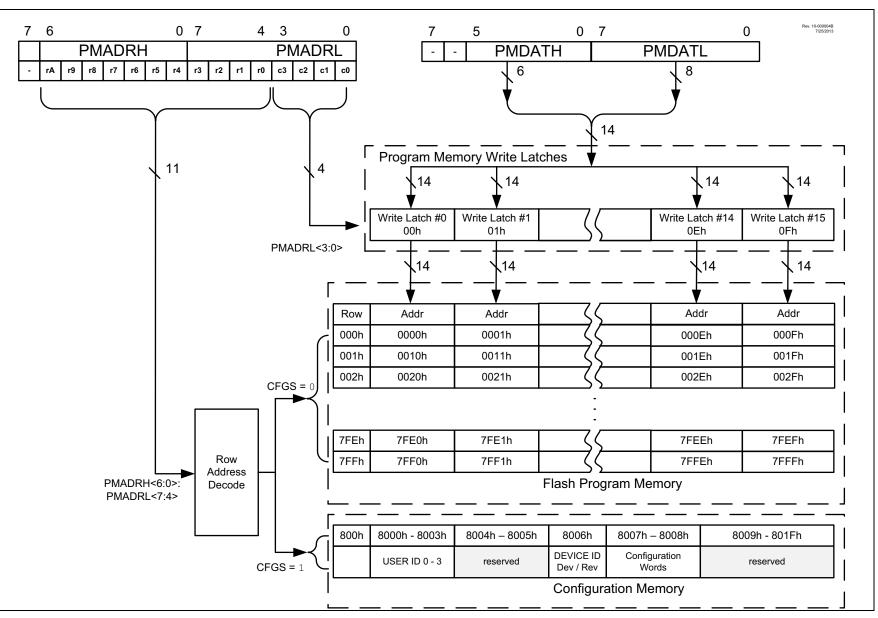

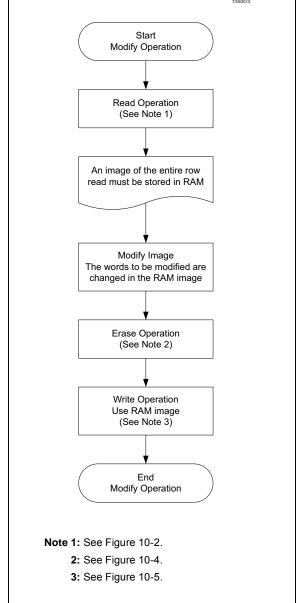

### 10.3 Modifying Flash Program Memory

When modifying existing data in a program memory row, and data within that row must be preserved, it must first be read and saved in a RAM image. Program memory is modified using the following steps:

- 1. Load the starting address of the row to be modified.

- 2. Read the existing data from the row into a RAM image.

- 3. Modify the RAM image to contain the new data to be written into program memory.

- 4. Load the starting address of the row to be rewritten.

- 5. Erase the program memory row.

- 6. Load the write latches with data from the RAM image.

- 7. Initiate a programming operation.

# FIGURE 10-7: FLASH PROGRAM MEMORY MODIFY FLOWCHART

| U-1              | R/W-0/0            | R/W-0/0                                     | R/W/HC-0/0            | R/W/HC-x/q <sup>(2)</sup>             | R/W-0/0           | R/S/HC-0/0           | R/S/HC-0/0       |

|------------------|--------------------|---------------------------------------------|-----------------------|---------------------------------------|-------------------|----------------------|------------------|

| (1)              | CFGS               | LWLO                                        | FREE                  | WRERR                                 | WREN              | WR                   | RD               |

| bit 7            |                    |                                             |                       |                                       |                   |                      | bit (            |

| Legend:          |                    |                                             |                       |                                       |                   |                      |                  |

| R = Readable     | bit                | W = Writable b                              | it                    | U = Unimplemer                        | nted bit, read as | s 'O'                |                  |

| S = Bit can on   | ly be set          | x = Bit is unkno                            | own                   | -n/n = Value at F                     | POR and BOR/      | /alue at all other I | Resets           |

| '1' = Bit is set |                    | '0' = Bit is clea                           | red                   | HC = Bit is clear                     | ed by hardware    | 9                    |                  |

| bit 7            | Unimplemen         | ted: Read as '1'                            |                       |                                       |                   |                      |                  |

| bit 6            | CFGS: Config       | guration Select bit                         |                       |                                       |                   |                      |                  |

|                  |                    | Configuration, Use<br>Flash program me      |                       | ID Registers                          |                   |                      |                  |

| bit 5            | LWLO: Load         | Write Latches On                            | ly bit <sup>(3)</sup> |                                       |                   |                      |                  |

|                  |                    | addressed progra                            |                       |                                       |                   |                      |                  |

|                  |                    | ressed program m<br>nitiated on the nex     |                       | n is loaded/update                    | ed and a write of | all program memo     | ory write latche |

| bit 4            | FREE: Progra       | am Flash Erase E                            | nable bit             |                                       |                   |                      |                  |

|                  |                    | s an erase operati<br>s a write operatior   |                       | •                                     | rdware cleared    | upon completion)     |                  |

| bit 3            |                    | gram/Erase Error                            | •                     |                                       |                   |                      |                  |

|                  |                    | n indicates an imp                          |                       |                                       | e attempt or te   | rmination (bit is s  | et automaticall  |

|                  |                    | et attempt (write '<br>gram or erase ope    |                       |                                       |                   |                      |                  |

| bit 2            |                    | ram/Erase Enable                            | •                     | , , , , , , , , , , , , , , , , , , , |                   |                      |                  |

|                  | 0                  | rogram/erase cyc                            |                       |                                       |                   |                      |                  |

|                  | 0 = Inhibits       | programming/eras                            | ing of program F      | lash                                  |                   |                      |                  |

| bit 1            | WR: Write Co       |                                             |                       |                                       |                   |                      |                  |

|                  |                    | a program Flash p<br>ration is self-timed   |                       |                                       | o onco onorativ   | on is complete       |                  |

|                  | •                  | bit can only be se                          |                       | •                                     | e once operatio   | on is complete.      |                  |

|                  |                    | /erase operation f                          | ` '                   |                                       | ive.              |                      |                  |

| bit 0            | RD: Read Co        | ontrol bit                                  |                       |                                       |                   |                      |                  |

|                  |                    | a program Flash r                           | ead. Read takes       | s one cycle. RD is                    | cleared in hard   | lware. The RD bit    | can only be se   |

|                  | ```                | ared) in software.<br>It initiate a prograr | n Flash read          |                                       |                   |                      |                  |

| Note 1: U        | nimplemented bit   |                                             |                       |                                       |                   |                      |                  |

|                  | •                  | automatically set I                         | by hardware whe       | en a program men                      | nory write or era | ase operation is st  | arted (WR = 1    |

|                  | he LWLO bit is igi | -                                           | -                     |                                       |                   | •                    | •                |

## REGISTER 10-5: PMCON1: PROGRAM MEMORY CONTROL 1 REGISTER

### 11.4 Register Definitions: PORTA

### REGISTER 11-2: PORTA: PORTA REGISTER

| U-0                                     | U-0 | R/W-x/x | R/W-x/x | R-x/x                                                 | R/W-x/x | R/W-x/x | R/W-x/x |  |

|-----------------------------------------|-----|---------|---------|-------------------------------------------------------|---------|---------|---------|--|

| —                                       | —   | RA5     | RA4     | RA3                                                   | RA2     | RA1     | RA0     |  |

| bit 7                                   |     |         |         |                                                       |         |         | bit 0   |  |

|                                         |     |         |         |                                                       |         |         |         |  |

| Legend:                                 |     |         |         |                                                       |         |         |         |  |

| R = Readable bit W = Writable bit       |     |         | bit     | U = Unimplemented bit, read as '0'                    |         |         |         |  |

| u = Bit is unchanged x = Bit is unknown |     |         | nown    | -n/n = Value at POR and BOR/Value at all other Resets |         |         |         |  |

| '1' = Bit is set '0' = Bit is cleared   |     |         | ared    |                                                       |         |         |         |  |

| bit 7-6 | Unimplemented: Read as '0' |

|---------|----------------------------|

|---------|----------------------------|

bit 5-0 RA<5:0>: PORTA I/O Value bits<sup>(1)</sup>

1 = Port pin is <u>></u> Vін

0 = Port pin is <u><</u> Vı∟

**Note 1:** Writes to PORTA are actually written to corresponding LATA register. Reads from PORTA register is return of actual I/O pin values.

### REGISTER 11-3: TRISA: PORTA TRI-STATE REGISTER

| U-0   | U-0 | R/W-1/1 | R/W-1/1 | U-1  | R/W-1/1 | R/W-1/1 | R/W-1/1 |

|-------|-----|---------|---------|------|---------|---------|---------|

| —     | —   | TRISA5  | TRISA4  | _(1) | TRISA2  | TRISA1  | TRISA0  |

| bit 7 |     |         |         |      |         |         | bit 0   |

| Legend:              |                      |                                                       |

|----------------------|----------------------|-------------------------------------------------------|

| R = Readable bit     | W = Writable bit     | U = Unimplemented bit, read as '0'                    |

| u = Bit is unchanged | x = Bit is unknown   | -n/n = Value at POR and BOR/Value at all other Resets |

| '1' = Bit is set     | '0' = Bit is cleared |                                                       |

| bit 7-6 | Unimplemented: Read as '0'                                                                                                                         |

|---------|----------------------------------------------------------------------------------------------------------------------------------------------------|

| bit 5-4 | <b>TRISA&lt;5:4&gt;:</b> PORTA Tri-State Control bit<br>1 = PORTA pin configured as an input (tri-stated)<br>0 = PORTA pin configured as an output |

| bit 3   | Unimplemented: Read as '1'                                                                                                                         |

| bit 2-0 | <b>TRISA&lt;2:0&gt;:</b> PORTA Tri-State Control bit<br>1 = PORTA pin configured as an input (tri-stated)<br>0 = PORTA pin configured as an output |

Note 1: Unimplemented, read as '1'.

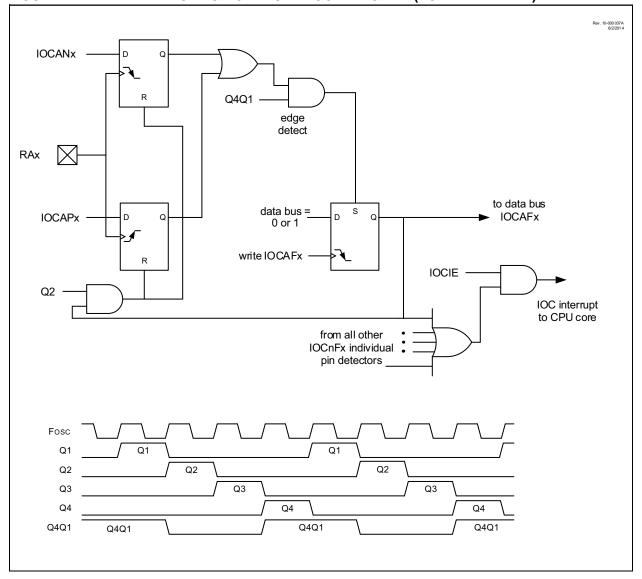

FIGURE 12-1: INTERRUPT-ON-CHANGE BLOCK DIAGRAM (PORTA EXAMPLE)

### 12.6 Register Definitions: Interrupt-on-Change Control

### REGISTER 12-1: IOCAP: INTERRUPT-ON-CHANGE PORTA POSITIVE EDGE REGISTER

| U-0                                                           | U-0 | R/W-0/0            | R/W-0/0                                               | R/W-0/0            | R/W-0/0 | R/W-0/0 | R/W-0/0 |

|---------------------------------------------------------------|-----|--------------------|-------------------------------------------------------|--------------------|---------|---------|---------|

| _                                                             | _   | IOCAP5             | IOCAP4                                                | IOCAP3             | IOCAP2  | IOCAP1  | IOCAP0  |

| bit 7                                                         |     |                    |                                                       |                    |         |         | bit 0   |

|                                                               |     |                    |                                                       |                    |         |         |         |

| Legend:                                                       |     |                    |                                                       |                    |         |         |         |

| R = Readable bit W = Writable bit U = Unimplemented bit, read |     |                    |                                                       | ented bit, read as | '0'     |         |         |

| u = Bit is unchanged x = Bit is unknown                       |     | wn                 | -n/n = Value at POR and BOR/Value at all other Resets |                    |         | Resets  |         |

| '1' = Bit is set                                              |     | '0' = Bit is clear | ed                                                    |                    |         |         |         |

bit 7-6 Unimplemented: Read as '0'

bit 5-0

bit 5-0

bit 5-0

IOCAP<5:0>: Interrupt-on-Change PORTA Positive Edge Enable bits

1 = Interrupt-on-Change enabled on the pin for a positive going edge. IOCAFx bit and IOCIF flag will be set upon detecting an edge.

0 = Interrupt-on-Change disabled for the associated pin.

### REGISTER 12-2: IOCAN: INTERRUPT-ON-CHANGE PORTA NEGATIVE EDGE REGISTER

| U-0   | U-0 | R/W-0/0 | R/W-0/0 | R/W-0/0 | R/W-0/0 | R/W-0/0 | R/W-0/0 |

|-------|-----|---------|---------|---------|---------|---------|---------|

| —     | _   | IOCAN5  | IOCAN4  | IOCAN3  | IOCAN2  | IOCAN1  | IOCAN0  |

| bit 7 |     |         |         |         |         |         | bit 0   |

| Legend:              |                      |                                                       |

|----------------------|----------------------|-------------------------------------------------------|

| R = Readable bit     | W = Writable bit     | U = Unimplemented bit, read as '0'                    |

| u = Bit is unchanged | x = Bit is unknown   | -n/n = Value at POR and BOR/Value at all other Resets |

| '1' = Bit is set     | '0' = Bit is cleared |                                                       |

bit 7-6 Unimplemented: Read as '0'

IOCAN<5:0>: Interrupt-on-Change PORTA Negative Edge Enable bits

- 1 = Interrupt-on-Change enabled on the pin for a negative going edge. IOCAFx bit and IOCIF flag will be set upon detecting an edge.

- 0 = Interrupt-on-Change disabled for the associated pin.

### REGISTER 12-3: IOCAF: INTERRUPT-ON-CHANGE PORTA FLAG REGISTER

| U-0         | U-0 | R/W/HS-0/0 | R/W/HS-0/0 | R/W/HS-0/0 | R/W/HS-0/0 | R/W/HS-0/0 | R/W/HS-0/0 |

|-------------|-----|------------|------------|------------|------------|------------|------------|

| _           | _   | IOCAF5     | IOCAF4     | IOCAF3     | IOCAF2     | IOCAF1     | IOCAF0     |

| bit 7 bit 0 |     |            |            |            |            |            |            |

| Legend:              |                      |                                                       |

|----------------------|----------------------|-------------------------------------------------------|

| R = Readable bit     | W = Writable bit     | U = Unimplemented bit, read as '0'                    |

| u = Bit is unchanged | x = Bit is unknown   | -n/n = Value at POR and BOR/Value at all other Resets |

| '1' = Bit is set     | '0' = Bit is cleared | HS - Bit is set in hardware                           |

bit 7-6 Unimplemented: Read as '0'

IOCAF<5:0>: Interrupt-on-Change PORTA Flag bits

1 = An enabled change was detected on the associated pin.

Set when IOCAPx = 1 and a rising edge was detected on RAx, or when IOCANx = 1 and a falling edge was detected on RAx.

0 = No change was detected, or the user cleared the detected change.

### 15.1.5 INTERRUPTS

The ADC module allows for the ability to generate an interrupt upon completion of an Analog-to-Digital conversion. The ADC Interrupt Flag is the ADIF bit in the PIR1 register. The ADC Interrupt Enable is the ADIE bit in the PIE1 register. The ADIF bit must be cleared in software.

- **Note 1:** The ADIF bit is set at the completion of every conversion, regardless of whether or not the ADC interrupt is enabled.

- **2:** The ADC operates during Sleep only when the FRC oscillator is selected.

This interrupt can be generated while the device is operating or while in Sleep. If the device is in Sleep, the interrupt will wake-up the device. Upon waking from Sleep, the next instruction following the SLEEP instruction is always executed. If the user is attempting to wake-up from Sleep and resume in-line code execution, the GIE and PEIE bits of the INTCON register must be disabled. If the GIE and PEIE bits of the INTCON register are enabled, execution will switch to the Interrupt Service Routine.

### 15.1.6 RESULT FORMATTING

The 10-bit ADC conversion result can be supplied in two formats, left justified or right justified. The ADFM bit of the ADCON1 register controls the output format.

Figure 15-3 shows the two output formats.

### Rev. 10-000054A 7/30/2013 ADRESH ADRESL (ADFM = 0) MSB LSB bit 7 bit 0 bit 7 bit 0 10-bit ADC Result Unimplemented: Read as '0' (ADFM = 1) LSB MSB bit 7 bit 0 bit 7 bit 0 Unimplemented: Read as '0' 10-bit ADC Result

### FIGURE 15-3: 10-BIT ADC CONVERSION RESULT FORMAT

### 21.2 SPI Mode Overview

The Serial Peripheral Interface (SPI) bus is a synchronous serial data communication bus that operates in Full-Duplex mode. Devices communicate in a master/slave environment where the master device initiates the communication. A slave device is controlled through a Chip Select known as Slave Select.

The SPI bus specifies four signal connections:

- Serial Clock (SCKx)

- Serial Data Out (SDOx)

- Serial Data In (SDIx)

- Slave Select (SSx)

Figure 21-1 shows the block diagram of the MSSP module when operating in SPI mode.

The SPI bus operates with a single master device and one or more slave devices. When multiple slave devices are used, an independent Slave Select connection is required from the master device to each slave device.

Figure 21-4 shows a typical connection between a master device and multiple slave devices.

The master selects only one slave at a time. Most slave devices have tri-state outputs so their output signal appears disconnected from the bus when they are not selected.

Transmissions involve two shift registers, eight bits in size, one in the master and one in the slave. With either the master or the slave device, data is always shifted out one bit at a time, with the Most Significant bit (MSb) shifted out first. At the same time, a new Least Significant bit (LSb) is shifted into the same register.

Figure 21-5 shows a typical connection between two processors configured as master and slave devices.

Data is shifted out of both shift registers on the programmed clock edge and latched on the opposite edge of the clock.

The master device transmits information out on its SDOx output pin which is connected to, and received by, the slave's SDIx input pin. The slave device transmits information out on its SDOx output pin, which is connected to, and received by, the master's SDIx input pin.

To begin communication, the master device first sends out the clock signal. Both the master and the slave devices should be configured for the same clock polarity.

The master device starts a transmission by sending out the MSb from its shift register. The slave device reads this bit from that same line and saves it into the LSb position of its shift register. During each SPI clock cycle, a full-duplex data transmission occurs. This means that while the master device is sending out the MSb from its shift register (on its SDOx pin) and the slave device is reading this bit and saving it as the LSb of its shift register, that the slave device is also sending out the MSb from its shift register (on its SDOx pin) and the master device is reading this bit and saving it as the LSb of its shift register.

After eight bits have been shifted out, the master and slave have exchanged register values.

If there is more data to exchange, the shift registers are loaded with new data and the process repeats itself.

Whether the data is meaningful or not (dummy data), depends on the application software. This leads to three scenarios for data transmission:

- Master sends useful data and slave sends dummy data.

- Master sends useful data and slave sends useful data.

- Master sends dummy data and slave sends useful data.

Transmissions may involve any number of clock cycles. When there is no more data to be transmitted, the master stops sending the clock signal and it deselects the slave.

Every slave device connected to the bus that has not been selected through its slave select line must disregard the clock and transmission signals and must not transmit out any data of its own.

### 23.1 CLCx Setup

Programming the CLCx module is performed by configuring the four stages in the logic signal flow. The four stages are:

- Data selection

- Data gating

- Logic function selection

- Output polarity

Each stage is setup at run time by writing to the corresponding CLCx Special Function Registers. This has the added advantage of permitting logic reconfiguration on-the-fly during program execution.

### 23.1.1 DATA SELECTION

There are 16 signals available as inputs to the configurable logic. Four 8-input multiplexers are used to select the inputs to pass on to the next stage. The 16 inputs to the multiplexers are arranged in groups of four. Each group is available to two of the four multiplexers, in each case, paired with a different group. This arrangement makes possible selection of up to two from a group without precluding a selection from another group.

Data selection is through four multiplexers as indicated on the left side of Figure 23-2. Data inputs in the figure are identified by a generic numbered input name.

Table 23-1 correlates the generic input name to the actual signal for each CLC module. The columns labeled lcxd1 through lcxd4 indicate the MUX output for the selected data input. D1S through D4S are abbreviations for the MUX select input codes: LCxD1S<2:0> through LCxD4S<2:0>, respectively. Selecting a data input in a column excludes all other inputs in that column.

Data inputs are selected with CLCxSEL0 and CLCxSEL1 registers (Register 23-3 and Register 23-5, respectively).

Note: Data selections are undefined at power-up.

| Data Input | lcxd1<br>D1S | lcxd2<br>D2S | lcxd3<br>D3S | lcxd4<br>D4S | CLC 1       | CLC 2       |

|------------|--------------|--------------|--------------|--------------|-------------|-------------|

| LCx_in[0]  | 000          | _            | _            | 100          | CLC1IN0     | CLC2IN0     |

| LCx_in[1]  | 001          | _            | _            | 101          | CLC1IN1     | CLC2IN1     |

| LCx_in[2]  | 010          | _            | _            | 110          | C1OUT_sync  | C1OUT_sync  |

| LCx_in[3]  | 011          | _            | _            | 111          | C2OUT_sync  | C2OUT_sync  |

| LCx_in[4]  | 100          | 000          | _            | _            | Fosc        | Fosc        |

| LCx_in[5]  | 101          | 001          | _            | _            | T0_overflow | T0_overflow |

| LCx_in[6]  | 110          | 010          | _            | _            | T1_overflow | T1_overflow |

| LCx_in[7]  | 111          | 011          | _            | _            | T2_match    | T2_match    |

| LCx_in[8]  | —            | 100          | 000          | _            | LC1_out     | LC1_out     |

| LCx_in[9]  |              | 101          | 001          | _            | LC2_out     | LC2_out     |

| LCx_in[10] |              | 110          | 010          | _            | Reserved    | Reserved    |

| LCx_in[11] | —            | 111          | 011          | _            | Reserved    | Reserved    |

| LCx_in[12] |              | _            | 100          | 000          | NCO1_out    | LFINTOSC    |

| LCx_in[13] |              | _            | 101          | 001          | HFINTOSC    | FRC         |

| LCx_in[14] | _            | _            | 110          | 010          | PWM3_out    | PWM1_out    |

| LCx_in[15] | _            | _            | 111          | 011          | PWM4_out    | PWM2_out    |

TABLE 23-1: CLCx DATA INPUT SELECTION

| RRF              | Rotate Right f through Carry                                                                                                                                                                                       |

|------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Syntax:          | [ <i>label</i> ] RRF f,d                                                                                                                                                                                           |

| Operands:        | $\begin{array}{l} 0 \leq f \leq 127 \\ d \in [0,1] \end{array}$                                                                                                                                                    |

| Operation:       | See description below                                                                                                                                                                                              |

| Status Affected: | С                                                                                                                                                                                                                  |

| Description:     | The contents of register 'f' are rotated<br>one bit to the right through the Carry<br>flag. If 'd' is '0', the result is placed in<br>the W register. If 'd' is '1', the result is<br>placed back in register 'f'. |

|                  | C Register f                                                                                                                                                                                                       |

| SUBLW                     | Subtract W        | from literal                                                                             |  |  |  |

|---------------------------|-------------------|------------------------------------------------------------------------------------------|--|--|--|

| Syntax:                   | [label] SU        | IBLW k                                                                                   |  |  |  |

| Operands:                 | $0 \le k \le 255$ |                                                                                          |  |  |  |

| Operation:                | $k - (W) \to (W)$ |                                                                                          |  |  |  |

| Status Affected: C, DC, Z |                   |                                                                                          |  |  |  |

| Description:              | plement meth      | er is subtracted (2's com-<br>nod) from the 8-bit literal<br>t is placed in the W regis- |  |  |  |

|                           | <b>C =</b> 0      | W > k                                                                                    |  |  |  |

|                           | <b>C =</b> 1      | $W \le k$                                                                                |  |  |  |

| C = 0        | W > k               |

|--------------|---------------------|

| <b>C =</b> 1 | $W \leq k$          |

| DC = 0       | W<3:0> > k<3:0>     |

| DC = 1       | $W<3:0> \le k<3:0>$ |

|              |                     |

$W<3:0> \le f<3:0>$

| SLEEP            | Enter Sleep mode                                                                                                                                                                                                                     |

|------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Syntax:          | [label] SLEEP                                                                                                                                                                                                                        |

| Operands:        | None                                                                                                                                                                                                                                 |

| Operation:       | $\begin{array}{l} 00h \rightarrow WDT, \\ 0 \rightarrow \underline{WDT} \text{ prescaler}, \\ 1 \rightarrow \underline{TO}, \\ 0 \rightarrow \overline{PD} \end{array}$                                                              |

| Status Affected: | TO, PD                                                                                                                                                                                                                               |

| Description:     | The power-down Status bit, $\overline{\text{PD}}$ is cleared. Time-out Status bit, $\overline{\text{TO}}$ is set. Watchdog Timer and its prescaler are cleared.<br>The processor is put into Sleep mode with the oscillator stopped. |

| SUBWF                                                                                                                                                                                     | Subtract W from f                                                 |                 |  |  |  |

|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------|-----------------|--|--|--|

| Syntax:                                                                                                                                                                                   | [label] SU                                                        | JBWF f,d        |  |  |  |

| Operands:                                                                                                                                                                                 | $\begin{array}{l} 0 \leq f \leq 127 \\ d  \in  [0,1] \end{array}$ |                 |  |  |  |

| Operation:                                                                                                                                                                                | (f) - $(W)$ → $(d)$                                               | lestination)    |  |  |  |

| Status Affected:                                                                                                                                                                          | C, DC, Z                                                          |                 |  |  |  |

| Description: Subtract (2's complement metho<br>register from register 'f'. If 'd' is 'd'<br>result is stored in the W<br>register. If 'd' is '1', the result is s<br>back in register 'f. |                                                                   |                 |  |  |  |

|                                                                                                                                                                                           | <b>C</b> = 0                                                      | W > f           |  |  |  |

|                                                                                                                                                                                           | <b>C =</b> 1                                                      | $W \leq f$      |  |  |  |

|                                                                                                                                                                                           | DC = 0                                                            | W<3:0> > f<3:0> |  |  |  |

| SUBWFB           | Subtract W from f with Borrow                                                                                                                                                                       |

|------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Syntax:          | SUBWFB f {,d}                                                                                                                                                                                       |

| Operands:        | $\begin{array}{l} 0\leq f\leq 127\\ d\in [0,1] \end{array}$                                                                                                                                         |

| Operation:       | $(f) - (W) - (\overline{B}) \rightarrow dest$                                                                                                                                                       |

| Status Affected: | C, DC, Z                                                                                                                                                                                            |

| Description:     | Subtract W and the BORROW flag<br>(CARRY) from register 'f' (2's comple-<br>ment method). If 'd' is '0', the result is<br>stored in W. If 'd' is '1', the result is<br>stored back in register 'f'. |

DC = 1

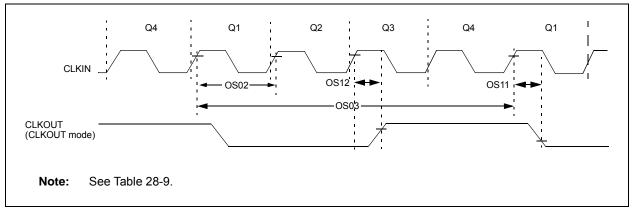

FIGURE 28-5: CLOCK TIMING

### TABLE 28-7: CLOCK OSCILLATOR TIMING REQUIREMENTS

| Param.<br>No. | Sym. | Characteristic                          | Min. | Тур† | Max.     | Units | Conditions           |  |

|---------------|------|-----------------------------------------|------|------|----------|-------|----------------------|--|

| OS01          | Fosc | External CLKIN Frequency <sup>(1)</sup> | DC   | —    | 0.5      | MHz   | External Clock (ECL) |  |

|               |      |                                         | DC   | —    | 4        | MHz   | External Clock (ECM) |  |

|               |      |                                         | DC   | —    | 20       | MHz   | External Clock (ECH) |  |

| OS02          | Tosc | External CLKIN Period <sup>(1)</sup>    | 50   | _    | $\infty$ | ns    | External Clock (EC)  |  |

| OS03          | Тсү  | Instruction Cycle Time <sup>(1)</sup>   | 200  | TCY  | DC       | ns    | Tcy = 4/Fosc         |  |

### Standard Operating Conditions (unless otherwise stated)

\* These parameters are characterized but not tested.

† Data in "Typ" column is at 3.0V, 25°C unless otherwise stated. These parameters are for design guidance only and are not tested.

Note 1: Instruction cycle period (TCY) equals four times the input oscillator time base period. All specified values are based on characterization data for that particular oscillator type under standard operating conditions with the device executing code. Exceeding these specified limits may result in an unstable oscillator operation and/or higher than expected current consumption. All devices are tested to operate at "min" values with an external clock applied to CLKIN pin. When an external clock input is used, the "max" cycle time limit is "DC" (no clock) for all devices.

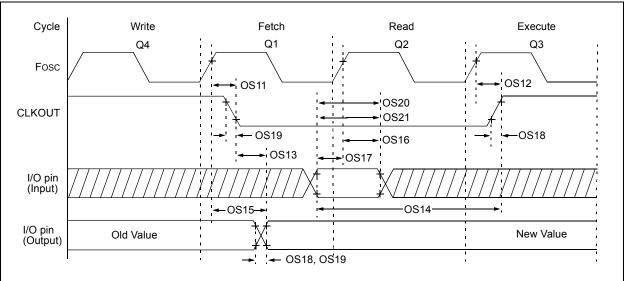

| TABLE 28-9: | CLKOUT AND I/O TIMING PARAMETERS |

|-------------|----------------------------------|

|-------------|----------------------------------|

| Standard Operating Conditions (unless otherwise stated) |          |                                                               |               |          |          |       |                                                                             |

|---------------------------------------------------------|----------|---------------------------------------------------------------|---------------|----------|----------|-------|-----------------------------------------------------------------------------|

| Param.<br>No.                                           | Sym.     | Characteristic                                                | Min.          | Тур†     | Max.     | Units | Conditions                                                                  |

| OS11                                                    | TosH2ckL | Fosc↑ to CLKOUT↓ <sup>(1)</sup>                               | _             | _        | 70       | ns    | $3.3V \le V\text{DD} \le 5.0V$                                              |

| OS12                                                    | TosH2ckH | Fosc↑ to CLKOUT↑ <sup>(1)</sup>                               | —             |          | 72       | ns    | $3.3V \le V\text{DD} \le 5.0V$                                              |

| OS13                                                    | TckL2ioV | CLKOUT↓ to Port out valid <sup>(1)</sup>                      | —             | -        | 20       | ns    |                                                                             |

| OS14                                                    | TioV2ckH | Port input valid before CLKOUT↑ <sup>(1)</sup>                | Tosc + 200 ns |          |          | ns    |                                                                             |

| OS15                                                    | TosH2ioV | Fosc↑ (Q1 cycle) to Port out valid                            | —             | 50       | 70*      | ns    | $3.3V \le V\text{DD} \le 5.0V$                                              |

| OS16                                                    | TosH2iol | Fosc↑ (Q2 cycle) to Port input invalid<br>(I/O in setup time) | 50            | —        | _        | ns    | $3.3V \le V\text{DD} \le 5.0V$                                              |

| OS17                                                    | TioV2osH | Port input valid to Fosc↑ (Q2 cycle)<br>(I/O in setup time)   | 20            | —        | —        | ns    |                                                                             |

| OS18*                                                   | TioR     | Port output rise time                                         | _             | 40<br>15 | 72<br>32 | ns    | $VDD = 1.8V$ $3.3V \le VDD \le 5.0V$                                        |

| OS19*                                                   | TioF     | Port output fall time                                         | —             | 28<br>15 | 55<br>30 | ns    | $\begin{array}{l} VDD \mbox{=} 1.8V \\ 3.3V \leq VDD \leq 5.0V \end{array}$ |

| OS20*                                                   | Tinp     | INT pin input high or low time                                | 25            | —        | —        | ns    |                                                                             |

| OS21*                                                   | Tioc     | Interrupt-on-change new input level time                      | 25            | —        | —        | ns    |                                                                             |

\* These parameters are characterized but not tested.

$\dagger$  Data in "Typ" column is at 3.0V, 25°C unless otherwise stated.

Note 1: Measurements are taken in EXTRC mode where CLKOUT output is 4 x Tosc.

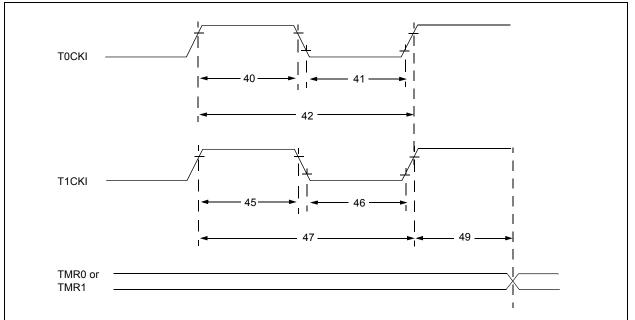

### FIGURE 28-10: TIMER0 AND TIMER1 EXTERNAL CLOCK TIMINGS

| TABLE 28-11: | TIMER0 AND TIMER1 EXTERNAL CLOCK REQUIREMENTS |

|--------------|-----------------------------------------------|

|--------------|-----------------------------------------------|

| Standar       | d Operating | Conditions (u                                     | nless otherwis              | e stated)      |                                           |        |      |                        |                    |

|---------------|-------------|---------------------------------------------------|-----------------------------|----------------|-------------------------------------------|--------|------|------------------------|--------------------|

| Param.<br>No. | Sym.        |                                                   | Characteristi               | c              | Min.                                      | Тур†   | Max. | Units                  | Conditions         |

| 40*           | T⊤0H        | T0CKI High Pulse Width No Pr                      |                             | No Prescaler   | 0.5 Tcy + 20                              | _      |      | ns                     |                    |

|               |             |                                                   |                             | With Prescaler | 10                                        | _      | _    | ns                     |                    |

| 41*           | T⊤0L        | T0CKI Low Pulse Width No Prescaler With Prescaler |                             | 0.5 Tcy + 20   | _                                         | _      | ns   |                        |                    |

|               |             |                                                   |                             | 10             |                                           | _      | ns   |                        |                    |

| 42*           | TT0P        | T0CKI Period                                      | 1                           |                | Greater of:<br>20 or <u>Tcy + 40</u><br>N | _      | _    | ns                     | N = prescale value |

| 45*           | Тт1Н        | T1CKI High<br>Time                                | Synchronous, N              | No Prescaler   | 0.5 Tcy + 20                              |        |      | ns                     |                    |

|               |             |                                                   | Synchronous, with Prescaler |                | 15                                        | _      |      | ns                     |                    |

|               |             |                                                   | Asynchronous                |                | 30                                        |        |      | ns                     |                    |

| 46*           | TT1L        | T1CKI Low<br>Time                                 | Synchronous, No Prescaler   |                | 0.5 Tcy + 20                              |        |      | ns                     |                    |

|               |             |                                                   | Synchronous, with Prescaler |                | 15                                        |        |      | ns                     |                    |

|               |             |                                                   | Asynchronous                |                | 30                                        | _      |      | ns                     |                    |

| 47*           | TT1P        | T1CKI Input<br>Period                             | Synchronous                 |                | Greater of:<br>30 or <u>Tcy + 40</u><br>N | _      |      | ns                     | N = prescale value |

|               |             |                                                   | Asynchronous                |                | 60                                        | _      | _    | ns                     |                    |

| 49*           | TCKEZTMR1   | Delay from E<br>Increment                         | xternal Clock Ed            | 2 Tosc         | _                                         | 7 Tosc | —    | Timers in Sync<br>mode |                    |

These parameters are characterized but not tested.

† Data in "Typ" column is at 3.0V, 25°C unless otherwise stated. These parameters are for design guidance only and are not tested.