Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Product Status             | Active                                                                    |

|----------------------------|---------------------------------------------------------------------------|

| Core Processor             | PIC                                                                       |

| Core Size                  | 8-Bit                                                                     |

| Speed                      | 20MHz                                                                     |

| Connectivity               | I <sup>2</sup> C, SPI                                                     |

| Peripherals                | Brown-out Detect/Reset, POR, PWM, WDT                                     |

| Number of I/O              | 11                                                                        |

| Program Memory Size        | 3.5KB (2K x 14)                                                           |

| Program Memory Type        | FLASH                                                                     |

| EEPROM Size                | -                                                                         |

| RAM Size                   | 128 x 8                                                                   |

| Voltage - Supply (Vcc/Vdd) | 2.3V ~ 5.5V                                                               |

| Data Converters            | A/D 8x10b                                                                 |

| Oscillator Type            | Internal                                                                  |

| Operating Temperature      | -40°C ~ 125°C (TA)                                                        |

| Mounting Type              | Surface Mount                                                             |

| Package / Case             | 16-UFQFN Exposed Pad                                                      |

| Supplier Device Package    | 16-UQFN (3x3)                                                             |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic16f1503-e-mv |

|                            |                                                                           |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

# TABLE OF CONTENTS

| 1.0   | Device Overview                                | 7   |

|-------|------------------------------------------------|-----|

| 2.0   | Enhanced Mid-Range CPU                         | 11  |

| 3.0   | Memory Organization                            | 13  |

| 4.0   | Device Configuration                           | 37  |

| 5.0   | Oscillator Module                              | 42  |

| 6.0   | Resets                                         | 51  |

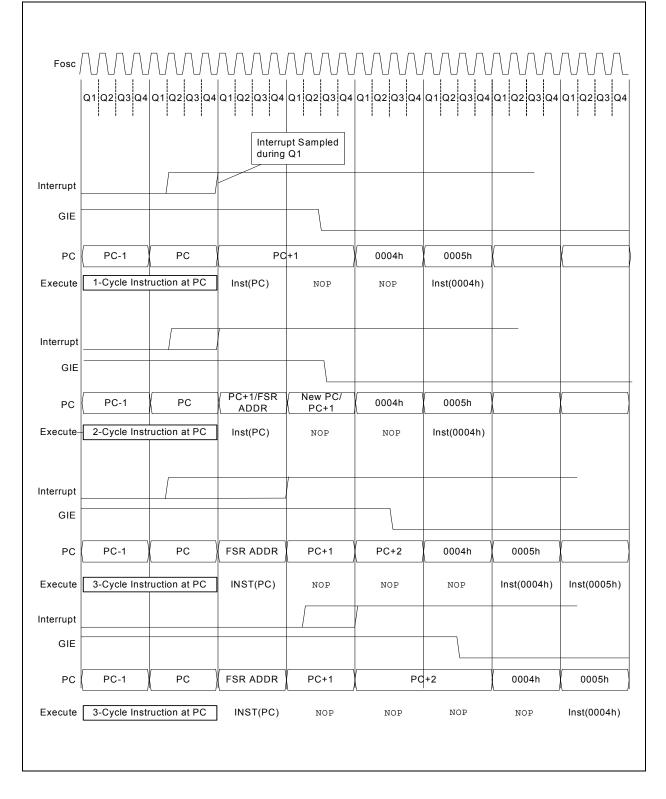

| 7.0   | Interrupts                                     | 59  |

| 8.0   | Power-Down Mode (Sleep)                        | 72  |

| 9.0   | Watchdog Timer (WDT)                           | 75  |

| 10.0  | Flash Program Memory Control                   | 79  |

| 11.0  | I/O Ports                                      | 95  |

| 12.0  | Interrupt-On-Change                            |     |

| 13.0  | Fixed Voltage Reference (FVR)                  | 108 |

| 14.0  | Temperature Indicator Module                   | 111 |

| 15.0  | Analog-to-Digital Converter (ADC) Module       | 113 |

| 16.0  | 5-Bit Digital-to-Analog Converter (DAC) Module | 127 |

| 17.0  | Comparator Module                              | 130 |

| 18.0  | Timer0 Module                                  |     |

| 19.0  | Timer1 Module with Gate Control                | 140 |

|       | Timer2 Module                                  |     |

|       |                                                |     |

| 22.0  | Pulse-Width Modulation (PWM) Module            | 208 |

| 23.0  |                                                |     |

| 24.0  | Numerically Controlled Oscillator (NCO) Module | 230 |

| 25.0  | Complementary Waveform Generator (CWG) Module  | 237 |

| 26.0  | In-Circuit Serial Programming™ (ICSP™)         |     |

| 27.0  | Instruction Set Summary                        |     |

|       | Electrical Specifications                      |     |

| 29.0  | DC and AC Characteristics Graphs and Charts    | 293 |

|       | Development Support                            |     |

| 31.0  | Packaging Information                          | 332 |

| Appe  | endix A: Data Sheet Revision History           | 347 |

|       | Microchip Website                              |     |

| Custo | omer Change Notification Service               | 348 |

|       | omer Support                                   |     |

| Produ | uct Identification System                      | 349 |

|       |                                                |     |

# 3.3.6 CORE FUNCTION REGISTERS SUMMARY

The Core Function registers listed in Table 3-4 can be addressed from any Bank.

| Addr            | Name   | Bit 7       | Bit 6                                                         | Bit 5         | Bit 4            | Bit 3        | Bit 2         | Bit 1  | Bit 0     | Value on<br>POR, BOR | Value on all other Resets |

|-----------------|--------|-------------|---------------------------------------------------------------|---------------|------------------|--------------|---------------|--------|-----------|----------------------|---------------------------|

| Bank            | 0-31   |             |                                                               |               |                  |              |               |        |           |                      |                           |

| x00h or<br>x80h | INDF0  |             | this location<br>ical register)                               |               | nts of FSR0H     | /FSR0L to a  | ddress data i | memory |           | xxxx xxxx            | uuuu uuuu                 |

| x01h or<br>x81h | INDF1  |             | this location<br>ical register)                               |               | nts of FSR1H     | /FSR1L to a  | ddress data i | memory |           | XXXX XXXX            | uuuu uuuu                 |

| x02h or<br>x82h | PCL    | Program C   | ounter (PC) I                                                 | Least Signifi | cant Byte        |              |               |        |           | 0000 0000            | 0000 0000                 |

| x03h or<br>x83h | STATUS | _           |                                                               |               | TO               | PD           | Z             | DC     | С         | 1 1000               | q quuu                    |

| x04h or<br>x84h | FSR0L  | Indirect Da | Indirect Data Memory Address 0 Low Pointer                    |               |                  |              |               |        |           | 0000 0000            | uuuu uuuu                 |

| x05h or<br>x85h | FSR0H  | Indirect Da | Indirect Data Memory Address 0 High Pointer                   |               |                  |              |               |        | 0000 0000 | 0000 0000            |                           |

| x06h or<br>x86h | FSR1L  | Indirect Da | Indirect Data Memory Address 1 Low Pointer 0000 0000 uuuuu uu |               |                  |              |               |        |           | uuuu uuuu            |                           |

| x07h or<br>x87h | FSR1H  | Indirect Da | Indirect Data Memory Address 1 High Pointer 0000 0000         |               |                  |              |               |        | 0000 0000 |                      |                           |

| x08h or<br>x88h | BSR    | _           | _                                                             | _             |                  |              | BSR<4:0>      |        |           | 0 0000               | 0 0000                    |

| x09h or<br>x89h | WREG   | Working Re  | Working Register                                              |               |                  |              |               |        |           | 0000 0000            | uuuu uuuu                 |

| x0Ahor<br>x8Ah  | PCLATH | _           | Write Buffer                                                  | for the upp   | er 7 bits of the | e Program Co | ounter        |        |           | -000 0000            | -000 0000                 |

| x0Bhor<br>x8Bh  | INTCON | GIE         | PEIE                                                          | TMR0IE        | INTE             | IOCIE        | TMR0IF        | INTF   | IOCIF     | 0000 0000            | 0000 0000                 |

### TABLE 3-4: CORE FUNCTION REGISTERS SUMMARY

Legend: x = unknown, u = unchanged, q = value depends on condition, - = unimplemented, read as '0', r = reserved. Shaded locations are unimplemented, read as '0'.

| IADLL    |                 |               |                                                    |               |               |             |        | 020)    |           |                      |                                 |

|----------|-----------------|---------------|----------------------------------------------------|---------------|---------------|-------------|--------|---------|-----------|----------------------|---------------------------------|

| Address  | Name            | Bit 7         | Bit 6                                              | Bit 5         | Bit 4         | Bit 3       | Bit 2  | Bit 1   | Bit 0     | Value on<br>POR, BOR | Value on all<br>other<br>Resets |

| Bank 3   | 1               |               |                                                    |               |               |             |        |         |           |                      |                                 |

| F8Ch     | _               | Unimplemen    | ted                                                |               |               |             |        |         |           | —                    | —                               |

| <br>FE3h |                 |               |                                                    |               |               |             |        |         |           |                      |                                 |

| FE4h     | STATUS_<br>SHAD | _             | _                                                  | -             | _             | —           | Z_SHAD | DC_SHAD | C_SHAD    | xxx                  | uuu                             |

| FE5h     | WREG_<br>SHAD   | Working Reg   | Working Register Shadow 22                         |               |               |             |        |         | XXXX XXXX | uuuu uuuu            |                                 |

| FE6h     | BSR_<br>SHAD    | _             | —                                                  | -             | Bank Select   | Register Sh | adow   |         |           | x xxxx               | u uuuu                          |

| FE7h     | PCLATH_<br>SHAD | -             | - Program Counter Latch High Register Shadow -     |               |               |             |        |         | -xxx xxxx | uuuu uuuu            |                                 |

| FE8h     | FSR0L_<br>SHAD  | Indirect Data | Memory Add                                         | Iress 0 Low F | Pointer Shado | W           |        |         |           | XXXX XXXX            | uuuu uuuu                       |

| FE9h     | FSR0H_<br>SHAD  | Indirect Data | ndirect Data Memory Address 0 High Pointer Shadow  |               |               |             |        |         |           | uuuu uuuu            |                                 |

| FEAh     | FSR1L_<br>SHAD  | Indirect Data | Indirect Data Memory Address 1 Low Pointer Shadow  |               |               |             |        |         |           | XXXX XXXX            | uuuu uuuu                       |

| FEBh     | FSR1H_<br>SHAD  | Indirect Data | Indirect Data Memory Address 1 High Pointer Shadow |               |               |             |        |         | XXXX XXXX | uuuu uuuu            |                                 |

| FECh     | —               | Unimplemen    | ted                                                |               |               |             |        |         |           |                      | _                               |

| FEDh     | STKPTR          | _             | —                                                  | —             | Current Star  | ck Pointer  |        |         |           | 1 1111               | 1 1111                          |

| FEEh     | TOSL            | Top-of-Stack  | Low byte                                           |               |               |             |        |         |           | XXXX XXXX            | uuuu uuuu                       |

| FEFh     | TOSH            | —             | Top-of-Stack                                       | High byte     |               |             |        |         |           | -xxx xxxx            | -uuu uuuu                       |

**TABLE 3-5:** SPECIAL FUNCTION REGISTER SUMMARY (CONTINUED)

x = unknown, u = unchanged, g = value depends on condition, - = unimplemented, r = reserved. Shaded locations are unimplemented, read as '0'.

PIC16F1503 only.

Unimplemented, read as '1'. Legend: : Note 1:

2:

### 4.6 Device ID and Revision ID

The memory location 8006h is where the Device ID and Revision ID are stored. The upper nine bits hold the Device ID. The lower five bits hold the Revision ID. See **Section 10.4 "User ID, Device ID and Configuration Word Access**" for more information on accessing these memory locations.

Development tools, such as device programmers and debuggers, may be used to read the Device ID and Revision ID.

### 4.7 Register Definitions: Device ID

### REGISTER 4-3: DEVID: DEVICE ID REGISTER

|       |          | R      | R | R   | R        | R | R     |

|-------|----------|--------|---|-----|----------|---|-------|

|       |          |        |   | DEV | <8:3>    |   |       |

|       |          | bit 13 |   |     |          |   | bit 8 |

|       |          |        |   |     |          |   |       |

| R     | R        | R      | R | R   | R        | R | R     |

|       | DEV<2:0> |        |   |     | REV<4:0> |   |       |

| bit 7 |          |        |   |     |          |   | bit 0 |

## Legend:

bit 13-5

R = Readable bit

'1' = Bit is set

| D | DEV<8:0>: Device ID bits |             |          |  |  |  |  |  |

|---|--------------------------|-------------|----------|--|--|--|--|--|

|   | Device                   | DEVID<13:0  | > Values |  |  |  |  |  |

|   | Device                   | DEV<8:0>    | REV<4:0> |  |  |  |  |  |

|   | PIC16LF1503              | 10 1101 101 | x xxxx   |  |  |  |  |  |

|   | PIC16F1503               | 10 1100 111 | x xxxx   |  |  |  |  |  |

'0' = Bit is cleared

#### bit 4-0 **REV<4:0>:** Revision ID bits

These bits are used to identify the revision (see Table under DEV<8:0> above).

### 5.2.2 INTERNAL CLOCK SOURCES

The device may be configured to use the internal oscillator block as the system clock by performing one of the following actions:

- Program the FOSC<1:0> bits in Configuration Words to select the INTOSC clock source, which will be used as the default system clock upon a device Reset.

- Write the SCS<1:0> bits in the OSCCON register to switch the system clock source to the internal oscillator during run-time. See Section

5.3 "Clock Switching" for more information.

In **INTOSC** mode, CLKIN is available for general purpose I/O. CLKOUT is available for general purpose I/O or CLKOUT.

The function of the CLKOUT pin is determined by the CLKOUTEN bit in Configuration Words.

The internal oscillator block has two independent oscillators that provides the internal system clock source.

- 1. The **HFINTOSC** (High-Frequency Internal Oscillator) is factory calibrated and operates at 16 MHz.

- 2. The **LFINTOSC** (Low-Frequency Internal Oscillator) operates at 31 kHz.

#### 5.2.2.1 HFINTOSC

The High-Frequency Internal Oscillator (HFINTOSC) is a factory calibrated 16 MHz internal clock source.

The output of the HFINTOSC connects to a postscaler and multiplexer (see Figure 5-1). The frequency derived from the HFINTOSC can be selected via software using the IRCF<3:0> bits of the OSCCON register. See **Section 5.2.2.6 "Internal Oscillator Clock Switch Timing"** for more information.

The HFINTOSC is enabled by:

- Configure the IRCF<3:0> bits of the OSCCON register for the desired HF frequency, and

- FOSC<1:0> = 00, or

- Set the System Clock Source (SCS) bits of the OSCCON register to '1x'.

A fast start-up oscillator allows internal circuits to power-up and stabilize before switching to HFINTOSC.

The High-Frequency Internal Oscillator Ready bit (HFIOFR) of the OSCSTAT register indicates when the HFINTOSC is running.

The High-Frequency Internal Oscillator Stable bit (HFIOFS) of the OSCSTAT register indicates when the HFINTOSC is running within 0.5% of its final value.

### 5.2.2.2 LFINTOSC

The Low-Frequency Internal Oscillator (LFINTOSC) is a 31 kHz internal clock source.

The output of the LFINTOSC connects to a multiplexer (see Figure 5-1). Select 31 kHz, via software, using the IRCF<3:0> bits of the OSCCON register. See Section 5.2.2.6 "Internal Oscillator Clock Switch Timing" for more information. The LFINTOSC is also the frequency for the Power-up Timer (PWRT) and the, Watchdog Timer (WDT).

The LFINTOSC is enabled by selecting 31 kHz (IRCF<3:0> bits of the OSCCON register = 000) as the system clock source (SCS bits of the OSCCON register = 1x), or when any of the following are enabled:

- Configure the IRCF<3:0> bits of the OSCCON register for the desired LF frequency, and

- FOSC<1:0> = 00, or

- Set the System Clock Source (SCS) bits of the OSCCON register to '1x'.

Peripherals that use the LFINTOSC are:

- Power-up Timer (PWRT)

- Watchdog Timer (WDT)

The Low-Frequency Internal Oscillator Ready bit (LFIOFR) of the OSCSTAT register indicates when the LFINTOSC is running.

#### 5.2.2.3 FRC

The FRC clock is an uncalibrated, nominal 600 kHz peripheral clock source.

The FRC is automatically turned on by the peripherals requesting the FRC clock.

The FRC clock continues to run during Sleep.

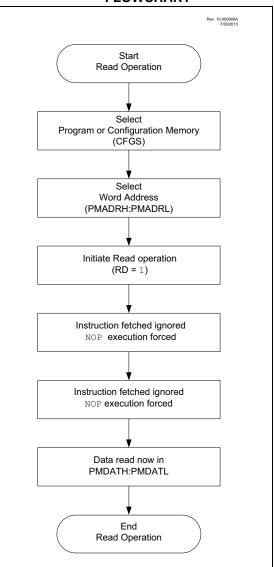

# 10.2.1 READING THE FLASH PROGRAM MEMORY

To read a program memory location, the user must:

- 1. Write the desired address to the PMADRH:PMADRL register pair.

- 2. Clear the CFGS bit of the PMCON1 register.

- 3. Then, set control bit RD of the PMCON1 register.

Once the read control bit is set, the program memory Flash controller will use the second instruction cycle to read the data. This causes the second instruction immediately following the "BSF PMCON1, RD" instruction to be ignored. The data is available in the very next cycle, in the PMDATH:PMDATL register pair; therefore, it can be read as two bytes in the following instructions.

PMDATH:PMDATL register pair will hold this value until another read or until it is written to by the user.

| Note: | The two instructions following a program    |

|-------|---------------------------------------------|

|       | memory read are required to be NOPs.        |

|       | This prevents the user from executing a     |

|       | 2-cycle instruction on the next instruction |

|       | after the RD bit is set.                    |

# FIGURE 10-1: FLASH PROGRAM MEMORY READ FLOWCHART

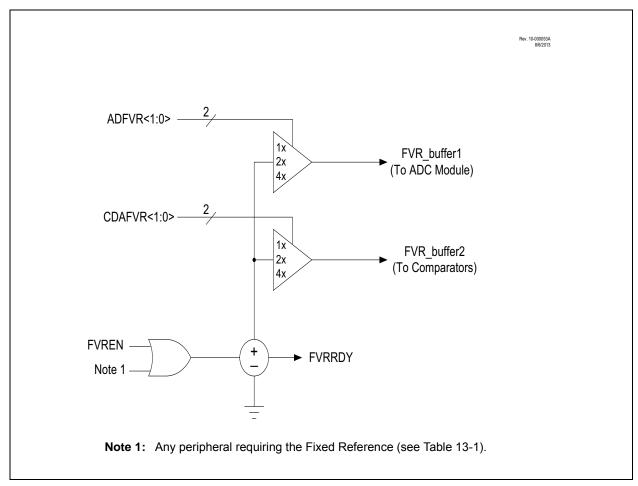

# 13.0 FIXED VOLTAGE REFERENCE (FVR)

The Fixed Voltage Reference (FVR) is a stable voltage reference, independent of VDD, with a nominal output level (VFVR) of 1.024V. The output of the FVR can be configured to supply a reference voltage to the following:

- ADC input channel

- · Comparator positive input

- · Comparator negative input

The FVR can be enabled by setting the FVREN bit of the FVRCON register.

### 13.1 Independent Gain Amplifier

The output of the FVR supplied to the peripherals, (listed above), is routed through a programmable gain amplifier. Each amplifier can be programmed for a gain of 1x, 2x or 4x, to produce the three possible voltage levels.

The ADFVR<1:0> bits of the FVRCON register are used to enable and configure the gain amplifier settings for the reference supplied to the ADC module. Reference **Section 15.0 "Analog-to-Digital Converter (ADC) Module**" for additional information.

The CDAFVR<1:0> bits of the FVRCON register are used to enable and configure the gain amplifier settings for the reference supplied to the comparator modules. Reference **Section 17.0 "Comparator Module"** for additional information.

To minimize current consumption when the FVR is disabled, the FVR buffers should be turned off by clearing the Buffer Gain Selection bits.

## 13.2 FVR Stabilization Period

When the Fixed Voltage Reference module is enabled, it requires time for the reference and amplifier circuits to stabilize. Once the circuits stabilize and are ready for use, the FVRRDY bit of the FVRCON register will be set. See the FVR Stabilization Period characterization graph, Figure 29-52.

## FIGURE 13-1: VOLTAGE REFERENCE BLOCK DIAGRAM

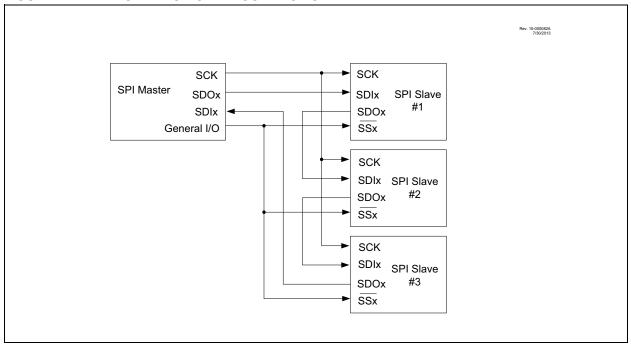

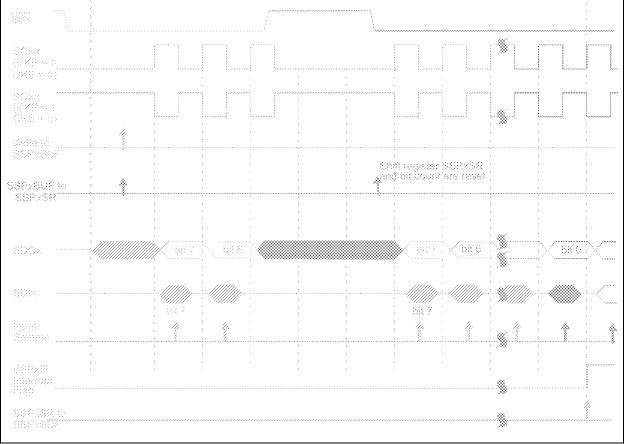

FIGURE 21-7: SPI DAISY-CHAIN CONNECTION

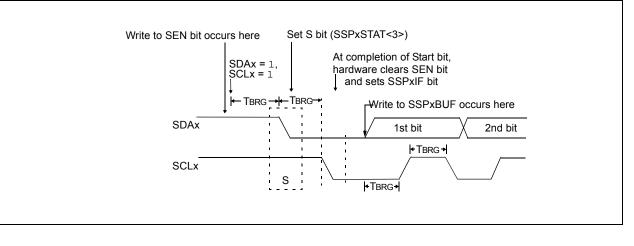

### 21.6.4 I<sup>2</sup>C MASTER MODE START CONDITION TIMING

To initiate a Start condition (Figure 21-26), the user sets the Start Enable bit, SEN bit of the SSPxCON2 register. If the SDAx and SCLx pins are sampled high, the Baud Rate Generator is reloaded with the contents of SSPxADD<7:0> and starts its count. If SCLx and SDAx are both sampled high when the Baud Rate Generator times out (TBRG), the SDAx pin is driven low. The action of the SDAx being driven low while SCLx is high is the Start condition and causes the S bit of the SSPxADD<7:0> and resumes its count. When the Baud Rate Generator times out (TBRG), the SEN bit of the SSPxADD<7:0> and resumes its count. When the Baud Rate Generator times out (TBRG), the SEN bit of the SSPxCON2 register will be automatically cleared

### FIGURE 21-26: FIRST START BIT TIMING

by hardware; the Baud Rate Generator is suspended, leaving the SDAx line held low and the Start condition is complete.

- Note 1: If at the beginning of the Start condition, the SDAx and SCLx pins are already sampled low, or if during the Start condition, the SCLx line is sampled low before the SDAx line is driven low, a bus collision occurs, the Bus Collision Interrupt Flag, BCLxIF, is set, the Start condition is aborted and the I<sup>2</sup>C module is reset into its Idle state.

- 2: The Philips I<sup>2</sup>C Specification states that a bus collision cannot occur on a Start.

| R-0/0                 | R/W-0/0                                                          | R/W-0/0                                                                                                                                                                                                                                                   | R/W-0/0                       | R/W-0/0                                                                  | R/W-0/0          | R/W-0/0          | R/W-0/0        |  |  |

|-----------------------|------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------|--------------------------------------------------------------------------|------------------|------------------|----------------|--|--|

| ACKTIM <sup>(3)</sup> | PCIE                                                             | SCIE                                                                                                                                                                                                                                                      | BOEN                          | SDAHT                                                                    | SBCDE            | AHEN             | DHEN           |  |  |

| bit 7                 |                                                                  |                                                                                                                                                                                                                                                           |                               |                                                                          |                  |                  | bit            |  |  |

| Legend:               |                                                                  |                                                                                                                                                                                                                                                           |                               |                                                                          |                  |                  |                |  |  |

| R = Readable          | bit                                                              | W = Writable                                                                                                                                                                                                                                              | bit                           | U = Unimpler                                                             | mented bit, read | l as '0'         |                |  |  |

| u = Bit is unch       | anged                                                            | x = Bit is unk                                                                                                                                                                                                                                            | nown                          | -n/n = Value a                                                           | at POR and BO    | R/Value at all c | ther Resets    |  |  |

| '1' = Bit is set      | -                                                                | '0' = Bit is cle                                                                                                                                                                                                                                          | eared                         |                                                                          |                  |                  |                |  |  |

| bit 7                 | ACKTIM: Ad                                                       | cknowledge Tim                                                                                                                                                                                                                                            | ne Status bit (I <sup>2</sup> | C mode only) <sup>(</sup>                                                | 3)               |                  |                |  |  |

|                       | 1 = Indicates                                                    | s the I <sup>2</sup> C bus is<br>Acknowledge se                                                                                                                                                                                                           | in an Acknowle                | edge sequence                                                            | e, set on eighth |                  | SCLx clock     |  |  |

| bit 6                 | PCIE: Stop                                                       | Condition Interre                                                                                                                                                                                                                                         | upt Enable bit (              | I <sup>2</sup> C mode only                                               | /)               |                  |                |  |  |

|                       |                                                                  | interrupt on detention interrupt                                                                                                                                                                                                                          |                               |                                                                          |                  |                  |                |  |  |

| bit 5                 | SCIE: Start                                                      | Condition Interr                                                                                                                                                                                                                                          | upt Enable bit (              | I <sup>2</sup> C mode only                                               | /)               |                  |                |  |  |

|                       |                                                                  | nterrupt on dete                                                                                                                                                                                                                                          |                               |                                                                          | litions          |                  |                |  |  |

| bit 4                 | BOEN: Buff                                                       | er Overwrite En                                                                                                                                                                                                                                           | able bit                      |                                                                          |                  |                  |                |  |  |

|                       | 0 = lf n                                                         | <u>e mode:</u> <sup>(1)</sup><br>PxBUF updates<br>ew byte is rece<br>PxCON1 registe                                                                                                                                                                       | ived with BF bi               | t of the SSPx                                                            | STAT register a  |                  |                |  |  |

|                       | In I <sup>2</sup> C Maste<br>This bit                            | er mode:<br>is ignored.                                                                                                                                                                                                                                   |                               |                                                                          |                  |                  |                |  |  |

|                       | state                                                            | <u>mode:</u><br>PxBUF is updat<br>e of the SSPOV<br>PxBUF is only u                                                                                                                                                                                       | / bit only if the I           | BF bit = 0.                                                              |                  | dress/data byte  | e, ignoring th |  |  |

| bit 3                 |                                                                  | Ax Hold Time S                                                                                                                                                                                                                                            | •                             |                                                                          | •                |                  |                |  |  |

|                       | 1 = Minimun                                                      | n of 300 ns hold                                                                                                                                                                                                                                          | time on SDAx                  | DAx after the falling edge of SCLx<br>DAx after the falling edge of SCLx |                  |                  |                |  |  |

| bit 2                 |                                                                  |                                                                                                                                                                                                                                                           |                               |                                                                          |                  |                  |                |  |  |

|                       | If on the risi                                                   | <b>SBCDE:</b> Slave Mode Bus Collision Detect Enable bit (I <sup>2</sup> C Slave mode only)<br>If on the rising edge of SCLx, SDAx is sampled low when the module is outputting a high state<br>BCLxIF bit of the PIR2 register is set, and bus goes idle |                               |                                                                          |                  |                  |                |  |  |

|                       | 1 = Enable s                                                     | slave bus collisi<br>us collision inter                                                                                                                                                                                                                   | on interrupts                 | -                                                                        |                  |                  |                |  |  |

| bit 1                 | AHEN: Address Hold Enable bit (I <sup>2</sup> C Slave mode only) |                                                                                                                                                                                                                                                           |                               |                                                                          |                  |                  |                |  |  |

|                       | SSPxC                                                            | ng the eighth fa<br>ON1 register wi<br>holding is disa                                                                                                                                                                                                    | Il be cleared ar              |                                                                          |                  | address byte,    | CKP bit of th  |  |  |

| bit 0                 | DHEN: Data                                                       | a Hold Enable b                                                                                                                                                                                                                                           | it (I <sup>2</sup> C Slave me | ode only)                                                                |                  |                  |                |  |  |

|                       | bit of the                                                       | g the eighth fall<br>e SSPxCON1 r<br>lding is disabled                                                                                                                                                                                                    | egister and SC                |                                                                          | •                | ave hardware o   | lears the CK   |  |  |

|                       | daisy-chained                                                    | d SPI operation,<br>is received and                                                                                                                                                                                                                       | allows the user               |                                                                          |                  |                  |                |  |  |

| • •                   | -                                                                |                                                                                                                                                                                                                                                           |                               |                                                                          |                  | -                |                |  |  |

### REGISTER 21-4: SSPxCON3: SSP CONTROL REGISTER 3

3: The ACKTIM Status bit is only active when the AHEN bit or DHEN bit is set.

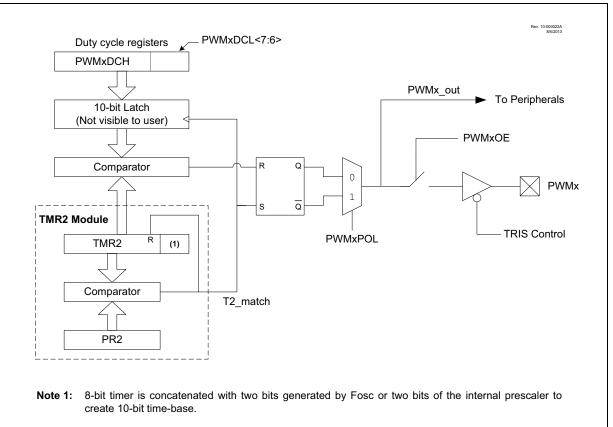

# 22.0 PULSE-WIDTH MODULATION (PWM) MODULE

The PWM module generates a Pulse-Width Modulated signal determined by the duty cycle, period, and resolution that are configured by the following registers:

- PR2

- T2CON

- PWMxDCH

- PWMxDCL

- PWMxCON

Figure 22-1 shows a simplified block diagram of PWM operation.

For a step-by-step procedure on how to set up this module for PWM operation, refer to Section 22.1.9 "Setup for PWM Operation using PWMx Pins".

### FIGURE 22-1: SIMPLIFIED PWM BLOCK DIAGRAM

### TABLE 25-2: SUMMARY OF REGISTERS ASSOCIATED WITH CWG

| Name     | Bit 7 | Bit 6   | Bit 5        | Bit 4        | Bit 3    | Bit 2    | Bit 1     | Bit 0      | Register<br>on Page |

|----------|-------|---------|--------------|--------------|----------|----------|-----------|------------|---------------------|

| ANSELA   | _     | —       | -            | ANSA4        | -        | ANSA2    | ANSA1     | ANSA0      | 99                  |

| CWG1CON0 | G1EN  | G10EB   | G10EA        | G1POLB       | G1POLA   | _        | _         | G1CS0      | 244                 |

| CWG1CON1 | G1ASD | LB<1:0> | G1ASDLA<1:0> |              | _        | _        | G1IS•     | 245        |                     |

| CWG1CON2 | G1ASE | G1ARSEN | _            | —            | G1ASDSC2 | G1ASDSC1 | G1ASDSFLT | G1ASDSCLC2 | 246                 |

| CWG1DBF  | -     | _       |              | CWG1DBF<5:0> |          |          |           |            | 247                 |

| CWG1DBR  | _     | —       |              | CWG1DBR<5:0> |          |          |           |            | 247                 |

| TRISA    | _     | —       | TRISA5       | TRISA4       | _(1)     | TRISA2   | TRISA1    | TRISA0     | 98                  |

| TRISC    |       | _       | TRISC5       | TRISC4       | TRISC3   | TRISC2   | TRISC1    | TRISC0     | 102                 |

Legend: x = unknown, u = unchanged, - = unimplemented locations read as '0'. Shaded cells are not used by CWG.

Note 1: Unimplemented, read as '1'.

| ΜΟνωι            | Move W to INDFn                                                                                                                                                                                                                                                                                                                                                                                        |

|------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Syntax:          | [ <i>label</i> ] MOVWI ++FSRn<br>[ <i>label</i> ] MOVWIFSRn<br>[ <i>label</i> ] MOVWI FSRn++<br>[ <i>label</i> ] MOVWI FSRn<br>[ <i>label</i> ] MOVWI k[FSRn]                                                                                                                                                                                                                                          |

| Operands:        | $n \in [0,1]$<br>mm $\in [00,01, 10, 11]$<br>-32 $\leq k \leq 31$                                                                                                                                                                                                                                                                                                                                      |

| Operation:       | $\label{eq:W} \begin{split} & W \rightarrow \text{INDFn} \\ & \text{Effective address is determined by} \\ & \text{FSR + 1 (preincrement)} \\ & \text{FSR - 1 (predecrement)} \\ & \text{FSR + k (relative offset)} \\ & \text{After the Move, the FSR value will be} \\ & \text{either:} \\ & \text{FSR + 1 (all increments)} \\ & \text{FSR - 1 (all decrements)} \\ & \text{Unchanged} \end{split}$ |

| Status Affected: | None                                                                                                                                                                                                                                                                                                                                                                                                   |

| Mode          | Syntax | mm |

|---------------|--------|----|

| Preincrement  | ++FSRn | 00 |

| Predecrement  | FSRn   | 01 |

| Postincrement | FSRn++ | 10 |

| Postdecrement | FSRn   | 11 |

Description:

This instruction is used to move data between W and one of the indirect registers (INDFn). Before/after this move, the pointer (FSRn) is updated by pre/post incrementing/decrementing it.

**Note:** The INDFn registers are not physical registers. Any instruction that accesses an INDFn register actually accesses the register at the address specified by the FSRn.

FSRn is limited to the range 0000h -FFFFh. Incrementing/decrementing it beyond these bounds will cause it to wrap-around.

The increment/decrement operation on FSRn WILL NOT affect any Status bits.

| NOP              | No Operation  |

|------------------|---------------|

| Syntax:          | [label] NOP   |

| Operands:        | None          |

| Operation:       | No operation  |

| Status Affected: | None          |

| Description:     | No operation. |

| Words:           | 1             |

| Cycles:          | 1             |

| Example:         | NOP           |

| OPTION           | Load OPTION_REG Register<br>with W                   |  |  |

|------------------|------------------------------------------------------|--|--|

| Syntax:          | [label] OPTION                                       |  |  |

| Operands:        | None                                                 |  |  |

| Operation:       | $(W) \to OPTION\_REG$                                |  |  |

| Status Affected: | None                                                 |  |  |

| Description:     | Move data from W register to<br>OPTION_REG register. |  |  |

| RESET            | Software Reset                                                                   |

|------------------|----------------------------------------------------------------------------------|

| Syntax:          | [label] RESET                                                                    |

| Operands:        | None                                                                             |

| Operation:       | Execute a device Reset. Resets the<br>nRI flag of the PCON register.             |

| Status Affected: | None                                                                             |

| Description:     | This instruction provides a way to<br>execute a hardware Reset by soft-<br>ware. |

# 28.3 DC Characteristics

## TABLE 28-1: SUPPLY VOLTAGE

| PIC16LF1503             |        |                                                                                  | Standard Operating Conditions (unless otherwise stated) |      |                      |        |                                                                                                                                                                                                                                                                                      |  |

|-------------------------|--------|----------------------------------------------------------------------------------|---------------------------------------------------------|------|----------------------|--------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| PIC16F1                 | 503    |                                                                                  |                                                         |      |                      |        |                                                                                                                                                                                                                                                                                      |  |

| Param.<br>No.           | Sym.   | Characteristic                                                                   | Min.                                                    | Тур† | Max.                 | Units  | Conditions                                                                                                                                                                                                                                                                           |  |

| D001 VDD Supply Voltage |        |                                                                                  |                                                         |      |                      |        |                                                                                                                                                                                                                                                                                      |  |

|                         |        |                                                                                  | VDDMIN<br>1.8<br>2.5                                    |      | VDDMAX<br>3.6<br>3.6 | V<br>V | Fosc ≤ 16 MHz<br>Fosc ≤ 20 MHz                                                                                                                                                                                                                                                       |  |

| D001                    |        |                                                                                  | 2.3<br>2.5                                              |      | 5.5<br>5.5           | V<br>V | Fosc ≤ 16 MHz<br>Fosc ≤ 20 MHz                                                                                                                                                                                                                                                       |  |

| D002*                   | Vdr    | RAM Data Retention Voltage <sup>(1)</sup>                                        |                                                         |      |                      |        |                                                                                                                                                                                                                                                                                      |  |

|                         |        |                                                                                  | 1.5                                                     | _    | —                    | V      | Device in Sleep mode                                                                                                                                                                                                                                                                 |  |

| D002*                   |        |                                                                                  | 1.7                                                     | _    | —                    | V      | Device in Sleep mode                                                                                                                                                                                                                                                                 |  |

| D002A*                  | VPOR   | Power-on Reset Release Voltage <sup>(2)</sup>                                    |                                                         |      |                      |        |                                                                                                                                                                                                                                                                                      |  |

|                         |        |                                                                                  | —                                                       | 1.6  | —                    | V      |                                                                                                                                                                                                                                                                                      |  |

| D002A*                  |        |                                                                                  | _                                                       | 1.6  | _                    | V      |                                                                                                                                                                                                                                                                                      |  |

| D002B*                  | VPORR* | Power-on Reset Rearm Voltage <sup>(2)</sup>                                      |                                                         |      |                      |        |                                                                                                                                                                                                                                                                                      |  |

|                         |        |                                                                                  | _                                                       | 0.8  | —                    | V      |                                                                                                                                                                                                                                                                                      |  |

| D002B*                  |        |                                                                                  | _                                                       | 1.5  | _                    | V      |                                                                                                                                                                                                                                                                                      |  |

| D003                    | VFVR   | Fixed Voltage Reference Voltage                                                  |                                                         |      |                      |        |                                                                                                                                                                                                                                                                                      |  |

|                         |        | 1x gain (1.024V nominal)<br>2x gain (2.048V nominal)<br>4x gain (4.096V nominal) | -4<br>-3                                                | _    | +4<br>+7             | %<br>% | $ \begin{array}{l} \mbox{VDD} \geq 2.5 \mbox{V}, -40 \mbox{°C} \leq \mbox{Ta} \leq +85 \mbox{°C} \\ \mbox{VDD} \geq 2.5 \mbox{V}, -40 \mbox{°C} \leq \mbox{Ta} \leq +85 \mbox{°C} \\ \mbox{VDD} \geq 4.75 \mbox{V}, -40 \mbox{°C} \leq \mbox{Ta} \leq +85 \mbox{°C} \\ \end{array} $ |  |

| D004*                   | SVDD   | VDD Rise Rate <sup>(2)</sup>                                                     | 0.05                                                    |      | —                    | V/ms   | Ensures that the Power-on Reset signal is released properly.                                                                                                                                                                                                                         |  |

\* These parameters are characterized but not tested.

† Data in "Typ" column is at 3.0V, 25°C unless otherwise stated. These parameters are for design guidance only and are not tested.

Note 1: This is the limit to which VDD can be lowered in Sleep mode without losing RAM data.

2: See Figure 28-3, POR and POR REARM with Slow Rising VDD.

### TABLE 28-4: I/O PORTS

Standard Operating Conditions (unless otherwise stated)

| Param.<br>No. | Sym.      | Characteristic                       | Min.              | Тур†     | Max.     | Units                                                   | Conditions                                                                 |

|---------------|-----------|--------------------------------------|-------------------|----------|----------|---------------------------------------------------------|----------------------------------------------------------------------------|

|               | VIL       | Input Low Voltage                    |                   |          |          |                                                         | ·                                                                          |

|               |           | I/O PORT:                            |                   |          |          |                                                         |                                                                            |

| D030          |           | with TTL buffer                      | —                 | _        | 0.8      | V                                                       | $4.5V \leq V\text{DD} \leq 5.5V$                                           |

| D030A         |           |                                      | —                 | _        | 0.15 VDD | V                                                       | $1.8V \le V\text{DD} \le 4.5V$                                             |

| D031          |           | with Schmitt Trigger buffer          | —                 | _        | 0.2 Vdd  | V                                                       | $2.0V \le V\text{DD} \le 5.5V$                                             |

|               |           | with I <sup>2</sup> C™ levels        | —                 | _        | 0.3 Vdd  | V                                                       |                                                                            |

|               |           | with SMbus levels                    | —                 | _        | 0.8      | V                                                       | $2.7V \le V\text{DD} \le 5.5V$                                             |

| D032          |           | MCLR                                 | —                 | _        | 0.2 Vdd  | V                                                       |                                                                            |

|               | VIH       | Input High Voltage                   |                   |          |          |                                                         |                                                                            |

|               |           | I/O PORT:                            |                   |          |          |                                                         |                                                                            |

| D040          |           | with TTL buffer                      | 2.0               | _        | _        | V                                                       | $4.5V \leq V\text{DD} \leq 5.5V$                                           |

| D040A         |           |                                      | 0.25 VDD +<br>0.8 | —        | -        | V                                                       | $1.8V \le VDD \le 4.5V$                                                    |

| D041          |           | with Schmitt Trigger buffer          | 0.8 VDD           | _        | —        | V                                                       | $2.0V \leq V\text{DD} \leq 5.5V$                                           |

|               |           | with I <sup>2</sup> C™ levels        | 0.7 Vdd           |          | —        | V                                                       |                                                                            |

|               |           | with SMbus levels                    | 2.1               |          | —        | V                                                       | $2.7V \le V\text{DD} \le 5.5V$                                             |

| D042          |           | MCLR                                 | 0.8 VDD           |          | —        | V                                                       |                                                                            |

|               | lil       | Input Leakage Current <sup>(1)</sup> |                   |          |          |                                                         |                                                                            |

| D060          | I/O Ports | —                                    | ± 5               | ± 125    | nA       | $Vss \le VPIN \le VDD$ ,<br>Pin at high-impedance, 85°C |                                                                            |

|               |           |                                      | —                 | ± 5      | ± 1000   | nA                                                      | Vss $\leq$ VPIN $\leq$ VDD, Pin at high-impedance, 125°C                   |

| D061          |           | MCLR <sup>(2)</sup>                  | —                 | ± 50     | ± 200    | nA                                                      | VSS $\leq$ VPIN $\leq$ VDD, Pin at high-impedance, 85°C                    |

|               | IPUR      | Weak Pull-up Current                 |                   |          |          |                                                         |                                                                            |

| D070*         |           |                                      | 25                | 100      | 200      | μΑ                                                      | VDD = 3.3V, VPIN = VSS                                                     |

|               |           |                                      | 25                | 140      | 300      | μΑ                                                      | VDD = 5.0V, VPIN = VSS                                                     |

|               | Vol       | Output Low Voltage                   |                   |          |          |                                                         |                                                                            |

| D080          |           | I/O Ports                            | _                 | _        | 0.6      | V                                                       | IOL = 8 mA, VDD = 5V<br>IOL = 6 mA, VDD = 3.3V<br>IOL = 1.8 mA, VDD = 1.8V |

|               | Voн       | Output High Voltage                  |                   |          | •        | •                                                       |                                                                            |

| D090          |           | I/O Ports                            | Vdd - 0.7         | _        | _        | V                                                       | IOH = 3.5 mA, VDD = 5V<br>IOH = 3 mA, VDD = 3.3V<br>IOH = 1 mA, VDD = 1.8V |

|               |           | Capacitive Loading Specification     | tions on Out      | out Pins |          |                                                         |                                                                            |

| D101A*        | CIO       | All I/O pins                         | _                 | _        | 50       | pF                                                      |                                                                            |

These parameters are characterized but not tested.

Data in "Typ" column is at 3.0V, 25°C unless otherwise stated. These parameters are for design guidance only and are † not tested.

**Note 1:** Negative current is defined as current sourced by the pin.

2: The leakage current on the MCLR pin is strongly dependent on the applied voltage level. The specified levels represent normal operating conditions. Higher leakage current may be measured at different input voltages.

# 28.4 AC Characteristics

Timing Parameter Symbology has been created with one of the following formats:

- 1. TppS2ppS

- 2. TppS

| Т      |                                       |     |                |

|--------|---------------------------------------|-----|----------------|

| F      | Frequency                             | Т   | Time           |

| Lowerc | case letters (pp) and their meanings: |     |                |

| рр     |                                       |     |                |

| сс     | CCP1                                  | osc | CLKIN          |

| ck     | CLKOUT                                | rd  | RD             |

| CS     | CS                                    | rw  | RD or WR       |

| di     | SDIx                                  | sc  | SCKx           |

| do     | SDO                                   | SS  | SS             |

| dt     | Data in                               | tO  | TOCKI          |

| io     | I/O PORT                              | t1  | T1CKI          |

| mc     | MCLR                                  | wr  | WR             |

| Upperc | case letters and their meanings:      |     |                |

| S      |                                       |     |                |

| F      | Fall                                  | Р   | Period         |

| Н      | High                                  | R   | Rise           |

| I      | Invalid (High-impedance)              | V   | Valid          |

| L      | Low                                   | Z   | High-impedance |

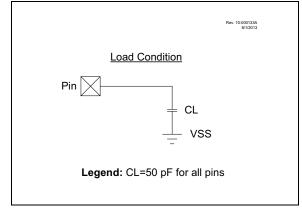

### FIGURE 28-4: LOAD CONDITIONS

## I<sup>2</sup>C BUS DATA REQUIREMENTS

| Param.<br>No.  | Symbol           | Characte              | eristic      | Min.       | Max. | Units                                      | Conditions                                  |

|----------------|------------------|-----------------------|--------------|------------|------|--------------------------------------------|---------------------------------------------|

| SP100*         | Тнідн            | Clock high time       | 100 kHz mode | 4.0        | _    | μS                                         | Device must operate at a minimum of 1.5 MHz |

|                |                  |                       | 400 kHz mode | 0.6        |      | μS                                         | Device must operate at a minimum of 10 MHz  |

|                |                  |                       | SSP module   | 1.5TCY     | _    |                                            |                                             |

| SP101*         | TLOW             | Clock low time        | 100 kHz mode | 4.7        |      | μS                                         | Device must operate at a minimum of 1.5 MHz |

|                |                  | 400 kHz mode          | 1.3          | _          | μS   | Device must operate at a minimum of 10 MHz |                                             |

|                |                  |                       | SSP module   | 1.5TCY     | _    |                                            |                                             |

| SP102* TR      | TR               | SDA and SCL rise      | 100 kHz mode | —          | 1000 | ns                                         |                                             |

|                |                  | time                  | 400 kHz mode | 20 + 0.1Св | 300  | ns                                         | CB is specified to be from 10-400 pF        |

| SP103* TF      | SDA and SCL fall | 100 kHz mode          | —            | 250        | ns   |                                            |                                             |

|                |                  | time                  | 400 kHz mode | 20 + 0.1Св | 250  | ns                                         | CB is specified to be from 10-400 pF        |

| SP106*         | THD:DAT          | Data input hold time  | 100 kHz mode | 0          | _    | ns                                         |                                             |

|                |                  |                       | 400 kHz mode | 0          | 0.9  | μs                                         |                                             |

| SP107* TSU:DAT | TSU:DAT          | Data input setup      | 100 kHz mode | 250        | _    | ns                                         | (Note 2)                                    |

|                |                  | time                  | 400 kHz mode | 100        | _    | ns                                         |                                             |

| SP109*         | ΤΑΑ              | Output valid from     | 100 kHz mode | —          | 3500 | ns                                         | (Note 1)                                    |

|                |                  | clock                 | 400 kHz mode | —          | _    | ns                                         |                                             |

| SP110*         | TBUF             | Bus free time         | 100 kHz mode | 4.7        | _    | μS                                         | Time the bus must be free                   |

|                |                  |                       | 400 kHz mode | 1.3        |      | μS                                         | before a new transmission<br>can start      |

| SP111          | Св               | Bus capacitive loadir | ng           |            | 400  | pF                                         |                                             |

\* These parameters are characterized but not tested.

**Note 1:** As a transmitter, the device must provide this internal minimum delay time to bridge the undefined region (min. 300 ns) of the falling edge of SCL to avoid unintended generation of Start or Stop conditions.

2: A Fast mode (400 kHz) I<sup>2</sup>C bus device can be used in a Standard mode (100 kHz) I<sup>2</sup>C bus system, but the requirement Tsu:DAT ≥ 250 ns must then be met. This will automatically be the case if the device does not stretch the low period of the SCL signal. If such a device does stretch the low period of the SCL signal, it must output the next data bit to the SDA line TR max. + Tsu:DAT = 1000 + 250 = 1250 ns (according to the Standard mode I<sup>2</sup>C bus specification), before the SCL line is released.

# 31.1 Package Marking Information (Continued)

16-Lead QFN (3x3x0.9 mm)

16-Lead UQFN (3x3x0.5 mm)

Example

Example

# TABLE 31-1:16-LEAD 3x3x0.9 QFN (MG)TOP MARKING

| Part Number         | Marking |

|---------------------|---------|

| PIC16F1503(T)-I/MG  | MGA     |

| PIC16F1503(T)-E/MG  | MGB     |

| PIC16LF1503(T)-I/MG | MGC     |

| PIC16LF1503(T)-E/MG | MGD     |

### TABLE 31-2: 16-LEAD 3x3x0.5 UQFN (MV) TOP MARKING

| Part Number         | Marking |

|---------------------|---------|

| PIC16F1503(T)-I/NL  | AAB     |

| PIC16F1503(T)-E/NL  | AAA     |

| PIC16LF1503(T)-I/NL | AAD     |

| PIC16LF1503(T)-E/NL | AAC     |