### Microchip Technology - PIC16F1503-E/P Datasheet

# E·XFL

#### Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

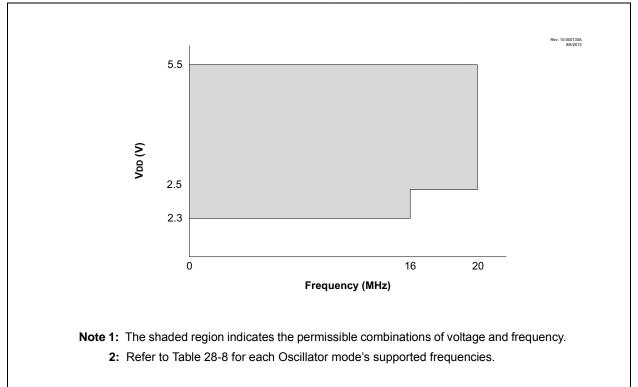

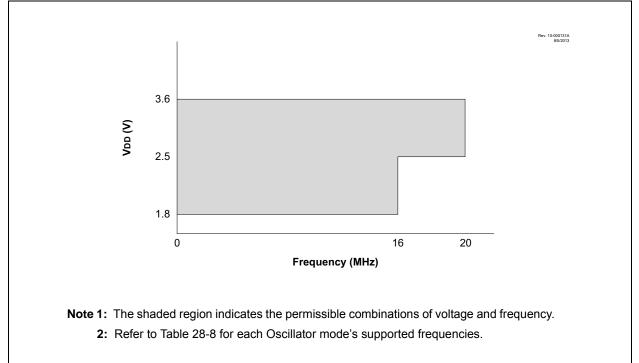

| Product Status             | Active                                                                   |

|----------------------------|--------------------------------------------------------------------------|

| Core Processor             | PIC                                                                      |

| Core Size                  | 8-Bit                                                                    |

| Speed                      | 20MHz                                                                    |

| Connectivity               | I <sup>2</sup> C, SPI                                                    |

| Peripherals                | Brown-out Detect/Reset, POR, PWM, WDT                                    |

| Number of I/O              | 11                                                                       |

| Program Memory Size        | 3.5KB (2K x 14)                                                          |

| Program Memory Type        | FLASH                                                                    |

| EEPROM Size                | -                                                                        |

| RAM Size                   | 128 x 8                                                                  |

| Voltage - Supply (Vcc/Vdd) | 2.3V ~ 5.5V                                                              |

| Data Converters            | A/D 8x10b                                                                |

| Oscillator Type            | Internal                                                                 |

| Operating Temperature      | -40°C ~ 125°C (TA)                                                       |

| Mounting Type              | Through Hole                                                             |

| Package / Case             | 14-DIP (0.300", 7.62mm)                                                  |

| Supplier Device Package    | 14-PDIP                                                                  |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic16f1503-e-p |

|                            |                                                                          |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

## 1.0 DEVICE OVERVIEW

The block diagram of these devices are shown in Figure 1-1, the available peripherals are shown in Table 1-1, and the pinout descriptions are shown in Table 1-2.

TABLE 1-1: DEVICE PERIPHERAL SUMMARY

| Peripheral                                                               | PIC12(L)F1501 | PIC16(L)F1503 | PIC16(L)F1507 | PIC16(L)F1508 | PIC16(L)F1509 |   |  |

|--------------------------------------------------------------------------|---------------|---------------|---------------|---------------|---------------|---|--|

| Analog-to-Digital Converter (A                                           | -             | •             | •             | •             | •             | • |  |

| Complementary Wave Generation                                            |               | •             | •             | •             | •             | • |  |

| Digital-to-Analog Converter (I                                           | DAC)          | •             | ٠             |               | •             | • |  |

| Enhanced Universal<br>Synchronous/Asynchronous  <br>Transmitter (EUSART) | Receiver/     |               |               |               | •             | • |  |

| Fixed Voltage Reference (FV                                              | R)            | •             | •             | •             | •             | • |  |

| Numerically Controlled Oscilla                                           | ator (NCO)    | ٠             | ٠             | •             | ٠             | • |  |

| Temperature Indicator                                                    | ٠             | ٠             | •             | ٠             | •             |   |  |

| Comparators                                                              | Comparators   |               |               |               |               |   |  |

|                                                                          | C1            | •             | ٠             |               | •             | • |  |

|                                                                          | C2            |               | •             |               | •             | • |  |

| Configurable Logic Cell (CLC                                             | ;)            |               |               |               |               |   |  |

|                                                                          | CLC1          | •             | •             | •             | •             | • |  |

|                                                                          | CLC2          | •             | ٠             | •             | •             | • |  |

|                                                                          | CLC3          |               |               |               | •             | • |  |

|                                                                          | CLC4          |               |               |               | •             | • |  |

| Master Synchronous Serial P                                              |               |               |               |               |               |   |  |

|                                                                          | MSSP1         |               | ٠             |               | •             | • |  |

| PWM Modules                                                              | 1             |               |               |               |               |   |  |

|                                                                          | PWM1          | •             | •             | •             | •             | • |  |

|                                                                          | PWM2          | •             | ٠             | •             | ٠             | • |  |

|                                                                          | PWM3          | •             | •             | •             | •             | • |  |

|                                                                          | PWM4          |               |               |               |               |   |  |

| Timers                                                                   |               |               |               |               |               |   |  |

|                                                                          | Timer0        | •             | •             | •             | •             | • |  |

|                                                                          | Timer1        | •             | •             | •             | •             | • |  |

|                                                                          | Timer2        | •             | •             | •             | •             | • |  |

### 3.3.2 SPECIAL FUNCTION REGISTER

The Special Function Registers are registers used by the application to control the desired operation of peripheral functions in the device. The Special Function Registers occupy the 20 bytes after the core registers of every data memory bank (addresses x0Ch/x8Ch through x1Fh/x9Fh). The registers associated with the operation of the peripherals are described in the appropriate peripheral chapter of this data sheet.

### 3.3.3 GENERAL PURPOSE RAM

There are up to 80 bytes of GPR in each data memory bank. The Special Function Registers occupy the 20 bytes after the core registers of every data memory bank (addresses x0Ch/x8Ch through x1Fh/x9Fh).

### 3.3.3.1 Linear Access to GPR

The general purpose RAM can be accessed in a non-banked method via the FSRs. This can simplify access to large memory structures. See **Section 3.6.2** "Linear Data Memory" for more information.

### 3.3.4 COMMON RAM

There are 16 bytes of common RAM accessible from all banks.

### FIGURE 3-2: BANKED MEMORY PARTITIONING

|                   | Rev. 10-00<br>7/3                             |

|-------------------|-----------------------------------------------|

| 7-bit Bank Offset | Memory Region                                 |

| 00h               | Core Registers                                |

| 0Bh               | (12 bytes)                                    |

| 0Ch<br>1Fh        | Special Function Registers (20 bytes maximum) |

| 20h               | General Purpose RAM                           |

| 6Eh               | (80 bytes maximum)                            |

| 70h               | Common RAM                                    |

| 7Fh               | (16 bytes)                                    |

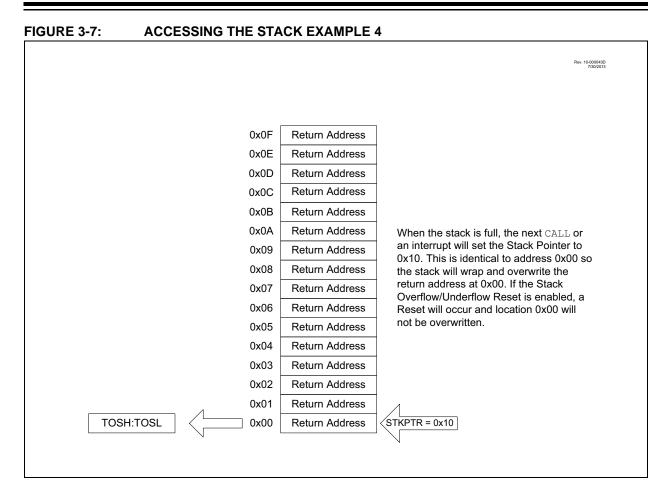

### 3.5.2 OVERFLOW/UNDERFLOW RESET

If the STVREN bit in Configuration Words is programmed to '1', the device will be reset if the stack is PUSHed beyond the sixteenth level or POPed beyond the first level, setting the appropriate bits (STKOVF or STKUNF, respectively) in the PCON register.

### 3.6 Indirect Addressing

The INDFn registers are not physical registers. Any instruction that accesses an INDFn register actually accesses the register at the address specified by the File Select Registers (FSR). If the FSRn address specifies one of the two INDFn registers, the read will return '0' and the write will not occur (though Status bits may be affected). The FSRn register value is created by the pair FSRnH and FSRnL.

The FSR registers form a 16-bit address that allows an addressing space with 65536 locations. These locations are divided into three memory regions:

- Traditional Data Memory

- Linear Data Memory

- Program Flash Memory

# 4.0 DEVICE CONFIGURATION

Device configuration consists of Configuration Words, Code Protection and Device ID.

### 4.1 Configuration Words

There are several Configuration Word bits that allow different oscillator and memory protection options. These are implemented as Configuration Word 1 at 8007h and Configuration Word 2 at 8008h.

Note: The DEBUG bit in Configuration Words is managed automatically by device development tools including debuggers and programmers. For normal device operation, this bit should be maintained as a '1'.

| U-0         | ) U-0                                           | U-0                                       | U-0            | U-0            | U-0              | R/W-0/0          | R/W-0/0      |  |

|-------------|-------------------------------------------------|-------------------------------------------|----------------|----------------|------------------|------------------|--------------|--|

| _           | —                                               | —                                         | _              | _              | —                | CLC2IF           | CLC1IF       |  |

| bit 7       |                                                 |                                           |                |                |                  |                  | bit 0        |  |

|             |                                                 |                                           |                |                |                  |                  |              |  |

| Legend:     |                                                 |                                           |                |                |                  |                  |              |  |

| R = Rea     | dable bit                                       | W = Writable                              | bit            | U = Unimpler   | mented bit, read | as '0'           |              |  |

| u = Bit is  | unchanged                                       | x = Bit is unkr                           | nown           | -n/n = Value a | at POR and BOI   | R/Value at all c | other Resets |  |

| '1' = Bit i | s set                                           | '0' = Bit is cle                          | ared           |                |                  |                  |              |  |

|             |                                                 |                                           |                |                |                  |                  |              |  |

| bit 7-2     | Unimpleme                                       | ented: Read as '                          | 0'             |                |                  |                  |              |  |

| bit 1       | CLC2IF: Co                                      | onfigurable Logic                         | Block 2 Interr | upt Flag bit   |                  |                  |              |  |

|             |                                                 | ot is pending                             |                |                |                  |                  |              |  |

|             | •                                               | ot is not pending                         |                |                |                  |                  |              |  |

| bit 0       |                                                 | onfigurable Logic                         | Block 1 Interr | upt Flag bit   |                  |                  |              |  |

|             |                                                 | t is pending                              |                |                |                  |                  |              |  |

|             | 0 = Interrup                                    | ot is not pending                         |                |                |                  |                  |              |  |

|             |                                                 |                                           |                |                |                  |                  |              |  |

| Note:       |                                                 |                                           |                |                |                  |                  |              |  |

|             |                                                 | , regardless of the<br>g enable bit or th |                |                |                  |                  |              |  |

|             |                                                 | of the INTCON                             |                |                |                  |                  |              |  |

| 1           | User software                                   |                                           | -              |                |                  |                  |              |  |

|             | appropriate interrupt flag hits are clear prior |                                           |                |                |                  |                  |              |  |

### REGISTER 7-7: PIR3: PERIPHERAL INTERRUPT REQUEST REGISTER 3

appropriate interrupt flag bits are clear prior to enabling an interrupt.

## 9.6 Register Definitions: Watchdog Timer Control

| U-0           | U-0                                 | R/W-0/0                                                        | R/W-1/1       | R/W-0/0                   | R/W-1/1        | R/W-1/1          | R/W-0/0      |

|---------------|-------------------------------------|----------------------------------------------------------------|---------------|---------------------------|----------------|------------------|--------------|

| —             | —                                   |                                                                |               | WDTPS<4:0>                |                |                  | SWDTEN       |

| it 7          |                                     |                                                                |               |                           |                |                  | bit (        |

| egend:        |                                     |                                                                |               |                           |                |                  |              |

| R = Readab    | ole bit                             | W = Writable                                                   | bit           | U = Unimpleme             | ented bit, rea | d as '0'         |              |

| u = Bit is un | changed                             | x = Bit is unkr                                                | iown          | -n/n = Value at           | POR and BC     | R/Value at all o | other Resets |

| 1' = Bit is s | et                                  | '0' = Bit is clea                                              | ared          |                           |                |                  |              |

| oit 7-6       | Unimpleme                           | nted: Read as '                                                | )'            |                           |                |                  |              |

| oit 5-1       | WDTPS<4:0                           | >: Watchdog Tir                                                | mer Period S  | elect bits <sup>(1)</sup> |                |                  |              |

|               | Bit Value =                         | Prescale Rate                                                  |               |                           |                |                  |              |

|               | 11111 = R                           | eserved. Results                                               | s in minimum  | interval (1:32)           |                |                  |              |

|               | •                                   |                                                                |               |                           |                |                  |              |

|               | •                                   |                                                                |               |                           |                |                  |              |

|               | •<br>10011 = R                      | eserved. Results                                               | s in minimum  | interval (1:32)           |                |                  |              |

|               | 10010 = <b>1</b> ·                  | 8388608 (2 <sup>23</sup> ) (I                                  | nterval 256s  | nominal)                  |                |                  |              |

|               |                                     | 4194304 (2 <sup>22</sup> ) (I                                  |               |                           |                |                  |              |

|               | 10000 = <b>1</b> :                  | 2097152 (2 <sup>21</sup> ) (I                                  | nterval 64s r | nominal)                  |                |                  |              |

|               | 01111 = <b>1</b> :                  | 1048576 (2 <sup>20</sup> ) (I                                  | nterval 32s r | nominal)                  |                |                  |              |

|               | 01110 = 1:                          | 524288 (2 <sup>19</sup> ) (In                                  | terval 16s no | ominal)                   |                |                  |              |

|               |                                     | 262144 (2 <sup>18</sup> ) (In<br>131072 (2 <sup>17</sup> ) (In |               |                           |                |                  |              |

|               |                                     | 65536 (Interval                                                |               | ,                         |                |                  |              |

|               |                                     | 32768 (Interval                                                |               |                           |                |                  |              |

|               |                                     | 16384 (Interval                                                | ,             | nal)                      |                |                  |              |

|               |                                     | 8192 (Interval 2                                               |               |                           |                |                  |              |

|               |                                     | 4096 (Interval 12                                              |               | ,                         |                |                  |              |

|               |                                     | 2048 (Interval 64                                              |               |                           |                |                  |              |

|               |                                     | 1024 (Interval 32<br>512 (Interval 16                          |               | ,                         |                |                  |              |

|               |                                     | 256 (Interval 8 n                                              |               |                           |                |                  |              |

|               |                                     | 128 (Interval 4 n                                              |               |                           |                |                  |              |

|               |                                     | 64 (Interval 2 m                                               | ,             |                           |                |                  |              |

|               | 00000 = 1:                          | 32 (Interval 1 m                                               | s nominal)    |                           |                |                  |              |

| oit O         | SWDTEN: S                           | oftware Enable/                                                | Disable for V | Vatchdog Timer b          | it             |                  |              |

|               | <u>If WDTE&lt;1:</u>                |                                                                |               |                           |                |                  |              |

|               | This bit is ig                      |                                                                |               |                           |                |                  |              |

|               | If WDTE<1:0                         |                                                                |               |                           |                |                  |              |

|               | 1 = WDT is<br>0 = WDT is            |                                                                |               |                           |                |                  |              |

|               | 0 = WDT IS<br><u>If WDTE&lt;1:(</u> |                                                                |               |                           |                |                  |              |

|               | This bit is ig                      |                                                                |               |                           |                |                  |              |

### REGISTER 9-1: WDTCON: WATCHDOG TIMER CONTROL REGISTER

### 10.6 Register Definitions: Flash Program Memory Control

### REGISTER 10-1: PMDATL: PROGRAM MEMORY DATA LOW BYTE REGISTER

| R/W-x/u             | R/W-x/u | R/W-x/u                                             | R/W-x/u                                                 | R/W-x/u | R/W-x/u | R/W-x/u | R/W-x/u |

|---------------------|---------|-----------------------------------------------------|---------------------------------------------------------|---------|---------|---------|---------|

|                     |         |                                                     | PMDA                                                    | T<7:0>  |         |         |         |

| bit 7               |         |                                                     |                                                         |         |         |         | bit 0   |

|                     |         |                                                     |                                                         |         |         |         |         |

| Legend:             |         |                                                     |                                                         |         |         |         |         |

| R = Readable bit    |         | W = Writable bit U = Unimplemented bit, read as '0' |                                                         |         | ,       |         |         |

| u = Bit is unchange | ed      | x = Bit is unknowr                                  | n -n/n = Value at POR and BOR/Value at all other Resets |         |         | ets     |         |

| '1' = Bit is set    |         | '0' = Bit is cleared                                |                                                         |         |         |         |         |

bit 7-0

PMDAT<7:0>: Read/write value for Least Significant bits of program memory

### REGISTER 10-2: PMDATH: PROGRAM MEMORY DATA HIGH BYTE REGISTER

| U-0   | U-0 | R/W-x/u | R/W-x/u     | R/W-x/u | R/W-x/u | R/W-x/u | R/W-x/u |

|-------|-----|---------|-------------|---------|---------|---------|---------|

| _     | —   |         | PMDAT<13:8> |         |         |         |         |

| bit 7 |     |         |             |         |         |         | bit 0   |

| Legend:              |                      |                                                       |

|----------------------|----------------------|-------------------------------------------------------|

| R = Readable bit     | W = Writable bit     | U = Unimplemented bit, read as '0'                    |

| u = Bit is unchanged | x = Bit is unknown   | -n/n = Value at POR and BOR/Value at all other Resets |

| '1' = Bit is set     | '0' = Bit is cleared |                                                       |

### bit 7-6 Unimplemented: Read as '0'

bit 5-0 PMDAT<13:8>: Read/write value for Most Significant bits of program memory

### REGISTER 10-3: PMADRL: PROGRAM MEMORY ADDRESS LOW BYTE REGISTER

| R/W-0/0    | R/W-0/0 | R/W-0/0 | R/W-0/0 | R/W-0/0 | R/W-0/0 | R/W-0/0 | R/W-0/0 |  |

|------------|---------|---------|---------|---------|---------|---------|---------|--|

| PMADR<7:0> |         |         |         |         |         |         |         |  |

| bit 7      |         |         |         |         |         |         | bit 0   |  |

|            |         |         |         |         |         |         |         |  |

| Legend:              |                      |                                                       |

|----------------------|----------------------|-------------------------------------------------------|

| R = Readable bit     | W = Writable bit     | U = Unimplemented bit, read as '0'                    |

| u = Bit is unchanged | x = Bit is unknown   | -n/n = Value at POR and BOR/Value at all other Resets |

| '1' = Bit is set     | '0' = Bit is cleared |                                                       |

bit 7-0

PMADR<7:0>: Specifies the Least Significant bits for program memory address

### REGISTER 10-4: PMADRH: PROGRAM MEMORY ADDRESS HIGH BYTE REGISTER

| U-1   | R/W-0/0 | R/W-0/0     | R/W-0/0 | R/W-0/0 | R/W-0/0 | R/W-0/0 | R/W-0/0 |  |

|-------|---------|-------------|---------|---------|---------|---------|---------|--|

| (1)   |         | PMADR<14:8> |         |         |         |         |         |  |

| bit 7 |         |             |         |         |         |         | bit 0   |  |

| Legend:              |                      |                                                       |

|----------------------|----------------------|-------------------------------------------------------|

| R = Readable bit     | W = Writable bit     | U = Unimplemented bit, read as '0'                    |

| u = Bit is unchanged | x = Bit is unknown   | -n/n = Value at POR and BOR/Value at all other Resets |

| '1' = Bit is set     | '0' = Bit is cleared |                                                       |

bit 7 Unimplemented: Read as '1'

bit 6-0 PMADR<14:8>: Specifies the Most Significant bits for program memory address

Note 1: Unimplemented, read as '1'.

### 11.4 Register Definitions: PORTA

### REGISTER 11-2: PORTA: PORTA REGISTER

| U-0                                   | U-0   | R/W-x/x            | R/W-x/x | R-x/x                                                 | R/W-x/x          | R/W-x/x  | R/W-x/x |  |

|---------------------------------------|-------|--------------------|---------|-------------------------------------------------------|------------------|----------|---------|--|

|                                       | —     | RA5                | RA4     | RA3                                                   | RA2              | RA1      | RA0     |  |

| bit 7                                 |       |                    |         |                                                       |                  |          | bit 0   |  |

|                                       |       |                    |         |                                                       |                  |          |         |  |

| Legend:                               |       |                    |         |                                                       |                  |          |         |  |

| R = Readable b                        | bit   | W = Writable       | bit     | U = Unimple                                           | mented bit, read | l as '0' |         |  |

| u = Bit is uncha                      | inged | x = Bit is unknown |         | -n/n = Value at POR and BOR/Value at all other Resets |                  |          |         |  |

| '1' = Bit is set '0' = Bit is cleared |       |                    | ared    |                                                       |                  |          |         |  |

| bit 7-6 | Unimplemented: Read as '0' |

|---------|----------------------------|

|---------|----------------------------|

bit 5-0 RA<5:0>: PORTA I/O Value bits<sup>(1)</sup>

1 = Port pin is <u>></u> Vін

0 = Port pin is <u><</u> Vı∟

**Note 1:** Writes to PORTA are actually written to corresponding LATA register. Reads from PORTA register is return of actual I/O pin values.

### REGISTER 11-3: TRISA: PORTA TRI-STATE REGISTER

| U-0   | U-0 | R/W-1/1 | R/W-1/1 | U-1  | R/W-1/1 | R/W-1/1 | R/W-1/1 |

|-------|-----|---------|---------|------|---------|---------|---------|

| —     | —   | TRISA5  | TRISA4  | _(1) | TRISA2  | TRISA1  | TRISA0  |

| bit 7 |     |         |         |      |         |         | bit 0   |

| Legend:              |                      |                                                       |

|----------------------|----------------------|-------------------------------------------------------|

| R = Readable bit     | W = Writable bit     | U = Unimplemented bit, read as '0'                    |

| u = Bit is unchanged | x = Bit is unknown   | -n/n = Value at POR and BOR/Value at all other Resets |

| '1' = Bit is set     | '0' = Bit is cleared |                                                       |

| bit 7-6 | Unimplemented: Read as '0'                                                                                                                         |

|---------|----------------------------------------------------------------------------------------------------------------------------------------------------|

| bit 5-4 | <b>TRISA&lt;5:4&gt;:</b> PORTA Tri-State Control bit<br>1 = PORTA pin configured as an input (tri-stated)<br>0 = PORTA pin configured as an output |

| bit 3   | Unimplemented: Read as '1'                                                                                                                         |

| bit 2-0 | <b>TRISA&lt;2:0&gt;:</b> PORTA Tri-State Control bit<br>1 = PORTA pin configured as an input (tri-stated)<br>0 = PORTA pin configured as an output |

Note 1: Unimplemented, read as '1'.

| Name   | Bit 7 | Bit 6 | Bit 5  | Bit 4  | Bit 3  | Bit 2  | Bit 1  | Bit 0  | Register<br>on Page |

|--------|-------|-------|--------|--------|--------|--------|--------|--------|---------------------|

| ANSELA | _     | —     | —      | ANSA4  | —      | ANSA2  | ANSA1  | ANSA0  | 99                  |

| INTCON | GIE   | PEIE  | TMR0IE | INTE   | IOCIE  | TMR0IF | INTF   | IOCIF  | 64                  |

| IOCAF  | _     | _     | IOCAF5 | IOCAF4 | IOCAF3 | IOCAF2 | IOCAF1 | IOCAF0 | 106                 |

| IOCAN  | —     | —     | IOCAN5 | IOCAN4 | IOCAN3 | IOCAN2 | IOCAN1 | IOCAN0 | 106                 |

| IOCAP  | _     | _     | IOCAP5 | IOCAP4 | IOCAP3 | IOCAP2 | IOCAP1 | IOCAP0 | 106                 |

| TRISA  | —     | _     | TRISA5 | TRISA4 | —(1)   | TRISA2 | TRISA1 | TRISA0 | 98                  |

TABLE 12-1: SUMMARY OF REGISTERS ASSOCIATED WITH INTERRUPT-ON-CHANGE

Legend: — = unimplemented location, read as '0'. Shaded cells are not used by interrupt-on-change.

**Note 1:** Unimplemented, read as '1'.

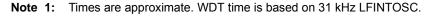

# 18.0 TIMER0 MODULE

The Timer0 module is an 8-bit timer/counter with the following features:

- 8-bit timer/counter register (TMR0)

- 3-bit prescaler (independent of Watchdog Timer)

- Programmable internal or external clock source

- Programmable external clock edge selection

- Interrupt on overflow

- TMR0 can be used to gate Timer1

Figure 18-1 is a block diagram of the Timer0 module.

### 18.1 Timer0 Operation

The Timer0 module can be used as either an 8-bit timer or an 8-bit counter.

### 18.1.1 8-BIT TIMER MODE

The Timer0 module will increment every instruction cycle, if used without a prescaler. 8-bit Timer mode is selected by clearing the TMR0CS bit of the OPTION\_REG register.

When TMR0 is written, the increment is inhibited for two instruction cycles immediately following the write.

| Note: | The value written to the TMR0 register   |  |  |  |  |  |  |  |  |

|-------|------------------------------------------|--|--|--|--|--|--|--|--|

|       | can be adjusted, in order to account for |  |  |  |  |  |  |  |  |

|       | the two instruction cycle delay when     |  |  |  |  |  |  |  |  |

|       | TMR0 is written.                         |  |  |  |  |  |  |  |  |

### FIGURE 18-1: TIMER0 BLOCK DIAGRAM

#### 18.1.2 8-BIT COUNTER MODE

In 8-Bit Counter mode, the Timer0 module will increment on every rising or falling edge of the T0CKI pin.

8-Bit Counter mode using the T0CKI pin is selected by setting the TMR0CS bit in the OPTION\_REG register to '1'.

The rising or falling transition of the incrementing edge for either input source is determined by the TMR0SE bit in the OPTION\_REG register.

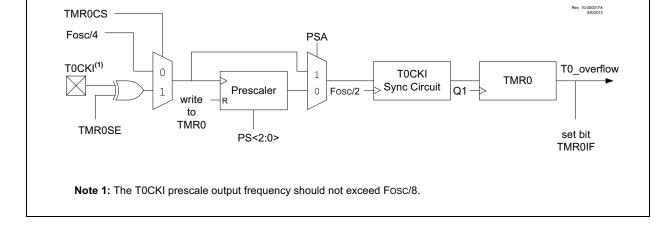

### 21.2 SPI Mode Overview

The Serial Peripheral Interface (SPI) bus is a synchronous serial data communication bus that operates in Full-Duplex mode. Devices communicate in a master/slave environment where the master device initiates the communication. A slave device is controlled through a Chip Select known as Slave Select.

The SPI bus specifies four signal connections:

- Serial Clock (SCKx)

- Serial Data Out (SDOx)

- Serial Data In (SDIx)

- Slave Select (SSx)

Figure 21-1 shows the block diagram of the MSSP module when operating in SPI mode.

The SPI bus operates with a single master device and one or more slave devices. When multiple slave devices are used, an independent Slave Select connection is required from the master device to each slave device.

Figure 21-4 shows a typical connection between a master device and multiple slave devices.

The master selects only one slave at a time. Most slave devices have tri-state outputs so their output signal appears disconnected from the bus when they are not selected.

Transmissions involve two shift registers, eight bits in size, one in the master and one in the slave. With either the master or the slave device, data is always shifted out one bit at a time, with the Most Significant bit (MSb) shifted out first. At the same time, a new Least Significant bit (LSb) is shifted into the same register.

Figure 21-5 shows a typical connection between two processors configured as master and slave devices.

Data is shifted out of both shift registers on the programmed clock edge and latched on the opposite edge of the clock.

The master device transmits information out on its SDOx output pin which is connected to, and received by, the slave's SDIx input pin. The slave device transmits information out on its SDOx output pin, which is connected to, and received by, the master's SDIx input pin.

To begin communication, the master device first sends out the clock signal. Both the master and the slave devices should be configured for the same clock polarity.

The master device starts a transmission by sending out the MSb from its shift register. The slave device reads this bit from that same line and saves it into the LSb position of its shift register. During each SPI clock cycle, a full-duplex data transmission occurs. This means that while the master device is sending out the MSb from its shift register (on its SDOx pin) and the slave device is reading this bit and saving it as the LSb of its shift register, that the slave device is also sending out the MSb from its shift register (on its SDOx pin) and the master device is reading this bit and saving it as the LSb of its shift register.

After eight bits have been shifted out, the master and slave have exchanged register values.

If there is more data to exchange, the shift registers are loaded with new data and the process repeats itself.

Whether the data is meaningful or not (dummy data), depends on the application software. This leads to three scenarios for data transmission:

- Master sends useful data and slave sends dummy data.

- Master sends useful data and slave sends useful data.

- Master sends dummy data and slave sends useful data.

Transmissions may involve any number of clock cycles. When there is no more data to be transmitted, the master stops sending the clock signal and it deselects the slave.

Every slave device connected to the bus that has not been selected through its slave select line must disregard the clock and transmission signals and must not transmit out any data of its own.

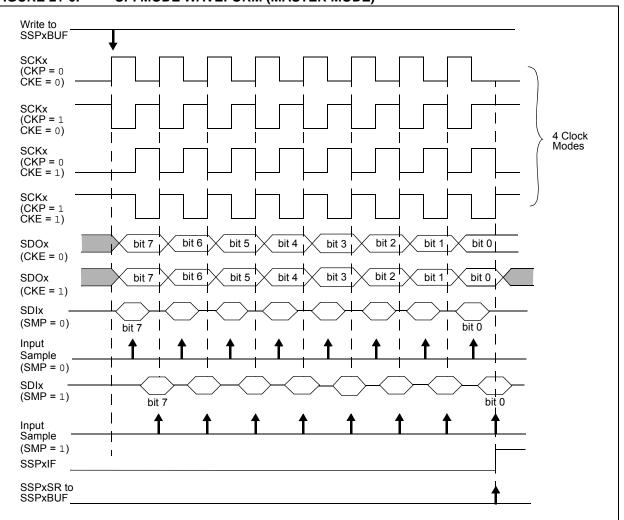

### 21.2.3 SPI MASTER MODE

The master can initiate the data transfer at any time because it controls the SCKx line. The master determines when the slave (Processor 2, Figure 21-5) is to broadcast data by the software protocol.

In Master mode, the data is transmitted/received as soon as the SSPxBUF register is written to. If the SPI is only going to receive, the SDOx output could be disabled (programmed as an input). The SSPxSR register will continue to shift in the signal present on the SDIx pin at the programmed clock rate. As each byte is received, it will be loaded into the SSPxBUF register as if a normal received byte (interrupts and Status bits appropriately set). The clock polarity is selected by appropriately programming the CKP bit of the SSPxCON1 register and the CKE bit of the SSPxSTAT register. This then, would give waveforms for SPI communication as shown in Figure 21-6, Figure 21-8, Figure 21-9 and Figure 21-10, where the MSb is transmitted first. In Master mode, the SPI clock rate (bit rate) is user programmable to be one of the following:

- · Fosc/4 (or Tcy)

- Fosc/16 (or 4 \* Tcy)

- Fosc/64 (or 16 \* Tcy)

- Timer2 output/2

- Fosc/(4 \* (SSPxADD + 1))

Figure 21-6 shows the waveforms for Master mode.

When the CKE bit is set, the SDOx data is valid before there is a clock edge on SCKx. The change of the input sample is shown based on the state of the SMP bit. The time when the SSPxBUF is loaded with the received data is shown.

FIGURE 21-6: SPI MODE WAVEFORM (MASTER MODE)

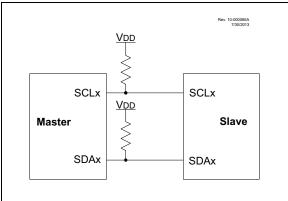

# 21.3 I<sup>2</sup>C MODE OVERVIEW

The Inter-Integrated Circuit Bus  $(I^2C)$  is a multi-master serial data communication bus. Devices communicate in a master/slave environment where the master devices initiate the communication. A slave device is controlled through addressing.

The I<sup>2</sup>C bus specifies two signal connections:

- · Serial Clock (SCLx)

- Serial Data (SDAx)

Figure 21-2 and Figure 21-3 show the block diagrams of the MSSP module when operating in  ${\rm I}^2{\rm C}$  mode.

Both the SCLx and SDAx connections are bidirectional open-drain lines, each requiring pull-up resistors for the supply voltage. Pulling the line to ground is considered a logical zero and letting the line float is considered a logical one.

Figure 21-11 shows a typical connection between two processors configured as master and slave devices.

The  $I^2C$  bus can operate with one or more master devices and one or more slave devices.

There are four potential modes of operation for a given device:

- Master Transmit mode

(master is transmitting data to a slave)

- Master Receive mode

(master is receiving data from a slave)

- Slave Transmit mode (slave is transmitting data to a master)

- Slave Receive mode (slave is receiving data from the master)

To begin communication, a master device starts out in Master Transmit mode. The master device sends out a Start bit followed by the address byte of the slave it intends to communicate with. This is followed by a single Read/Write bit, which determines whether the master intends to transmit to or receive data from the slave device.

If the requested slave exists on the bus, it will respond with an Acknowledge bit, otherwise known as an ACK. The master then continues in either Transmit mode or Receive mode and the slave continues in the complement, either in Receive mode or Transmit mode, respectively.

A Start bit is indicated by a high-to-low transition of the SDAx line while the SCLx line is held high. Address and data bytes are sent out, Most Significant bit (MSb) first. The Read/Write bit is sent out as a logical one when the master intends to read data from the slave, and is sent out as a logical zero when it intends to write data to the slave.

### FIGURE 21-11: I<sup>2</sup>C MASTER/ SLAVE CONNECTION

The Acknowledge bit  $(\overline{ACK})$  is an active-low signal, which holds the SDAx line low to indicate to the transmitter that the slave device has received the transmitted data and is ready to receive more.

The transition of a data bit is always performed while the SCLx line is held low. Transitions that occur while the SCLx line is held high are used to indicate Start and Stop bits.

If the master intends to write to the slave, then it repeatedly sends out a byte of data, with the slave responding after each byte with an  $\overline{ACK}$  bit. In this example, the master device is in Master Transmit mode and the slave is in Slave Receive mode.

If the master intends to read from the slave, then it repeatedly receives a byte of data from the slave, and responds after each byte with an  $\overrightarrow{ACK}$  bit. In this example, the master device is in Master Receive mode and the slave is Slave Transmit mode.

On the last byte of data communicated, the master device may end the transmission by sending a Stop bit. If the master device is in Receive mode, it sends the Stop bit in place of the last ACK bit. A Stop bit is indicated by a low-to-high transition of the SDAx line while the SCLx line is held high.

In some cases, the master may want to maintain control of the bus and re-initiate another transmission. If so, the master device may send another Start bit in place of the Stop bit or last ACK bit when it is in receive mode.

The I<sup>2</sup>C bus specifies three message protocols;

- Single message where a master writes data to a slave.

- Single message where a master reads data from a slave.

- Combined message where a master initiates a minimum of two writes, or two reads, or a combination of writes and reads, to one or more slaves.

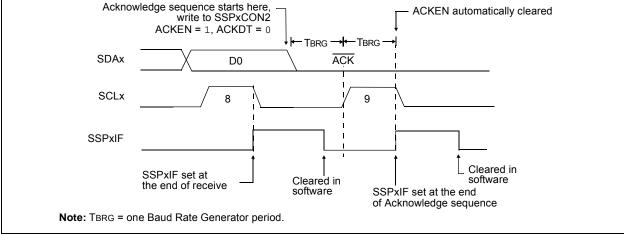

### 21.6.8 ACKNOWLEDGE SEQUENCE TIMING

An Acknowledge sequence is enabled by setting the Acknowledge Sequence Enable bit, ACKEN bit of the SSPxCON2 register. When this bit is set, the SCLx pin is pulled low and the contents of the Acknowledge data bit are presented on the SDAx pin. If the user wishes to generate an Acknowledge, then the ACKDT bit should be cleared. If not, the user should set the ACKDT bit before starting an Acknowledge sequence. The Baud Rate Generator then counts for one rollover period (TBRG) and the SCLx pin is deasserted (pulled high). When the SCLx pin is sampled high (clock arbitration), the Baud Rate Generator counts for TBRG. The SCLx pin is then pulled low. Following this, the ACKEN bit is automatically cleared, the Baud Rate Generator is turned off and the MSSP module then goes into Idle mode (Figure 21-30).

### 21.6.8.1 WCOL Status Flag

If the user writes the SSPxBUF when an Acknowledge sequence is in progress, then the WCOL bit is set and the contents of the buffer are unchanged (the write does not occur).

### 21.6.9 STOP CONDITION TIMING

A Stop bit is asserted on the SDAx pin at the end of a receive/transmit by setting the Stop Sequence Enable bit, PEN bit of the SSPxCON2 register. At the end of a receive/transmit, the SCLx line is held low after the falling edge of the ninth clock. When the PEN bit is set, the master will assert the SDAx line low. When the SDAx line is sampled low, the Baud Rate Generator is reloaded and counts down to '0'. When the Baud Rate Generator times out, the SCLx pin will be brought high and one TBRG (Baud Rate Generator rollover count) later, the SDAx pin will be deasserted. When the SDAx pin is sampled high while SCLx is high, the P bit of the SSPxSTAT register is set. A TBRG later, the PEN bit is cleared and the SSPxIF bit is set (Figure 21-31).

### 21.6.9.1 WCOL Status Flag

If the user writes the SSPxBUF when a Stop sequence is in progress, then the WCOL bit is set and the contents of the buffer are unchanged (the write does not occur).

| Name     | Bit7     | Bit6                 | Bit5        | Bit4     | Blt3     | Bit2         | Bit1       | Bit0     | Register<br>on Page |

|----------|----------|----------------------|-------------|----------|----------|--------------|------------|----------|---------------------|

| ANSELA   | —        | —                    | —           | ANSA4    | _        | ANSA2        | ANSA1      | ANSA0    | 99                  |

| ANSELC   | _        | _                    | —           | _        | ANSC3    | ANSC2        | ANSC1      | ANSC0    | 103                 |

| CLC1CON  | LC1EN    | LC10E                | LC10UT      | LC1INTP  | LC1INTN  | L            | C1MODE<2:0 | >        | 220                 |

| CLCDATA  | _        | _                    | _           | _        | _        | MLC3OUT      | MLC2OUT    | MLC1OUT  | 228                 |

| CLC1GLS0 | LC1G1D4T | LC1G1D4N             | LC1G1D3T    | LC1G1D3N | LC1G1D2T | LC1G1D2N     | LC1G1D1T   | LC1G1D1N | 224                 |

| CLC1GLS1 | LC1G2D4T | LC1G2D4N             | LC1G2D3T    | LC1G2D3N | LC1G2D2T | LC1G2D2N     | LC1G2D1T   | LC1G2D1N | 225                 |

| CLC1GLS2 | LC1G3D4T | LC1G3D4N             | LC1G3D3T    | LC1G3D3N | LC1G3D2T | LC1G3D2N     | LC1G3D1T   | LC1G3D1N | 226                 |

| CLC1GLS3 | LC1G4D4T | LC1G4D4N             | LC1G4D3T    | LC1G4D3N | LC1G4D2T | LC1G4D2N     | LC1G4D1T   | LC1G4D1N | 227                 |

| CLC1POL  | LC1POL   | —                    | —           |          | LC1G4POL | LC1G3POL     | LC1G2POL   | LC1G1POL | 221                 |

| CLC1SEL0 | —        | LC1D2S<2:0>          |             |          | _        | LC1D1S<2:0>  |            |          | 222                 |

| CLC1SEL1 | —        | LC1D4S<2:0>          |             |          | _        | LC1D3S<2:0>  |            |          | 223                 |

| CLC2CON  | LC2EN    | LC2OE LC2OUT LC2INTP |             |          | LC2INTN  | LC2MODE<2:0> |            |          | 220                 |

| CLC2GLS0 | LC2G1D4T | LC2G1D4N             | LC2G1D3T    | LC2G1D3N | LC2G1D2T | LC2G1D2N     | LC2G1D1T   | LC2G1D1N | 224                 |

| CLC2GLS1 | LC2G2D4T | LC2G2D4N             | LC2G2D3T    | LC2G2D3N | LC2G2D2T | LC2G2D2N     | LC2G2D1T   | LC2G2D1N | 225                 |

| CLC2GLS2 | LC2G3D4T | LC2G3D4N             | LC2G3D3T    | LC2G3D3N | LC2G3D2T | LC2G3D2N     | LC2G3D1T   | LC2G3D1N | 226                 |

| CLC2GLS3 | LC2G4D4T | LC2G4D4N             | LC2G4D3T    | LC2G4D3N | LC2G4D2T | LC2G4D2N     | LC2G4D1T   | LC2G4D1N | 227                 |

| CLC2POL  | LC2POL   | _                    | _           | _        | LC2G4POL | LC2G3POL     | LC2G2POL   | LC2G1POL | 221                 |

| CLC2SEL0 | —        |                      | LC2D2S<2:0> |          |          | LC2D1S<2:0>  |            |          | 222                 |

| CLC2SEL1 | —        |                      | LC2D4S<2:0> |          |          | LC2D3S<2:0>  |            |          | 223                 |

| INTCON   | GIE      | PEIE                 | TMR0IE      | INTE     | IOCIE    | TMR0IF       | INTF       | IOCIF    | 64                  |

| PIE3     | —        | —                    | —           | -        | _        | —            | CLC2IE     | CLC1IE   | 67                  |

| PIR3     | —        | —                    | —           |          | _        | —            | CLC2IF     | CLC1IF   | 70                  |

| TRISA    | —        | —                    | TRISA5      | TRISA4   | (1)      | TRISA2       | TRISA1     | TRISA0   | 98                  |

| TRISC    | —        | —                    | TRISC5      | TRISC4   | TRISC3   | TRISC2       | TRISC1     | TRISC0   | 102                 |

— = unimplemented read as '0', Shaded cells are not used for CLC module. Unimplemented, read as '1'. Legend: Note 1:

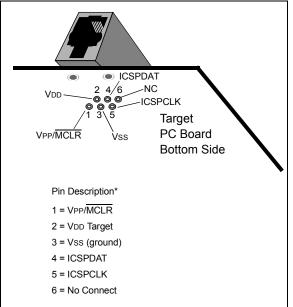

# 26.0 IN-CIRCUIT SERIAL PROGRAMMING<sup>™</sup> (ICSP<sup>™</sup>)

ICSP<sup>™</sup> programming allows customers to manufacture circuit boards with unprogrammed devices. Programming can be done after the assembly process allowing the device to be programmed with the most recent firmware or a custom firmware. Five pins are needed for ICSP<sup>™</sup> programming:

- ICSPCLK

- ICSPDAT

- MCLR/VPP

- VDD

- Vss

In Program/Verify mode the program memory, user IDs and the Configuration Words are programmed through serial communications. The ICSPDAT pin is a bidirectional I/O used for transferring the serial data and the ICSPCLK pin is the clock input. For more information on ICSP<sup>TM</sup> refer to the "*PIC12(L)F1501/PIC16(L)F150X Memory Programming Specification*" (DS41573).

### 26.1 High-Voltage Programming Entry Mode

The device is placed into High-Voltage Programming Entry mode by holding the ICSPCLK and ICSPDAT pins low then raising the voltage on MCLR/VPP to VIHH.

### 26.2 Low-Voltage Programming Entry Mode

The Low-Voltage Programming Entry mode allows the PIC<sup>®</sup> Flash MCUs to be programmed using VDD only, without high voltage. When the LVP bit of Configuration Words is set to '1', the ICSP Low-Voltage Programming Entry mode is enabled. To disable the Low-Voltage ICSP mode, the LVP bit must be programmed to '0'.

Entry into the Low-Voltage Programming Entry mode requires the following steps:

- 1. MCLR is brought to VIL.

- 2. A 32-bit key sequence is presented on ICSPDAT, while clocking ICSPCLK.

Once the key sequence is complete,  $\overline{\text{MCLR}}$  must be held at VIL for as long as Program/Verify mode is to be maintained.

If low-voltage programming is enabled (LVP = 1), the  $\overline{\text{MCLR}}$  Reset function is automatically enabled and cannot be disabled. See **Section 6.5 "MCLR**" for more information.

The LVP bit can only be reprogrammed to '0' by using the High-Voltage Programming mode.

### 26.3 Common Programming Interfaces

Connection to a target device is typically done through an ICSP<sup>™</sup> header. A commonly found connector on development tools is the RJ-11 in the 6P6C (6-pin, 6-connector) configuration. See Figure 26-1.

Another connector often found in use with the PICkit<sup>™</sup> programmers is a standard 6-pin header with 0.1 inch spacing. Refer to Figure 26-2.

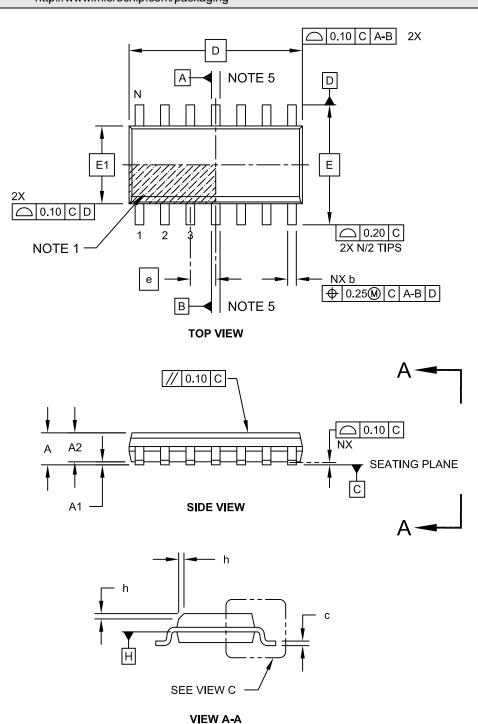

### 14-Lead Plastic Small Outline (SL) - Narrow, 3.90 mm Body [SOIC]

**Note:** For the most current package drawings, please see the Microchip Packaging Specification located at http://www.microchip.com/packaging

Microchip Technology Drawing No. C04-065C Sheet 1 of 2