Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

#### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Product Status             | Active                                                                     |

|----------------------------|----------------------------------------------------------------------------|

| Core Processor             | PIC                                                                        |

| Core Size                  | 8-Bit                                                                      |

| Speed                      | 20MHz                                                                      |

| Connectivity               | I <sup>2</sup> C, SPI                                                      |

| Peripherals                | Brown-out Detect/Reset, POR, PWM, WDT                                      |

| Number of I/O              | 11                                                                         |

| Program Memory Size        | 3.5KB (2K x 14)                                                            |

| Program Memory Type        | FLASH                                                                      |

| EEPROM Size                | -                                                                          |

| RAM Size                   | 128 x 8                                                                    |

| Voltage - Supply (Vcc/Vdd) | 2.3V ~ 5.5V                                                                |

| Data Converters            | A/D 8x10b                                                                  |

| Oscillator Type            | Internal                                                                   |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                          |

| Mounting Type              | Surface Mount                                                              |

| Package / Case             | 14-SOIC (0.154", 3.90mm Width)                                             |

| Supplier Device Package    | 14-SOIC                                                                    |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic16f1503t-i-sl |

|                            |                                                                            |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

## 3.3.2 SPECIAL FUNCTION REGISTER

The Special Function Registers are registers used by the application to control the desired operation of peripheral functions in the device. The Special Function Registers occupy the 20 bytes after the core registers of every data memory bank (addresses x0Ch/x8Ch through x1Fh/x9Fh). The registers associated with the operation of the peripherals are described in the appropriate peripheral chapter of this data sheet.

### 3.3.3 GENERAL PURPOSE RAM

There are up to 80 bytes of GPR in each data memory bank. The Special Function Registers occupy the 20 bytes after the core registers of every data memory bank (addresses x0Ch/x8Ch through x1Fh/x9Fh).

#### 3.3.3.1 Linear Access to GPR

The general purpose RAM can be accessed in a non-banked method via the FSRs. This can simplify access to large memory structures. See **Section 3.6.2** "Linear Data Memory" for more information.

#### 3.3.4 COMMON RAM

There are 16 bytes of common RAM accessible from all banks.

#### FIGURE 3-2: BANKED MEMORY PARTITIONING

|                   | Rev. 10-00<br>7/3                             |

|-------------------|-----------------------------------------------|

| 7-bit Bank Offset | Memory Region                                 |

| 00h<br>0Bh        | Core Registers<br>(12 bytes)                  |

| 0Ch<br>1Fh        | Special Function Registers (20 bytes maximum) |

| 6Fh               | General Purpose RAM<br>(80 bytes maximum)     |

| 70h<br>7Fh        | Common RAM<br>(16 bytes)                      |

### 3.3.5 DEVICE MEMORY MAPS

The memory maps for Bank 0 through Bank 31 are shown in the tables in this section.

### TABLE 3-3: PIC16(L)F1503 MEMORY MAP

| IADI  | BANK 0                        |              | BANK 1                                |       | BANK 2                                |       | BANK 3                                |              | BANK 4                                |              | BANK 5                                |              | BANK 6                                |              | BANK 7                                |

|-------|-------------------------------|--------------|---------------------------------------|-------|---------------------------------------|-------|---------------------------------------|--------------|---------------------------------------|--------------|---------------------------------------|--------------|---------------------------------------|--------------|---------------------------------------|

| 000h  |                               | 080h         |                                       | 100h  |                                       | 180h  |                                       | 200h         |                                       | 280h         |                                       | 300h         |                                       | 380h         |                                       |

| 00011 | Core Registers<br>(Table 3-2) | 00011        | Core Registers<br>(Table 3-2)         | 10011 | Core Registers<br>(Table 3-2)         | Tooli | Core Registers<br>(Table 3-2)         | 20011        | Core Registers<br>(Table 3-2)         | 20011        | Core Registers<br>(Table 3-2)         | 00011        | Core Registers<br>(Table 3-2)         | 00011        | Core Registers<br>(Table 3-2)         |

| 00Bh  |                               | 08Bh         |                                       | 10Bh  |                                       | 18Bh  |                                       | 20Bh         |                                       | 28Bh         |                                       | 30Bh         |                                       | 38Bh         |                                       |

| 00Ch  | PORTA                         | 08Ch         | TRISA                                 | 10Ch  | LATA                                  | 18Ch  | ANSELA                                | 20Ch         | WPUA                                  | 28Ch         | _                                     | 30Ch         | _                                     | 38Ch         | _                                     |

| 00Dh  | _                             | 08Dh         | _                                     | 10Dh  | _                                     | 18Dh  | _                                     | 20Dh         | —                                     | 28Dh         | _                                     | 30Dh         | —                                     | 38Dh         | _                                     |

| 00Eh  | PORTC                         | 08Eh         | TRISC                                 | 10Eh  | LATC                                  | 18Eh  | ANSELC                                | 20Eh         |                                       | 28Eh         | —                                     | 30Eh         | _                                     | 38Eh         | _                                     |

| 00Fh  | _                             | 08Fh         | —                                     | 10Fh  |                                       | 18Fh  |                                       | 20Fh         |                                       | 28Fh         |                                       | 30Fh         | —                                     | 38Fh         | —                                     |

| 010h  | —                             | 090h         | —                                     | 110h  | —                                     | 190h  | —                                     | 210h         | —                                     | 290h         | _                                     | 310h         | _                                     | 390h         | _                                     |

| 011h  | PIR1                          | 091h         | PIE1                                  | 111h  | CM1CON0                               | 191h  | PMADRL                                | 211h         | SSP1BUF                               | 291h         | _                                     | 311h         | _                                     | 391h         | IOCAP                                 |

| 012h  | PIR2                          | 092h         | PIE2                                  | 112h  | CM1CON1                               | 192h  | PMADRH                                | 212h         | SSP1ADD                               | 292h         | _                                     | 312h         | _                                     | 392h         | IOCAN                                 |

| 013h  | PIR3                          | 093h         | PIE3                                  | 113h  | CM2CON0                               | 193h  | PMDATL                                | 213h         | SSP1MSK                               | 293h         | —                                     | 313h         | _                                     | 393h         | IOCAF                                 |

| 014h  | _                             | 094h         | —                                     | 114h  | CM2CON1                               | 194h  | PMDATH                                | 214h         | SSP1STAT                              | 294h         | —                                     | 314h         | —                                     | 394h         | _                                     |

| 015h  | TMR0                          | 095h         | OPTION_REG                            | 115h  | CMOUT                                 | 195h  | PMCON1                                | 215h         | SSP1CON1                              | 295h         | _                                     | 315h         | _                                     | 395h         | _                                     |

| 016h  | TMR1L                         | 096h         | PCON                                  | 116h  | BORCON                                | 196h  | PMCON2                                | 216h         | SSP1CON2                              | 296h         | _                                     | 316h         | —                                     | 396h         | _                                     |

| 017h  | TMR1H                         | 097h         | WDTCON                                | 117h  | FVRCON                                | 197h  | VREGCON                               | 217h         | SSP1CON3                              | 297h         | _                                     | 317h         | _                                     | 397h         | —                                     |

| 018h  | T1CON                         | 098h         |                                       | 118h  | DACCON0                               | 198h  | —                                     | 218h         | _                                     | 298h         | —                                     | 318h         | _                                     | 398h         | —                                     |

| 019h  | T1GCON                        | 099h         | OSCCON                                | 119h  | DACCON1                               | 199h  | —                                     | 219h         | —                                     | 299h         | —                                     | 319h         | _                                     | 399h         | —                                     |

| 01Ah  | TMR2                          | 09Ah         | OSCSTAT                               | 11Ah  | —                                     | 19Ah  | _                                     | 21Ah         | _                                     | 29Ah         | —                                     | 31Ah         | _                                     | 39Ah         | _                                     |

| 01Bh  | PR2                           | 09Bh         | ADRESL                                | 11Bh  | —                                     | 19Bh  | _                                     | 21Bh         | —                                     | 29Bh         | —                                     | 31Bh         | _                                     | 39Bh         | —                                     |

| 01Ch  | T2CON                         | 09Ch         | ADRESH                                | 11Ch  | _                                     | 19Ch  | _                                     | 21Ch         | _                                     | 29Ch         | —                                     | 31Ch         | _                                     | 39Ch         | _                                     |

| 01Dh  | _                             | 09Dh         | ADCON0                                | 11Dh  | APFCON                                | 19Dh  | _                                     | 21Dh         | _                                     | 29Dh         | —                                     | 31Dh         | _                                     | 39Dh         | _                                     |

| 01Eh  | _                             | 09Eh         | ADCON1                                | 11Eh  | _                                     | 19Eh  | _                                     | 21Eh         | _                                     | 29Eh         | _                                     | 31Eh         | _                                     | 39Eh         | _                                     |

| 01Fh  | _                             | 09Fh         | ADCON2                                | 11Fh  | _                                     | 19Fh  | _                                     | 21Fh         | _                                     | 29Fh         | _                                     | 31Fh         | _                                     | 39Fh         | _                                     |

| 020h  |                               | 0A0h         | General                               | 120h  |                                       | 1A0h  |                                       | 220h         |                                       | 2A0h         |                                       | 320h         |                                       | 3A0h         |                                       |

|       | General<br>Purpose            | 0BFh         | Purpose<br>Register<br>32 Bytes       |       | Unimplemented                         |       | Unimplemented                         |              | Unimplemented                         |              | Unimplemented                         |              | Unimplemented                         |              | Unimplemented                         |

|       | Register<br>80 Bytes          | 0C0h         | Unimplemented<br>Read as '0'          |       | Read as '0'                           |       | Read as '0'                           |              | Read as '0'                           |              | Read as '0'                           |              | Read as '0'                           |              | Read as '0'                           |

| 06Fh  |                               | 0EFh         |                                       | 16Fh  |                                       | 1EFh  |                                       | 26Fh         |                                       | 2EFh         |                                       | 36Fh         |                                       | 3EFh         |                                       |

| 070h  | Common RAM                    | 0F0h<br>0FFh | Common RAM<br>(Accesses<br>70h – 7Fh) | 170h  | Common RAM<br>(Accesses<br>70h – 7Fh) | 1F0h  | Common RAM<br>(Accesses<br>70h – 7Fh) | 270h<br>27Fh | Common RAM<br>(Accesses<br>70h – 7Fh) | 2F0h<br>2FFh | Common RAM<br>(Accesses<br>70h – 7Fh) | 370h<br>37Fh | Common RAM<br>(Accesses<br>70h – 7Fh) | 3F0h<br>3FFh | Common RAM<br>(Accesses<br>70h – 7Fh) |

| VI 11 |                               |              |                                       |       |                                       |       |                                       |              |                                       |              |                                       | 51111        |                                       |              |                                       |

Legend: = Unimplemented data memory locations, read as '0'

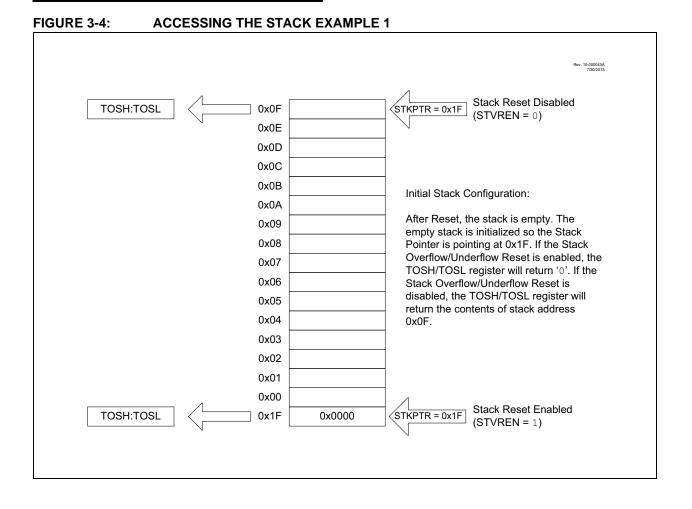

## 3.5 Stack

All devices have a 16-level x 15-bit wide hardware stack (refer to Figures 3-4 through 3-7). The stack space is not part of either program or data space. The PC is PUSHed onto the stack when CALL or CALLW instructions are executed or an interrupt causes a branch. The stack is POPed in the event of a RETURN, RETLW or a RETFIE instruction execution. PCLATH is not affected by a PUSH or POP operation.

The stack operates as a circular buffer if the STVREN bit is programmed to '0' (Configuration Words). This means that after the stack has been PUSHed sixteen times, the seventeenth PUSH overwrites the value that was stored from the first PUSH. The eighteenth PUSH overwrites the second PUSH (and so on). The STKOVF and STKUNF flag bits will be set on an Overflow/Underflow, regardless of whether the Reset is enabled.

Note 1: There are no instructions/mnemonics called PUSH or POP. These are actions that occur from the execution of the CALL, CALLW, RETURN, RETLW and RETFIE instructions or the vectoring to an interrupt address.

## 3.5.1 ACCESSING THE STACK

The stack is available through the TOSH, TOSL and STKPTR registers. STKPTR is the current value of the Stack Pointer. TOSH:TOSL register pair points to the TOP of the stack. Both registers are read/writable. TOS is split into TOSH and TOSL due to the 15-bit size of the PC. To access the stack, adjust the value of STKPTR, which will position TOSH:TOSL, then read/write to TOSH:TOSL. STKPTR is 5 bits to allow detection of overflow and underflow.

| Note: | Care should be taken when modifying the |

|-------|-----------------------------------------|

|       | STKPTR while interrupts are enabled.    |

During normal program operation, CALL, CALLW and Interrupts will increment STKPTR while RETLW, RETURN, and RETFIE will decrement STKPTR. At any time STKPTR can be inspected to see how much stack is left. The STKPTR always points at the currently used place on the stack. Therefore, a CALL or CALLW will increment the STKPTR and then write the PC, and a return will unload the PC and then decrement the STKPTR.

Reference Figure 3-4 through Figure 3-7 for examples of accessing the stack.

|                                                                                               |                                         |                                   | 11.0         |                  |                  |     | 11.0  |  |  |  |  |

|-----------------------------------------------------------------------------------------------|-----------------------------------------|-----------------------------------|--------------|------------------|------------------|-----|-------|--|--|--|--|

| U-0                                                                                           | R/W-0/0                                 | R/W-0/0                           | U-0          | R/W-0/0          | R/W-0/0          | U-0 | U-0   |  |  |  |  |

|                                                                                               | C2IE                                    | C1IE                              |              | BCL1IE           | NCO1IE           | —   | —     |  |  |  |  |

| bit 7                                                                                         |                                         |                                   |              |                  |                  |     | bit 0 |  |  |  |  |

|                                                                                               |                                         |                                   |              |                  |                  |     |       |  |  |  |  |

| Legend:                                                                                       |                                         |                                   |              |                  |                  |     |       |  |  |  |  |

| R = Readable                                                                                  |                                         | W = Writable                      |              |                  | nented bit, read |     |       |  |  |  |  |

| u = Bit is unchanged x = Bit is unknown -n/n = Value at POR and BOR/Value at all other Resets |                                         |                                   |              |                  |                  |     |       |  |  |  |  |

| '1' = Bit is set                                                                              |                                         | '0' = Bit is clea                 | ared         |                  |                  |     |       |  |  |  |  |

|                                                                                               |                                         |                                   |              |                  |                  |     |       |  |  |  |  |

| bit 7                                                                                         | 7 Unimplemented: Read as '0'            |                                   |              |                  |                  |     |       |  |  |  |  |

| bit 6                                                                                         | C2IE: Compa                             | rator C2 Interru                  | upt Enable b | it               |                  |     |       |  |  |  |  |

|                                                                                               | 1 = Enables the Comparator C2 interrupt |                                   |              |                  |                  |     |       |  |  |  |  |

|                                                                                               |                                         | the Comparate                     |              |                  |                  |     |       |  |  |  |  |

| bit 5                                                                                         | •                                       | rator C1 Interru                  | •            |                  |                  |     |       |  |  |  |  |

|                                                                                               |                                         | the Comparato<br>the Comparato    |              |                  |                  |     |       |  |  |  |  |

| h:+ 4                                                                                         |                                         |                                   | •            | JL               |                  |     |       |  |  |  |  |

| bit 4                                                                                         | •                                       | ted: Read as '                    |              |                  |                  |     |       |  |  |  |  |

| bit 3                                                                                         |                                         | SP Bus Collisio                   | •            |                  |                  |     |       |  |  |  |  |

|                                                                                               |                                         | the MSSP Bus<br>the MSSP Bus      |              |                  |                  |     |       |  |  |  |  |

| bit 2                                                                                         |                                         |                                   |              | or Interrupt Ena | ble bit          |     |       |  |  |  |  |

|                                                                                               |                                         | the NCO interr                    |              |                  |                  |     |       |  |  |  |  |

|                                                                                               |                                         | the NCO interr                    |              |                  |                  |     |       |  |  |  |  |

| bit 1-0                                                                                       |                                         | ted: Read as '                    | •            |                  |                  |     |       |  |  |  |  |

|                                                                                               | •                                       |                                   |              |                  |                  |     |       |  |  |  |  |

|                                                                                               |                                         |                                   |              |                  |                  |     |       |  |  |  |  |

|                                                                                               |                                         | TCON register<br>peripheral inter |              |                  |                  |     |       |  |  |  |  |

| Set                                                                                           | to enable ally p                        |                                   | iupt.        |                  |                  |     |       |  |  |  |  |

## REGISTER 7-3: PIE2: PERIPHERAL INTERRUPT ENABLE REGISTER 2

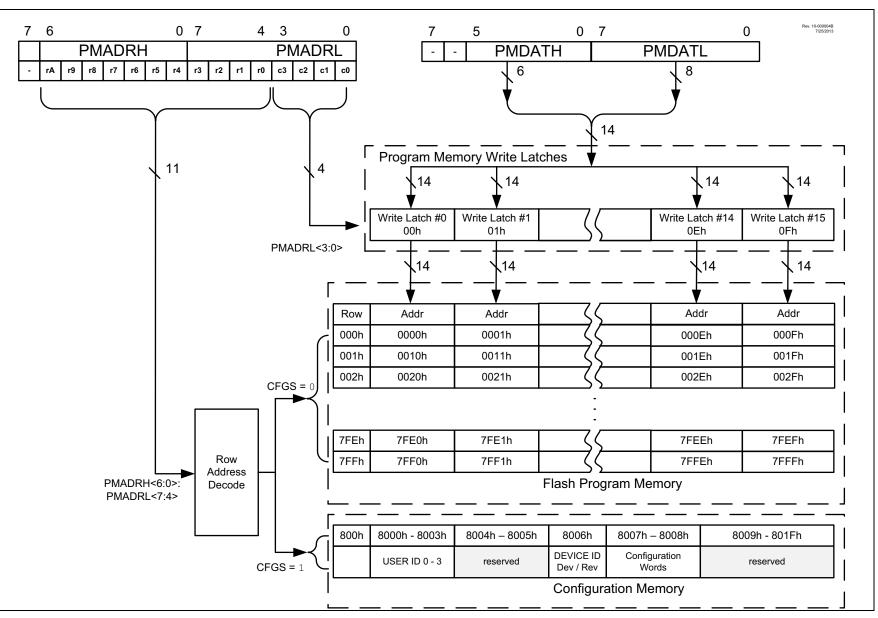

### EXAMPLE 10-2: ERASING ONE ROW OF PROGRAM MEMORY

|                      |                                              |                                                      | s the following:<br>erase row is loaded in ADDRH:ADDRL                                                                                                                                                                                                                                                                                                         |

|----------------------|----------------------------------------------|------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| ; 2. A               | ADDRH and AI                                 | DDRL are located                                     | d in shared data memory 0x70 - 0x7F (common RAM)                                                                                                                                                                                                                                                                                                               |

|                      | BCF<br>BANKSEL<br>MOVF<br>MOVWF<br>MOVF      | INTCON,GIE<br>PMADRL<br>ADDRL,W<br>PMADRL<br>ADDRH,W | ; Disable ints so required sequences will execute properly<br>; Load lower 8 bits of erase address boundary<br>; Load upper 6 bits of erase address boundary                                                                                                                                                                                                   |

|                      | MOVWF<br>BCF<br>BSF<br>BSF                   | PMADRH<br>PMCON1,CFGS<br>PMCON1,FREE<br>PMCON1,WREN  | ; Not configuration space<br>; Specify an erase operation<br>; Enable writes                                                                                                                                                                                                                                                                                   |

| Required<br>Sequence | MOVLW<br>MOVWF<br>MOVWF<br>BSF<br>NOP<br>NOP | 55h<br>PMCON2<br>0AAh<br>PMCON2<br>PMCON1,WR         | <pre>; Start of required sequence to initiate erase<br/>; Write 55h<br/>;<br/>; Write AAh<br/>; Set WR bit to begin erase<br/>; NOP instructions are forced as processor starts<br/>; row erase of program memory.<br/>;<br/>;<br/>; The processor stalls until the erase process is complete<br/>; after erase processor continues with 3rd instruction</pre> |

|                      | BCF<br>BSF                                   | PMCON1,WREN<br>INTCON,GIE                            | ; Disable writes<br>; Enable interrupts                                                                                                                                                                                                                                                                                                                        |

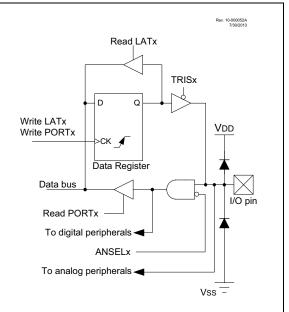

## 11.0 I/O PORTS

Each port has three standard registers for its operation. These registers are:

- · TRISx registers (data direction)

- PORTx registers (reads the levels on the pins of the device)

- LATx registers (output latch)

Some ports may have one or more of the following additional registers. These registers are:

- · ANSELx (analog select)

- · WPUx (weak pull-up)

In general, when a peripheral is enabled on a port pin, that pin cannot be used as a general purpose output. However, the pin can still be read.

## TABLE 11-1:PORT AVAILABILITY PER<br/>DEVICE

| Device        | PORTA | PORTB | PORTC |

|---------------|-------|-------|-------|

| PIC16(L)F1503 | ٠     |       | ٠     |

The Data Latch (LATx registers) is useful for read-modify-write operations on the value that the I/O pins are driving.

A write operation to the LATx register has the same effect as a write to the corresponding PORTx register. A read of the LATx register reads of the values held in the I/O PORT latches, while a read of the PORTx register reads the actual I/O pin value.

Ports that support analog inputs have an associated ANSELx register. When an ANSEL bit is set, the digital input buffer associated with that bit is disabled. Disabling the input buffer prevents analog signal levels on the pin between a logic high and low from causing excessive current in the logic input circuitry. A simplified model of a generic I/O port, without the interfaces to other peripherals, is shown in Figure 11-1.

## FIGURE 11-1: GE

#### GENERIC I/O PORT OPERATION

## 11.1 Alternate Pin Function

The Alternate Pin Function Control (APFCON) register is used to steer specific peripheral input and output functions between different pins. The APFCON register is shown in Register 11-1. For this device family, the following functions can be moved between different pins.

- <u>ss</u>

- T1G

- CLC1

- NCO1

- SDOSEL

## 11.2 Register Definitions: Alternate Pin Function Control

### **REGISTER 11-1: APFCON: ALTERNATE PIN FUNCTION CONTROL REGISTER**

| U-0   | U-0 | R/W-0/0 | R/W-0/0 | R/W-0/0 | U-0 | R/W-0/0 | R/W-0/0 |

|-------|-----|---------|---------|---------|-----|---------|---------|

|       | _   | SDOSEL  | SSSEL   | T1GSEL  | _   | CLC1SEL | NCO1SEL |

| bit 7 |     |         |         |         |     |         | bit 0   |

| Legend:              |                      |                                                       |

|----------------------|----------------------|-------------------------------------------------------|

| R = Readable bit     | W = Writable bit     | U = Unimplemented bit, read as '0'                    |

| u = Bit is unchanged | x = Bit is unknown   | -n/n = Value at POR and BOR/Value at all other Resets |

| '1' = Bit is set     | '0' = Bit is cleared |                                                       |

| bit 7-6 | Unimplemented: Read as '0'             |

|---------|----------------------------------------|

| bit 5   | SDOSEL: Pin Selection bit              |

|         | 1 = SDO function is on RA4             |

|         | 0 = SDO function is on RC2             |

| bit 4   | SSSEL: Pin Selection bit               |

|         | $1 = \overline{SS}$ function is on RA3 |

|         | $0 = \overline{SS}$ function is on RC3 |

| bit 3   | T1GSEL: Pin Selection bit              |

|         | 1 = T1G function is on RA3             |

|         | 0 = T1G function is on RA4             |

| bit 2   | Unimplemented: Read as '0'             |

| bit 1   | CLC1SEL: Pin Selection bit             |

|         | 1 = CLC1 function is on RC5            |

|         | 0 = CLC1 function is on RA2            |

| bit 0   | NCO1SEL: Pin Selection bit             |

|         | 1 = NCO1 function is on RA4            |

|         | 0 = NCO1 function is on RC1            |

These bits have no effect on the values of any TRIS register. PORT and TRIS overrides will be routed to the correct pin. The unselected pin will be unaffected.

## 20.5 Register Definitions: Timer2 Control

|                                                                                  | Unimplemen<br>T2OUTPS<3<br>0000 = 1:1 F<br>0001 = 1:2 F<br>0010 = 1:3 F<br>0011 = 1:4 F<br>0100 = 1:5 F | W = Writa<br>x = Bit is u<br>'0' = Bit is<br>nted: Read<br>3:0>: Timer2<br>Postscaler<br>Postscaler<br>Postscaler<br>Postscaler<br>Postscaler | unknown<br>cleared<br>as '0' |                       | U = Unimple<br>-n/n = Value<br>er Select bits |           | read as '0' |             | bit          |  |  |  |

|----------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------|------------------------------|-----------------------|-----------------------------------------------|-----------|-------------|-------------|--------------|--|--|--|

| <b>.egend:</b><br>R = Readable t<br>a = Bit is uncha<br>1' = Bit is set<br>bit 7 | Unimplemen<br>T2OUTPS<3<br>0000 = 1:1 F<br>0001 = 1:2 F<br>0010 = 1:3 F<br>0011 = 1:4 F<br>0100 = 1:5 F | x = Bit is u<br>'0' = Bit is<br>nted: Read<br>3:0>: Timer2<br>Postscaler<br>Postscaler<br>Postscaler<br>Postscaler<br>Postscaler              | unknown<br>cleared<br>as '0' |                       | -n/n = Value                                  |           |             |             |              |  |  |  |

| R = Readable b<br>u = Bit is uncha<br>1' = Bit is set<br>bit 7                   | Unimplemen<br>T2OUTPS<3<br>0000 = 1:1 F<br>0001 = 1:2 F<br>0010 = 1:3 F<br>0011 = 1:4 F<br>0100 = 1:5 F | x = Bit is u<br>'0' = Bit is<br>nted: Read<br>3:0>: Timer2<br>Postscaler<br>Postscaler<br>Postscaler<br>Postscaler<br>Postscaler              | unknown<br>cleared<br>as '0' |                       | -n/n = Value                                  |           |             |             | other Resets |  |  |  |

| R = Readable b<br>u = Bit is uncha<br>1' = Bit is set<br>bit 7                   | Unimplemen<br>T2OUTPS<3<br>0000 = 1:1 F<br>0001 = 1:2 F<br>0010 = 1:3 F<br>0011 = 1:4 F<br>0100 = 1:5 F | x = Bit is u<br>'0' = Bit is<br>nted: Read<br>3:0>: Timer2<br>Postscaler<br>Postscaler<br>Postscaler<br>Postscaler<br>Postscaler              | unknown<br>cleared<br>as '0' |                       | -n/n = Value                                  |           |             |             | other Resets |  |  |  |

| u = Bit is uncha<br>'1' = Bit is set<br>bit 7                                    | Unimplemen<br>T2OUTPS<3<br>0000 = 1:1 F<br>0001 = 1:2 F<br>0010 = 1:3 F<br>0011 = 1:4 F<br>0100 = 1:5 F | x = Bit is u<br>'0' = Bit is<br>nted: Read<br>3:0>: Timer2<br>Postscaler<br>Postscaler<br>Postscaler<br>Postscaler<br>Postscaler              | unknown<br>cleared<br>as '0' |                       | -n/n = Value                                  |           |             |             | other Resets |  |  |  |

| '1' = Bit is set<br>bit 7                                                        | Unimplemen<br>T2OUTPS<3<br>0000 = 1:1 F<br>0001 = 1:2 F<br>0010 = 1:3 F<br>0011 = 1:4 F<br>0100 = 1:5 F | '0' = Bit is<br>nted: Read<br>3:0>: Timer2<br>Postscaler<br>Postscaler<br>Postscaler<br>Postscaler                                            | cleared                      |                       |                                               | at POR an | d BOR/Valu  | ue at all c | other Resets |  |  |  |

| bit 7                                                                            | <b>T2OUTPS&lt;3</b><br>0000 = 1:1 F<br>0001 = 1:2 F<br>0010 = 1:3 F<br>0011 = 1:4 F<br>0100 = 1:5 F     | nted: Read<br>3:0>: Timer2<br>Postscaler<br>Postscaler<br>Postscaler<br>Postscaler<br>Postscaler                                              | <b>as</b> '0'                | Postscale             | er Select bits                                |           |             |             |              |  |  |  |

| bit 7<br>bit 6-3                                                                 | <b>T2OUTPS&lt;3</b><br>0000 = 1:1 F<br>0001 = 1:2 F<br>0010 = 1:3 F<br>0011 = 1:4 F<br>0100 = 1:5 F     | <b>3:0&gt;:</b> Timer2<br>Postscaler<br>Postscaler<br>Postscaler<br>Postscaler                                                                |                              | Postscale             | er Select bits                                |           |             |             |              |  |  |  |

| bit 7<br>bit 6-3                                                                 | <b>T2OUTPS&lt;3</b><br>0000 = 1:1 F<br>0001 = 1:2 F<br>0010 = 1:3 F<br>0011 = 1:4 F<br>0100 = 1:5 F     | <b>3:0&gt;:</b> Timer2<br>Postscaler<br>Postscaler<br>Postscaler<br>Postscaler                                                                |                              | Postscale             | er Select bits                                |           |             |             |              |  |  |  |

| bit 6-3                                                                          | 0000 = 1:1 F<br>0001 = 1:2 F<br>0010 = 1:3 F<br>0011 = 1:4 F<br>0100 = 1:5 F                            | Postscaler<br>Postscaler<br>Postscaler<br>Postscaler                                                                                          | Output                       | Postscale             | er Select bits                                |           |             |             |              |  |  |  |

|                                                                                  | 0001 = 1:2 F<br>0010 = 1:3 F<br>0011 = 1:4 F<br>0100 = 1:5 F                                            | Postscaler<br>Postscaler<br>Postscaler                                                                                                        |                              |                       |                                               |           |             |             |              |  |  |  |

|                                                                                  | 0010 = 1:3 F<br>0011 = 1:4 F<br>0100 = 1:5 F                                                            | Postscaler<br>Postscaler                                                                                                                      |                              |                       |                                               |           |             |             |              |  |  |  |

|                                                                                  | 0011 = 1:4 F<br>0100 = 1:5 F                                                                            | Postscaler                                                                                                                                    |                              |                       |                                               |           |             |             |              |  |  |  |

|                                                                                  | 0100 = 1:5 F                                                                                            |                                                                                                                                               |                              | 0010 = 1:3 Postscaler |                                               |           |             |             |              |  |  |  |

|                                                                                  |                                                                                                         | USISCAICI                                                                                                                                     | 0100 = 1:5 Postscaler        |                       |                                               |           |             |             |              |  |  |  |

|                                                                                  | 0101 = 1:6 Postscaler                                                                                   |                                                                                                                                               |                              |                       |                                               |           |             |             |              |  |  |  |

|                                                                                  | 0110 = 1:7 Postscaler                                                                                   |                                                                                                                                               |                              |                       |                                               |           |             |             |              |  |  |  |

|                                                                                  | 0111 = 1:8 F                                                                                            |                                                                                                                                               |                              |                       |                                               |           |             |             |              |  |  |  |

|                                                                                  | 1000 = 1:9 F                                                                                            | Postscaler                                                                                                                                    |                              |                       |                                               |           |             |             |              |  |  |  |

|                                                                                  | 1001 = 1:10                                                                                             | Postscaler                                                                                                                                    |                              |                       |                                               |           |             |             |              |  |  |  |

|                                                                                  | 1010 = 1:11                                                                                             | Postscaler                                                                                                                                    |                              |                       |                                               |           |             |             |              |  |  |  |

|                                                                                  | 1011 = 1:12 Postscaler                                                                                  |                                                                                                                                               |                              |                       |                                               |           |             |             |              |  |  |  |

|                                                                                  | 1100 = 1:13 Postscaler                                                                                  |                                                                                                                                               |                              |                       |                                               |           |             |             |              |  |  |  |

|                                                                                  | 1101 = 1:14                                                                                             |                                                                                                                                               |                              |                       |                                               |           |             |             |              |  |  |  |

|                                                                                  | 1110 = 1:15 Postscaler<br>1111 = 1:16 Postscaler                                                        |                                                                                                                                               |                              |                       |                                               |           |             |             |              |  |  |  |

| h:+ 0                                                                            |                                                                                                         |                                                                                                                                               |                              |                       |                                               |           |             |             |              |  |  |  |

| bit 2                                                                            | TMR2ON: Ti                                                                                              |                                                                                                                                               |                              |                       |                                               |           |             |             |              |  |  |  |

|                                                                                  | 1 = Timer2 i<br>0 = Timer2 i                                                                            |                                                                                                                                               |                              |                       |                                               |           |             |             |              |  |  |  |

| bit 1-0                                                                          | T2CKPS<1:                                                                                               |                                                                                                                                               | Clock Pr                     | escale Se             | lect hits                                     |           |             |             |              |  |  |  |

|                                                                                  | 00 = Prescal                                                                                            |                                                                                                                                               |                              |                       |                                               |           |             |             |              |  |  |  |

|                                                                                  | 01 = Prescal                                                                                            |                                                                                                                                               |                              |                       |                                               |           |             |             |              |  |  |  |

|                                                                                  | 10 = Prescal                                                                                            |                                                                                                                                               |                              |                       |                                               |           |             |             |              |  |  |  |

|                                                                                  | 11 = Prescal                                                                                            | ler is 64                                                                                                                                     |                              |                       |                                               |           |             |             |              |  |  |  |

| TABLE 20-1:                                                                      | SUMMAR                                                                                                  |                                                                                                                                               | SISTER                       | S ASSO                |                                               |           | 2           |             |              |  |  |  |

| Name                                                                             |                                                                                                         |                                                                                                                                               | Rit 5                        | Bit 4                 | Bit 3                                         | Bit 2     | Bit 1       | Bit 0       | Regist       |  |  |  |

## REGISTER 20-1: T2CON: TIMER2 CONTROL REGISTER

| Name   | Bit 7                         | Bit 6                           | Bit 5        | Bit 4 | Bit 3  | Bit 2  | Bit 1  | Bit 0  | Register<br>on Page |  |  |

|--------|-------------------------------|---------------------------------|--------------|-------|--------|--------|--------|--------|---------------------|--|--|

| INTCON | GIE                           | PEIE                            | TMR0IE       | INTE  | IOCIE  | TMR0IF | INTF   | IOCIF  | 64                  |  |  |

| PIE1   | TMR1GIE                       | ADIE                            | _            | -     | SSP1IE | _      | TMR2IE | TMR1IE | 65                  |  |  |

| PIR1   | TMR1GIF                       | ADIF                            | _            | _     | SSP1IF | —      | TMR2IF | TMR1IF | 65                  |  |  |

| PR2    | Timer2 Module Period Register |                                 |              |       |        |        |        |        |                     |  |  |

| T2CON  | _                             | T2OUTPS<3:0> TMR2ON T2CKPS<1:0> |              |       |        |        |        |        | 153                 |  |  |

| TMR2   | Holding Reg                   | ister for the 8                 | -bit TMR2 Co | unt   |        |        |        |        | 151*                |  |  |

Legend: — = unimplemented location, read as '0'. Shaded cells are not used for Timer2 module.

Page provides register information.

### 21.6.6 I<sup>2</sup>C MASTER MODE TRANSMISSION

Transmission of a data byte, a 7-bit address or the other half of a 10-bit address is accomplished by simply writing a value to the SSPxBUF register. This action will set the Buffer Full flag bit, BF, and allow the Baud Rate Generator to begin counting and start the next transmission. Each bit of address/data will be shifted out onto the SDAx pin after the falling edge of SCLx is asserted. SCLx is held low for one Baud Rate Generator rollover count (TBRG). Data should be valid before SCLx is released high. When the SCLx pin is released high, it is held that way for TBRG. The data on the SDAx pin must remain stable for that duration and some hold time after the next falling edge of SCLx. After the eighth bit is shifted out (the falling edge of the eighth clock), the BF flag is cleared and the master releases SDAx. This allows the slave device being addressed to respond with an ACK bit during the ninth bit time if an address match occurred, or if data was received properly. The status of ACK is written into the ACKSTAT bit on the rising edge of the ninth clock. If the master receives an Acknowledge, the Acknowledge Status bit, ACKSTAT, is cleared. If not, the bit is set. After the ninth clock, the SSPxIF bit is set and the master clock (Baud Rate Generator) is suspended until the next data byte is loaded into the SSPxBUF, leaving SCLx low and SDAx unchanged (Figure 21-28).

After the write to the SSPxBUF, each bit of the address will be shifted out on the falling edge of SCLx until all seven address bits and the R/W bit are completed. On the falling edge of the eighth clock, the master will release the SDAx pin, allowing the slave to respond with an Acknowledge. On the falling edge of the ninth clock, the master will sample the SDAx pin to see if the address was recognized by a slave. The status of the ACK bit is loaded into the ACKSTAT Status bit of the SSPxCON2 register. Following the falling edge of the ninth clock transmission of the address, the SSPxIF is set, the BF flag is cleared and the Baud Rate Generator is turned off until another write to the SSPxBUF takes place, holding SCLx low and allowing SDAx to float.

#### 21.6.6.1 BF Status Flag

In Transmit mode, the BF bit of the SSPxSTAT register is set when the CPU writes to SSPxBUF and is cleared when all eight bits are shifted out.

### 21.6.6.2 WCOL Status Flag

If the user writes the SSPxBUF when a transmit is already in progress (i.e., SSPxSR is still shifting out a data byte), the WCOL bit is set and the contents of the buffer are unchanged (the write does not occur).

WCOL must be cleared by software before the next transmission.

### 21.6.6.3 ACKSTAT Status Flag

In Transmit mode, the ACKSTAT bit of the SSPxCON2 register is cleared when the slave has sent an Acknowledge ( $\overrightarrow{ACK} = 0$ ) and is set when the slave does not Acknowledge ( $\overrightarrow{ACK} = 1$ ). A slave sends an Acknowledge when it has recognized its address (including a general call), or when the slave has properly received its data.

21.6.6.4 Typical transmit sequence:

- 1. The user generates a Start condition by setting the SEN bit of the SSPxCON2 register.

- 2. SSPxIF is set by hardware on completion of the Start.

- 3. SSPxIF is cleared by software.

- 4. The MSSPx module will wait the required start time before any other operation takes place.

- 5. The user loads the SSPxBUF with the slave address to transmit.

- Address is shifted out the SDAx pin until all eight bits are transmitted. Transmission begins as soon as SSPxBUF is written to.

- 7. The MSSPx module shifts in the ACK bit from the slave device and writes its value into the ACKSTAT bit of the SSPxCON2 register.

- The MSSPx module generates an interrupt at the end of the ninth clock cycle by setting the SSPxIF bit.

- 9. The user loads the SSPxBUF with eight bits of data.

- 10. Data is shifted out the SDAx pin until all eight bits are transmitted.

- 11. The MSSPx module shifts in the ACK bit from the slave device and writes its value into the ACKSTAT bit of the SSPxCON2 register.

- 12. Steps 8-11 are repeated for all transmitted data bytes.

- 13. The user generates a Stop or Restart condition by setting the PEN or RSEN bits of the SSPxCON2 register. Interrupt is generated once the Stop/Restart condition is complete.

| R/W-x/u                                  | R/W-x/u                                                              | R/W-x/u              | R/W-x/u  | R/W-x/u                                               | R/W-x/u  | R/W-x/u  | R/W-x/u  |  |  |

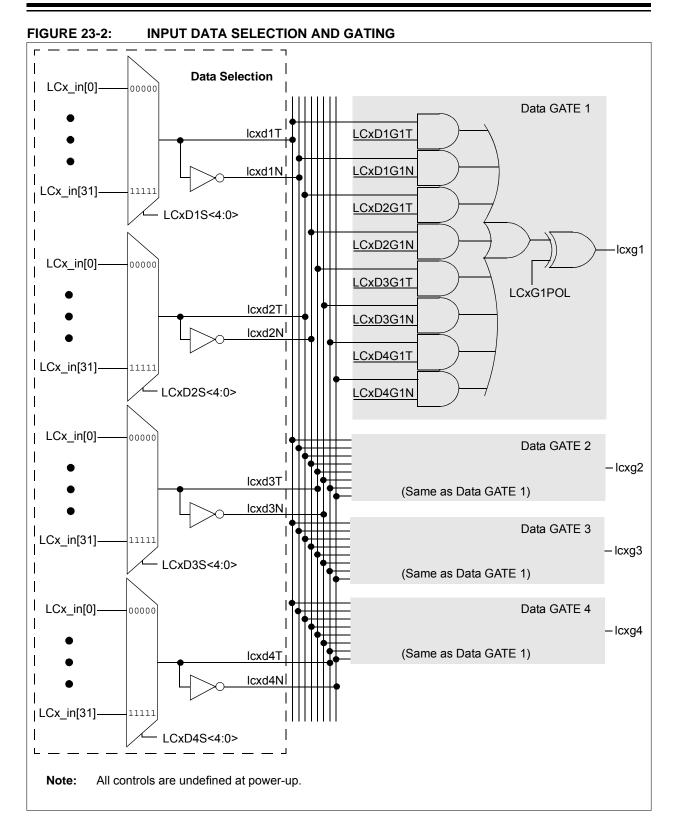

|------------------------------------------|----------------------------------------------------------------------|----------------------|----------|-------------------------------------------------------|----------|----------|----------|--|--|

| LCxG3D4T                                 | LCxG3D4N                                                             | LCxG3D3T             | LCxG3D3N | LCxG3D2T                                              | LCxG3D2N | LCxG3D1T | LCxG3D1N |  |  |

| bit 7                                    |                                                                      |                      | ·        |                                                       |          |          | bit      |  |  |

| Legend:                                  |                                                                      |                      |          |                                                       |          |          |          |  |  |

| R = Readable bit                         |                                                                      | W = Writable bit     |          | U = Unimplemented bit, read as '0'                    |          |          |          |  |  |

| u = Bit is unchanged<br>'1' = Bit is set |                                                                      | x = Bit is unknown   |          | -n/n = Value at POR and BOR/Value at all other Resets |          |          |          |  |  |

|                                          |                                                                      | '0' = Bit is cleared |          |                                                       |          |          |          |  |  |

|                                          |                                                                      |                      |          |                                                       |          |          |          |  |  |

| bit 7                                    | LCxG3D4T: Gate 3 Data 4 True (non-inverted) bit                      |                      |          |                                                       |          |          |          |  |  |

|                                          | 1 = Icxd4T is gated into lcxg3<br>0 = Icxd4T is not gated into lcxg3 |                      |          |                                                       |          |          |          |  |  |

| bit 6                                    | LCxG3D4N: Gate 3 Data 4 Negated (inverted) bit                       |                      |          |                                                       |          |          |          |  |  |

|                                          | 1 = lcxd4N is gated into lcxg3                                       |                      |          |                                                       |          |          |          |  |  |

|                                          | 0 = Icxd4N is not gated into Icxg3                                   |                      |          |                                                       |          |          |          |  |  |

| bit 5                                    | LCxG3D3T: Gate 3 Data 3 True (non-inverted) bit                      |                      |          |                                                       |          |          |          |  |  |

|                                          | 1 = Icxd3T is gated into Icxg3                                       |                      |          |                                                       |          |          |          |  |  |

|                                          | 0 = Icxd3T is not gated into Icxg3                                   |                      |          |                                                       |          |          |          |  |  |

| bit 4                                    | LCxG3D3N: Gate 3 Data 3 Negated (inverted) bit                       |                      |          |                                                       |          |          |          |  |  |

|                                          | 1 = lcxd3N is gated into lcxg3                                       |                      |          |                                                       |          |          |          |  |  |

|                                          | 0 = Icxd3N is not gated into Icxg3                                   |                      |          |                                                       |          |          |          |  |  |

| bit 3                                    | LCxG3D2T: Gate 3 Data 2 True (non-inverted) bit                      |                      |          |                                                       |          |          |          |  |  |

|                                          | 1 = lcxd2T is gated into lcxg3<br>0 = lcxd2T is not gated into lcxg3 |                      |          |                                                       |          |          |          |  |  |

| bit 2                                    | LCxG3D2N: Gate 3 Data 2 Negated (inverted) bit                       |                      |          |                                                       |          |          |          |  |  |

|                                          | 1 = lcxd2N is gated into lcxg3                                       |                      |          |                                                       |          |          |          |  |  |

|                                          | 0 = lcxd2N is not gated into lcxg3                                   |                      |          |                                                       |          |          |          |  |  |

| bit 1                                    | LCxG3D1T: Gate 3 Data 1 True (non-inverted) bit                      |                      |          |                                                       |          |          |          |  |  |

|                                          | 1 = Icxd1T is gated into Icxg3                                       |                      |          |                                                       |          |          |          |  |  |

|                                          | 0 = Icxd1T is not gated into Icxg3                                   |                      |          |                                                       |          |          |          |  |  |

| bit 0                                    | LCxG3D1N: Gate 3 Data 1 Negated (inverted) bit                       |                      |          |                                                       |          |          |          |  |  |

|                                          | 1 = lcxd1N is gated into lcxg3<br>0 = lcxd1N is not gated into lcxg3 |                      |          |                                                       |          |          |          |  |  |

|                                          | 0 = ICX01N IS                                                        | not dated into       | ICX03    |                                                       |          |          |          |  |  |

## REGISTER 23-7: CLCxGLS2: GATE 3 LOGIC SELECT REGISTER

## 24.0 NUMERICALLY CONTROLLED OSCILLATOR (NCO) MODULE

The Numerically Controlled Oscillator (NCOx) module is a timer that uses the overflow from the addition of an increment value to divide the input frequency. The advantage of the addition method over simple counter driven timer is that the resolution of division does not vary with the divider value. The NCOx is most useful for applications that require frequency accuracy and fine resolution at a fixed duty cycle.

Features of the NCOx include:

- 16-bit increment function

- Fixed Duty Cycle (FDC) mode

- Pulse Frequency (PF) mode

- Output pulse width control

- Multiple clock input sources

- Output polarity control

- Interrupt capability

Figure 24-1 is a simplified block diagram of the NCOx module.

## 24.1 NCOx Operation

The NCOx operates by repeatedly adding a fixed value to an accumulator. Additions occur at the input clock rate. The accumulator will overflow with a carry periodically, which is the raw NCOx output (NCO\_overflow). This effectively reduces the input clock by the ratio of the addition value to the maximum accumulator value. See Equation 24-1.

The NCOx output can be further modified by stretching the pulse or toggling a flip-flop. The modified NCOx output is then distributed internally to other peripherals and optionally output to a pin. The accumulator overflow also generates an interrupt (NCO\_interrupt).

The NCOx period changes in discrete steps to create an average frequency. This output depends on the ability of the receiving circuit (i.e., CWG or external resonant converter circuitry) to average the NCOx output to reduce uncertainty.

## 24.1.1 NCOx CLOCK SOURCES

Clock sources available to the NCOx include:

- HFINTOSC

- Fosc

- LC1\_out

- CLKIN pin

The NCOx clock source is selected by configuring the NxCKS<2:0> bits in the NCOxCLK register.

## EQUATION 24-1:

FOVERFLOW= <u>NCO Clock Frequency × Increment Value</u>

$2^n$

n = Accumulator width in bits

### 24.1.2 ACCUMULATOR

The accumulator is a 20-bit register. Read and write access to the accumulator is available through three registers:

- NCOxACCL

- NCOxACCH

- NCOxACCU

### 24.1.3 ADDER

The NCOx adder is a full adder, which operates independently from the system clock. The addition of the previous result and the increment value replaces the accumulator value on the rising edge of each input clock.

### 24.1.4 INCREMENT REGISTERS

The increment value is stored in two 8-bit registers making up a 16-bit increment. In order of LSB to MSB they are:

- NCOxINCL

- NCOxINCH

When the NCO module is enabled, the NCOxINCH should be written first, then the NCOxINCL register. Writing to the NCOxINCL register initiates the increment buffer registers to be loaded simultaneously on the second rising edge of the NCOx\_clk signal.

The registers are readable and writable. The increment registers are double-buffered to allow value changes to be made without first disabling the NCOx module.

When the NCO module is disabled, the increment buffers are loaded immediately after a write to the increment registers.

Note: The increment buffer registers are not user-accessible.

## 28.4 AC Characteristics

Timing Parameter Symbology has been created with one of the following formats:

- 1. TppS2ppS

- 2. TppS

| Т                                     |                                            |     |                |  |  |  |  |

|---------------------------------------|--------------------------------------------|-----|----------------|--|--|--|--|

| F                                     | Frequency                                  | Т   | Time           |  |  |  |  |

| Lowerc                                | Lowercase letters (pp) and their meanings: |     |                |  |  |  |  |

| рр                                    |                                            |     |                |  |  |  |  |

| сс                                    | CCP1                                       | osc | CLKIN          |  |  |  |  |

| ck                                    | CLKOUT                                     | rd  | RD             |  |  |  |  |

| CS                                    | CS                                         | rw  | RD or WR       |  |  |  |  |

| di                                    | SDIx                                       | sc  | SCKx           |  |  |  |  |

| do                                    | SDO                                        | ss  | SS             |  |  |  |  |

| dt                                    | Data in                                    | tO  | TOCKI          |  |  |  |  |

| io                                    | I/O PORT                                   | t1  | T1CKI          |  |  |  |  |

| mc                                    | MCLR                                       | wr  | WR             |  |  |  |  |

| Uppercase letters and their meanings: |                                            |     |                |  |  |  |  |

| S                                     |                                            |     |                |  |  |  |  |

| F                                     | Fall                                       | Р   | Period         |  |  |  |  |

| Н                                     | High                                       | R   | Rise           |  |  |  |  |

| I                                     | Invalid (High-impedance)                   | V   | Valid          |  |  |  |  |

| L                                     | Low                                        | Z   | High-impedance |  |  |  |  |

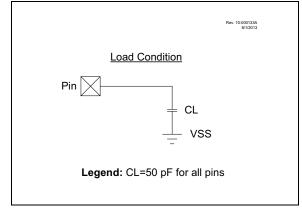

### FIGURE 28-4: LOAD CONDITIONS

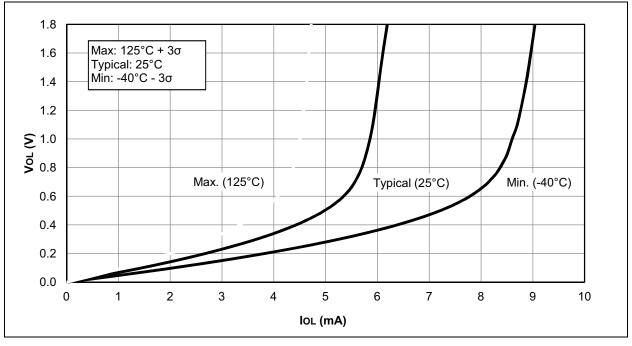

## 29.0 DC AND AC CHARACTERISTICS GRAPHS AND CHARTS

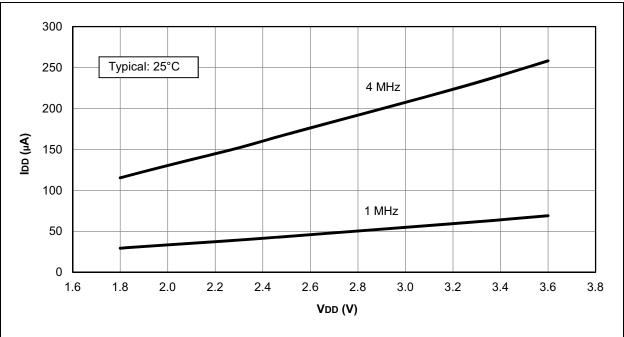

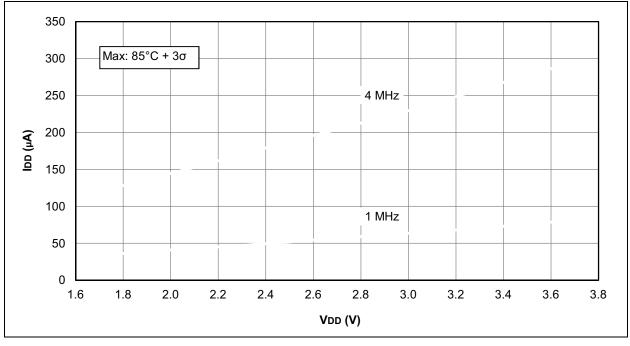

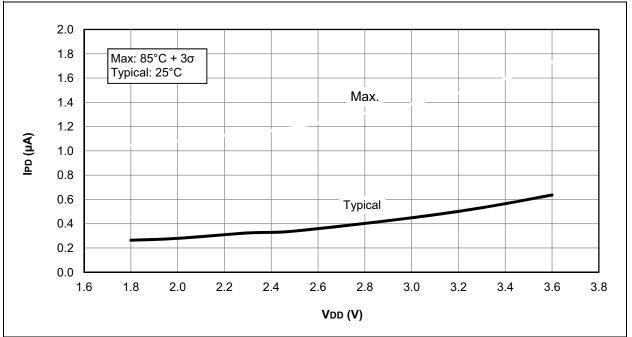

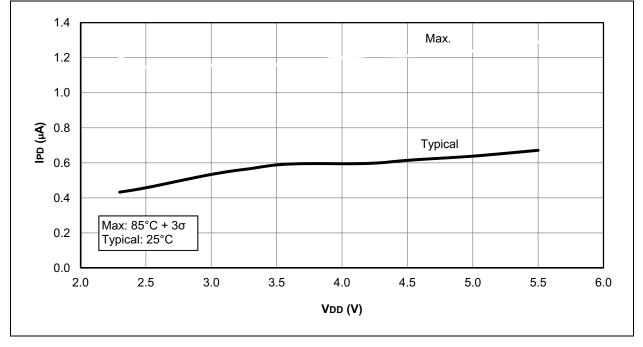

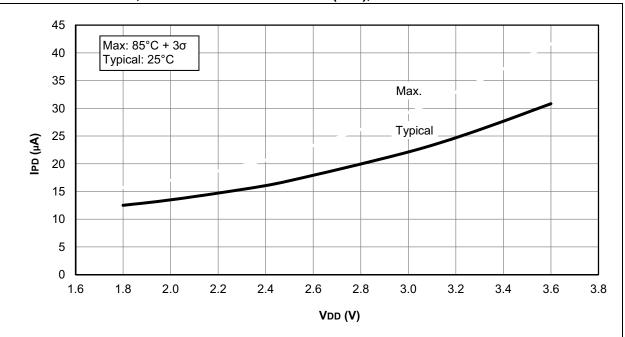

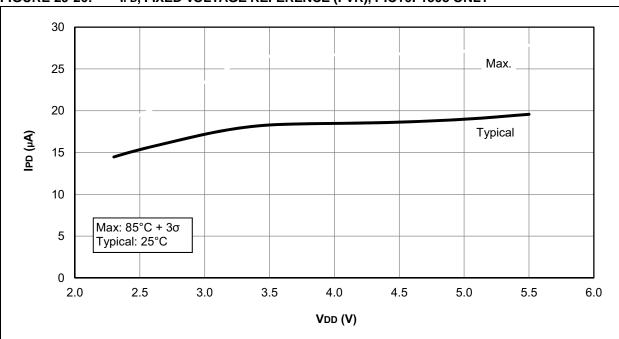

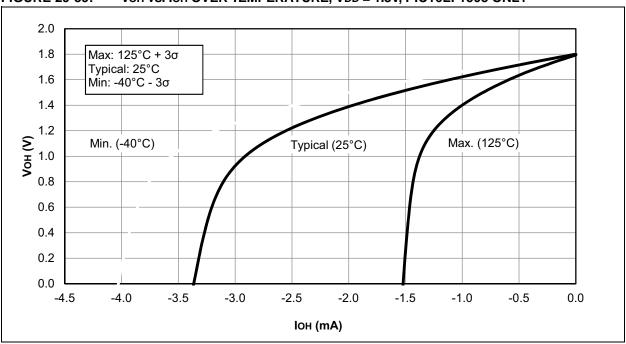

The graphs and tables provided in this section are for design guidance and are not tested.

In some graphs or tables, the data presented are **outside specified operating range** (i.e., outside specified VDD range). This is for **information only** and devices are ensured to operate properly only within the specified range.

**Note:** The graphs and tables provided following this note are a statistical summary based on a limited number of samples and are provided for informational purposes only. The performance characteristics listed herein are not tested or guaranteed. In some graphs or tables, the data presented may be outside the specified operating range (e.g., outside specified power supply range) and therefore, outside the warranted range.

"Typical" represents the mean of the distribution at 25°C. "MAXIMUM", "Max.", "MINIMUM" or "Min." represents (mean +  $3\sigma$ ) or (mean -  $3\sigma$ ) respectively, where  $\sigma$  is a standard deviation, over each temperature range.

FIGURE 29-6: IDD MAXIMUM, EXTERNAL CLOCK (ECM), MEDIUM POWER MODE, PIC16LF1503 ONLY

FIGURE 29-26: IPD, FIXED VOLTAGE REFERENCE (FVR), PIC16F1503 ONLY

FIGURE 29-39: VOH vs. IOH OVER TEMPERATURE, VDD = 1.8V, PIC16LF1503 ONLY