# E·XFL

Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Details                    |                                                                            |

|----------------------------|----------------------------------------------------------------------------|

| Product Status             | Active                                                                     |

| Core Processor             | PIC                                                                        |

| Core Size                  | 8-Bit                                                                      |

| Speed                      | 20MHz                                                                      |

| Connectivity               | I <sup>2</sup> C, SPI                                                      |

| Peripherals                | Brown-out Detect/Reset, POR, PWM, WDT                                      |

| Number of I/O              | 11                                                                         |

| Program Memory Size        | 3.5KB (2K x 14)                                                            |

| Program Memory Type        | FLASH                                                                      |

| EEPROM Size                | -                                                                          |

| RAM Size                   | 128 x 8                                                                    |

| Voltage - Supply (Vcc/Vdd) | 1.8V ~ 3.6V                                                                |

| Data Converters            | A/D 8x10b                                                                  |

| Oscillator Type            | Internal                                                                   |

| Operating Temperature      | -40°C ~ 125°C (TA)                                                         |

| Mounting Type              | Surface Mount                                                              |

| Package / Case             | 16-VFQFN Exposed Pad                                                       |

| Supplier Device Package    | 16-QFN (3x3)                                                               |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic16lf1503-e-mg |

|                            |                                                                            |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

### 6.12 Determining the Cause of a Reset

Upon any Reset, multiple bits in the STATUS and PCON registers are updated to indicate the cause of the Reset. Table 6-3 and Table 6-4 show the Reset conditions of these registers.

| STKOVF | STKUNF | RWDT | RMCLR | RI | POR | BOR | то | PD | Condition                                                         |

|--------|--------|------|-------|----|-----|-----|----|----|-------------------------------------------------------------------|

| 0      | 0      | 1    | 1     | 1  | 0   | х   | 1  | 1  | Power-on Reset                                                    |

| 0      | 0      | 1    | 1     | 1  | 0   | x   | 0  | x  | Illegal, $\overline{\text{TO}}$ is set on $\overline{\text{POR}}$ |

| 0      | 0      | 1    | 1     | 1  | 0   | x   | x  | 0  | Illegal, PD is set on POR                                         |

| 0      | 0      | u    | 1     | 1  | u   | 0   | 1  | 1  | Brown-out Reset                                                   |

| u      | u      | 0    | u     | u  | u   | u   | 0  | u  | WDT Reset                                                         |

| u      | u      | u    | u     | u  | u   | u   | 0  | 0  | WDT Wake-up from Sleep                                            |

| u      | u      | u    | u     | u  | u   | u   | 1  | 0  | Interrupt Wake-up from Sleep                                      |

| u      | u      | u    | 0     | u  | u   | u   | u  | u  | MCLR Reset during normal operation                                |

| u      | u      | u    | 0     | u  | u   | u   | 1  | 0  | MCLR Reset during Sleep                                           |

| u      | u      | u    | u     | 0  | u   | u   | u  | u  | RESET Instruction Executed                                        |

| 1      | u      | u    | u     | u  | u   | u   | u  | u  | Stack Overflow Reset (STVREN = 1)                                 |

| u      | 1      | u    | u     | u  | u   | u   | u  | u  | Stack Underflow Reset (STVREN = 1)                                |

### TABLE 6-3: RESET STATUS BITS AND THEIR SIGNIFICANCE

### TABLE 6-4: RESET CONDITION FOR SPECIAL REGISTERS

| Condition                          |                       | STATUS<br>Register | PCON<br>Register |

|------------------------------------|-----------------------|--------------------|------------------|

| Power-on Reset                     | 0000h                 | 1 1000             | 00 110x          |

| MCLR Reset during normal operation | 0000h                 | u muumuu           | uu Ouuu          |

| MCLR Reset during Sleep            | 0000h                 | 1 Ouuu             | uu Ouuu          |

| WDT Reset                          | 0000h                 | 0 muumuu           | uu uuuu          |

| WDT Wake-up from Sleep             | PC + 1                | 0 Ouuu             | uu uuuu          |

| Brown-out Reset                    | 0000h                 | 1 luuu             | 00 11u0          |

| Interrupt Wake-up from Sleep       | PC + 1 <sup>(1)</sup> | 1 Ouuu             | uu uuuu          |

| RESET Instruction Executed         | 0000h                 | u uuuu             | uu u0uu          |

| Stack Overflow Reset (STVREN = 1)  | 0000h                 | u uuuu             | lu uuuu          |

| Stack Underflow Reset (STVREN = 1) | 0000h                 | u uuuu             | ul uuuu          |

**Legend:** u = unchanged, x = unknown, - = unimplemented bit, reads as '0'.

**Note 1:** When the wake-up is due to an interrupt and the Global Interrupt Enable bit (GIE) is set, the return address is pushed on the stack and PC is loaded with the interrupt vector (0004h) after execution of PC + 1.

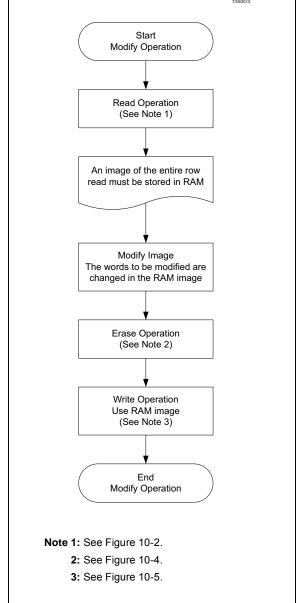

### 10.3 Modifying Flash Program Memory

When modifying existing data in a program memory row, and data within that row must be preserved, it must first be read and saved in a RAM image. Program memory is modified using the following steps:

- 1. Load the starting address of the row to be modified.

- 2. Read the existing data from the row into a RAM image.

- 3. Modify the RAM image to contain the new data to be written into program memory.

- 4. Load the starting address of the row to be rewritten.

- 5. Erase the program memory row.

- 6. Load the write latches with data from the RAM image.

- 7. Initiate a programming operation.

### FIGURE 10-7: FLASH PROGRAM MEMORY MODIFY FLOWCHART

### REGISTER 11-10: ANSELC: PORTC ANALOG SELECT REGISTER

| U-0                                     | U-0 | U-0               | U-0  | R/W-1/1                                               | R/W-1/1 | R/W-1/1 | R/W-1/1 |  |  |

|-----------------------------------------|-----|-------------------|------|-------------------------------------------------------|---------|---------|---------|--|--|

| _                                       | _   | —                 | _    | ANSC3                                                 | ANSC2   | ANSC1   | ANSC0   |  |  |

| bit 7                                   |     |                   |      | ·                                                     | •       | •       | bit 0   |  |  |

|                                         |     |                   |      |                                                       |         |         |         |  |  |

| Legend:                                 |     |                   |      |                                                       |         |         |         |  |  |

| R = Readable I                          | bit | W = Writable      | bit  | U = Unimplemented bit, read as '0'                    |         |         |         |  |  |

| u = Bit is unchanged x = Bit is unknown |     |                   | nown | -n/n = Value at POR and BOR/Value at all other Resets |         |         |         |  |  |

| '1' = Bit is set                        |     | '0' = Bit is clea | ared |                                                       |         |         |         |  |  |

|                                         |     |                   |      |                                                       |         |         |         |  |  |

bit 7-4 Unimplemented: Read as '0'

bit 3-0

ANSC<3:0>: Analog Select between Analog or Digital Function on pins RC<3:0>, respectively

- 1 = Analog input. Pin is assigned as analog input<sup>(1)</sup>. Digital input buffer disabled.

- 0 = Digital I/O. Pin is assigned to port or digital special function.

- **Note 1:** When setting a pin to an analog input, the corresponding TRIS bit must be set to Input mode in order to allow external control of the voltage on the pin.

### TABLE 11-6: SUMMARY OF REGISTERS ASSOCIATED WITH PORTC

| Name   | Bit 7 | Bit 6 | Bit 5  | Bit 4  | Bit 3  | Bit 2  | Bit 1  | Bit 0  | Register<br>on Page |

|--------|-------|-------|--------|--------|--------|--------|--------|--------|---------------------|

| ANSELC | —     |       |        | —      | ANSC3  | ANSC2  | ANSC1  | ANSC0  | 103                 |

| LATC   | _     | —     | LATC5  | LATC4  | LATC3  | LATC2  | LATC1  | LATC0  | 102                 |

| PORTC  | _     | —     | RC5    | RC4    | RC3    | RC2    | RC1    | RC0    | 102                 |

| TRISC  |       |       | TRISC5 | TRISC4 | TRISC3 | TRISC2 | TRISC1 | TRISC0 | 102                 |

Legend: x = unknown, u = unchanged, - = unimplemented locations read as '0'. Shaded cells are not used by PORTC.

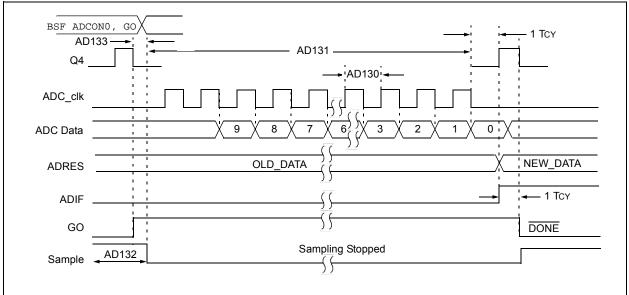

### 15.1 ADC Configuration

When configuring and using the ADC the following functions must be considered:

- · Port configuration

- · Channel selection

- ADC voltage reference selection

- ADC conversion clock source

- · Interrupt control

- Result formatting

### 15.1.1 PORT CONFIGURATION

The ADC can be used to convert both analog and digital signals. When converting analog signals, the I/O pin should be configured for analog by setting the associated TRIS and ANSEL bits. Refer to **Section 11.0 "I/O Ports"** for more information.

| Note: | Analog voltages on any pin that is defined |  |  |  |  |  |  |  |

|-------|--------------------------------------------|--|--|--|--|--|--|--|

|       | as a digital input may cause the input     |  |  |  |  |  |  |  |

|       | buffer to conduct excess current.          |  |  |  |  |  |  |  |

### 15.1.2 CHANNEL SELECTION

There are 11 channel selections available:

- AN<7:0> pins

- · Temperature Indicator

- FVR\_buffer1

The CHS bits of the ADCON0 register determine which channel is connected to the sample and hold circuit.

When changing channels, a delay (TACQ) is required before starting the next conversion. Refer to **Section 15.2.6 "ADC Conversion Procedure"** for more information.

### 15.1.3 ADC VOLTAGE REFERENCE

The ADC module uses a positive and a negative voltage reference. The positive reference is labeled ref+ and the negative reference is labeled ref-.

The positive voltage reference (ref+) is selected by the ADPREF bits in the ADCON1 register. The positive voltage reference source can be:

- VREF+ pin

- Vdd

The negative voltage reference (ref-) source is:

Vss

### 15.1.4 CONVERSION CLOCK

The source of the conversion clock is software selectable via the ADCS bits of the ADCON1 register. There are seven possible clock options:

- Fosc/2

- · Fosc/4

- Fosc/8

- Fosc/16

- Fosc/32

- Fosc/64

- FRC (internal RC oscillator)

The time to complete one bit conversion is defined as TAD. One full 10-bit conversion requires 11.5 TAD periods as shown in Figure 15-2.

For correct conversion, the appropriate TAD specification must be met. Refer to the ADC conversion requirements in **Section 28.0 "Electrical Specifications"** for more information. Table 15-1 gives examples of appropriate ADC clock selections.

| Note: | Unless using the FRC, any changes in the |  |  |  |  |  |  |

|-------|------------------------------------------|--|--|--|--|--|--|

|       | system clock frequency will change the   |  |  |  |  |  |  |

|       | ADC clock frequency, which may           |  |  |  |  |  |  |

|       | adversely affect the ADC result.         |  |  |  |  |  |  |

#### 21.5.4 SLAVE MODE 10-BIT ADDRESS RECEPTION

This section describes a standard sequence of events for the MSSP module configured as an  $I^2C$  slave in 10-bit Addressing mode.

Figure 21-20 is used as a visual reference for this description.

This is a step by step process of what must be done by slave software to accomplish  $I^2C$  communication.

- 1. Bus starts idle.

- Master sends Start condition; S bit of SSPxSTAT is set; SSPxIF is set if interrupt on Start detect is enabled.

- Master sends matching high address with R/W bit clear; UA bit of the SSPxSTAT register is set.

- 4. Slave sends ACK and SSPxIF is set.

- 5. Software clears the SSPxIF bit.

- 6. Software reads received address from SSPxBUF clearing the BF flag.

- 7. Slave loads low address into SSPxADD, releasing SCLx.

- 8. Master sends matching low address byte to the slave; UA bit is set.

**Note:** Updates to the SSPxADD register are not allowed until after the ACK sequence.

9. Slave sends ACK and SSPxIF is set.

**Note:** If the low address does not match, SSPxIF and UA are still set so that the slave software can set SSPxADD back to the high address. BF is not set because there is no match. CKP is unaffected.

- 10. Slave clears SSPxIF.

- 11. Slave reads the received matching address from SSPxBUF clearing BF.

- 12. Slave loads high address into SSPxADD.

- 13. Master clocks a data byte to the slave and clocks out the slaves ACK on the ninth SCLx pulse; SSPxIF is set.

- 14. If SEN bit of SSPxCON2 is set, CKP is cleared by hardware and the clock is stretched.

- 15. Slave clears SSPxIF.

- 16. Slave reads the received byte from SSPxBUF clearing BF.

- 17. If SEN is set the slave sets CKP to release the SCLx.

- 18. Steps 13-17 repeat for each received byte.

- 19. Master sends Stop to end the transmission.

### 21.5.5 10-BIT ADDRESSING WITH ADDRESS OR DATA HOLD

Reception using 10-bit addressing with AHEN or DHEN set is the same as with 7-bit modes. The only difference is the need to update the SSPxADD register using the UA bit. All functionality, specifically when the CKP bit is cleared and SCLx line is held low are the same. Figure 21-21 can be used as a reference of a slave in 10-bit addressing with AHEN set.

Figure 21-22 shows a standard waveform for a slave transmitter in 10-bit Addressing mode.

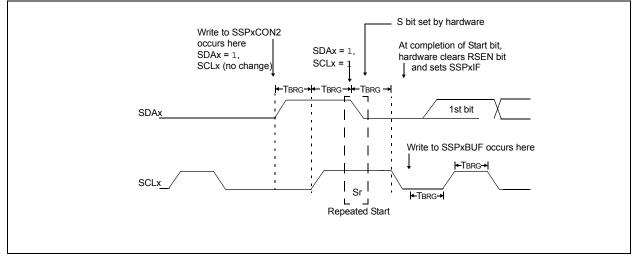

### 21.6.5 I<sup>2</sup>C MASTER MODE REPEATED START CONDITION TIMING

A Repeated Start condition (Figure 21-27) occurs when the RSEN bit of the SSPxCON2 register is programmed high and the master state machine is no longer active. When the RSEN bit is set, the SCLx pin is asserted low. When the SCLx pin is sampled low, the Baud Rate Generator is loaded and begins counting. The SDAx pin is released (brought high) for one Baud Rate Generator count (TBRG). When the Baud Rate Generator times out, if SDAx is sampled high, the SCLx pin will be deasserted (brought high). When SCLx is sampled high, the Baud Rate Generator is reloaded and begins counting. SDAx and SCLx must be sampled high for one TBRG. This action is then followed by assertion of the SDAx pin (SDAx = 0) for one TBRG while SCLx is high. SCLx is asserted low. Following this, the RSEN bit of the SSPxCON2 register will be automatically cleared and the Baud Rate Generator will not be reloaded, leaving the SDAx pin held low. As soon as a Start condition is detected on the SDAx and SCLx pins, the S bit of the SSPxSTAT register will be set. The SSPxIF bit will not be set until the Baud Rate Generator has timed out.

- Note 1: If RSEN is programmed while any other event is in progress, it will not take effect.

- **2:** A bus collision during the Repeated Start condition occurs if:

- SDAx is sampled low when SCLx goes from low-to-high.

- SCLx goes low before SDAx is asserted low. This may indicate that another master is attempting to transmit a data '1'.

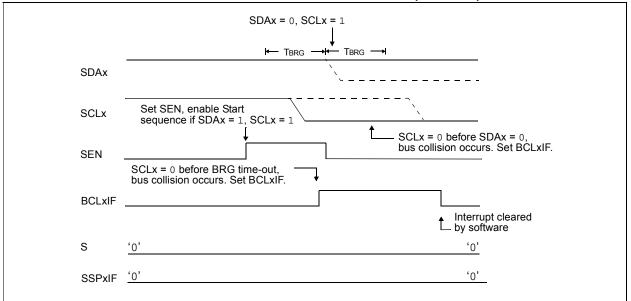

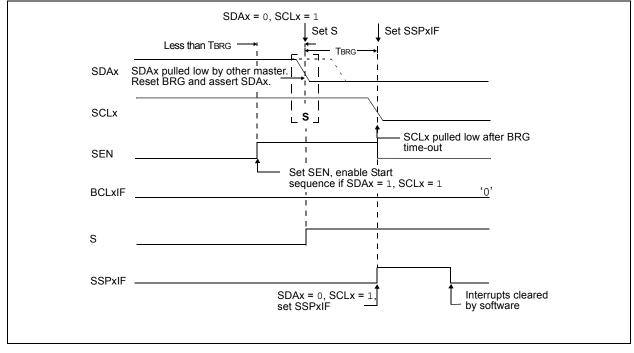

### FIGURE 21-27: REPEAT START CONDITION WAVEFORM

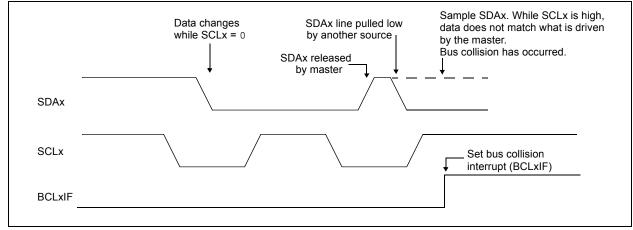

### 21.6.13.3 Bus Collision During a Stop Condition

Bus collision occurs during a Stop condition if:

- a) After the SDAx pin has been deasserted and allowed to float high, SDAx is sampled low after the BRG has timed out (Case 1).

- b) After the SCLx pin is deasserted, SCLx is sampled low before SDAx goes high (Case 2).

The Stop condition begins with SDAx asserted low. When SDAx is sampled low, the SCLx pin is allowed to float. When the pin is sampled high (clock arbitration), the Baud Rate Generator is loaded with SSPxADD and counts down to 0. After the BRG times out, SDAx is sampled. If SDAx is sampled low, a bus collision has occurred. This is due to another master attempting to drive a data '0' (Figure 21-38). If the SCLx pin is sampled low before SDAx is allowed to float high, a bus collision occurs. This is another case of another master attempting to drive a data '0' (Figure 21-39).

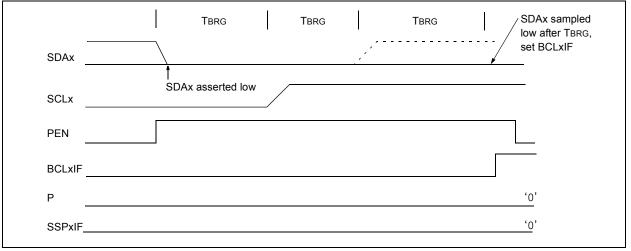

### FIGURE 21-38: BUS COLLISION DURING A STOP CONDITION (CASE 1)

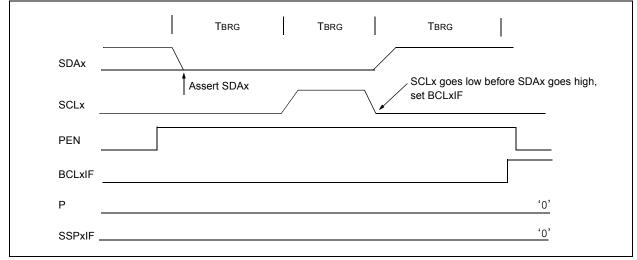

### FIGURE 21-39: BUS COLLISION DURING A STOP CONDITION (CASE 2)

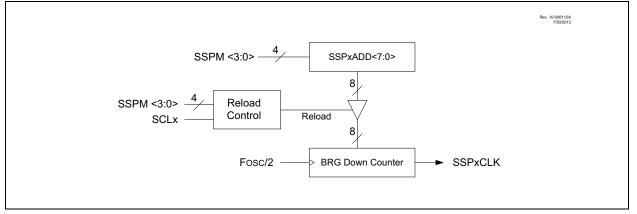

### 21.7 BAUD RATE GENERATOR

The MSSP module has a Baud Rate Generator available for clock generation in both I<sup>2</sup>C and SPI Master modes. The Baud Rate Generator (BRG) reload value is placed in the SSPxADD register (Register 21-6). When a write occurs to SSPxBUF, the Baud Rate Generator will automatically begin counting down.

Once the given operation is complete, the internal clock will automatically stop counting and the clock pin will remain in its last state.

An internal signal "Reload" in Figure 21-40 triggers the value from SSPxADD to be loaded into the BRG counter. This occurs twice for each oscillation of the

module clock line. The logic dictating when the reload signal is asserted depends on the mode the MSSP is being operated in.

Table 21-4 demonstrates clock rates based on instruction cycles and the BRG value loaded into SSPxADD.

### **EQUATION 21-1:**

$$FCLOCK = \frac{FOSC}{(SSPxADD + 1)(4)}$$

### FIGURE 21-40: BAUD RATE GENERATOR BLOCK DIAGRAM

**Note:** Values of 0x00, 0x01 and 0x02 are not valid for SSPxADD when used as a Baud Rate Generator for I<sup>2</sup>C. This is an implementation limitation.

### TABLE 21-4: MSSP CLOCK RATE W/BRG

| Fosc   | Fcy   | BRG Value | FcLocк<br>(Two Rollovers of BRG) |  |  |

|--------|-------|-----------|----------------------------------|--|--|

| 16 MHz | 4 MHz | 09h       | 400 kHz                          |  |  |

| 16 MHz | 4 MHz | 0Ch       | 308 kHz                          |  |  |

| 16 MHz | 4 MHz | 27h       | 100 kHz                          |  |  |

| 4 MHz  | 1 MHz | 09h       | 100 kHz                          |  |  |

**Note:** Refer to the I/O port electrical and timing specifications in Table 28-9 and Figure 28-7 to ensure the system is designed to support the I/O timing requirements.

### 21.8 Register Definitions: MSSP Control

| R/W-0/0          | R/W-0/0                                                                                                                                                                                        | R-0/0                                    | R-0/0                                    | R-0/0               | R-0/0                                 | R-0/0               | R-0/0         |  |  |  |

|------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------|------------------------------------------|---------------------|---------------------------------------|---------------------|---------------|--|--|--|

| SMP              | CKE                                                                                                                                                                                            | D/A                                      | Р                                        | S                   | R/W                                   | UA                  | BF            |  |  |  |

| bit 7            |                                                                                                                                                                                                |                                          |                                          |                     |                                       |                     | bit (         |  |  |  |

|                  |                                                                                                                                                                                                |                                          |                                          |                     |                                       |                     |               |  |  |  |

| Legend:          |                                                                                                                                                                                                |                                          |                                          |                     |                                       |                     |               |  |  |  |

| R = Readable b   | bit                                                                                                                                                                                            | W = Writable b                           | it                                       | •                   | nented bit, read as                   |                     |               |  |  |  |

| u = Bit is uncha | nged                                                                                                                                                                                           | x = Bit is unkno                         |                                          | -n/n = Value a      | t POR and BOR/V                       | alue at all other I | Resets        |  |  |  |

| '1' = Bit is set |                                                                                                                                                                                                | '0' = Bit is clea                        | red                                      |                     |                                       |                     |               |  |  |  |

| bit 7            | SPI Master mo                                                                                                                                                                                  |                                          |                                          |                     |                                       |                     |               |  |  |  |

|                  | 0 = Input data                                                                                                                                                                                 | sampled at end o sampled at midd         |                                          |                     |                                       |                     |               |  |  |  |

|                  | SPI Slave mod<br>SMP must be                                                                                                                                                                   | <u>de:</u><br>cleared when SP            | I is used in Slav                        | ve mode             |                                       |                     |               |  |  |  |

|                  |                                                                                                                                                                                                | or Slave mode:<br>control disabled       |                                          |                     |                                       |                     |               |  |  |  |

|                  | 0 = Slew rate                                                                                                                                                                                  | control enabled                          |                                          |                     |                                       |                     |               |  |  |  |

| bit 6            | CKE: SPI Clo                                                                                                                                                                                   | ck Edge Select bi                        | t (SPI mode on                           | ly)                 |                                       |                     |               |  |  |  |

|                  | In SPI Master or Slave mode:                                                                                                                                                                   |                                          |                                          |                     |                                       |                     |               |  |  |  |

|                  | <ul> <li>1 = Transmit occurs on transition from active to Idle clock state</li> <li>0 = Transmit occurs on transition from Idle to active clock state</li> </ul>                               |                                          |                                          |                     |                                       |                     |               |  |  |  |

|                  |                                                                                                                                                                                                |                                          |                                          | ompliant with SM    | Bus specification                     |                     |               |  |  |  |

| bit 5            | D/A: Data/Address bit (I <sup>2</sup> C mode only)                                                                                                                                             |                                          |                                          |                     |                                       |                     |               |  |  |  |

|                  |                                                                                                                                                                                                | hat the last byte<br>hat the last byte i |                                          |                     |                                       |                     |               |  |  |  |

| bit 4            | P: Stop bit                                                                                                                                                                                    |                                          |                                          |                     |                                       |                     |               |  |  |  |

|                  | (I <sup>2</sup> C mode only. This bit is cleared when the MSSP module is disabled, SSPEN is cleared.)<br>1 = Indicates that a Stop bit has been detected last (this bit is '0' on Reset)       |                                          |                                          |                     |                                       |                     |               |  |  |  |

|                  |                                                                                                                                                                                                | as not detected la                       |                                          | last (this bit is ' | 0' on Reset)                          |                     |               |  |  |  |

| bit 3            | S: Start bit                                                                                                                                                                                   |                                          |                                          |                     |                                       |                     |               |  |  |  |

|                  | (I <sup>2</sup> C mode only. This bit is cleared when the MSSP module is disabled, SSPEN is cleared.)                                                                                          |                                          |                                          |                     |                                       |                     |               |  |  |  |

|                  | <ul> <li>1 = Indicates that a Start bit has been detected last (this bit is '0' on Reset)</li> <li>0 = Start bit was not detected last</li> </ul>                                              |                                          |                                          |                     |                                       |                     |               |  |  |  |

| bit 2            | <b>R/W</b> : Read/Write bit information (I <sup>2</sup> C mode only)<br>This bit holds the R/W bit information following the last address match. This bit is only valid from the address match |                                          |                                          |                     |                                       |                     |               |  |  |  |

|                  | This bit holds t<br>to the next Sta<br>In $I^2C$ Slave m<br>1 = Read<br>0 = Write                                                                                                              | art bit, Stop bit, or                    | atio <u>n foll</u> owing<br>not ACK bit. | the last address    | match. This bit is c                  | nly valid from the  | address match |  |  |  |

|                  | 0 = vvnte<br>In I <sup>2</sup> C Master mode:                                                                                                                                                  |                                          |                                          |                     |                                       |                     |               |  |  |  |

|                  |                                                                                                                                                                                                | is not in progress                       |                                          |                     |                                       |                     |               |  |  |  |

| 1-14-A           | -                                                                                                                                                                                              |                                          |                                          |                     | will indicate if the                  | MSSP is in Idle n   | node.         |  |  |  |

| bit 1            |                                                                                                                                                                                                | ddress bit (10-bit<br>bat the user need  |                                          |                     | SSPxADD register                      |                     |               |  |  |  |

|                  |                                                                                                                                                                                                | oes not need to b                        | •                                        |                     |                                       |                     |               |  |  |  |

| bit 0            | BF: Buffer Ful                                                                                                                                                                                 | l Status bit                             |                                          |                     |                                       |                     |               |  |  |  |

|                  |                                                                                                                                                                                                | and I <sup>2</sup> C modes):             | 15 in 6 11                               |                     |                                       |                     |               |  |  |  |

|                  |                                                                                                                                                                                                | omplete, SSPxBL<br>ot complete, SSP      |                                          |                     |                                       |                     |               |  |  |  |

|                  | 0 = Receive h                                                                                                                                                                                  |                                          | ABOF IS empty                            |                     |                                       |                     |               |  |  |  |

|                  | 1 = Data trans                                                                                                                                                                                 | mit in progress (o                       |                                          |                     | top bits), SSPxBU<br>p bits), SSPxBUF |                     |               |  |  |  |

### REGISTER 21-1: SSPxSTAT: SSP STATUS REGISTER

### REGISTER 21-2: SSPxCON1: SSP CONTROL REGISTER 1

| R/C/HS-0/0        | R/C/HS-0/0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | R/W-0/0                                                                                                                                               | R/W-0/0                                                                                                                                                                                     | R/W-0/0                                                                                  | R/W-0/0              | R/W-0/0                | R/W-0/0         |  |

|-------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------|----------------------|------------------------|-----------------|--|

| WCOL              | SSPOV <sup>(1)</sup>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | SSPEN                                                                                                                                                 | CKP                                                                                                                                                                                         |                                                                                          | SSPI                 | M<3:0>                 |                 |  |

| bit 7             | •                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | ·                                                                                                                                                     |                                                                                                                                                                                             | ·                                                                                        |                      |                        | bit             |  |

|                   |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |                                                                                                                                                       |                                                                                                                                                                                             |                                                                                          |                      |                        |                 |  |

| Legend:           |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |                                                                                                                                                       |                                                                                                                                                                                             |                                                                                          |                      |                        |                 |  |

| R = Readable bi   | t                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | W = Writable bit                                                                                                                                      |                                                                                                                                                                                             | U = Unimplement                                                                          | ted bit, read as '0' |                        |                 |  |

| u = Bit is unchar | nged                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | x = Bit is unknow                                                                                                                                     | 'n                                                                                                                                                                                          | -n/n = Value at Po                                                                       | OR and BOR/Value     | e at all other Resets  |                 |  |

| '1' = Bit is set  |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | '0' = Bit is cleared                                                                                                                                  | b                                                                                                                                                                                           | HS = Bit is set by                                                                       | hardware             | C = User cleared       |                 |  |

| bit 7             | 0 = No collisior<br>Slave mode:                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | he SSPxBUF regist<br>ו<br>UF register is writter                                                                                                      | ·                                                                                                                                                                                           | d while the I <sup>2</sup> C condi<br>smitting the previous                              |                      |                        | to be started   |  |

| bit 6             | <ul> <li>0 = No collision</li> <li>SSPOV: Receive Overflow Indicator bit<sup>(1)</sup> <ul> <li>In SPI mode:</li> <li>1 = A new byte is received while the SSPxBUF register is still holding the previous data. In case of overflow, the data in SSF Overflow can only occur in Slave mode. In Slave mode, the user must read the SSPxBUF, even if only transmitting da setting overflow. In Master mode, the overflow bit is not set since each new reception (and transmission) is initiated by w SSPxBUF register (must be cleared in software).</li> <li>0 = No overflow</li> <li>In I<sup>2</sup>C mode:</li> <li>1 = A byte is received while the SSPxBUF register is still holding the previous byte. SSPOV is a "don't care" in Transmitting the cleared in software).</li> <li>0 = No overflow</li> </ul> </li> </ul> |                                                                                                                                                       |                                                                                                                                                                                             |                                                                                          |                      |                        |                 |  |

| bit 5             | In both modes, w<br>In <u>SPI mode:</u><br>1 = Enables set<br>0 = Disables set<br>In I <sup>2</sup> C mode:<br>1 = Enables the                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | rial port and configue<br>erial port and configue<br>e serial port and config                                                                         | e pins must be pr<br>res SCKx, SDOx,<br>jures these pins<br>figures the SDAx a                                                                                                              | x and SCLx pins as the source of the serial port pins <sup>(3)</sup>                     |                      |                        |                 |  |

| bit 4             | <ul> <li>0 = Disables serial port and configures these pins as I/O port pins</li> <li>CKP: Clock Polarity Select bit <ul> <li>In SPI mode:</li> </ul> </li> <li>1 = Idle state for clock is a high level</li> <li>0 = Idle state for clock is a low level <ul> <li>In I<sup>2</sup>C Slave mode:</li> <li>SCLx release control</li> <li>1 = Enable clock</li> <li>0 = Holds clock low (clock stretch). (Used to ensure data setup time.)</li> <li>In I<sup>2</sup>C Master mode:</li> <li>Unused in this mode</li> </ul> </li> </ul>                                                                                                                                                                                                                                                                                           |                                                                                                                                                       |                                                                                                                                                                                             |                                                                                          |                      |                        |                 |  |

| bit 3-0           | 0000 = SPI Mas<br>0001 = SPI Mas<br>0010 = SPI Mas<br>0010 = SPI Mas<br>0100 = SPI Slav<br>0101 = SPI Slav<br>0110 = I <sup>2</sup> C Slave<br>0110 = I <sup>2</sup> C Slave<br>1000 = I <sup>2</sup> C Mast<br>1001 = Reservee<br>1010 = SPI Mas<br>1011 = I <sup>2</sup> C firmw<br>1100 = Reservee<br>1101 = Reservee<br>1101 = Reservee<br>1101 = Reservee<br>1100 = Reservee                                                                                                                                                                                                                                                                                                                                                                                                                                              | e mode, 7-bit addre<br>e mode, 10-bit addr<br>er mode, clock = Fr<br>d<br>ter mode, clock = F<br>vare controlled Mas<br>d<br>d<br>e mode, 7-bit addre | osc/4<br>osc/16<br>osc/64<br>2_match/2<br>XKx pin, <u>SS</u> pin c<br>SKx pin, <u>SS</u> pin c<br>ss<br>ess<br>osc/(4 * (SSPxAl<br>osc/(4 * (SSPxAl<br>ter mode (Slave<br>ss with Start and | ontrol enabled<br>ontrol disabled, SSx<br>DD+1)) <sup>(4)</sup><br>DD+1)) <sup>(5)</sup> | nabled               | ) pin                  |                 |  |

| 2: W<br>3: W      | Master mode, the ov<br>hen enabled, these p<br>hen enabled, the SD/<br>SPXADD values of 0,                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | erflow bit is not set<br>ins must be proper<br>Ax and SCLx pins r                                                                                     | since each new<br>ly configured as i<br>nust be configure                                                                                                                                   | reception (and transi<br>input or output.<br>ed as inputs.                               |                      | I by writing to the SS | PxBUF register. |  |

- SSPxADD values of 0, 1 or 2 are not supported for I<sup>2</sup>C mode.

SSPxADD value of '0' is not supported. Use SSPM = 0000 instead.

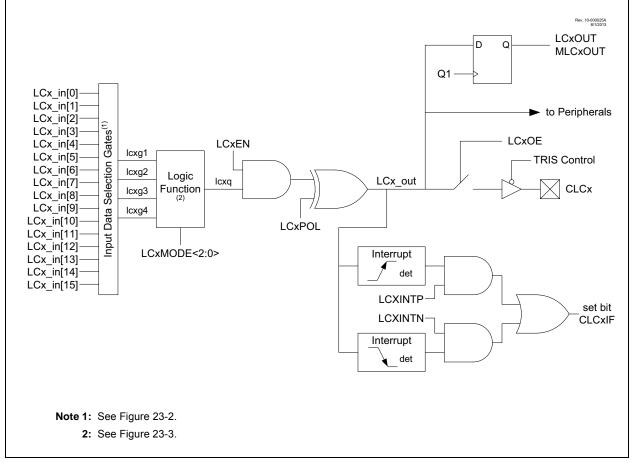

### 23.0 CONFIGURABLE LOGIC CELL (CLC)

The Configurable Logic Cell (CLCx) provides programmable logic that operates outside the speed limitations of software execution. The logic cell takes up to 16 input signals, and through the use of configurable gates, reduces the 16 inputs to four logic lines that drive one of eight selectable single-output logic functions.

Input sources are a combination of the following:

- · I/O pins

- Internal clocks

- · Peripherals

- Register bits

The output can be directed internally to peripherals and to an output pin.

Refer to Figure 23-1 for a simplified diagram showing signal flow through the CLCx.

Possible configurations include:

- Combinatorial Logic

- AND

- NAND

- AND-OR

- AND-OR-INVERT

- OR-XOR

- OR-XNOR

- Latches

- S-R

- Clocked D with Set and Reset

- Transparent D with Set and Reset

- Clocked J-K with Reset

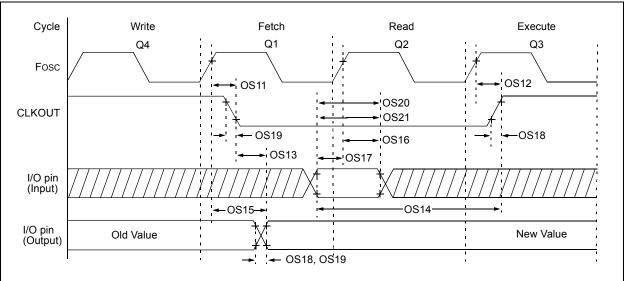

| TABLE 28-9: | CLKOUT AND I/O TIMING PARAMETERS |

|-------------|----------------------------------|

|-------------|----------------------------------|

| Standard Operating Conditions (unless otherwise stated) |          |                                                               |               |          |          |       |                                                                           |  |  |

|---------------------------------------------------------|----------|---------------------------------------------------------------|---------------|----------|----------|-------|---------------------------------------------------------------------------|--|--|

| Param.<br>No.                                           | Sym.     | Characteristic                                                | Min.          | Тур†     | Max.     | Units | Conditions                                                                |  |  |

| OS11                                                    | TosH2ckL | Fosc↑ to CLKOUT↓ <sup>(1)</sup>                               | _             | _        | 70       | ns    | $3.3V \le V\text{DD} \le 5.0V$                                            |  |  |

| OS12                                                    | TosH2ckH | Fosc↑ to CLKOUT↑ <sup>(1)</sup>                               | —             |          | 72       | ns    | $3.3V \le V\text{DD} \le 5.0V$                                            |  |  |

| OS13                                                    | TckL2ioV | CLKOUT↓ to Port out valid <sup>(1)</sup>                      | —             | -        | 20       | ns    |                                                                           |  |  |

| OS14                                                    | TioV2ckH | Port input valid before CLKOUT↑ <sup>(1)</sup>                | Tosc + 200 ns |          | _        | ns    |                                                                           |  |  |

| OS15                                                    | TosH2ioV | Fosc↑ (Q1 cycle) to Port out valid                            | —             | 50       | 70*      | ns    | $3.3V \le V\text{DD} \le 5.0V$                                            |  |  |

| OS16                                                    | TosH2iol | Fosc↑ (Q2 cycle) to Port input invalid<br>(I/O in setup time) | 50            | —        | —        | ns    | $3.3V \le V\text{DD} \le 5.0V$                                            |  |  |

| OS17                                                    | TioV2osH | Port input valid to Fosc↑ (Q2 cycle)<br>(I/O in setup time)   | 20            | —        | _        | ns    |                                                                           |  |  |

| OS18*                                                   | TioR     | Port output rise time                                         | _             | 40<br>15 | 72<br>32 | ns    | $VDD = 1.8V$ $3.3V \le VDD \le 5.0V$                                      |  |  |

| OS19*                                                   | TioF     | Port output fall time                                         | —             | 28<br>15 | 55<br>30 | ns    | $\begin{array}{l} VDD \mbox{=} 1.8V \\ 3.3V \le VDD \le 5.0V \end{array}$ |  |  |

| OS20*                                                   | Tinp     | INT pin input high or low time                                | 25            | —        | —        | ns    |                                                                           |  |  |

| OS21*                                                   | Tioc     | Interrupt-on-change new input level time                      | 25            | —        | —        | ns    |                                                                           |  |  |

\* These parameters are characterized but not tested.

$\dagger$  Data in "Typ" column is at 3.0V, 25°C unless otherwise stated.

Note 1: Measurements are taken in EXTRC mode where CLKOUT output is 4 x Tosc.

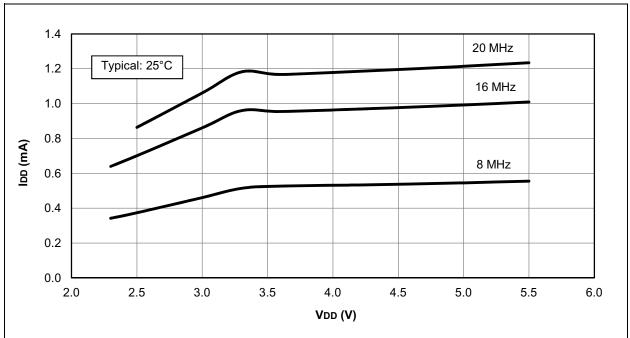

FIGURE 29-11: IDD TYPICAL, EXTERNAL CLOCK (ECH), HIGH-POWER MODE, PIC16F1503 ONLY

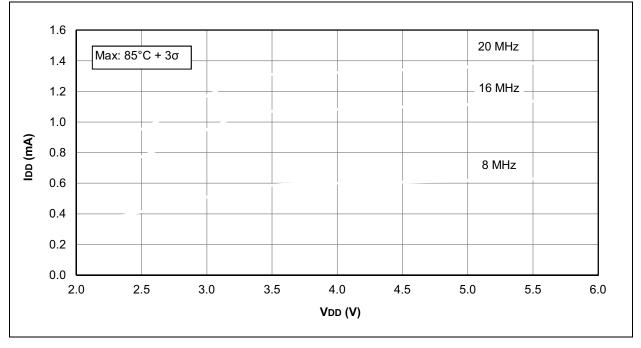

FIGURE 29-12: IDD MAXIMUM, EXTERNAL CLOCK (ECH), HIGH-POWER MODE, PIC16F1503 ONLY

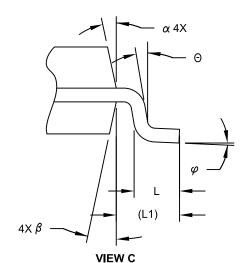

### 14-Lead Plastic Small Outline (SL) - Narrow, 3.90 mm Body [SOIC]

**Note:** For the most current package drawings, please see the Microchip Packaging Specification located at http://www.microchip.com/packaging

| Units                    |    | MILLIMETERS |     |      |

|--------------------------|----|-------------|-----|------|

| Dimension Limits         |    | MIN         | NOM | MAX  |

| Number of Pins           | N  | 14          |     |      |

| Pitch                    | е  | 1.27 BSC    |     |      |

| Overall Height           | A  | -           | -   | 1.75 |

| Molded Package Thickness | A2 | 1.25        | -   | -    |

| Standoff §               | A1 | 0.10        | -   | 0.25 |

| Overall Width            | E  | 6.00 BSC    |     |      |

| Molded Package Width     | E1 | 3.90 BSC    |     |      |

| Overall Length           | D  | 8.65 BSC    |     |      |

| Chamfer (Optional)       | h  | 0.25        | I   | 0.50 |

| Foot Length              | L  | 0.40        | -   | 1.27 |

| Footprint                | L1 | 1.04 REF    |     |      |

| Lead Angle               | Θ  | 0°          | II. | -    |

| Foot Angle               | φ  | 0°          | -   | 8°   |

| Lead Thickness           | С  | 0.10        | -   | 0.25 |

| Lead Width               | b  | 0.31        | -   | 0.51 |

| Mold Draft Angle Top     | α  | 5°          | -   | 15°  |

| Mold Draft Angle Bottom  | β  | 5°          | -   | 15°  |

#### Notes:

- 1. Pin 1 visual index feature may vary, but must be located within the hatched area.

- 2. § Significant Characteristic

- Dimension D does not include mold flash, protrusions or gate burrs, which shall not exceed 0.15 mm per end. Dimension E1 does not include interlead flash or protrusion, which shall not exceed 0.25 mm per side.

- Dimensioning and tolerancing per ASME Y14.5M BSC: Basic Dimension. Theoretically exact value shown without tolerances. REF: Reference Dimension, usually without tolerance, for information purposes only.

- 5. Datums A & B to be determined at Datum H.

Microchip Technology Drawing No. C04-065C Sheet 2 of 2

### 14-Lead Plastic Thin Shrink Small Outline (ST) - 4.4 mm Body [TSSOP]

**Note:** For the most current package drawings, please see the Microchip Packaging Specification located at http://www.microchip.com/packaging

|                          | Units | MILLIMETERS |      | S    |

|--------------------------|-------|-------------|------|------|

| Dimension Limits         |       | MIN         | NOM  | MAX  |

| Number of Pins           | N     | 14          |      |      |

| Pitch                    | е     | 0.65 BSC    |      |      |

| Overall Height           | Α     | -           | -    | 1.20 |

| Molded Package Thickness | A2    | 0.80        | 1.00 | 1.05 |

| Standoff                 | A1    | 0.05        | -    | 0.15 |

| Overall Width            | E     | 6.40 BSC    |      |      |

| Molded Package Width     | E1    | 4.30        | 4.40 | 4.50 |

| Molded Package Length    | D     | 4.90        | 5.00 | 5.10 |

| Foot Length              | L     | 0.45        | 0.60 | 0.75 |

| Footprint                | (L1)  | 1.00 REF    |      |      |

| Foot Angle               | φ     | 0°          | -    | 8°   |

| Lead Thickness           | С     | 0.09        | -    | 0.20 |

| Lead Width               | b     | 0.19        | -    | 0.30 |

Notes:

1. Pin 1 visual index feature may vary, but must be located within the hatched area.

- 2. Dimensions D and E1 do not include mold flash or protrusions. Mold flash or protrusions shall not exceed 0.15mm per side.

- 3. Dimensioning and tolerancing per ASME Y14.5M

BSC: Basic Dimension. Theoretically exact value shown without tolerances. REF: Reference Dimension, usually without tolerance, for information purposes only.

Microchip Technology Drawing No. C04-087C Sheet 2 of 2

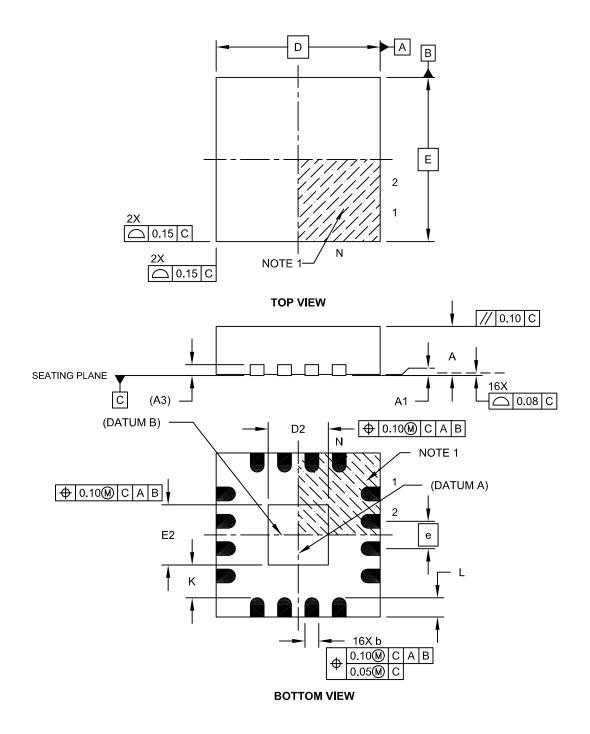

### 16-Lead Plastic Quad Flat, No Lead Package (MG) - 3x3x0.9 mm Body [QFN]

**Note:** For the most current package drawings, please see the Microchip Packaging Specification located at http://www.microchip.com/packaging

Microchip Technology Drawing C04-142A Sheet 1 of 2

### **PRODUCT IDENTIFICATION SYSTEM**

To order or obtain information, e.g., on pricing or delivery, refer to the factory or the listed sales office.

| PART NO.                 | [X] <sup>(1)</sup> - X /XX XXX<br>T Tape and Reel Temperature Package Pattern<br>Option Range                                        | Examples:<br>a) PIC16LF1503T - I/SL<br>Tape and Reel,<br>Industrial temperature,<br>SOIC package                                                                                                                                               |  |

|--------------------------|--------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| Device:                  | PIC16LF1503, PIC16F1503                                                                                                              | b) PIC16F1503 - I/P<br>Industrial temperature<br>PDIP package                                                                                                                                                                                  |  |

| Tape and Reel<br>Option: | Blank = Standard packaging (tube or tray)<br>T = Tape and Reel <sup>(1)</sup>                                                        | c) PIC16F1503 - E/MG 298<br>Extended temperature,<br>QFN package<br>QTP pattern #298                                                                                                                                                           |  |

| Temperature<br>Range:    | $I = -40^{\circ}C \text{ to } +85^{\circ}C  (Industrial)$ $E = -40^{\circ}C \text{ to } +125^{\circ}C  (Extended)$                   |                                                                                                                                                                                                                                                |  |

| Package:                 | MG = Micro Lead Frame (QFN) 3x3x0.9<br>MV = Ultra Thin Micro Lead Frame (UQFN) 3x3x0.5<br>P = Plastic DIP<br>SL = SOIC<br>ST = TSSOP | Note 1: Tape and Reel identifier only appears in the catalog part number description. This identifier is used for ordering purposes and is not printed on the device package. Check with your Microchip Sales Office for package               |  |

| Pattern:                 | QTP, SQTP, Code or Special Requirements (blank otherwise)                                                                            | <ul> <li>availability with the Tape and Reel option.</li> <li>2: For other small form-factor package<br/>availability and marking information, please<br/>visit www.microchip.com/packaging or<br/>contact your local sales office.</li> </ul> |  |