# E·XFL

#### Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

#### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Product Status             | Active                                                                     |

|----------------------------|----------------------------------------------------------------------------|

| Core Processor             | PIC                                                                        |

| Core Size                  | 8-Bit                                                                      |

| Speed                      | 20MHz                                                                      |

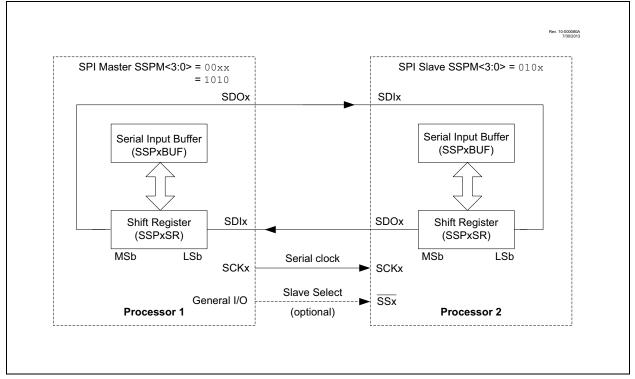

| Connectivity               | I <sup>2</sup> C, SPI                                                      |

| Peripherals                | Brown-out Detect/Reset, POR, PWM, WDT                                      |

| Number of I/O              | 11                                                                         |

| Program Memory Size        | 3.5KB (2K x 14)                                                            |

| Program Memory Type        | FLASH                                                                      |

| EEPROM Size                | -                                                                          |

| RAM Size                   | 128 x 8                                                                    |

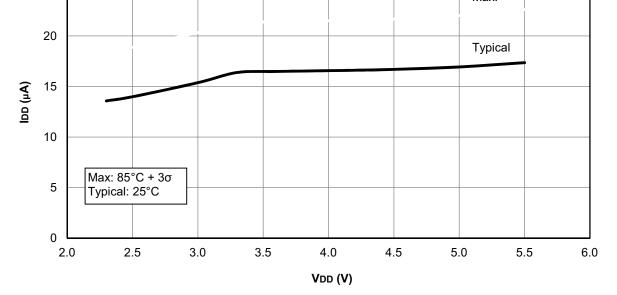

| Voltage - Supply (Vcc/Vdd) | 1.8V ~ 3.6V                                                                |

| Data Converters            | A/D 8x10b                                                                  |

| Oscillator Type            | Internal                                                                   |

| Operating Temperature      | -40°C ~ 125°C (TA)                                                         |

| Mounting Type              | Surface Mount                                                              |

| Package / Case             | 16-UFQFN Exposed Pad                                                       |

| Supplier Device Package    | 16-UQFN (3x3)                                                              |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic16lf1503-e-mv |

|                            |                                                                            |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

## 3.3.6 CORE FUNCTION REGISTERS SUMMARY

The Core Function registers listed in Table 3-4 can be addressed from any Bank.

| Addr            | Name      | Bit 7                                       | Bit 6                                                    | Bit 5         | Bit 4        | Bit 3       | Bit 2         | Bit 1     | Bit 0     | Value on<br>POR, BOR | Value on all other Resets |

|-----------------|-----------|---------------------------------------------|----------------------------------------------------------|---------------|--------------|-------------|---------------|-----------|-----------|----------------------|---------------------------|

| Bank            | Bank 0-31 |                                             |                                                          |               |              |             |               |           |           |                      |                           |

| x00h or<br>x80h | INDF0     |                                             | this location<br>ical register)                          |               | nts of FSR0H | /FSR0L to a | ddress data i | memory    |           | xxxx xxxx            | uuuu uuuu                 |

| x01h or<br>x81h | INDF1     |                                             | this location<br>ical register)                          |               | nts of FSR1H | /FSR1L to a | ddress data i | memory    |           | XXXX XXXX            | uuuu uuuu                 |

| x02h or<br>x82h | PCL       | Program C                                   | ounter (PC) I                                            | Least Signifi | cant Byte    |             |               |           |           | 0000 0000            | 0000 0000                 |

| x03h or<br>x83h | STATUS    | _                                           |                                                          |               | TO           | PD          | Z             | DC        | С         | 1 1000               | q quuu                    |

| x04h or<br>x84h | FSR0L     | Indirect Data Memory Address 0 Low Pointer  |                                                          |               |              |             |               |           | 0000 0000 | uuuu uuuu            |                           |

| x05h or<br>x85h | FSR0H     | Indirect Data Memory Address 0 High Pointer |                                                          |               |              |             |               | 0000 0000 | 0000 0000 |                      |                           |

| x06h or<br>x86h | FSR1L     | Indirect Data Memory Address 1 Low Pointer  |                                                          |               |              |             |               | 0000 0000 | uuuu uuuu |                      |                           |

| x07h or<br>x87h | FSR1H     | Indirect Da                                 | ta Memory A                                              | ddress 1 Hię  | gh Pointer   |             |               |           |           | 0000 0000            | 0000 0000                 |

| x08h or<br>x88h | BSR       | _                                           | BSR<4:0>                                                 |               |              |             |               |           | 0 0000    | 0 0000               |                           |

| x09h or<br>x89h | WREG      | Working Register                            |                                                          |               |              |             |               | 0000 0000 | uuuu uuuu |                      |                           |

| x0Ahor<br>x8Ah  | PCLATH    | _                                           | Write Buffer for the upper 7 bits of the Program Counter |               |              |             |               |           | -000 0000 | -000 0000            |                           |

| x0Bhor<br>x8Bh  | INTCON    | GIE                                         | PEIE                                                     | TMR0IE        | INTE         | IOCIE       | TMR0IF        | INTF      | IOCIF     | 0000 0000            | 0000 0000                 |

#### TABLE 3-4: CORE FUNCTION REGISTERS SUMMARY

Legend: x = unknown, u = unchanged, q = value depends on condition, - = unimplemented, read as '0', r = reserved. Shaded locations are unimplemented, read as '0'.

### 4.3 Code Protection

Code protection allows the device to be protected from unauthorized access. Internal access to the program memory is unaffected by any code protection setting.

#### 4.3.1 PROGRAM MEMORY PROTECTION

The entire program memory space is protected from external reads and writes by the  $\overline{CP}$  bit in Configuration Words. When  $\overline{CP} = 0$ , external reads and writes of program memory are inhibited and a read will return all '0's. The CPU can continue to read program memory, regardless of the protection bit settings. Writing the program memory is dependent upon the write protection setting. See **Section 4.4 "Write Protection"** for more information.

### 4.4 Write Protection

Write protection allows the device to be protected from unintended self-writes. Applications, such as bootloader software, can be protected while allowing other regions of the program memory to be modified.

The WRT<1:0> bits in Configuration Words define the size of the program memory block that is protected.

### 4.5 User ID

Four memory locations (8000h-8003h) are designated as ID locations where the user can store checksum or other code identification numbers. These locations are readable and writable during normal execution. See **Section 10.4 "User ID, Device ID and Configuration Word Access"** for more information on accessing these memory locations. For more information on checksum calculation, see the "*PIC12(L)F1501/PIC16(L)F150X Memory Programming Specification*" (DS41573).

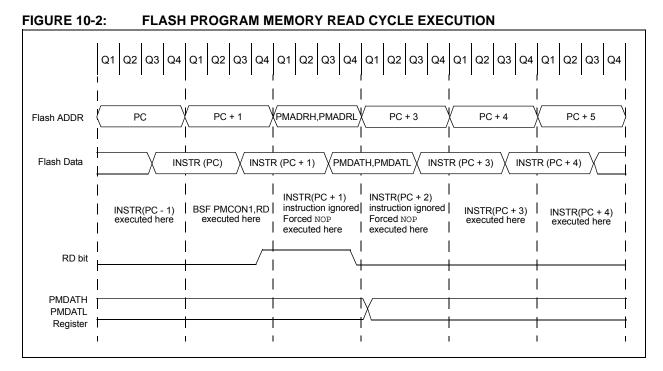

#### EXAMPLE 10-1: FLASH PROGRAM MEMORY READ

```

* This code block will read 1 word of program

* memory at the memory address:

PROG_ADDR_HI : PROG_ADDR_LO

data will be returned in the variables;

PROG_DATA_HI, PROG_DATA_LO

BANKSEL PMADRL

; Select Bank for PMCON registers

PROG_ADDR_LO

MOVLW

;

MOVWF

PMADRL

; Store LSB of address

PROG_ADDR_HI

MOVLW

;

MOVWF

PMADRH

; Store MSB of address

BCF

PMCON1,CFGS

; Do not select Configuration Space

BSF

PMCON1,RD

; Initiate read

NOP

; Ignored (Figure 10-2)

NOP

; Ignored (Figure 10-2)

MOVF

PMDATL,W

; Get LSB of word

MOVWF

PROG_DATA_LO

; Store in user location

; Get MSB of word

PMDATH,W

MOVF

MOVWF

PROG_DATA_HI

; Store in user location

```

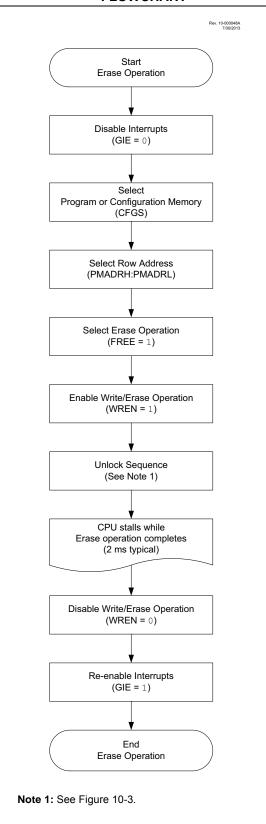

#### 10.2.3 ERASING FLASH PROGRAM MEMORY

While executing code, program memory can only be erased by rows. To erase a row:

- 1. Load the PMADRH:PMADRL register pair with any address within the row to be erased.

- 2. Clear the CFGS bit of the PMCON1 register.

- 3. Set the FREE and WREN bits of the PMCON1 register.

- 4. Write 55h, then AAh, to PMCON2 (Flash programming unlock sequence).

- 5. Set control bit WR of the PMCON1 register to begin the erase operation.

See Example 10-2.

After the "BSF PMCON1, WR" instruction, the processor requires two cycles to set up the erase operation. The user must place two NOP instructions immediately following the WR bit set instruction. The processor will halt internal operations for the typical 2 ms erase time. This is not Sleep mode as the clocks and peripherals will continue to run. After the erase cycle, the processor will resume operation with the third instruction after the PMCON1 write instruction.

#### FLASH PROGRAM MEMORY ERASE FLOWCHART

#### 10.4 User ID, Device ID and Configuration Word Access

Instead of accessing program memory, the User ID's, Device ID/Revision ID and Configuration Words can be accessed when CFGS = 1 in the PMCON1 register. This is the region that would be pointed to by PC<15> = 1, but not all addresses are accessible. Different access may exist for reads and writes. Refer to Table 10-2.

When read access is initiated on an address outside the parameters listed in Table 10-2, the PMDATH:PMDATL register pair is cleared, reading back '0's.

| Address     | Function                    | Read Access | Write Access |

|-------------|-----------------------------|-------------|--------------|

| 8000h-8003h | User IDs                    | Yes         | Yes          |

| 8006h       | Device ID/Revision ID       | Yes         | No           |

| 8007h-8008h | Configuration Words 1 and 2 | Yes         | No           |

#### EXAMPLE 10-4: CONFIGURATION WORD AND DEVICE ID ACCESS

\* This code block will read 1 word of program memory at the memory address:

\* PROG\_ADDR\_LO (must be 00h-08h) data will be returned in the variables;

\* PROG\_DATA\_HI, PROG\_DATA\_LO

| BANKSEL | PMADRL       | ; Select correct Bank        |

|---------|--------------|------------------------------|

| MOVLW   | PROG_ADDR_LO | ;                            |

| MOVWF   | PMADRL       | ; Store LSB of address       |

| CLRF    | PMADRH       | ; Clear MSB of address       |

| BSF     | PMCON1,CFGS  | ; Select Configuration Space |

| BCF     | INTCON,GIE   | ; Disable interrupts         |

| BSF     | PMCON1,RD    | ; Initiate read              |

| NOP     |              | ; Executed (See Figure 10-2) |

| NOP     |              | ; Ignored (See Figure 10-2)  |

| BSF     | INTCON,GIE   | ; Restore interrupts         |

| MOVF    | PMDATL,W     | ; Get LSB of word            |

| MOVWF   | PROG_DATA_LO | ; Store in user location     |

| MOVF    | PMDATH,W     | ; Get MSB of word            |

| MOVWF   | PROG_DATA_HI | ; Store in user location     |

#### 11.1 Alternate Pin Function

The Alternate Pin Function Control (APFCON) register is used to steer specific peripheral input and output functions between different pins. The APFCON register is shown in Register 11-1. For this device family, the following functions can be moved between different pins.

- <u>ss</u>

- T1G

- CLC1

- NCO1

- SDOSEL

### 11.2 Register Definitions: Alternate Pin Function Control

#### **REGISTER 11-1: APFCON: ALTERNATE PIN FUNCTION CONTROL REGISTER**

| U-0   | U-0 | R/W-0/0 | R/W-0/0 | R/W-0/0 | U-0 | R/W-0/0 | R/W-0/0 |

|-------|-----|---------|---------|---------|-----|---------|---------|

|       | _   | SDOSEL  | SSSEL   | T1GSEL  | _   | CLC1SEL | NCO1SEL |

| bit 7 |     |         |         |         |     |         | bit 0   |

| Legend:              |                      |                                                       |

|----------------------|----------------------|-------------------------------------------------------|

| R = Readable bit     | W = Writable bit     | U = Unimplemented bit, read as '0'                    |

| u = Bit is unchanged | x = Bit is unknown   | -n/n = Value at POR and BOR/Value at all other Resets |

| '1' = Bit is set     | '0' = Bit is cleared |                                                       |

| bit 7-6 | Unimplemented: Read as '0'             |  |  |  |  |  |

|---------|----------------------------------------|--|--|--|--|--|

| bit 5   | SDOSEL: Pin Selection bit              |  |  |  |  |  |

|         | 1 = SDO function is on RA4             |  |  |  |  |  |

|         | 0 = SDO function is on RC2             |  |  |  |  |  |

| bit 4   | SSSEL: Pin Selection bit               |  |  |  |  |  |

|         | $1 = \overline{SS}$ function is on RA3 |  |  |  |  |  |

|         | $0 = \overline{SS}$ function is on RC3 |  |  |  |  |  |

| bit 3   | T1GSEL: Pin Selection bit              |  |  |  |  |  |

|         | 1 = T1G function is on RA3             |  |  |  |  |  |

|         | 0 = T1G function is on RA4             |  |  |  |  |  |

| bit 2   | Unimplemented: Read as '0'             |  |  |  |  |  |

| bit 1   | CLC1SEL: Pin Selection bit             |  |  |  |  |  |

|         | 1 = CLC1 function is on RC5            |  |  |  |  |  |

|         | 0 = CLC1 function is on RA2            |  |  |  |  |  |

| bit 0   | NCO1SEL: Pin Selection bit             |  |  |  |  |  |

|         | 1 = NCO1 function is on RA4            |  |  |  |  |  |

|         | 0 = NCO1 function is on RC1            |  |  |  |  |  |

These bits have no effect on the values of any TRIS register. PORT and TRIS overrides will be routed to the correct pin. The unselected pin will be unaffected.

| Name     | Bit 7 | Bit 6  | Bit 5  | Bit 4  | Bit 3  | Bit 2     | Bit 1      | Bit 0    | Register<br>on Page |

|----------|-------|--------|--------|--------|--------|-----------|------------|----------|---------------------|

| ANSELA   | _     | —      | —      | ANSA4  | —      | ANSA2     | ANSA1      | ANSA0    | 99                  |

| ANSELC   | _     | _      | _      | —      | ANSC3  | ANSC2     | ANSC1      | ANSC0    | 103                 |

| CM1CON0  | C10N  | C10UT  | C10E   | C1POL  | _      | C1SP      | C1HYS      | C1SYNC   | 134                 |

| CM2CON0  | C2ON  | C2OUT  | C2OE   | C2POL  | _      | C2SP      | C2HYS      | C2SYNC   | 134                 |

| CM1CON1  | C1NTP | C1INTN | C1PCI  | H<1:0> | —      |           | C1NCH<2:0> | <b>`</b> | 135                 |

| CM2CON1  | C2NTP | C2INTN | C2PCI  | H<1:0> | —      |           | C2NCH<2:0> | <b>`</b> | 135                 |

| CMOUT    | _     |        | _      | _      | _      | _         | MC2OUT     | MC10UT   | 135                 |

| DAC1CON0 | DACEN | _      | DACOE1 | DACOE2 | —      | DACPSS    | _          | _        | 129                 |

| DAC1CON1 | _     | _      | —      |        |        | DACR<4:0> |            |          | 129                 |

| FVRCON   | FVREN | FVRRDY | TSEN   | TSRNG  | CDAFV  | ′R<1:0>   | ADFV       | R<1:0>   | 110                 |

| INTCON   | GIE   | PEIE   | TMR0IE | INTE   | IOCIE  | TMR0IF    | INTF       | IOCIF    | 64                  |

| PIE2     |       | C2IE   | C1IE   | —      | BCL1IE | NCO1IE    | _          | _        | 66                  |

| PIR2     | _     | C2IF   | C1IF   | _      | BCL1IF | NCO1IF    | _          | _        | 69                  |

| PORTA    | _     | _      | RA5    | RA4    | RA3    | RA2       | RA1        | RA0      | 98                  |

| PORTC    | _     | _      | RC5    | RC4    | RC3    | RC2       | RC1        | RC0      | 102                 |

| LATA     | _     | _      | LATA5  | LATA4  | _      | LATA2     | LATA1      | LATA0    | 99                  |

| LATC     | _     | _      | LATC5  | LATC4  | LATC3  | LATC2     | LATC1      | LATC0    | 102                 |

| TRISA    | _     | _      | TRISA5 | TRISA4 | _(1)   | TRISA2    | TRISA1     | TRISA0   | 98                  |

| TRISC    |       |        | TRISC5 | TRISC4 | TRISC3 | TRISC2    | TRISC1     | TRISC0   | 102                 |

#### TABLE 17-3: SUMMARY OF REGISTERS ASSOCIATED WITH COMPARATOR MODULE

Legend: — = unimplemented location, read as '0'. Shaded cells are unused by the comparator module.

Note 1: Unimplemented, read as '1'.

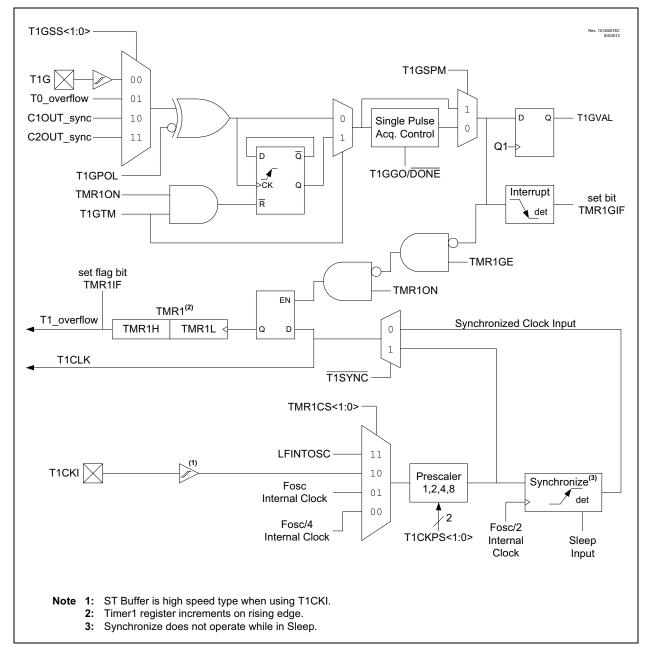

### 19.0 TIMER1 MODULE WITH GATE CONTROL

The Timer1 module is a 16-bit timer/counter with the following features:

- 16-bit timer/counter register pair (TMR1H:TMR1L)

- · Programmable internal or external clock source

- · 2-bit prescaler

- · Optionally synchronized comparator out

- · Multiple Timer1 gate (count enable) sources

- Interrupt on overflow

- Wake-up on overflow (external clock, Asynchronous mode only)

- ADC Auto-Conversion Trigger(s)

- · Selectable Gate Source Polarity

- · Gate Toggle mode

- · Gate Single-Pulse mode

- Gate Value Status

- · Gate Event Interrupt

Figure 19-1 is a block diagram of the Timer1 module.

#### FIGURE 19-1: TIMER1 BLOCK DIAGRAM

#### **19.1** Timer1 Operation

The Timer1 module is a 16-bit incrementing counter which is accessed through the TMR1H:TMR1L register pair. Writes to TMR1H or TMR1L directly update the counter.

When used with an internal clock source, the module is a timer and increments on every instruction cycle. When used with an external clock source, the module can be used as either a timer or counter and increments on every selected edge of the external source.

Timer1 is enabled by configuring the TMR1ON and TMR1GE bits in the T1CON and T1GCON registers, respectively. Table 19-1 displays the Timer1 enable selections.

TABLE 19-1: TIMER1 ENABLE SELECTIONS

| TMR10N | TMR1GE | Timer1<br>Operation |

|--------|--------|---------------------|

| 0      | 0      | Off                 |

| 0      | 1      | Off                 |

| 1      | 0      | Always On           |

| 1      | 1      | Count Enabled       |

#### 19.2 Clock Source Selection

The TMR1CS<1:0> bits of the T1CON register are used to select the clock source for Timer1. Table 19-2 displays the clock source selections.

#### 19.2.1 INTERNAL CLOCK SOURCE

When the internal clock source is selected, the TMR1H:TMR1L register pair will increment on multiples of Fosc as determined by the Timer1 prescaler.

When the Fosc internal clock source is selected, the Timer1 register value will increment by four counts every instruction clock cycle. Due to this condition, a 2 LSB error in resolution will occur when reading the Timer1 value. To utilize the full resolution of Timer1, an asynchronous input signal must be used to gate the Timer1 clock input.

The following asynchronous sources may be used:

- Asynchronous event on the T1G pin to Timer1

gate

- C1 or C2 comparator input to Timer1 gate

#### 19.2.2 EXTERNAL CLOCK SOURCE

When the external clock source is selected, the Timer1 module may work as a timer or a counter.

When enabled to count, Timer1 is incremented on the rising edge of the external clock input T1CKI. The external clock source can be synchronized to the microcontroller system clock or it can run asynchronously.

**Note:** In Counter mode, a falling edge must be registered by the counter prior to the first incrementing rising edge after any one or more of the following conditions:

- Timer1 enabled after POR

- Write to TMR1H or TMR1L

- Timer1 is disabled

- Timer1 is disabled (TMR1ON = 0) when T1CKI is high then Timer1 is enabled (TMR1ON=1) when T1CKI is low.

#### TABLE 19-2: CLOCK SOURCE SELECTIONS

| TMR1CS<1:0> | Clock Source                   |  |  |  |  |  |

|-------------|--------------------------------|--|--|--|--|--|

| 11          | LFINTOSC                       |  |  |  |  |  |

| 10          | External Clocking on T1CKI Pin |  |  |  |  |  |

| 01          | System Clock (Fosc)            |  |  |  |  |  |

| 00          | Instruction Clock (Fosc/4)     |  |  |  |  |  |

#### 21.5.3.3 7-bit Transmission with Address Hold Enabled

Setting the AHEN bit of the SSPxCON3 register enables additional clock stretching and interrupt generation after the eighth falling edge of a received matching address. Once a matching address has been clocked in, CKP is cleared and the SSPxIF interrupt is set.

Figure 21-19 displays a standard waveform of a 7-bit Address Slave Transmission with AHEN enabled.

- 1. Bus starts idle.

- Master sends Start condition; the S bit of SSPxSTAT is set; SSPxIF is set if interrupt on Start detect is enabled.

- Master sends matching address with R/W bit set. After the eighth falling edge of the SCLx line the CKP bit is cleared and SSPxIF interrupt is generated.

- 4. Slave software clears SSPxIF.

- 5. Slave software reads ACKTIM bit of SSPxCON3 register, and  $R/\overline{W}$  and  $D/\overline{A}$  of the SSPxSTAT register to determine the source of the interrupt.

- 6. Slave reads the address value from the SSPxBUF register clearing the BF bit.

- Slave software decides from this information if it wishes to ACK or not ACK and sets the ACKDT bit of the SSPxCON2 register accordingly.

- 8. Slave sets the CKP bit releasing SCLx.

- 9. Master clocks in the  $\overline{ACK}$  value from the slave.

- 10. Slave hardware automatically clears the CKP bit and sets SSPxIF after the ACK if the R/W bit is set.

- 11. Slave software clears SSPxIF.

- 12. Slave loads value to transmit to the master into SSPxBUF setting the BF bit.

Note: SSPxBUF cannot be loaded until after the ACK.

- 13. Slave sets the CKP bit, releasing the clock.

- 14. Master clocks out the data from the slave and sends an ACK value on the ninth SCLx pulse.

- 15. Slave hardware copies the ACK value into the ACKSTAT bit of the SSPxCON2 register.

- 16. Steps 10-15 are repeated for each byte transmitted to the master from the slave.

- 17. If the master sends a not ACK the slave releases the bus allowing the master to send a Stop and end the communication.

**Note:** Master must send a not ACK on the last byte to ensure that the slave releases the SCLx line to receive a Stop.

| U-0            | R/W-x/u   |                                                                                  | R/W-x/u      | U-0                        | R/W-x/u          | R/W-x/u                    | R/W-x/u    |  |  |  |  |

|----------------|-----------|----------------------------------------------------------------------------------|--------------|----------------------------|------------------|----------------------------|------------|--|--|--|--|

| —              |           | LCxD4S<2:0>(1)                                                                   |              | —                          | I                | _CxD3S<2:0> <sup>(1)</sup> |            |  |  |  |  |

| bit 7          |           |                                                                                  |              |                            |                  |                            | bit 0      |  |  |  |  |

|                |           |                                                                                  |              |                            |                  |                            |            |  |  |  |  |

| Legend:        |           |                                                                                  |              |                            |                  |                            |            |  |  |  |  |

| R = Readab     | ole bit   | W = Writable I                                                                   | oit          | U = Unimple                | mented bit, read | d as '0'                   |            |  |  |  |  |

| u = Bit is ur  | nchanged  | x = Bit is unkn                                                                  | own          | -n/n = Value               | at POR and BC    | R/Value at all of          | her Resets |  |  |  |  |

| '1' = Bit is s | et        | '0' = Bit is clea                                                                | ared         |                            |                  |                            |            |  |  |  |  |

|                |           |                                                                                  |              |                            |                  |                            |            |  |  |  |  |

| bit 7          | Unimplem  | ented: Read as '0                                                                | )'           |                            |                  |                            |            |  |  |  |  |

| bit 6-4        | LCxD4S<2  | 2:0>: Input Data 4                                                               | Selection Co | ontrol bits <sup>(1)</sup> |                  |                            |            |  |  |  |  |

|                | 111 = LCx | _in[3] is selected                                                               | for lcxd4    |                            |                  |                            |            |  |  |  |  |

|                |           | 110 = LCx_in[2] is selected for lcxd4                                            |              |                            |                  |                            |            |  |  |  |  |

|                |           | _in[1] is selected                                                               |              |                            |                  |                            |            |  |  |  |  |

|                |           | _in[0] is selected                                                               |              |                            |                  |                            |            |  |  |  |  |

|                |           | _in[15] is selected                                                              |              |                            |                  |                            |            |  |  |  |  |

|                |           | _in[14] is selected                                                              |              |                            |                  |                            |            |  |  |  |  |

|                |           | <pre>_in[13] is selected ( in[12] is selected</pre>                              |              |                            |                  |                            |            |  |  |  |  |

| bit 3          |           | ented: Read as '(                                                                |              |                            |                  |                            |            |  |  |  |  |

| bit 2-0        | -         | 2:0>: Input Data 3                                                               |              | ntrol hits(1)              |                  |                            |            |  |  |  |  |

|                |           | -                                                                                |              |                            |                  |                            |            |  |  |  |  |

|                |           | 111 = LCx_in[15] is selected for lcxd3<br>110 = LCx in[14] is selected for lcxd3 |              |                            |                  |                            |            |  |  |  |  |

|                |           | $100 = LCx_in[13]$ is selected for lcxd3                                         |              |                            |                  |                            |            |  |  |  |  |

|                |           | $101 = LCx_in[13]$ is selected for lcxd3                                         |              |                            |                  |                            |            |  |  |  |  |

|                |           | ( in[11] is selected                                                             |              |                            |                  |                            |            |  |  |  |  |

|                |           | in[10] is selected                                                               |              |                            |                  |                            |            |  |  |  |  |

|                |           | _in[9] is selected                                                               |              |                            |                  |                            |            |  |  |  |  |

|                |           | in[8] is selected                                                                |              |                            |                  |                            |            |  |  |  |  |

#### REGISTER 23-4: CLCxSEL1: MULTIPLEXER DATA 3 AND 4 SELECT REGISTER

**Note 1:** See Table 23-1 for signal names associated with inputs.

| R/W-x/u                                  | R/W-x/u                                                              | R/W-x/u            | R/W-x/u  | R/W-x/u                                               | R/W-x/u  | R/W-x/u  | R/W-x/u  |  |  |  |

|------------------------------------------|----------------------------------------------------------------------|--------------------|----------|-------------------------------------------------------|----------|----------|----------|--|--|--|

| LCxG3D4T                                 | LCxG3D4N                                                             | LCxG3D3T           | LCxG3D3N | LCxG3D2T                                              | LCxG3D2N | LCxG3D1T | LCxG3D1N |  |  |  |

| bit 7                                    |                                                                      |                    | ·        |                                                       |          |          | bit      |  |  |  |

| Legend:                                  |                                                                      |                    |          |                                                       |          |          |          |  |  |  |

| R = Readable bit                         |                                                                      | W = Writable bit   |          | U = Unimplemented bit, read as '0'                    |          |          |          |  |  |  |

| u = Bit is unchanged<br>'1' = Bit is set |                                                                      | x = Bit is unknown |          | -n/n = Value at POR and BOR/Value at all other Resets |          |          |          |  |  |  |

|                                          |                                                                      | '0' = Bit is cle   | ared     |                                                       |          |          |          |  |  |  |

|                                          |                                                                      |                    |          |                                                       |          |          |          |  |  |  |

| bit 7                                    | LCxG3D4T: Gate 3 Data 4 True (non-inverted) bit                      |                    |          |                                                       |          |          |          |  |  |  |

|                                          | 1 = Icxd4T is gated into Icxg3<br>0 = Icxd4T is not gated into Icxg3 |                    |          |                                                       |          |          |          |  |  |  |

| bit 6                                    | <b>LCxG3D4N:</b> Gate 3 Data 4 Negated (inverted) bit                |                    |          |                                                       |          |          |          |  |  |  |

| DIL O                                    | 1 = lcxd4N is gated into lcxg3                                       |                    |          |                                                       |          |          |          |  |  |  |

|                                          | 0 = Icxd4N is not gated into Icxg3                                   |                    |          |                                                       |          |          |          |  |  |  |

| bit 5                                    | LCxG3D3T: Gate 3 Data 3 True (non-inverted) bit                      |                    |          |                                                       |          |          |          |  |  |  |

|                                          | 1 = lcxd3T is gated into lcxg3                                       |                    |          |                                                       |          |          |          |  |  |  |

|                                          | 0 = Icxd3T is not gated into Icxg3                                   |                    |          |                                                       |          |          |          |  |  |  |

| bit 4                                    | LCxG3D3N: Gate 3 Data 3 Negated (inverted) bit                       |                    |          |                                                       |          |          |          |  |  |  |

|                                          | 1 = lcxd3N is gated into lcxg3                                       |                    |          |                                                       |          |          |          |  |  |  |

|                                          | 0 = Icxd3N is not gated into Icxg3                                   |                    |          |                                                       |          |          |          |  |  |  |

| bit 3                                    | LCxG3D2T: Gate 3 Data 2 True (non-inverted) bit                      |                    |          |                                                       |          |          |          |  |  |  |

|                                          | 1 = Icxd2T is gated into Icxg3<br>0 = Icxd2T is not gated into Icxg3 |                    |          |                                                       |          |          |          |  |  |  |

| bit 2                                    | LCxG3D2N: Gate 3 Data 2 Negated (inverted) bit                       |                    |          |                                                       |          |          |          |  |  |  |

|                                          | 1 = lcxd2N is gated into lcxg3                                       |                    |          |                                                       |          |          |          |  |  |  |

|                                          | 0 = lcxd2N is not gated into lcxg3                                   |                    |          |                                                       |          |          |          |  |  |  |

| bit 1                                    | LCxG3D1T: Gate 3 Data 1 True (non-inverted) bit                      |                    |          |                                                       |          |          |          |  |  |  |

|                                          | 1 = Icxd1T is gated into Icxg3                                       |                    |          |                                                       |          |          |          |  |  |  |

|                                          | 0 = lcxd1T is not gated into lcxg3                                   |                    |          |                                                       |          |          |          |  |  |  |

| bit 0                                    | LCxG3D1N: Gate 3 Data 1 Negated (inverted) bit                       |                    |          |                                                       |          |          |          |  |  |  |

|                                          | 1 = lcxd1N is gated into lcxg3<br>0 = lcxd1N is not gated into lcxg3 |                    |          |                                                       |          |          |          |  |  |  |

|                                          | 0 = ICX01N IS                                                        | not dated into     | ICX03    |                                                       |          |          |          |  |  |  |

#### REGISTER 23-7: CLCxGLS2: GATE 3 LOGIC SELECT REGISTER

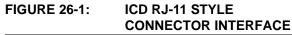

### 26.0 IN-CIRCUIT SERIAL PROGRAMMING<sup>™</sup> (ICSP<sup>™</sup>)

ICSP<sup>™</sup> programming allows customers to manufacture circuit boards with unprogrammed devices. Programming can be done after the assembly process allowing the device to be programmed with the most recent firmware or a custom firmware. Five pins are needed for ICSP<sup>™</sup> programming:

- ICSPCLK

- ICSPDAT

- MCLR/VPP

- VDD

- Vss

In Program/Verify mode the program memory, user IDs and the Configuration Words are programmed through serial communications. The ICSPDAT pin is a bidirectional I/O used for transferring the serial data and the ICSPCLK pin is the clock input. For more information on ICSP<sup>TM</sup> refer to the "*PIC12(L)F1501/PIC16(L)F150X Memory Programming Specification*" (DS41573).

#### 26.1 High-Voltage Programming Entry Mode

The device is placed into High-Voltage Programming Entry mode by holding the ICSPCLK and ICSPDAT pins low then raising the voltage on MCLR/VPP to VIHH.

#### 26.2 Low-Voltage Programming Entry Mode

The Low-Voltage Programming Entry mode allows the PIC<sup>®</sup> Flash MCUs to be programmed using VDD only, without high voltage. When the LVP bit of Configuration Words is set to '1', the ICSP Low-Voltage Programming Entry mode is enabled. To disable the Low-Voltage ICSP mode, the LVP bit must be programmed to '0'.

Entry into the Low-Voltage Programming Entry mode requires the following steps:

- 1. MCLR is brought to VIL.

- 2. A 32-bit key sequence is presented on ICSPDAT, while clocking ICSPCLK.

Once the key sequence is complete,  $\overline{\text{MCLR}}$  must be held at VIL for as long as Program/Verify mode is to be maintained.

If low-voltage programming is enabled (LVP = 1), the  $\overline{\text{MCLR}}$  Reset function is automatically enabled and cannot be disabled. See **Section 6.5 "MCLR**" for more information.

The LVP bit can only be reprogrammed to '0' by using the High-Voltage Programming mode.

#### 26.3 Common Programming Interfaces

Connection to a target device is typically done through an ICSP<sup>™</sup> header. A commonly found connector on development tools is the RJ-11 in the 6P6C (6-pin, 6-connector) configuration. See Figure 26-1.

Another connector often found in use with the PICkit<sup>™</sup> programmers is a standard 6-pin header with 0.1 inch spacing. Refer to Figure 26-2.

#### TABLE 28-4: I/O PORTS

Standard Operating Conditions (unless otherwise stated)

| Param.<br>No. | Sym. | Characteristic                       | Min.              | Тур†     | Max.     | Units | Conditions                                                                 |  |  |

|---------------|------|--------------------------------------|-------------------|----------|----------|-------|----------------------------------------------------------------------------|--|--|

|               | VIL  | Input Low Voltage                    |                   |          |          |       | ·                                                                          |  |  |

|               |      | I/O PORT:                            |                   |          |          |       |                                                                            |  |  |

| D030          |      | with TTL buffer                      | _                 | _        | 0.8      | V     | $4.5V \leq V\text{DD} \leq 5.5V$                                           |  |  |

| D030A         |      |                                      | —                 | _        | 0.15 VDD | V     | $1.8V \le V\text{DD} \le 4.5V$                                             |  |  |

| D031          |      | with Schmitt Trigger buffer          | —                 | _        | 0.2 Vdd  | V     | $2.0V \le V\text{DD} \le 5.5V$                                             |  |  |

|               |      | with I <sup>2</sup> C™ levels        | —                 | _        | 0.3 VDD  | V     |                                                                            |  |  |

|               |      | with SMbus levels                    | —                 | _        | 0.8      | V     | $2.7V \le V\text{DD} \le 5.5V$                                             |  |  |

| D032          |      | MCLR                                 | —                 | _        | 0.2 Vdd  | V     |                                                                            |  |  |

|               | VIH  | Input High Voltage                   |                   |          |          |       |                                                                            |  |  |

|               |      | I/O PORT:                            |                   |          |          |       |                                                                            |  |  |

| D040          |      | with TTL buffer                      | 2.0               | _        | —        | V     | $4.5V \leq V\text{DD} \leq 5.5V$                                           |  |  |

| D040A         |      |                                      | 0.25 VDD +<br>0.8 | —        | -        | V     | $1.8V \le VDD \le 4.5V$                                                    |  |  |

| D041          |      | with Schmitt Trigger buffer          | 0.8 VDD           | _        | —        | V     | $2.0V \leq V\text{DD} \leq 5.5V$                                           |  |  |

|               |      | with I <sup>2</sup> C™ levels        | 0.7 Vdd           |          | —        | V     |                                                                            |  |  |

|               |      | with SMbus levels                    | 2.1               |          | —        | V     | $2.7V \le V\text{DD} \le 5.5V$                                             |  |  |

| D042          |      | MCLR                                 | 0.8 Vdd           | _        | —        | V     |                                                                            |  |  |

|               | lil  | Input Leakage Current <sup>(1)</sup> |                   |          |          |       |                                                                            |  |  |

| D060          |      | I/O Ports                            | —                 | ± 5      | ± 125    | nA    | $Vss \le VPIN \le VDD$ ,<br>Pin at high-impedance, 85°C                    |  |  |

|               |      |                                      | —                 | ± 5      | ± 1000   | nA    | Vss $\leq$ VPIN $\leq$ VDD, Pin at high-impedance, 125°C                   |  |  |

| D061          |      | MCLR <sup>(2)</sup>                  | —                 | ± 50     | ± 200    | nA    | VSS $\leq$ VPIN $\leq$ VDD, Pin at high-impedance, 85°C                    |  |  |

| D070*         | IPUR | IPUR Weak Pull-up Current            |                   |          |          |       |                                                                            |  |  |

|               |      |                                      | 25                | 100      | 200      | μΑ    | VDD = 3.3V, VPIN = VSS                                                     |  |  |

|               |      |                                      | 25                | 140      | 300      | μΑ    | VDD = 5.0V, VPIN = VSS                                                     |  |  |

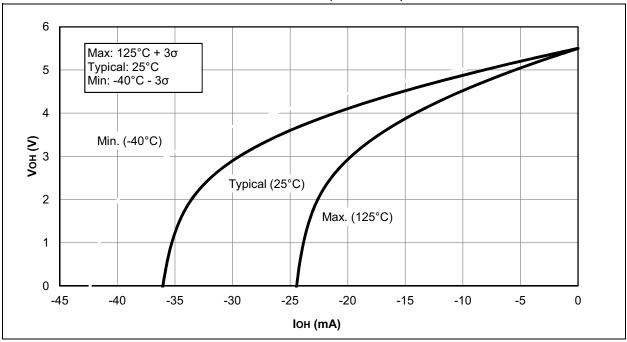

| D080          | Vol  | Output Low Voltage                   |                   |          |          |       |                                                                            |  |  |

|               |      | I/O Ports                            | _                 | _        | 0.6      | V     | IOL = 8 mA, VDD = 5V<br>IOL = 6 mA, VDD = 3.3V<br>IOL = 1.8 mA, VDD = 1.8V |  |  |

| D090          | Voн  | Output High Voltage                  |                   |          |          |       |                                                                            |  |  |

|               |      | I/O Ports                            | Vdd - 0.7         | _        | _        | v     | IOH = 3.5 mA, VDD = 5V<br>IOH = 3 mA, VDD = 3.3V<br>IOH = 1 mA, VDD = 1.8V |  |  |

|               |      | Capacitive Loading Specification     | tions on Out      | out Pins |          | •     | 1                                                                          |  |  |

| D101A*        | CIO  | All I/O pins                         | _                 | _        | 50       | pF    |                                                                            |  |  |

These parameters are characterized but not tested.

Data in "Typ" column is at 3.0V, 25°C unless otherwise stated. These parameters are for design guidance only and are † not tested.

**Note 1:** Negative current is defined as current sourced by the pin.

2: The leakage current on the MCLR pin is strongly dependent on the applied voltage level. The specified levels represent normal operating conditions. Higher leakage current may be measured at different input voltages.

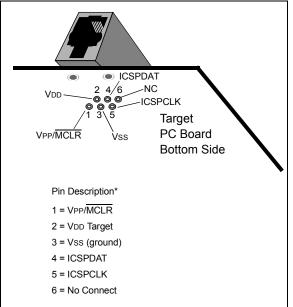

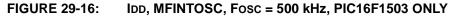

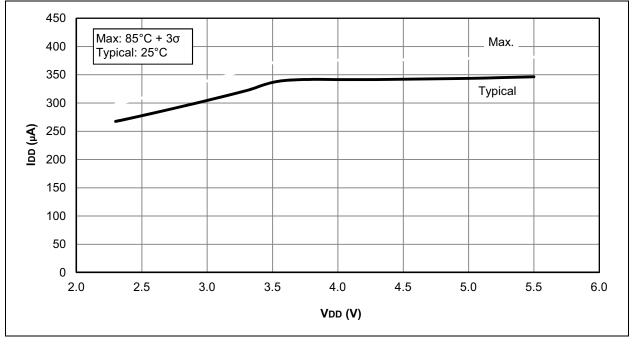

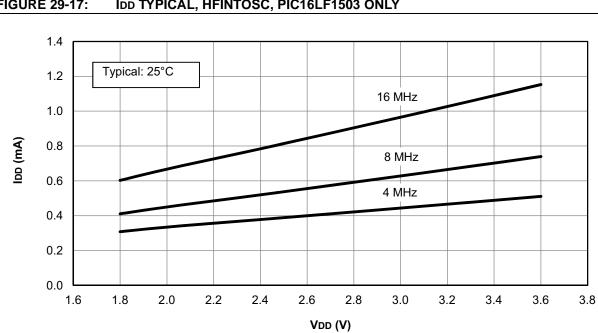

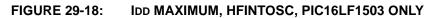

FIGURE 29-15: IDD, MFINTOSC, Fosc = 500 kHz, PIC16LF1503 ONLY

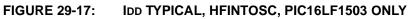

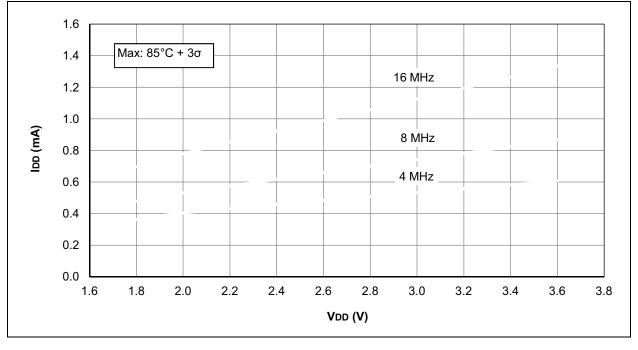

FIGURE 29-35: VOH vs. IOH OVER TEMPERATURE, VDD = 5.5V, PIC16F1503 ONLY

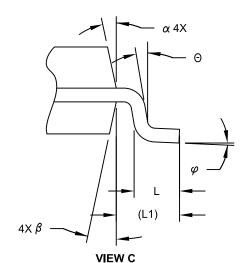

#### 14-Lead Plastic Small Outline (SL) - Narrow, 3.90 mm Body [SOIC]

**Note:** For the most current package drawings, please see the Microchip Packaging Specification located at http://www.microchip.com/packaging

|                          | MILLIMETERS |          |     |      |  |  |

|--------------------------|-------------|----------|-----|------|--|--|

| Dimension Lin            | nits        | MIN      | NOM | MAX  |  |  |

| Number of Pins           | N           | 14       |     |      |  |  |

| Pitch                    | е           | 1.27 BSC |     |      |  |  |

| Overall Height           | A           | -        | -   | 1.75 |  |  |

| Molded Package Thickness | A2          | 1.25     | -   | -    |  |  |

| Standoff §               | A1          | 0.10     | -   | 0.25 |  |  |

| Overall Width            | E           | 6.00 BSC |     |      |  |  |

| Molded Package Width     | E1          | 3.90 BSC |     |      |  |  |

| Overall Length           | D           | 8.65 BSC |     |      |  |  |

| Chamfer (Optional)       | h           | 0.25     | I   | 0.50 |  |  |

| Foot Length              | L           | 0.40     | -   | 1.27 |  |  |

| Footprint                | L1          | 1.04 REF |     |      |  |  |

| Lead Angle               | Θ           | 0°       | i i | -    |  |  |

| Foot Angle               | φ           | 0°       | -   | 8°   |  |  |

| Lead Thickness           | С           | 0.10     | -   | 0.25 |  |  |

| Lead Width               | b           | 0.31     | -   | 0.51 |  |  |

| Mold Draft Angle Top     | α           | 5°       | -   | 15°  |  |  |

| Mold Draft Angle Bottom  | β           | 5°       | -   | 15°  |  |  |

#### Notes:

- 1. Pin 1 visual index feature may vary, but must be located within the hatched area.

- 2. § Significant Characteristic

- Dimension D does not include mold flash, protrusions or gate burrs, which shall not exceed 0.15 mm per end. Dimension E1 does not include interlead flash or protrusion, which shall not exceed 0.25 mm per side.

- Dimensioning and tolerancing per ASME Y14.5M BSC: Basic Dimension. Theoretically exact value shown without tolerances. REF: Reference Dimension, usually without tolerance, for information purposes only.

- 5. Datums A & B to be determined at Datum H.

Microchip Technology Drawing No. C04-065C Sheet 2 of 2