Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

#### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Details                    |                                                                            |

|----------------------------|----------------------------------------------------------------------------|

| Product Status             | Active                                                                     |

| Core Processor             | PIC                                                                        |

| Core Size                  | 8-Bit                                                                      |

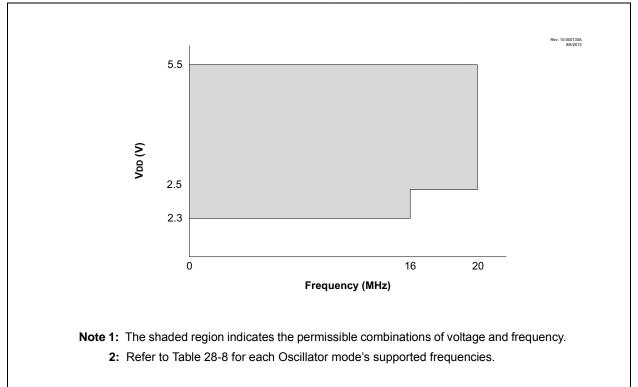

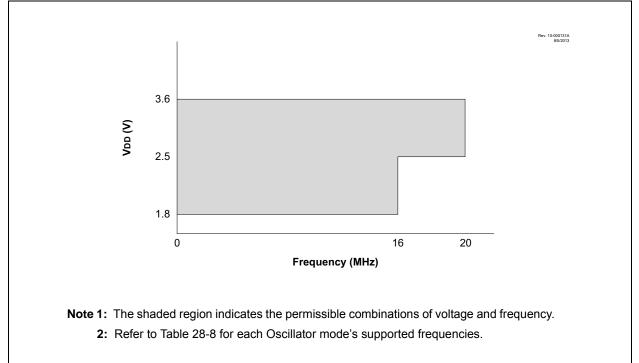

| Speed                      | 20MHz                                                                      |

| Connectivity               | I <sup>2</sup> C, SPI                                                      |

| Peripherals                | Brown-out Detect/Reset, POR, PWM, WDT                                      |

| Number of I/O              | 11                                                                         |

| Program Memory Size        | 3.5KB (2K x 14)                                                            |

| Program Memory Type        | FLASH                                                                      |

| EEPROM Size                | -                                                                          |

| RAM Size                   | 128 x 8                                                                    |

| Voltage - Supply (Vcc/Vdd) | 1.8V ~ 3.6V                                                                |

| Data Converters            | A/D 8x10b                                                                  |

| Oscillator Type            | Internal                                                                   |

| Operating Temperature      | -40°C ~ 125°C (TA)                                                         |

| Mounting Type              | Surface Mount                                                              |

| Package / Case             | 14-SOIC (0.154", 3.90mm Width)                                             |

| Supplier Device Package    | 14-SOIC                                                                    |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic16lf1503-e-sl |

|                            |                                                                            |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

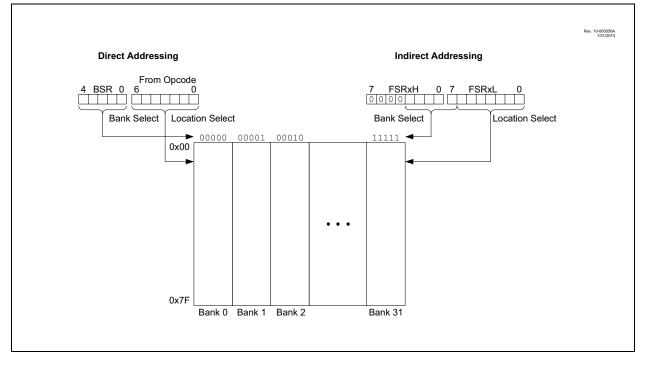

#### 3.6.1 TRADITIONAL DATA MEMORY

The traditional data memory is a region from FSR address 0x000 to FSR address 0xFFF. The addresses correspond to the absolute addresses of all SFR, GPR and common registers.

### FIGURE 3-9: TRADITIONAL DATA MEMORY MAP

| (27.97777) - 2000 - 2000 - 2000 - 2000 - 2000 - 2000 - 2000 - 2000 - 2000 - 2000 - 2000 - 2000 - 2000 - 2000 - 2 | PHYTORC (WDT disabled)                                            |

|------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------|

| HFINTOSC _                                                                                                       | Cepileior Defizy <sup>(1)</sup> - 2-cycly, Sylve, i Primeina      |

| LFINTOSC                                                                                                         |                                                                   |

| IRCF <3:0>                                                                                                       | $\neq 0$ $X = 0$                                                  |

| System Clock                                                                                                     |                                                                   |

| 19100770990                                                                                                      | SUSTONE (WET enabled)                                             |

| HFINTOSC                                                                                                         |                                                                   |

| LFINTOSC -                                                                                                       |                                                                   |

| IRCF <3:0>                                                                                                       | $\neq 0$ $\chi = 0$                                               |

| System Clock                                                                                                     |                                                                   |

| 1910990000                                                                                                       | IFINYOSC<br>UNITYOSC have off unless WOT is enabled <sup>93</sup> |

| LENEOSC                                                                                                          |                                                                   |

| 5587702C                                                                                                         | Ordby: Orley'S, 2-1996-3996;                                      |

|                                                                                                                  |                                                                   |

| System Clock                                                                                                     |                                                                   |

## 9.6 Register Definitions: Watchdog Timer Control

| U-0              | U-0                                 | R/W-0/0                                                                                                  | R/W-1/1                                                                                       | R/W-0/0                   | R/W-1/1        | R/W-1/1          | R/W-0/0      |  |  |

|------------------|-------------------------------------|----------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------|---------------------------|----------------|------------------|--------------|--|--|

| —                | —                                   |                                                                                                          |                                                                                               | WDTPS<4:0>                |                |                  | SWDTEN       |  |  |

| it 7             |                                     |                                                                                                          |                                                                                               |                           |                |                  | bit (        |  |  |

| egend:           |                                     |                                                                                                          |                                                                                               |                           |                |                  |              |  |  |

| R = Readab       | ole bit                             | W = Writable                                                                                             | bit                                                                                           | U = Unimpleme             | ented bit, rea | d as '0'         |              |  |  |

| u = Bit is un    | changed                             | x = Bit is unkr                                                                                          | iown                                                                                          | -n/n = Value at           | POR and BC     | R/Value at all o | other Resets |  |  |

| '1' = Bit is set |                                     | '0' = Bit is clea                                                                                        | '0' = Bit is cleared                                                                          |                           |                |                  |              |  |  |

| oit 7-6          | Unimpleme                           | nted: Read as '                                                                                          | )'                                                                                            |                           |                |                  |              |  |  |

| oit 5-1          | WDTPS<4:0                           | >: Watchdog Tir                                                                                          | mer Period S                                                                                  | elect bits <sup>(1)</sup> |                |                  |              |  |  |

|                  | Bit Value =                         | Prescale Rate                                                                                            |                                                                                               |                           |                |                  |              |  |  |

|                  | 11111 = R                           | eserved. Results                                                                                         | s in minimum                                                                                  | interval (1:32)           |                |                  |              |  |  |

|                  | •                                   |                                                                                                          |                                                                                               |                           |                |                  |              |  |  |

|                  | •                                   |                                                                                                          |                                                                                               |                           |                |                  |              |  |  |

| • 10011          |                                     | eserved. Results                                                                                         | s in minimum                                                                                  | interval (1:32)           |                |                  |              |  |  |

| :                | 10010 = <b>1</b> ·                  | 8388608 (2 <sup>23</sup> ) (I                                                                            | nterval 256s                                                                                  | nominal)                  |                |                  |              |  |  |

|                  |                                     | 8388608 (2 <sup>23</sup> ) (Interval 256s nominal)<br>4194304 (2 <sup>22</sup> ) (Interval 128s nominal) |                                                                                               |                           |                |                  |              |  |  |

|                  | 10000 = <b>1</b> :                  | 0 = 1:2097152 (2 <sup>21</sup> ) (Interval 64s nominal)                                                  |                                                                                               |                           |                |                  |              |  |  |

|                  | 01111 = <b>1</b> :                  | 1048576 (2 <sup>20</sup> ) (I                                                                            | nterval 32s r                                                                                 | nominal)                  |                |                  |              |  |  |

|                  | 01110 = 1:                          | 524288 (2 <sup>19</sup> ) (In                                                                            | terval 16s no                                                                                 | ominal)                   |                |                  |              |  |  |

|                  |                                     |                                                                                                          | 262144 (2 <sup>18</sup> ) (Interval 8s nominal)                                               |                           |                |                  |              |  |  |

|                  |                                     | . , .                                                                                                    | 131072 (2 <sup>17</sup> ) (Interval 4s nominal)<br>65536  (Interval 2s nominal) (Reset value) |                           |                |                  |              |  |  |

|                  |                                     | 32768 (Interval                                                                                          |                                                                                               |                           |                |                  |              |  |  |

|                  |                                     | 16384 (Interval                                                                                          | ,                                                                                             | nal)                      |                |                  |              |  |  |

|                  |                                     | 8192 (Interval 2                                                                                         |                                                                                               |                           |                |                  |              |  |  |

|                  |                                     | 4096 (Interval 12                                                                                        |                                                                                               | ,                         |                |                  |              |  |  |

|                  |                                     | 2048 (Interval 64                                                                                        |                                                                                               |                           |                |                  |              |  |  |

|                  |                                     | 1024 (Interval 32<br>512 (Interval 16                                                                    |                                                                                               | ,                         |                |                  |              |  |  |

|                  |                                     | 256 (Interval 8 n                                                                                        |                                                                                               |                           |                |                  |              |  |  |

|                  |                                     | 128 (Interval 4 n                                                                                        |                                                                                               |                           |                |                  |              |  |  |

|                  |                                     | 64 (Interval 2 m                                                                                         | ,                                                                                             |                           |                |                  |              |  |  |

|                  | 00000 = 1:                          | 32 (Interval 1 m                                                                                         | s nominal)                                                                                    |                           |                |                  |              |  |  |

| oit O            | SWDTEN: S                           | oftware Enable/                                                                                          | Disable for V                                                                                 | Vatchdog Timer b          | it             |                  |              |  |  |

|                  | <u>If WDTE&lt;1:</u>                |                                                                                                          |                                                                                               |                           |                |                  |              |  |  |

|                  | This bit is ig                      |                                                                                                          |                                                                                               |                           |                |                  |              |  |  |

|                  | If WDTE<1:0                         |                                                                                                          |                                                                                               |                           |                |                  |              |  |  |

|                  | 1 = WDT is<br>0 = WDT is            |                                                                                                          |                                                                                               |                           |                |                  |              |  |  |

|                  | 0 = WDT IS<br><u>If WDTE&lt;1:(</u> |                                                                                                          |                                                                                               |                           |                |                  |              |  |  |

|                  | This bit is ig                      |                                                                                                          |                                                                                               |                           |                |                  |              |  |  |

## REGISTER 9-1: WDTCON: WATCHDOG TIMER CONTROL REGISTER

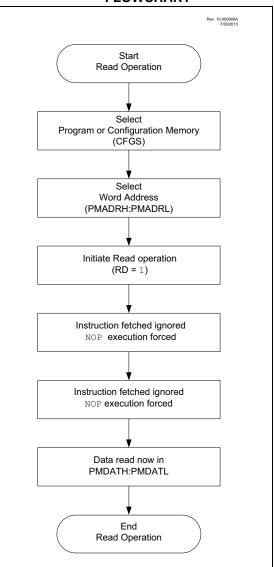

## 10.2.1 READING THE FLASH PROGRAM MEMORY

To read a program memory location, the user must:

- 1. Write the desired address to the PMADRH:PMADRL register pair.

- 2. Clear the CFGS bit of the PMCON1 register.

- 3. Then, set control bit RD of the PMCON1 register.

Once the read control bit is set, the program memory Flash controller will use the second instruction cycle to read the data. This causes the second instruction immediately following the "BSF PMCON1, RD" instruction to be ignored. The data is available in the very next cycle, in the PMDATH:PMDATL register pair; therefore, it can be read as two bytes in the following instructions.

PMDATH:PMDATL register pair will hold this value until another read or until it is written to by the user.

| Note: | The two instructions following a program    |

|-------|---------------------------------------------|

|       | memory read are required to be NOPs.        |

|       | This prevents the user from executing a     |

|       | 2-cycle instruction on the next instruction |

|       | after the RD bit is set.                    |

## FIGURE 10-1: FLASH PROGRAM MEMORY READ FLOWCHART

## 10.2.4 WRITING TO FLASH PROGRAM MEMORY

Program memory is programmed using the following steps:

- 1. Load the address in PMADRH:PMADRL of the row to be programmed.

- 2. Load each write latch with data.

- 3. Initiate a programming operation.

- 4. Repeat steps 1 through 3 until all data is written.

Before writing to program memory, the word(s) to be written must be erased or previously unwritten. Program memory can only be erased one row at a time. No automatic erase occurs upon the initiation of the write.

Program memory can be written one or more words at a time. The maximum number of words written at one time is equal to the number of write latches. See Figure 10-5 (row writes to program memory with 16 write latches) for more details.

The write latches are aligned to the Flash row address boundary defined by the upper 10-bits of PMADRH:PMADRL, (PMADRH<6:0>:PMADRL<7:5>) with the lower five bits of PMADRL, (PMADRL<7:0>) determining the write latch being loaded. Write operations do not cross these boundaries. At the completion of a program memory write operation, the data in the write latches is reset to contain 0x3FFF. The following steps should be completed to load the write latches and program a row of program memory. These steps are divided into two parts. First, each write latch is loaded with data from the PMDATH:PMDATL using the unlock sequence with LWLO = 1. When the last word to be loaded into the write latch is ready, the LWLO bit is cleared and the unlock sequence executed. This initiates the programming operation, writing all the latches into Flash program memory.

| Note: | The special unlock sequence is required<br>to load a write latch with data or initiate a<br>Flash programming operation. If the |

|-------|---------------------------------------------------------------------------------------------------------------------------------|

|       | unlock sequence is interrupted, writing to the latches or program memory will not be initiated.                                 |

- 1. Set the WREN bit of the PMCON1 register.

- 2. Clear the CFGS bit of the PMCON1 register.

- 3. Set the LWLO bit of the PMCON1 register. When the LWLO bit of the PMCON1 register is '1', the write sequence will only load the write latches and will not initiate the write to Flash program memory.

- 4. Load the PMADRH:PMADRL register pair with the address of the location to be written.

- 5. Load the PMDATH:PMDATL register pair with the program memory data to be written.

- Execute the unlock sequence (Section 10.2.2 "Flash Memory Unlock Sequence"). The write latch is now loaded.

- 7. Increment the PMADRH:PMADRL register pair to point to the next location.

- 8. Repeat steps 5 through 7 until all but the last write latch has been loaded.

- Clear the LWLO bit of the PMCON1 register. When the LWLO bit of the PMCON1 register is '0', the write sequence will initiate the write to Flash program memory.

- 10. Load the PMDATH:PMDATL register pair with the program memory data to be written.

- Execute the unlock sequence (Section 10.2.2 "Flash Memory Unlock Sequence"). The entire program memory latch content is now written to Flash program memory.

- Note: The program memory write latches are reset to the blank state (0x3FFF) at the completion of every write or erase operation. As a result, it is not necessary to load all the program memory write latches. Unloaded latches will remain in the blank state.

An example of the complete write sequence is shown in Example 10-3. The initial address is loaded into the PMADRH:PMADRL register pair; the data is loaded using indirect addressing.

## 15.2 ADC Operation

### 15.2.1 STARTING A CONVERSION

To enable the ADC module, the ADON bit of the ADCON0 register must be set to a '1'. Setting the GO/ DONE bit of the ADCON0 register to a '1' will start the Analog-to-Digital conversion.

| Note: | The GO/DONE bit should not be set in the |

|-------|------------------------------------------|

|       | same instruction that turns on the ADC.  |

|       | Refer to Section 15.2.6 "ADC Conver-     |

|       | sion Procedure".                         |

### 15.2.2 COMPLETION OF A CONVERSION

When the conversion is complete, the ADC module will:

- Clear the GO/DONE bit

- Set the ADIF Interrupt Flag bit

- Update the ADRESH and ADRESL registers with new conversion result

#### 15.2.3 TERMINATING A CONVERSION

If a conversion must be terminated before completion, the GO/DONE bit can be cleared in software. The ADRESH and ADRESL registers will be updated with the partially complete Analog-to-Digital conversion sample. Incomplete bits will match the last bit converted.

| Note: | A device Reset forces all registers to their |

|-------|----------------------------------------------|

|       | Reset state. Thus, the ADC module is         |

|       | turned off and any pending conversion is     |

|       | terminated.                                  |

## 15.2.4 ADC OPERATION DURING SLEEP

The ADC module can operate during Sleep. This requires the ADC clock source to be set to the FRC option. Performing the ADC conversion during Sleep can reduce system noise. If the ADC interrupt is enabled, the device will wake-up from Sleep when the conversion completes. If the ADC interrupt is disabled, the ADC module is turned off after the conversion completes, although the ADON bit remains set.

When the ADC clock source is something other than FRC, a SLEEP instruction causes the present conversion to be aborted and the ADC module is turned off, although the ADON bit remains set.

## 15.2.5 AUTO-CONVERSION TRIGGER

The auto-conversion trigger allows periodic ADC measurements without software intervention. When a rising edge of the selected source occurs, the GO/DONE bit is set by hardware.

The auto-conversion trigger source is selected with the TRIGSEL<3:0> bits of the ADCON2 register.

Using the auto-conversion trigger does not assure proper ADC timing. It is the user's responsibility to ensure that the ADC timing requirements are met.

See Table 15-2 for auto-conversion sources.

### TABLE 15-2: AUTO-CONVERSION SOURCES

| Source Peripheral | Signal Name |

|-------------------|-------------|

| Timer0            | T0_overflow |

| Timer1            | T1_overflow |

| Timer2            | T2_match    |

| Comparator C1     | C1OUT_sync  |

| Comparator C2     | C2OUT_sync  |

| CLC1              | LC1_out     |

| CLC2              | LC2_out     |

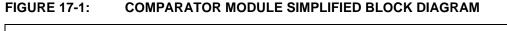

## 17.0 COMPARATOR MODULE

Comparators are used to interface analog circuits to a digital circuit by comparing two analog voltages and providing a digital indication of their relative magnitudes. Comparators are very useful mixed signal building blocks because they provide analog functionality independent of program execution. The analog comparator module includes the following features:

- Independent comparator control

- · Programmable input selection

- · Comparator output is available internally/externally

- · Programmable output polarity

- · Interrupt-on-change

- · Wake-up from Sleep

- · Programmable Speed/Power optimization

- PWM shutdown

- · Programmable and fixed voltage reference

## 17.1 Comparator Overview

A single comparator is shown in Figure 17-2 along with the relationship between the analog input levels and the digital output. When the analog voltage at VIN+ is less than the analog voltage at VIN-, the output of the comparator is a digital low level. When the analog voltage at VIN+ is greater than the analog voltage at VIN-, the output of the comparator is a digital high level.

The comparators available for this device are listed in Table 17-1.

#### TABLE 17-1: AVAILABLE COMPARATORS

| Device        | C1 | C2 |

|---------------|----|----|

| PIC16(L)F1503 | •  | •  |

## 18.2 Register Definitions: Option Register

| R/W-1/1        | R/W-1/1         | R/W-1/1                                                                                    | R/W-1/1       | R/W-1/1        | R/W-1/1          | R/W-1/1          | R/W-1/1      |  |  |  |

|----------------|-----------------|--------------------------------------------------------------------------------------------|---------------|----------------|------------------|------------------|--------------|--|--|--|

| WPUEN          | INTEDG          | TMR0CS                                                                                     | TMR0SE        | PSA            |                  | PS<2:0>          |              |  |  |  |

| bit 7          |                 |                                                                                            |               |                |                  |                  | bit (        |  |  |  |

|                |                 |                                                                                            |               |                |                  |                  |              |  |  |  |

| Legend:        |                 |                                                                                            |               |                |                  |                  |              |  |  |  |

| R = Readab     | ole bit         | W = Writable                                                                               | bit           |                | nented bit, read |                  |              |  |  |  |

| u = Bit is un  | changed         | x = Bit is unki                                                                            | nown          | -n/n = Value a | at POR and BO    | R/Value at all c | other Resets |  |  |  |

| '1' = Bit is s | et              | '0' = Bit is cle                                                                           | ared          |                |                  |                  |              |  |  |  |

|                |                 |                                                                                            |               |                |                  |                  |              |  |  |  |

| bit 7          |                 | ak Pull-Up Ena                                                                             |               |                |                  |                  |              |  |  |  |

|                |                 | pull-ups are dis                                                                           | • •           |                | ,                |                  |              |  |  |  |

|                |                 | ll-ups are enab                                                                            | -             | al WPUX latch  | values           |                  |              |  |  |  |

|                |                 | errupt Edge Sel                                                                            |               |                |                  |                  |              |  |  |  |

|                |                 | 1 = Interrupt on rising edge of INT pin<br>0 = Interrupt on falling edge of INT pin        |               |                |                  |                  |              |  |  |  |

| bit 5          | •               | mer0 Clock Sou                                                                             | •             |                |                  |                  |              |  |  |  |

|                | 1 = Transitior  | n on T0CKI pin                                                                             |               |                |                  |                  |              |  |  |  |

|                | 0 = Internal in | nstruction cycle                                                                           | clock (Fosc/4 | •)             |                  |                  |              |  |  |  |

| bit 4          |                 | TMR0SE: Timer0 Source Edge Select bit                                                      |               |                |                  |                  |              |  |  |  |

|                |                 | nt on high-to-low                                                                          |               | •              |                  |                  |              |  |  |  |

| <b>L</b> # 0   |                 | nt on low-to-hig                                                                           |               | TUCKI pin      |                  |                  |              |  |  |  |

| bit 3          |                 | <b>PSA:</b> Prescaler Assignment bit<br>1 = Prescaler is not assigned to the Timer0 module |               |                |                  |                  |              |  |  |  |

|                |                 | r is assigned to                                                                           |               |                |                  |                  |              |  |  |  |

| bit 2-0        |                 | escaler Rate Se                                                                            |               |                |                  |                  |              |  |  |  |

|                | Bit             | Value Timer0                                                                               | Rate          |                |                  |                  |              |  |  |  |

|                |                 | 000 1:2                                                                                    |               |                |                  |                  |              |  |  |  |

|                |                 | 001 1:4                                                                                    |               |                |                  |                  |              |  |  |  |

|                |                 | 010 1:8                                                                                    |               |                |                  |                  |              |  |  |  |

|                |                 | 011 1:1<br>100 1:3                                                                         |               |                |                  |                  |              |  |  |  |

|                |                 | 101 1:6                                                                                    |               |                |                  |                  |              |  |  |  |

## REGISTER 18-1: OPTION\_REG: OPTION REGISTER

## TABLE 18-1: SUMMARY OF REGISTERS ASSOCIATED WITH TIMER0

1:128

1:256

110

111

| Name       | Bit 7                                  | Bit 6                                       | Bit 5  | Bit 4  | Bit 3 | Bit 2  | Bit 1  | Bit 0  | Register<br>on Page |

|------------|----------------------------------------|---------------------------------------------|--------|--------|-------|--------|--------|--------|---------------------|

| ADCON2     | TRIGSEL<3:0>                           |                                             |        |        | _     | -      |        |        | 121                 |

| INTCON     | GIE                                    | PEIE                                        | TMR0IE | INTE   | IOCIE | TMR0IF | INTF   | IOCIF  | 64                  |

| OPTION_REG | WPUEN INTEDG TMR0CS TMR0SE PSA PS<2:0> |                                             |        |        |       | 139    |        |        |                     |

| TMR0       | Holding Reg                            | Holding Register for the 8-bit Timer0 Count |        |        |       |        | 137*   |        |                     |

| TRISA      | _                                      | _                                           | TRISA5 | TRISA4 | _(1)  | TRISA2 | TRISA1 | TRISA0 | 98                  |

Legend: — = Unimplemented location, read as '0'. Shaded cells are not used by the Timer0 module. \* Page provides register information.

Note 1: Unimplemented, read as '1'.

### 19.5.2.1 T1G Pin Gate Operation

The T1G pin is one source for Timer1 gate control. It can be used to supply an external source to the Timer1 gate circuitry.

#### 19.5.2.2 Timer0 Overflow Gate Operation

When Timer0 increments from FFh to 00h, a low-tohigh pulse will automatically be generated and internally supplied to the Timer1 gate circuitry.

### 19.5.3 TIMER1 GATE TOGGLE MODE

When Timer1 Gate Toggle mode is enabled, it is possible to measure the full-cycle length of a Timer1 gate signal, as opposed to the duration of a single level pulse.

The Timer1 gate source is routed through a flip-flop that changes state on every incrementing edge of the signal. See Figure 19-4 for timing details.

Timer1 Gate Toggle mode is enabled by setting the T1GTM bit of the T1GCON register. When the T1GTM bit is cleared, the flip-flop is cleared and held clear. This is necessary in order to control which edge is measured.

| Note: | Enabling Toggle mode at the same time       |

|-------|---------------------------------------------|

|       | as changing the gate polarity may result in |

|       | indeterminate operation.                    |

#### 19.5.4 TIMER1 GATE SINGLE-PULSE MODE

When Timer1 Gate Single-Pulse mode is enabled, it is possible to capture a single pulse gate event. Timer1 Gate Single-Pulse mode is first enabled by setting the T1GSPM bit in the T1GCON register. Next, the T1GGO/ DONE bit in the T1GCON register must be set. The Timer1 will be fully enabled on the next incrementing edge. On the next trailing edge of the pulse, the T1GGO/ DONE bit will automatically be cleared. No other gate events will be allowed to increment Timer1 until the T1GGO/DONE bit is once again set in software. See Figure 19-5 for timing details.

If the Single Pulse Gate mode is disabled by clearing the T1GSPM bit in the T1GCON register, the T1GGO/DONE bit should also be cleared.

Enabling the Toggle mode and the Single-Pulse mode simultaneously will permit both sections to work together. This allows the cycle times on the Timer1 gate source to be measured. See Figure 19-6 for timing details.

### 19.5.5 TIMER1 GATE VALUE STATUS

When Timer1 Gate Value Status is utilized, it is possible to read the most current level of the gate control value. The value is stored in the T1GVAL bit in the T1GCON register. The T1GVAL bit is valid even when the Timer1 gate is not enabled (TMR1GE bit is cleared).

## 19.5.6 TIMER1 GATE EVENT INTERRUPT

When Timer1 Gate Event Interrupt is enabled, it is possible to generate an interrupt upon the completion of a gate event. When the falling edge of T1GVAL occurs, the TMR1GIF flag bit in the PIR1 register will be set. If the TMR1GIE bit in the PIE1 register is set, then an interrupt will be recognized.

The TMR1GIF flag bit operates even when the Timer1 gate is not enabled (TMR1GE bit is cleared).

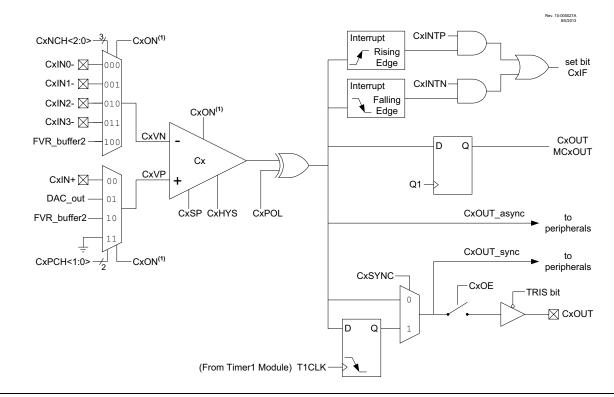

### FIGURE 21-4: SPI MASTER AND MULTIPLE SLAVE CONNECTION

#### 21.2.1 SPI MODE REGISTERS

The MSSP module has five registers for SPI mode operation. These are:

- MSSP STATUS register (SSPxSTAT)

- MSSP Control Register 1 (SSPxCON1)

- MSSP Control Register 3 (SSPxCON3)

- MSSP Data Buffer register (SSPxBUF)

- MSSP Address register (SSPxADD)

- MSSP Shift register (SSPxSR) (Not directly accessible)

SSPxCON1 and SSPxSTAT are the control and STATUS registers in SPI mode operation. The SSPxCON1 register is readable and writable. The lower six bits of the SSPxSTAT are read-only. The upper two bits of the SSPxSTAT are read/write.

In SPI master mode, SSPxADD can be loaded with a value used in the Baud Rate Generator. More information on the Baud Rate Generator is available in **Section21.7 "Baud Rate Generator**".

SSPxSR is the shift register used for shifting data in and out. SSPxBUF provides indirect access to the SSPxSR register. SSPxBUF is the buffer register to which data bytes are written, and from which data bytes are read.

In receive operations, SSPxSR and SSPxBUF together create a buffered receiver. When SSPxSR receives a complete byte, it is transferred to SSPxBUF and the SSPxIF interrupt is set.

During transmission, the SSPxBUF is not buffered. A write to SSPxBUF will write to both SSPxBUF and SSPxSR.

### 21.5.3.3 7-bit Transmission with Address Hold Enabled

Setting the AHEN bit of the SSPxCON3 register enables additional clock stretching and interrupt generation after the eighth falling edge of a received matching address. Once a matching address has been clocked in, CKP is cleared and the SSPxIF interrupt is set.

Figure 21-19 displays a standard waveform of a 7-bit Address Slave Transmission with AHEN enabled.

- 1. Bus starts idle.

- Master sends Start condition; the S bit of SSPxSTAT is set; SSPxIF is set if interrupt on Start detect is enabled.

- Master sends matching address with R/W bit set. After the eighth falling edge of the SCLx line the CKP bit is cleared and SSPxIF interrupt is generated.

- 4. Slave software clears SSPxIF.

- 5. Slave software reads ACKTIM bit of SSPxCON3 register, and  $R/\overline{W}$  and  $D/\overline{A}$  of the SSPxSTAT register to determine the source of the interrupt.

- 6. Slave reads the address value from the SSPxBUF register clearing the BF bit.

- Slave software decides from this information if it wishes to ACK or not ACK and sets the ACKDT bit of the SSPxCON2 register accordingly.

- 8. Slave sets the CKP bit releasing SCLx.

- 9. Master clocks in the  $\overline{ACK}$  value from the slave.

- 10. Slave hardware automatically clears the CKP bit and sets SSPxIF after the ACK if the R/W bit is set.

- 11. Slave software clears SSPxIF.

- 12. Slave loads value to transmit to the master into SSPxBUF setting the BF bit.

Note: SSPxBUF cannot be loaded until after the ACK.

- 13. Slave sets the CKP bit, releasing the clock.

- 14. Master clocks out the data from the slave and sends an ACK value on the ninth SCLx pulse.

- 15. Slave hardware copies the ACK value into the ACKSTAT bit of the SSPxCON2 register.

- 16. Steps 10-15 are repeated for each byte transmitted to the master from the slave.

- 17. If the master sends a not ACK the slave releases the bus allowing the master to send a Stop and end the communication.

**Note:** Master must send a not ACK on the last byte to ensure that the slave releases the SCLx line to receive a Stop.

| R/W-x/u          | R/W-x/u                                                                                                        | R/W-x/u                             | R/W-x/u        | R/W-x/u        | R/W-x/u          | R/W-x/u          | R/W-x/u      |  |

|------------------|----------------------------------------------------------------------------------------------------------------|-------------------------------------|----------------|----------------|------------------|------------------|--------------|--|

| LCxG2D4T         | LCxG2D4N                                                                                                       | LCxG2D3T                            | LCxG2D3N       | LCxG2D2T       | LCxG2D2N         | LCxG2D1T         | LCxG2D1N     |  |

| bit 7            |                                                                                                                |                                     |                |                |                  |                  | bit 0        |  |

|                  |                                                                                                                |                                     |                |                |                  |                  |              |  |

| Legend:          |                                                                                                                |                                     |                |                |                  |                  |              |  |

| R = Readable     |                                                                                                                | W = Writable                        |                |                | mented bit, read |                  |              |  |

| u = Bit is unch  | anged                                                                                                          | x = Bit is unknown                  |                | -n/n = Value a | at POR and BO    | R/Value at all c | other Resets |  |

| '1' = Bit is set |                                                                                                                | '0' = Bit is clea                   | ared           |                |                  |                  |              |  |

| hit 7            |                                                                                                                | Cata 2 Data 4 T                     |                | rtad) bit      |                  |                  |              |  |

| bit 7            |                                                                                                                | Gate 2 Data 4 7<br>gated into lcxg  |                | neu) bii       |                  |                  |              |  |

|                  |                                                                                                                | not gated into                      |                |                |                  |                  |              |  |

| bit 6            |                                                                                                                | Gate 2 Data 4 I                     | •              | rted) bit      |                  |                  |              |  |

|                  | 1 = Icxd4N is                                                                                                  | gated into lcxg                     | g2             | ·              |                  |                  |              |  |

|                  |                                                                                                                | not gated into                      | •              |                |                  |                  |              |  |

| bit 5            |                                                                                                                | Gate 2 Data 3 T                     | •              | rted) bit      |                  |                  |              |  |

|                  | 1 = lcxd3T is gated into lcxg2                                                                                 |                                     |                |                |                  |                  |              |  |

| bit 4            | <ul> <li>0 = lcxd3T is not gated into lcxg2</li> <li>LCxG2D3N: Gate 2 Data 3 Negated (inverted) bit</li> </ul> |                                     |                |                |                  |                  |              |  |

| bit 4            |                                                                                                                | gated into lcx                      | •              |                |                  |                  |              |  |

|                  | 0 = Icxd3N is not gated into Icxg2                                                                             |                                     |                |                |                  |                  |              |  |

| bit 3            | LCxG2D2T: (                                                                                                    | Gate 2 Data 2 T                     | rue (non-invei | rted) bit      |                  |                  |              |  |

|                  | 1 = lcxd2T is gated into lcxg2                                                                                 |                                     |                |                |                  |                  |              |  |

|                  |                                                                                                                | not gated into                      | -              |                |                  |                  |              |  |

| bit 2            |                                                                                                                | Gate 2 Data 2 I                     | •              | rted) bit      |                  |                  |              |  |

|                  |                                                                                                                | s gated into lcxo<br>not gated into |                |                |                  |                  |              |  |

| bit 1            |                                                                                                                | •                                   | •              | rted) bit      |                  |                  |              |  |

| 2                | LCxG2D1T: Gate 2 Data 1 True (non-inverted) bit<br>1 = lcxd1T is gated into lcxg2                              |                                     |                |                |                  |                  |              |  |

|                  |                                                                                                                | not gated into                      |                |                |                  |                  |              |  |

| bit 0            | LCxG2D1N:                                                                                                      | Gate 2 Data 1 I                     | Negated (inver | rted) bit      |                  |                  |              |  |

|                  |                                                                                                                | gated into lcxo                     |                |                |                  |                  |              |  |

|                  | 0 = ICX01N IS                                                                                                  | not gated into                      | icxg2          |                |                  |                  |              |  |

|                  |                                                                                                                |                                     |                |                |                  |                  |              |  |

|                  |                                                                                                                |                                     |                |                |                  |                  |              |  |

## REGISTER 23-6: CLCxGLS1: GATE 2 LOGIC SELECT REGISTER

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | R/W-x/u          | R/W-x/u       | R/W-x/u            | R/W-x/u        | R/W-x/u        | R/W-x/u       | R/W-x/u          | R/W-x/u      |  |

|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------|---------------|--------------------|----------------|----------------|---------------|------------------|--------------|--|

| Legend:         R = Readable bit       W = Writable bit       U = Unimplemented bit, read as '0'         u = Bit is unchanged       x = Bit is unknown       -n/n = Value at POR and BOR/Value at all other Resets         '1' = Bit is set       '0' = Bit is cleared         bit 7       LCxG4D4T: Gate 4 Data 4 True (non-inverted) bit         1 = lcxd4T is gated into lcxg4       0 = lcxd4T is not gated into lcxg4         0 = lcxd4T is gated into lcxg4       0 = lcxd4N is not gated into lcxg4         0 = lcxd4N is gated into lcxg4       0 = lcxd4N is not gated into lcxg4         0 = lcxd3T is gated into lcxg4       0 = lcxd3N is gated into lcxg4         0 = lcxd3T is gated into lcxg4       0 = lcxd3T is gated into lcxg4         0 = lcxd3T is gated into lcxg4       0 = lcxd3T is not gated into lcxg4         0 = lcxd3T is not gated into lcxg4       0 = lcxd3N is gated into lcxg4         0 = lcxd3N is gated into lcxg4       0 = lcxd3N is gated into lcxg4         0 = lcxd3N is not gated into lcxg4       0 = lcxd3N is not gated into lcxg4         0 = lcxd2T is not gated into lcxg4       0 = lcxd2T is not gated into lcxg4         0 = lcxd2T is not gated into lcxg4       0 = lcxd2T is not gated into lcxg4         0 = lcxd2T is not gated into lcxg4       0 = lcxd2T is not gated into lcxg4         0 = lcxd2T is not gated into lcxg4       0 = lcxd2T is not gated into lcxg4                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | LCxG4D4T         | LCxG4D4N      | LCxG4D3T           | LCxG4D3N       | LCxG4D2T       | LCxG4D2N      | LCxG4D1T         | LCxG4D1N     |  |

| R = Readable bit       W = Writable bit       U = Unimplemented bit, read as '0'         u = Bit is unchanged       x = Bit is unknown       -n/n = Value at POR and BOR/Value at all other Resets         '1' = Bit is set       '0' = Bit is cleared         bit 7       LCxG4D4T: Gate 4 Data 4 True (non-inverted) bit         1 = lcxd4T is gated into lcxg4       0 = lcxd4T is not gated into lcxg4         0 = lcxd4T is not gated into lcxg4       0 = lcxd4N is gated into lcxg4         0 = lcxd4N is gated into lcxg4       0 = lcxd4N is gated into lcxg4         0 = lcxd4N is not gated into lcxg4       0 = lcxd3T is not gated into lcxg4         0 = lcxd3T is gated into lcxg4       0 = lcxd3T is gated into lcxg4         0 = lcxd3T is gated into lcxg4       0 = lcxd3T is gated into lcxg4         0 = lcxd3T is not gated into lcxg4       0 = lcxd3N is gated into lcxg4         0 = lcxd3N is gated into lcxg4       0 = lcxd3N is gated into lcxg4         0 = lcxd3N is not gated into lcxg4       0 = lcxd3N is not gated into lcxg4         0 = lcxd2T is gated into lcxg4       0 = lcxd2T is not gated into lcxg4         0 = lcxd2T is not gated into lcxg4       0 = lcxd2T is not gated into lcxg4         0 = lcxd2N is gated into lcxg4       0 = lcxd2N is gated into lcxg4         0 = lcxd2N is gated into lcxg4       0 = lcxd2N is gated into lcxg4         0 = lcxd2N is not gated into lcxg4       0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | bit 7            |               |                    |                |                |               |                  | bit 0        |  |

| R = Readable bit       W = Writable bit       U = Unimplemented bit, read as '0'         u = Bit is unchanged       x = Bit is unknown       -n/n = Value at POR and BOR/Value at all other Resets         '1' = Bit is set       '0' = Bit is cleared         bit 7       LCxG4D4T: Gate 4 Data 4 True (non-inverted) bit         1 = lcxd4T is gated into lcxg4       0 = lcxd4T is not gated into lcxg4         0 = lcxd4T is ong gated into lcxg4       0 = lcxd4N is gated into lcxg4         0 = lcxd4N is gated into lcxg4       0 = lcxd4N is gated into lcxg4         0 = lcxd4N is not gated into lcxg4       0 = lcxd4N is not gated into lcxg4         0 = lcxd3T is not gated into lcxg4       0 = lcxd3T is not gated into lcxg4         0 = lcxd3T is gated into lcxg4       0 = lcxd3N is gated into lcxg4         0 = lcxd3N is gated into lcxg4       0 = lcxd3N is gated into lcxg4         0 = lcxd3N is gated into lcxg4       0 = lcxd3N is not gated into lcxg4         0 = lcxd3N is not gated into lcxg4       0 = lcxd2T is not gated into lcxg4         0 = lcxd2T is gated into lcxg4       0 = lcxd2T is not gated into lcxg4         0 = lcxd2N is gated into lcxg4       0 = lcxd2N is gated into lcxg4         0 = lcxd2T is not gated into lcxg4       0 = lcxd2N is gated into lcxg4         0 = lcxd2N is gated into lcxg4       0 = lcxd2N is gated into lcxg4         0 = lcxd2N is gated into lcxg4       0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |                  |               |                    |                |                |               |                  |              |  |

| u = Bit is unchanged       x = Bit is unknown       -n/n = Value at POR and BOR/Value at all other Resets         '1' = Bit is set       '0' = Bit is cleared         bit 7       LCxG4D4T: Gate 4 Data 4 True (non-inverted) bit         1 = lcxd4T is gated into lcxg4       0 = lcxd4T is not gated into lcxg4         bit 6       LCxG4D4N: Gate 4 Data 4 Negated (inverted) bit         1 = lcxd4N is gated into lcxg4       0 = lcxd4N is not gated into lcxg4         bit 5       LCxG4D3T: Gate 4 Data 3 True (non-inverted) bit         1 = lcxd3T is gated into lcxg4       0 = lcxd3T is not gated into lcxg4         bit 4       LCxG4D3N: Gate 4 Data 3 True (non-inverted) bit         1 = lcxd3T is gated into lcxg4       0 = lcxd3T is not gated into lcxg4         bit 4       LCxG4D3N: Gate 4 Data 3 Negated (inverted) bit         1 = lcxd3T is gated into lcxg4       0 = lcxd3T is not gated into lcxg4         0 = lcxd3T is not gated into lcxg4       0 = lcxd2T is gated into lcxg4         0 = lcxd2T is not gated into lcxg4       0 = lcxd2T is gated into lcxg4         0 = lcxd2T is gated into lcxg4       0 = lcxd2T is gated into lcxg4         0 = lcxd2T is not gated into lcxg4       0 = lcxd2T is not gated into lcxg4         0 = lcxd2T is not gated into lcxg4       0 = lcxd2T is not gated into lcxg4         0 = lcxd2T is not gated into lcxg4       0 = lcxd2T is not gated into lcxg4                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | -                |               |                    |                |                |               |                  |              |  |

| '1' = Bit is set       '0' = Bit is cleared         bit 7       LCxG4D4T: Gate 4 Data 4 True (non-inverted) bit         1 = lcxd4T is gated into lcxg4       0 = lcxd4T is not gated into lcxg4         bit 6       LCxG4DAN: Gate 4 Data 4 Negated (inverted) bit         1 = lcxd4N is gated into lcxg4       0 = lcxd4N is gated into lcxg4         0 = lcxd4N is gated into lcxg4       0 = lcxd4N is not gated into lcxg4         0 = lcxd3T is gated into lcxg4       0 = lcxd3T is gated into lcxg4         0 = lcxd3T is gated into lcxg4       0 = lcxd3T is not gated into lcxg4         0 = lcxd3T is gated into lcxg4       0 = lcxd3T is gated into lcxg4         0 = lcxd3T is gated into lcxg4       0 = lcxd3T is gated into lcxg4         0 = lcxd3T is gated into lcxg4       0 = lcxd3T is not gated into lcxg4         0 = lcxd3N is gated into lcxg4       0 = lcxd3N is gated into lcxg4         0 = lcxd3N is gated into lcxg4       0 = lcxd2T is not gated into lcxg4         0 = lcxd2T is gated into lcxg4       0 = lcxd2T is gated into lcxg4         0 = lcxd2N is gated into lcxg4       0 = lcxd2N is gated into lcxg4         0 = lcxd2T is not gated into lcxg4       0 = lcxd2T is not gated into lcxg4         0 = lcxd2N is gated into lcxg4       0 = lcxd2N is not gated into lcxg4         0 = lcxd2N is gated into lcxg4       0 = lcxd2N is not gated into lcxg4         bit 1       L                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | R = Readable     | bit           | W = Writable       | bit            | •              |               |                  |              |  |

| bit 7 LCxG4D4T: Gate 4 Data 4 True (non-inverted) bit<br>1 = lcxd4T is gated into lcxg4<br>0 = lcxd4T is not gated into lcxg4<br>bit 6 LCxG4D4N: Gate 4 Data 4 Negated (inverted) bit<br>1 = lcxd4N is gated into lcxg4<br>0 = lcxd4N is not gated into lcxg4<br>bit 5 LCxG4D3T: Gate 4 Data 3 True (non-inverted) bit<br>1 = lcxd3T is gated into lcxg4<br>0 = lcxd3T is not gated into lcxg4<br>bit 4 LCxG4D3N: Gate 4 Data 3 Negated (inverted) bit<br>1 = lcxd3N is gated into lcxg4<br>0 = lcxd3N is not gated into lcxg4<br>0 = lcxd3N is not gated into lcxg4<br>0 = lcxd3N is not gated into lcxg4<br>0 = lcxd2T is gated into lcxg4<br>0 = lcxd2T is gated into lcxg4<br>0 = lcxd2T is not gated into lcxg4<br>0 = lcxd2N is gated into lcxg4<br>0 = lcxd2T is not gated into lcxg4<br>0 = lcxd2T is not gated into lcxg4<br>0 = lcxd2T is not gated into lcxg4<br>0 = lcxd2T is gated into lcxg4<br>0 = lcxd2T is not gated into lcxg4<br>0 = lcxd1T is not gated into lcxg4                                                                                                                                                                                                                                             |                  | anged         | x = Bit is unknown |                | -n/n = Value a | at POR and BO | R/Value at all c | other Resets |  |

| 1 = lcxd4T is gated into lcxg4         0 = lcxd4T is not gated into lcxg4         bit 6       LCxG4D4N: Gate 4 Data 4 Negated (inverted) bit         1 = lcxd4N is gated into lcxg4         0 = lcxd4N is not gated into lcxg4         bit 5       LCxG4D3T: Gate 4 Data 3 True (non-inverted) bit         1 = lcxd3T is gated into lcxg4         0 = lcxd3T is not gated into lcxg4         0 = lcxd3T is not gated into lcxg4         0 = lcxd3T is not gated into lcxg4         bit 4       LCxG4D3N: Gate 4 Data 3 Negated (inverted) bit         1 = lcxd3N is gated into lcxg4         0 = lcxd3T is not gated into lcxg4         0 = lcxd3N is not gated into lcxg4         0 = lcxd2N is gated into lcxg4         0 = lcxd2T is not gated into lcxg4         0 = lcxd2N: Gate 4 Data 2 Negated (inverted) bit         1 = lcxd2N: gated into lcxg4         0 = lcxd2T is not gated into lcxg4         0 = lcxd2T is not gated into lcxg4         0 = lcxd2N: is not gated into lcxg4                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | '1' = Bit is set |               | '0' = Bit is clea  | ared           |                |               |                  |              |  |

| 1 = lcxd4T is gated into lcxg4         0 = lcxd4T is not gated into lcxg4         bit 6       LCxG4D4N: Gate 4 Data 4 Negated (inverted) bit         1 = lcxd4N is gated into lcxg4         0 = lcxd4N is not gated into lcxg4         bit 5       LCxG4D3T: Gate 4 Data 3 True (non-inverted) bit         1 = lcxd3T is gated into lcxg4         0 = lcxd3T is not gated into lcxg4         0 = lcxd3T is not gated into lcxg4         0 = lcxd3T is not gated into lcxg4         bit 4       LCxG4D3N: Gate 4 Data 3 Negated (inverted) bit         1 = lcxd3N is gated into lcxg4         0 = lcxd3T is not gated into lcxg4         0 = lcxd3N is not gated into lcxg4         0 = lcxd2N is gated into lcxg4         0 = lcxd2T is not gated into lcxg4         0 = lcxd2N: Gate 4 Data 2 Negated (inverted) bit         1 = lcxd2N: gated into lcxg4         0 = lcxd2T is not gated into lcxg4         0 = lcxd2T is not gated into lcxg4         0 = lcxd2N: is not gated into lcxg4                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | L:1 7            |               |                    |                | 4              |               |                  |              |  |

| 0 = lcxd4T is not gated into lcxg4         bit 6       LCxG4D4N: Gate 4 Data 4 Negated (inverted) bit         1 = lcxd4N is gated into lcxg4       0 = lcxd4N is not gated into lcxg4         bit 5       LCxG4D3T: Gate 4 Data 3 True (non-inverted) bit         1 = lcxd3T is gated into lcxg4       0 = lcxd3T is not gated into lcxg4         bit 4       LCxG4D3N: Gate 4 Data 3 Negated (inverted) bit         1 = lcxd3N is gated into lcxg4       0 = lcxd3N is gated into lcxg4         bit 3       LCxG4D2T: Gate 4 Data 2 Negated (inverted) bit         1 = lcxd3N is gated into lcxg4       0 = lcxd2T is gated into lcxg4         bit 3       LCxG4D2T: Gate 4 Data 2 True (non-inverted) bit         1 = lcxd2T is gated into lcxg4       0 = lcxd2T is not gated into lcxg4         0 = lcxd2T is gated into lcxg4       0 = lcxd2T is not gated into lcxg4         0 = lcxd2T is gated into lcxg4       0 = lcxd2T is not gated into lcxg4         bit 2       LCxG4D2N: Gate 4 Data 2 Negated (inverted) bit         1 = lcxd2N is gated into lcxg4       0 = lcxd2N is not gated into lcxg4         bit 1       LCxG4D1T: Gate 4 Data 1 True (non-inverted) bit         1 = lcxd1T is gated into lcxg4       0 = lcxd1T is not gated into lcxg4         bit 1       LCxG4D1T: Gate 4 Data 1 True (non-inverted) bit         1 = lcxd1T is gated into lcxg4       0 = lcxd1T is not gated into lcxg4                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | DIT /            |               |                    |                | ted) bit       |               |                  |              |  |

| bit 6       LCxG4D4N: Gate 4 Data 4 Negated (inverted) bit         1 = lcxd4N is gated into lcxg4       0 = lcxd4N is not gated into lcxg4         bit 5       LCxG4D3T: Gate 4 Data 3 True (non-inverted) bit         1 = lcxd3T is gated into lcxg4       0 = lcxd3T is not gated into lcxg4         0 = lcxd3T is not gated into lcxg4       0 = lcxd3T is not gated into lcxg4         bit 4       LCxG4D3N: Gate 4 Data 3 Negated (inverted) bit         1 = lcxd3N is gated into lcxg4       0 = lcxd3N is not gated into lcxg4         0 = lcxd3N is not gated into lcxg4       0 = lcxd3N is not gated into lcxg4         0 = lcxd3N is not gated into lcxg4       0 = lcxd2T is gated into lcxg4         0 = lcxd2T is gated into lcxg4       0 = lcxd2T is not gated into lcxg4         0 = lcxd2T is not gated into lcxg4       0 = lcxd2T is not gated into lcxg4         0 = lcxd2N is gated into lcxg4       0 = lcxd2N is not gated into lcxg4         0 = lcxd2N is gated into lcxg4       0 = lcxd2N is not gated into lcxg4         0 = lcxd2N is not gated into lcxg4       0 = lcxd2N is not gated into lcxg4         bit 1       LCxG4D1T: Gate 4 Data 1 True (non-inverted) bit         1 = lcxd1T is gated into lcxg4       0 = lcxd1T is not gated into lcxg4         0 = lcxd1T is not gated into lcxg4       0 = lcxd1T is not gated into lcxg4         bit 0       LCxG4D1N: Gate 4 Data 1 Negated (inverted) bit <tr< td=""><td></td><td></td><td></td><td></td><td></td><td></td><td></td><td></td></tr<>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |                  |               |                    |                |                |               |                  |              |  |