Welcome to **E-XFL.COM**

What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded - Microcontrollers</u>"

| Details                    |                                                                            |

|----------------------------|----------------------------------------------------------------------------|

| Product Status             | Active                                                                     |

| Core Processor             | PIC                                                                        |

| Core Size                  | 8-Bit                                                                      |

| Speed                      | 20MHz                                                                      |

| Connectivity               | I <sup>2</sup> C, SPI                                                      |

| Peripherals                | Brown-out Detect/Reset, POR, PWM, WDT                                      |

| Number of I/O              | 11                                                                         |

| Program Memory Size        | 3.5KB (2K x 14)                                                            |

| Program Memory Type        | FLASH                                                                      |

| EEPROM Size                | -                                                                          |

| RAM Size                   | 128 x 8                                                                    |

| Voltage - Supply (Vcc/Vdd) | 1.8V ~ 3.6V                                                                |

| Data Converters            | A/D 8x10b                                                                  |

| Oscillator Type            | Internal                                                                   |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                          |

| Mounting Type              | Surface Mount                                                              |

| Package / Case             | 16-UFQFN Exposed Pad                                                       |

| Supplier Device Package    | 16-UQFN (3x3)                                                              |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic16lf1503-i-mv |

# 2.1 Automatic Interrupt Context Saving

During interrupts, certain registers are automatically saved in shadow registers and restored when returning from the interrupt. This saves stack space and user code. See Section 7.5 "Automatic Context Saving", for more information.

# 2.2 16-Level Stack with Overflow and Underflow

These devices have a hardware stack memory 15 bits wide and 16 words deep. A Stack Overflow or Underflow will set the appropriate bit (STKOVF or STKUNF) in the PCON register, and if enabled, will cause a software Reset. See **Section 3.5** "Stack" for more details.

# 2.3 File Select Registers

There are two 16-bit File Select Registers (FSR). FSRs can access all file registers and program memory, which allows one Data Pointer for all memory. When an FSR points to program memory, there is one additional instruction cycle in instructions using INDF to allow the data to be fetched. General purpose memory can now also be addressed linearly, providing the ability to access contiguous data larger than 80 bytes. There are also new instructions to support the FSRs. See **Section 3.6 "Indirect Addressing"** for more details.

### 2.4 Instruction Set

There are 49 instructions for the enhanced mid-range CPU to support the features of the CPU. See **Section 27.0** "Instruction **Set Summary**" for more details.

DS40001607D-page 20

Legend:

|               | BANK 8                       |              | BANK 9                       |              | BANK 10                      |              | BANK 11                      |              | BANK 12                      |              | BANK 13                      |               | BANK 14                      |              | BANK 15                      |

|---------------|------------------------------|--------------|------------------------------|--------------|------------------------------|--------------|------------------------------|--------------|------------------------------|--------------|------------------------------|---------------|------------------------------|--------------|------------------------------|

| 400h          | Core Registers               | 480h         | Core Registers               | 500h         | Core Registers               | 580h         | Core Registers               | 600h         | Core Registers               | 680h         | Core Registers               | 700h          | Core Registers               | 780h         | Core Registers               |

| 4001          | (Table 3-2)                  | 4001         | (Table 3-2)                  | =001         | (Table 3-2)                  | =001         | (Table 3-2)                  | 0001         | (Table 3-2)                  | 0001         | (Table 3-2)                  |               | (Table 3-2)                  | =001         | (Table 3-2)                  |

| 40Bh          |                              | 48Bh         |                              | 50Bh         |                              | 58Bh         |                              | 60Bh         |                              | 68Bh         |                              | 70Bh          |                              | 78Bh         |                              |

| 40Ch          |                              | 48Ch         | _                            | 50Ch         | _                            | 58Ch         |                              | 60Ch         | _                            | 68Ch         | _                            | 70Ch          | _                            | 78Ch         |                              |

| 40Dh          |                              | 48Dh<br>48Eh |                              | 50Dh<br>50Eh |                              | 58Dh<br>58Eh |                              | 60Dh<br>60Eh |                              | 68Dh<br>68Eh | <u> </u>                     | 70Dh<br>70Eh  |                              | 78Dh<br>78Eh |                              |

| 40Eh<br>40Fh  |                              | 48En<br>48Fh |                              | 50En<br>50Fh |                              | 58En<br>58Fh |                              | 60Fh         |                              | 68Fh         |                              | 70En<br>70Fh  |                              | 78En<br>78Fh |                              |

| 40FII<br>410h |                              | 490h         |                              | 510h         |                              | 590h         |                              | 610h         |                              | 690h         |                              | 70FII<br>710h |                              | 790h         |                              |

| 411h          |                              | 491h         |                              | 510h         |                              | 591h         |                              | 611h         | PWM1DCL                      | 691h         | CWG1DBR                      | 711h          |                              | 791h         |                              |

| 412h          |                              | 492h         |                              | 511h         |                              | 592h         |                              | 612h         | PWM1DCH                      | 692h         | CWG1DBR<br>CWG1DBF           | 712h          |                              | 792h         | _                            |

| 413h          |                              | 493h         |                              | 512h         |                              | 593h         |                              | 613h         | PWM1CON                      | 693h         | CWG1CON0                     | 713h          |                              | 793h         |                              |

| 414h          | _                            | 494h         | _                            | 514h         | _                            | 594h         | _                            | 614h         | PWM2DCL                      | 694h         | CWG1CON1                     | 714h          | _                            | 794h         | _                            |

| 415h          | _                            | 495h         | _                            | 515h         | _                            | 595h         | _                            | 615h         | PWM2DCH                      | 695h         | CWG1CON2                     | 715h          | _                            | 795h         | _                            |

| 416h          | _                            | 496h         | _                            | 516h         | _                            | 596h         | _                            | 616h         | PWM2CON                      | 696h         | _                            | 716h          | _                            | 796h         | _                            |

| 417h          | _                            | 497h         | _                            | 517h         | _                            | 597h         | _                            | 617h         | PWM3DCL                      | 697h         | _                            | 717h          | _                            | 797h         | _                            |

| 418h          | _                            | 498h         | NCO1ACCL                     | 518h         | _                            | 598h         | _                            | 618h         | PWM3DCH                      | 698h         | _                            | 718h          | _                            | 798h         | _                            |

| 419h          | _                            | 499h         | NCO1ACCH                     | 519h         | _                            | 599h         | _                            | 619h         | PWM3CON                      | 699h         | _                            | 719h          | -                            | 799h         | _                            |

| 41Ah          | _                            | 49Ah         | NCO1ACCU                     | 51Ah         | _                            | 59Ah         | _                            | 61Ah         | PWM4DCL                      | 69Ah         | _                            | 71Ah          |                              | 79Ah         | _                            |

| 41Bh          | _                            | 49Bh         | NCO1INCL                     | 51Bh         | _                            | 59Bh         | _                            | 61Bh         | PWM4DCH                      | 69Bh         | _                            | 71Bh          | _                            | 79Bh         | _                            |

| 41Ch          | _                            | 49Ch         | NCO1INCH                     | 51Ch         | _                            | 59Ch         | _                            | 61Ch         | PWM4CON                      | 69Ch         | _                            | 71Ch          |                              | 79Ch         | _                            |

| 41Dh          | _                            | 49Dh         | _                            | 51Dh         | _                            | 59Dh         | _                            | 61Dh         | _                            | 69Dh         | _                            | 71Dh          | _                            | 79Dh         | _                            |

| 41Eh          | _                            | 49Eh         | NCO1CON                      | 51Eh         | _                            | 59Eh         |                              | 61Eh         | _                            | 69Eh         | _                            | 71Eh          | _                            | 79Eh         | _                            |

| 41Fh          | _                            | 49Fh         | NCO1CLK                      | 51Fh         | _                            | 59Fh         | _                            | 61Fh         | _                            | 69Fh         | _                            | 71Fh          | _                            | 79Fh         | _                            |

| 420h          |                              | 4A0h         |                              | 520h         |                              | 5A0h         |                              | 620h         |                              | 6A0h         |                              | 720h          |                              | 7A0h         |                              |

|               | Unimplemented<br>Read as '0' |              | Unimplemented<br>Read as '0' |              | Unimplemented<br>Read as '0' |              | Unimplemented<br>Read as '0' |              | Unimplemented<br>Read as '0' |              | Unimplemented<br>Read as '0' |               | Unimplemented<br>Read as '0' |              | Unimplemented<br>Read as '0' |

| 46Fh          |                              | 4EFh         |                              | 56Fh         |                              | 5EFh         |                              | 66Fh         |                              | 6EFh         |                              | 76Fh          |                              | 7EFh         |                              |

| 470h          |                              | 4F0h         |                              | 570h         |                              | 5F0h         |                              | 670h         |                              | 6F0h         |                              | 770h          |                              | 7F0h         |                              |

|               | Common RAM                   |              | Common RAM                   |              | Common RAM                   |              | Common RAM                   |              | Common RAM                   |              | Common RAM                   |               | Common RAM                   |              | Common RAM                   |

|               | (Accesses                    |              | (Accesses                    |              | (Accesses                    |              | (Accesses                    |              | (Accesses                    |              | (Accesses                    |               | (Accesses                    |              | (Accesses                    |

| 47Fh          | 70h – 7Fh)                   | 4FFh         | 70h – 7Fh)                   | 57Fh         | 70h – 7Fh)                   | 5FFh         | 70h – 7Fh)                   | 67Fh         | 70h – 7Fh)                   | 6FFh         | 70h – 7Fh)                   | 77Fh          | 70h – 7Fh)                   | 7FFh         | 70h – 7Fh)                   |

|               |                              |              |                              | 0            |                              | 0            |                              | 0            |                              | ] •          |                              |               |                              |              |                              |

| _             | BANK 16                      |              | BANK 17                      |              | BANK 18                      |              | BANK 19                      |              | BANK 20                      | _            | BANK 21                      | -             | BANK 22                      |              | BANK 23                      |

| 800h          | Core Registers               | 880h         | Core Registers               | 900h         | Core Registers               | 980h         | Core Registers               | A00h         | Core Registers               | A80h         | Core Registers               | B00h          | Core Registers               | B80h         | Core Registers               |

|               | (Table 3-2)                  |              | (Table 3-2)                  |              | (Table 3-2)                  |              | (Table 3-2)                  |              | (Table 3-2)                  |              | (Table 3-2)                  |               | (Table 3-2)                  |              | (Table 3-2)                  |

| 80Bh          |                              | 88Bh         |                              | 90Bh         |                              | 98Bh         |                              | A0Bh         |                              | A8Bh         |                              | B0Bh          |                              | B8Bh         |                              |

| 80Ch          |                              | 88Ch         |                              | 90Ch         |                              | 98Ch         |                              | A0Ch         |                              | A8Ch         |                              | B0Ch          |                              | B8Ch         |                              |

|               | Unimplemented<br>Read as '0' |              | Unimplemented<br>Read as '0' |              | Unimplemented<br>Read as '0' |              | Unimplemented<br>Read as '0' |              | Unimplemented<br>Read as '0' |              | Unimplemented<br>Read as '0' |               | Unimplemented<br>Read as '0' |              | Unimplemented<br>Read as '0' |

| 86Fh          |                              | 8EFh         |                              | 96Fh         |                              | 9EFh         |                              | A6Fh         |                              | AEFh         |                              | B6Fh          |                              | BEFh         |                              |

| 870h          |                              | 8F0h         |                              | 970h         |                              | 9F0h         |                              | A70h         |                              | AF0h         |                              | B70h          |                              | BF0h         |                              |

|               | Common RAM                   |              | Common RAM                   |              | Common RAM                   |              | Common RAM                   |              | Common RAM                   |              | Common RAM                   |               | Common RAM                   |              | Common RAM                   |

|               | (10000000                    |              | //                           |              | //                           |              |                              |              | //                           |              | //                           |               | //                           |              | //                           |

|               | (Accesses<br>70h – 7Fh)      |              | (Accesses<br>70h – 7Fh)      |              | (Accesses<br>70h – 7Fh)      |              | (Accesses<br>70h – 7Fh)      |              | (Accesses<br>70h – 7Fh)      |              | (Accesses<br>70h – 7Fh)      |               | (Accesses<br>70h – 7Fh)      |              | (Accesses<br>70h – 7Fh)      |

= Unimplemented data memory locations, read as '0'

**SPECIAL FUNCTION REGISTER SUMMARY (CONTINUED) TABLE 3-5:**

| Address            | Name                   | Bit 7        | Bit 6        | Bit 5         | Bit 4         | Bit 3          | Bit 2          | Bit 1   | Bit 0    | Value on POR, BOR | Value on all<br>other<br>Resets |

|--------------------|------------------------|--------------|--------------|---------------|---------------|----------------|----------------|---------|----------|-------------------|---------------------------------|

| Bank 2             | 2                      |              |              |               |               |                |                |         |          |                   |                                 |

| 10Ch               | LATA                   | _            | _            | LATA5         | LATA4         | _              | LATA2          | LATA1   | LATA0    | xx -xxx           | uu -uuu                         |

| 10Dh               | _                      | Unimplemen   | ted          |               |               |                |                |         |          | -                 | _                               |

| 10Eh               | LATC                   | _            | _            | LATC5         | LATC4         | LATC3          | LATC2          | LATC1   | LATC0    | xx xxxx           | uu uuuu                         |

| 10Fh               | _                      | Unimplemen   | ted          |               |               |                |                |         |          | _                 | _                               |

| 110h               | _                      | Unimplemen   | ted          |               |               |                |                |         |          | -                 | _                               |

| 111h               | CM1CON0                | C1ON         | C1OUT        | C10E          | C1POL         | _              | C1SP           | C1HYS   | C1SYNC   | 0000 -100         | 0000 -100                       |

| 112h<br>to<br>114h | _                      | Unimplemen   | ted          |               |               |                |                |         |          | _                 | _                               |

| 115h               | CMOUT                  | _            | _            | _             | _             | _              | _              | MC2OUT  | MC1OUT   | 00                | 00                              |

| 116h               | BORCON                 | SBOREN       | BORFS        | _             | _             | _              | _              | _       | BORRDY   | 10q               | uuu                             |

| 117h               | FVRCON                 | FVREN        | FVRRDY       | TSEN          | TSRNG         | CDAFV          | ′R<1:0>        | ADFV    | 'R<1:0>  | 0q00 0000         | 0q00 0000                       |

| 118h               | DAC1CON0               | DACEN        | _            | DACOE1        | DACOE2        | _              | DACPSS         | _       | I        | 0-00 -0           | 0-00 -0                         |

| 119h               | DAC1CON1               | _            | _            | _             |               |                | DACR<4:        | 0>      |          | 0 0000            | 0 0000                          |

| 11Ah<br>to<br>11Ch | _                      | Unimplemen   | ted          |               |               |                |                |         |          | _                 | _                               |

| 11Dh               | APFCON                 | _            | _            | SDOSEL        | SSSEL         | T1GSEL         | _              | CLC1SEL | NCO1SEL  | 00 0-00           | 00 0-00                         |

| 11Eh               | _                      | Unimplemen   | ted          |               |               |                |                |         |          | _                 | _                               |

| 11Fh               | _                      | Unimplemen   | ted          |               |               |                |                |         |          | _                 | _                               |

| Bank 3             | 3                      |              |              |               |               |                |                |         |          |                   |                                 |

| 18Ch               | ANSELA                 | _            | _            | _             | ANSA4         | _              | ANSA2          | ANSA1   | ANSA0    | 1 -111            | 1 -111                          |

| 18Dh               | _                      | Unimplemen   | ted          |               |               |                |                |         |          | _                 | _                               |

| 18Eh               | ANSELC                 | _            | _            | _             | _             | ANSC3          | ANSC2          | ANSC1   | ANSC0    | 1111              | 1111                            |

| 18Fh               | _                      | Unimplemen   | ted          |               |               |                |                |         |          | _                 | _                               |

| 190h               | _                      | Unimplemen   | ted          |               |               |                |                |         |          | _                 | _                               |

| 191h               | PMADRL                 | Flash Progra | m Memory A   | ddress Regis  | ter Low Byte  |                |                |         |          | 0000 0000         | 0000 0000                       |

| 192h               | PMADRH                 | (2)          | Flash Progra | am Memory A   | Address Regis | ster High Byte | е              |         |          | 1000 0000         | 1000 0000                       |

| 193h               | PMDATL                 | Flash Progra | m Memory R   | ead Data Re   | gister Low By | rte            |                |         |          | xxxx xxxx         | uuuu uuuu                       |

| 194h               | PMDATH                 | _            | _            | Flash Progr   | am Memory F   | Read Data Re   | egister High I | Byte    |          | xx xxxx           | uu uuuu                         |

| 195h               | PMCON1                 | (2)          | CFGS         | LWLO          | FREE          | WRERR          | WREN           | WR      | RD       | 1000 x000         | 1000 q000                       |

| 196h               | PMCON2                 | Flash Progra | m Memory C   | ontrol Regist | er 2          |                |                |         |          | 0000 0000         | 0000 0000                       |

| 197h               | VREGCON <sup>(1)</sup> | _            | _            | _             | _             | _              | _              | VREGPM  | Reserved | 01                | 01                              |

| 198h<br>to<br>19Fh | _                      | Unimplemen   | ted          |               |               |                |                |         |          | _                 | _                               |

x = unknown, u = unchanged, q = value depends on condition, - = unimplemented, r = reserved. Shaded locations are unimplemented, read as '0'. PIC16F1503 only. Unimplemented, read as '1'.

Legend: Note 1:

# 6.12 Determining the Cause of a Reset

Upon any Reset, multiple bits in the STATUS and PCON registers are updated to indicate the cause of the Reset. Table 6-3 and Table 6-4 show the Reset conditions of these registers.

TABLE 6-3: RESET STATUS BITS AND THEIR SIGNIFICANCE

| STKOVF | STKUNF | RWDT | RMCLR | RI | POR | BOR | то | PD | Condition                          |

|--------|--------|------|-------|----|-----|-----|----|----|------------------------------------|

| 0      | 0      | 1    | 1     | 1  | 0   | Х   | 1  | 1  | Power-on Reset                     |

| 0      | 0      | 1    | 1     | 1  | 0   | х   | 0  | х  | Illegal, TO is set on POR          |

| 0      | 0      | 1    | 1     | 1  | 0   | х   | х  | 0  | Illegal, PD is set on POR          |

| 0      | 0      | u    | 1     | 1  | u   | 0   | 1  | 1  | Brown-out Reset                    |

| u      | u      | 0    | u     | u  | u   | u   | 0  | u  | WDT Reset                          |

| u      | u      | u    | u     | u  | u   | u   | 0  | 0  | WDT Wake-up from Sleep             |

| u      | u      | u    | u     | u  | u   | u   | 1  | 0  | Interrupt Wake-up from Sleep       |

| u      | u      | u    | 0     | u  | u   | u   | u  | u  | MCLR Reset during normal operation |

| u      | u      | u    | 0     | u  | u   | u   | 1  | 0  | MCLR Reset during Sleep            |

| u      | u      | u    | u     | 0  | u   | u   | u  | u  | RESET Instruction Executed         |

| 1      | u      | u    | u     | u  | u   | u   | u  | u  | Stack Overflow Reset (STVREN = 1)  |

| u      | 1      | u    | u     | u  | u   | u   | u  | u  | Stack Underflow Reset (STVREN = 1) |

TABLE 6-4: RESET CONDITION FOR SPECIAL REGISTERS

| Condition                          | Program<br>Counter    | STATUS<br>Register | PCON<br>Register |

|------------------------------------|-----------------------|--------------------|------------------|

| Power-on Reset                     | 0000h                 | 1 1000             | 00 110x          |

| MCLR Reset during normal operation | 0000h                 | u muumuu           | uu 0uuu          |

| MCLR Reset during Sleep            | 0000h                 | 1 0uuu             | uu 0uuu          |

| WDT Reset                          | 0000h                 | 0 muumuu           | uu uuuu          |

| WDT Wake-up from Sleep             | PC + 1                | 0 0uuu             | uu uuuu          |

| Brown-out Reset                    | 0000h                 | 1 1uuu             | 00 11u0          |

| Interrupt Wake-up from Sleep       | PC + 1 <sup>(1)</sup> | 1 Ouuu             | uu uuuu          |

| RESET Instruction Executed         | 0000h                 | u uuuu             | uu u0uu          |

| Stack Overflow Reset (STVREN = 1)  | 0000h                 | u uuuu             | 1u uuuu          |

| Stack Underflow Reset (STVREN = 1) | 0000h                 | u uuuu             | u1 uuuu          |

**Legend:** u = unchanged, x = unknown, - = unimplemented bit, reads as '0'.

**Note 1:** When the wake-up is due to an interrupt and the Global Interrupt Enable bit (GIE) is set, the return address is pushed on the stack and PC is loaded with the interrupt vector (0004h) after execution of PC + 1.

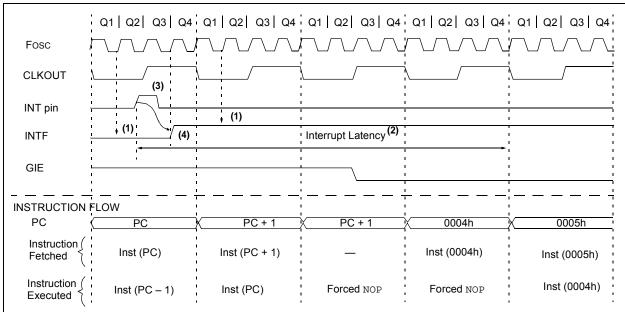

### FIGURE 7-3: INT PIN INTERRUPT TIMING

- Note 1: INTF flag is sampled here (every Q1).

- 2: Asynchronous interrupt latency = 3-5 Tcy. Synchronous latency = 3-4 Tcy, where Tcy = instruction cycle time. Latency is the same whether Inst (PC) is a single cycle or a 2-cycle instruction.

- 3: For minimum width of INT pulse, refer to AC specifications in Section 28.0 "Electrical Specifications".

- 4: INTF is enabled to be set any time during the Q4-Q1 cycles.

### REGISTER 7-5: PIR1: PERIPHERAL INTERRUPT REQUEST REGISTER 1

| R/W-0/0 | R/W-0/0 | U-0 | U-0 | R/W-0/0 | U-0 | R/W-0/0 | R/W-0/0 |

|---------|---------|-----|-----|---------|-----|---------|---------|

| TMR1GIF | ADIF    | _   | _   | SSP1IF  | _   | TMR2IF  | TMR1IF  |

| bit 7   |         |     |     |         |     |         | bit 0   |

Legend:

bit 5-4

R = Readable bit W = Writable bit U = Unimplemented bit, read as '0'

u = Bit is unchanged x = Bit is unknown -n/n = Value at POR and BOR/Value at all other Resets

'1' = Bit is set '0' = Bit is cleared

bit 7 TMR1GIF: Timer1 Gate Interrupt Flag bit

1 = Interrupt is pending

0 = Interrupt is not pending

bit 6 ADIF: ADC Interrupt Flag bit

1 = Interrupt is pending0 = Interrupt is not pending

Unimplemented: Read as '0'

bit 3 SSP1IF: Synchronous Serial Port (MSSP) Interrupt Flag bit

1 = Interrupt is pending0 = Interrupt is not pending

bit 2 Unimplemented: Read as '0'

bit 1 TMR2IF: Timer2 to PR2 Interrupt Flag bit

1 = Interrupt is pending0 = Interrupt is not pending

bit 0 TMR1IF: Timer1 Overflow Interrupt Flag bit

1 = Interrupt is pending0 = Interrupt is not pending

**Note:** Interrupt flag bits are set when an interrupt condition occurs, regardless of the state of its corresponding enable bit or the Global

Interrupt Enable bit, GIE of the INTCON register. User software should ensure the appropriate interrupt flag bits are clear prior

to enabling an interrupt.

#### 15.2.6 ADC CONVERSION PROCEDURE

This is an example procedure for using the ADC to perform an Analog-to-Digital conversion:

- 1. Configure Port:

- Disable pin output driver (Refer to the TRIS register)

- Configure pin as analog (Refer to the ANSEL register)

- Disable weak pull-ups either globally (Refer to the OPTION\_REG register) or individually (Refer to the appropriate WPUx register).

- 2. Configure the ADC module:

- · Select ADC conversion clock

- Configure voltage reference

- · Select ADC input channel

- · Turn on ADC module

- 3. Configure ADC interrupt (optional):

- · Clear ADC interrupt flag

- · Enable ADC interrupt

- · Enable peripheral interrupt

- Enable global interrupt<sup>(1)</sup>

- 4. Wait the required acquisition time(2).

- 5. Start conversion by setting the GO/DONE bit.

- Wait for ADC conversion to complete by one of the following:

- Polling the GO/DONE bit

- Waiting for the ADC interrupt (interrupts enabled)

- 7. Read ADC Result.

- 8. Clear the ADC interrupt flag (required if interrupt is enabled).

- **Note 1:** The global interrupt can be disabled if the user is attempting to wake-up from Sleep and resume in-line code execution.

- 2: Refer to Section 15.4 "ADC Acquisition Requirements".

### **EXAMPLE 15-1: ADC CONVERSION**

```

;This code block configures the ADC

; for polling, Vdd and Vss references, FRC

;oscillator and ANO input.

;Conversion start & polling for completion

; are included.

BANKSEL ADCON1

B'11110000' ; Right justify, FRC

MOVLW

;oscillator

ADCON1

MOVWF

;Vdd and Vss Vref+

BANKSEL

TRISA

BSF

TRISA,0

;Set RAO to input

BANKSEL ANSEL

ANSEL,0

;Set RAO to analog

BSF

BANKSEL

WPUA

WPUA,0

BCF

;Disable weak

pull-up on RA0

BANKSEL ADCON0

B'00000001' ;Select channel AN0

MOVLW

ADCONO ;Turn ADC On

SampleTime ;Acquisiton delay

MOVWF

CALL

ADCON0, ADGO ; Start conversion

BSF

BTFSC

ADCON0, ADGO ; Is conversion done?

GOTO

$-1

;No, test again

BANKSEL ADRESH

MOVF

ADRESH,W ;Read upper 2 bits

RESULTHI ;store in GPR space

MOVWF

ADRESL

BANKSEL

ADRESL,W

MOVF

;Read lower 8 bits

MOVWF

RESULTLO

;Store in GPR space

```

## 15.4 ADC Acquisition Requirements

For the ADC to meet its specified accuracy, the charge holding capacitor (CHOLD) must be allowed to fully charge to the input channel voltage level. The Analog Input model is shown in Figure 15-4. The source impedance (Rs) and the internal sampling switch (Rss) impedance directly affect the time required to charge the capacitor CHOLD. The sampling switch (Rss) impedance varies over the device voltage (VDD), refer to Figure 15-4. The maximum recommended impedance for analog sources is 10 kΩ. As the

source impedance is decreased, the acquisition time may be decreased. After the analog input channel is selected (or changed), an ADC acquisition must be done before the conversion can be started. To calculate the minimum acquisition time, Equation 15-1 may be used. This equation assumes that 1/2 LSb error is used (1,024 steps for the ADC). The 1/2 LSb error is the maximum error allowed for the ADC to meet its specified resolution.

### **EQUATION 15-1: ACQUISITION TIME EXAMPLE**

Assumptions: Temperature =  $50^{\circ}$ C and external impedance of  $10k\Omega 5.0V VDD$

$$TACQ = Amplifier Settling Time + Hold Capacitor Charging Time + Temperature Coefficient$$

=  $TAMP + TC + TCOFF$

=  $2\mu s + TC + [(Temperature - 25°C)(0.05\mu s/°C)]$

*The value for TC can be approximated with the following equations:*

$$V_{APPLIED}\left(1 - \frac{1}{(2^{n+1}) - 1}\right) = V_{CHOLD}$$

;[1] VCHOLD charged to within 1/2 lsb

$$V_{APPLIED} \left( 1 - e^{\frac{-Tc}{RC}} \right) = V_{CHOLD}$$

;[2] VCHOLD charge response to VAPPLIED

$$V_{APPLIED}\left(1-e^{\frac{-Tc}{RC}}\right) = V_{APPLIED}\left(1-\frac{1}{(2^{n+1})-1}\right)$$

; combining [1] and [2]

*Note:* Where n = number of bits of the ADC.

Solving for TC:

$$TC = -C_{HOLD}(RIC + RSS + RS) \ln(1/2047)$$

=  $-12.5pF(1k\Omega + 7k\Omega + 10k\Omega) \ln(0.0004885)$

=  $1.72\mu s$

*Therefore:*

$$TACQ = 2\mu s + 1.72\mu s + [(50^{\circ}C - 25^{\circ}C)(0.05\mu s/^{\circ}C)]$$

= 4.97\mu s

- Note 1: The reference voltage (VRPOS) has no effect on the equation, since it cancels itself out.

- 2: The charge holding capacitor (CHOLD) is not discharged after each conversion.

- 3: The maximum recommended impedance for analog sources is 10 k $\Omega$ . This is required to meet the pin leakage specification.

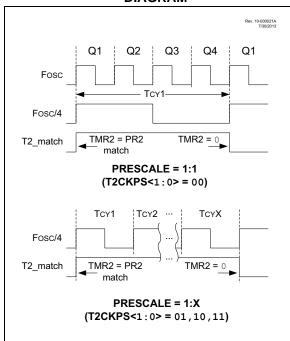

## 20.1 Timer2 Operation

The clock input to the Timer2 module is the system instruction clock (Fosc/4).

TMR2 increments from 00h on each clock edge.

A 4-bit counter/prescaler on the clock input allows direct input, divide-by-4 and divide-by-16 prescale options. These options are selected by the prescaler control bits, T2CKPS<1:0> of the T2CON register. The value of TMR2 is compared to that of the Period register, PR2, on each clock cycle. When the two values match, the comparator generates a match signal as the timer output. This signal also resets the value of TMR2 to 00h on the next cycle and drives the output counter/postscaler (see Section 20.2 "Timer2 Interrupt").

The TMR2 and PR2 registers are both directly readable and writable. The TMR2 register is cleared on any device Reset, whereas the PR2 register initializes to FFh. Both the prescaler and postscaler counters are cleared on the following events:

- · a write to the TMR2 register

- a write to the T2CON register

- Power-on Reset (POR)

- · Brown-out Reset (BOR)

- MCLR Reset

- · Watchdog Timer (WDT) Reset

- · Stack Overflow Reset

- · Stack Underflow Reset

- RESET Instruction

**Note:** TMR2 is not cleared when T2CON is written.

# 20.2 Timer2 Interrupt

Timer2 can also generate an optional device interrupt. The Timer2 output signal (T2\_match) provides the input for the 4-bit counter/postscaler. This counter generates the TMR2 match interrupt flag which is latched in TMR2IF of the PIR1 register. The interrupt is enabled by setting the TMR2 Match Interrupt Enable bit, TMR2IE of the PIE1 register.

A range of 16 postscale options (from 1:1 through 1:16 inclusive) can be selected with the postscaler control bits, T2OUTPS<3:0>, of the T2CON register.

### 20.3 Timer2 Output

The output of TMR2 is T2\_match. T2\_match is available to the following peripherals:

- · Configurable Logic Cell (CLC)

- Master Synchronous Serial Port (MSSP)

- · Numerically Controlled Oscillator (NCO)

- · Pulse Width Modulator (PWM)

The T2\_match signal is synchronous with the system clock. Figure 20-3 shows two examples of the timing of the T2\_match signal relative to Fosc and prescale value, T2CKPS<1:0>. The upper diagram illustrates 1:1 prescale timing and the lower diagram, 1:X prescale timing.

FIGURE 20-3: T2\_MATCH TIMING DIAGRAM

### 20.4 Timer2 Operation During Sleep

Timer2 cannot be operated while the processor is in Sleep mode. The contents of the TMR2 and PR2 registers will remain unchanged while the processor is in Sleep mode.

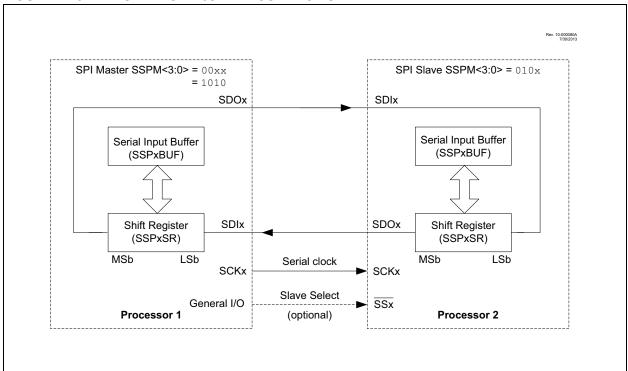

# FIGURE 21-5: SPI MASTER/SLAVE CONNECTION

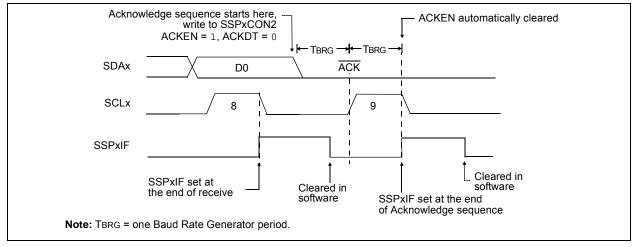

# 21.6.8 ACKNOWLEDGE SEQUENCE TIMING

An Acknowledge sequence is enabled by setting the Acknowledge Sequence Enable bit, ACKEN bit of the SSPxCON2 register. When this bit is set, the SCLx pin is pulled low and the contents of the Acknowledge data bit are presented on the SDAx pin. If the user wishes to generate an Acknowledge, then the ACKDT bit should be cleared. If not, the user should set the ACKDT bit before starting an Acknowledge sequence. The Baud Rate Generator then counts for one rollover period (TBRG) and the SCLx pin is deasserted (pulled high). When the SCLx pin is sampled high (clock arbitration), the Baud Rate Generator counts for TBRG. The SCLx pin is then pulled low. Following this, the ACKEN bit is automatically cleared, the Baud Rate Generator is turned off and the MSSP module then goes into Idle mode (Figure 21-30).

### 21.6.8.1 WCOL Status Flag

If the user writes the SSPxBUF when an Acknowledge sequence is in progress, then the WCOL bit is set and the contents of the buffer are unchanged (the write does not occur).

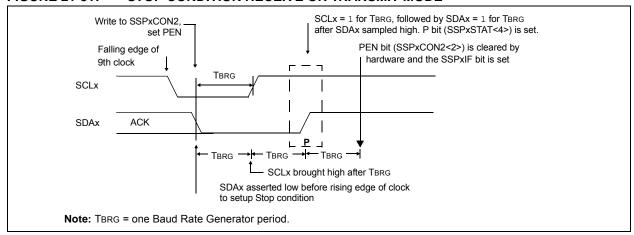

#### 21.6.9 STOP CONDITION TIMING

A Stop bit is asserted on the SDAx pin at the end of a receive/transmit by setting the Stop Sequence Enable bit, PEN bit of the SSPxCON2 register. At the end of a receive/transmit, the SCLx line is held low after the falling edge of the ninth clock. When the PEN bit is set, the master will assert the SDAx line low. When the SDAx line is sampled low, the Baud Rate Generator is reloaded and counts down to '0'. When the Baud Rate Generator times out, the SCLx pin will be brought high and one TBRG (Baud Rate Generator rollover count) later, the SDAx pin will be deasserted. When the SDAx pin is sampled high while SCLx is high, the P bit of the SSPxSTAT register is set. A TBRG later, the PEN bit is cleared and the SSPxIF bit is set (Figure 21-31).

### 21.6.9.1 WCOL Status Flag

If the user writes the SSPxBUF when a Stop sequence is in progress, then the WCOL bit is set and the contents of the buffer are unchanged (the write does not occur).

### FIGURE 21-31: STOP CONDITION RECEIVE OR TRANSMIT MODE

#### 21.6.10 SLEEP OPERATION

While in Sleep mode, the I<sup>2</sup>C slave module can receive addresses or data and when an address match or complete byte transfer occurs, wake the processor from Sleep (if the MSSP interrupt is enabled).

#### 21.6.11 EFFECTS OF A RESET

A Reset disables the MSSP module and terminates the current transfer.

#### 21.6.12 MULTI-MASTER MODE

In Multi-Master mode, the interrupt generation on the detection of the Start and Stop conditions allows the determination of when the bus is free. The Stop (P) and Start (S) bits are cleared from a Reset or when the MSSP module is disabled. Control of the I<sup>2</sup>C bus may be taken when the P bit of the SSPxSTAT register is set, or the bus is idle, with both the S and P bits clear. When the bus is busy, enabling the SSP interrupt will generate the interrupt when the Stop condition occurs.

In Multi-Master mode, the SDAx line must be monitored for arbitration to see if the signal level is the expected output level. This check is performed by hardware with the result placed in the BCLxIF bit.

The states where arbitration can be lost are:

- · Address Transfer

- Data Transfer

- · A Start Condition

- · A Repeated Start Condition

- · An Acknowledge Condition

## 21.6.13 MULTI -MASTER COMMUNICATION, BUS COLLISION AND BUS ARBITRATION

Multi-Master mode support is achieved by bus arbitration. When the master outputs address/data bits onto the SDAx pin, arbitration takes place when the master outputs a '1' on SDAx, by letting SDAx float high and another master asserts a '0'. When the SCLx pin floats high, data should be stable. If the expected data on SDAx is a '1' and the data sampled on the SDAx pin is '0', then a bus collision has taken place. The master will set the Bus Collision Interrupt Flag, BCLxIF and reset the I<sup>2</sup>C port to its Idle state (Figure 21-32).

If a transmit was in progress when the bus collision occurred, the transmission is halted, the BF flag is cleared, the SDAx and SCLx lines are deasserted and the SSPxBUF can be written to. When the user services the bus collision Interrupt Service Routine and if the  $\rm I^2C$  bus is free, the user can resume communication by asserting a Start condition.

If a Start, Repeated Start, Stop or Acknowledge condition was in progress when the bus collision occurred, the condition is aborted, the SDAx and SCLx lines are deasserted and the respective control bits in the SSPxCON2 register are cleared. When the user services the bus collision Interrupt Service Routine and if the I<sup>2</sup>C bus is free, the user can resume communication by asserting a Start condition.

The master will continue to monitor the SDAx and SCLx pins. If a Stop condition occurs, the SSPxIF bit will be set.

A write to the SSPxBUF will start the transmission of data at the first data bit, regardless of where the transmitter left off when the bus collision occurred.

In Multi-Master mode, the interrupt generation on the detection of Start and Stop conditions allows the determination of when the bus is free. Control of the  $I^2C$  bus can be taken when the P bit is set in the SSPxSTAT register, or the bus is idle and the S and P bits are cleared.

# 22.1.9 SETUP FOR PWM OPERATION USING PWMx PINS

The following steps should be taken when configuring the module for PWM operation using the PWMx pins:

- Disable the PWMx pin output driver(s) by setting the associated TRIS bit(s).

- 2. Clear the PWMxCON register.

- Load the PR2 register with the PWM period value.

- Clear the PWMxDCH register and bits <7:6> of the PWMxDCL register.

- 5. Configure and start Timer2:

- Clear the TMR2IF interrupt flag bit of the PIR1 register. See note below.

- Configure the T2CKPS bits of the T2CON register with the Timer2 prescale value.

- Enable Timer2 by setting the TMR2ON bit of the T2CON register.

- Enable PWM output pin and wait until Timer2 overflows, TMR2IF bit of the PIR1 register is set. See note below.

- 7. Enable the PWMx pin output driver(s) by clearing the associated TRIS bit(s) and setting the PWMxOE bit of the PWMxCON register.

- 8. Configure the PWM module by loading the PWMxCON register with the appropriate values.

- Note 1: In order to send a complete duty cycle and period on the first PWM output, the above steps must be followed in the order given. If it is not critical to start with a complete PWM signal, then move Step 8 to replace Step 4.

- **2:** For operation with other peripherals only, disable PWMx pin outputs.

### REGISTER 22-2: PWMxDCH: PWM DUTY CYCLE HIGH BITS

| R/W-x/u | R/W-x/u      | R/W-x/u | R/W-x/u | R/W-x/u | R/W-x/u | R/W-x/u | R/W-x/u |  |  |  |  |  |

|---------|--------------|---------|---------|---------|---------|---------|---------|--|--|--|--|--|

|         | PWMxDCH<7:0> |         |         |         |         |         |         |  |  |  |  |  |

| bit 7   |              |         |         |         |         |         | bit 0   |  |  |  |  |  |

Legend:

R = Readable bit W = Writable bit U = Unimplemented bit, read as '0'

u = Bit is unchanged x = Bit is unknown -n/n = Value at POR and BOR/Value at all other Resets

'1' = Bit is set '0' = Bit is cleared

bit 7-0 PWMxDCH<7:0>: PWM Duty Cycle Most Significant bits

These bits are the MSbs of the PWM duty cycle. The two LSbs are found in the PWMxDCL register.

### REGISTER 22-3: PWMxDCL: PWM DUTY CYCLE LOW BITS

| R/W-x/u      | R/W-x/u | U-0 | U-0 | U-0 | U-0 | U-0 | U-0   |

|--------------|---------|-----|-----|-----|-----|-----|-------|

| PWMxDCL<7:6> |         | _   | _   | _   | _   | _   | _     |

| bit 7        |         |     |     |     |     |     | bit 0 |

Legend:

R = Readable bit W = Writable bit U = Unimplemented bit, read as '0'

u = Bit is unchanged x = Bit is unknown -n/n = Value at POR and BOR/Value at all other Resets

'1' = Bit is set '0' = Bit is cleared

bit 7-6 PWMxDCL<7:6>: PWM Duty Cycle Least Significant bits

These bits are the LSbs of the PWM duty cycle. The MSbs are found in the PWMxDCH register.

bit 5-0 **Unimplemented:** Read as '0'

### TABLE 22-3: SUMMARY OF REGISTERS ASSOCIATED WITH PWM

| Name    | Bit 7  | Bit 6        | Bit 5   | Bit 4           | Bit 3           | Bit 2  | Bit 1  | Bit 0  | Register<br>on Page |

|---------|--------|--------------|---------|-----------------|-----------------|--------|--------|--------|---------------------|

| PR2     |        |              |         | Timer2 module f | Period Register |        |        |        | 151*                |

| PWM1CON | PWM1EN | PWM10E       | PWM1OUT | PWM1POL         | _               | _      | _      | _      | 212                 |

| PWM1DCH |        |              |         | PWM1D0          | CH<7:0>         |        |        |        | 213                 |

| PWM1DCL | PWM1D  | CL<7:6>      | _       | _               | _               | _      | _      | _      | 213                 |

| PWM2CON | PWM2EN | PWM2OE       | PWM2OUT | PWM2POL         | _               | _      | _      | _      | 212                 |

| PWM2DCH |        | PWM2DCH<7:0> |         |                 |                 |        |        |        | 213                 |

| PWM2DCL | PWM2D  | CL<7:6>      | _       | _               | _               | _      | _      | _      | 213                 |

| PWM3CON | PWM3EN | PWM3OE       | PWM3OUT | PWM3POL         | _               | _      | _      | _      | 212                 |

| PWM3DCH |        |              |         | PWM3D0          | CH<7:0>         |        |        |        | 213                 |

| PWM3DCL | PWM3D  | CL<7:6>      | _       | _               | _               | _      | _      | _      | 213                 |

| PWM4CON | PWM4EN | PWM4OE       | PWM4OUT | PWM4POL         | _               | _      | _      | _      | 212                 |

| PWM4DCH |        |              |         | PWM4D0          | CH<7:0>         |        |        |        | 213                 |

| PWM4DCL | PWM4D  | CL<7:6>      | _       | _               | _               | _      | _      | _      | 213                 |

| T2CON   | _      |              | T2OUT   | PS<3:0>         |                 | TMR2ON | T2CKP  | S<1:0> | 153                 |

| TMR2    |        |              |         | Timer2 modu     | ıle Register    |        |        |        | 151*                |

| TRISA   | _      | _            | TRISA5  | TRISA4          | —(1)            | TRISA2 | TRISA1 | TRISA0 | 98                  |

| TRISC   | _      | _            | TRISC5  | TRISC4          | TRISC3          | TRISC2 | TRISC1 | TRISC0 | 102                 |

Legend: - = Unimplemented locations, read as '0', u = unchanged, x = unknown. Shaded cells are not used by the PWM.

\* Page provides register information.

Note 1: Unimplemented, read as '1'.

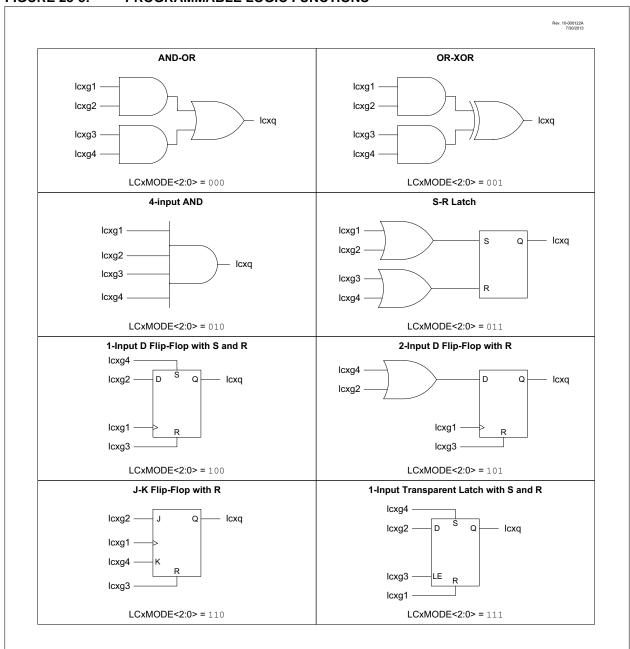

FIGURE 23-3: PROGRAMMABLE LOGIC FUNCTIONS

### REGISTER 23-9: CLCDATA: CLC DATA OUTPUT

| U-0   | U-0 | U-0 | U-0 | U-0 | U-0 | R-0     | R-0     |

|-------|-----|-----|-----|-----|-----|---------|---------|

| _     | _   | _   | _   |     |     | MLC2OUT | MLC1OUT |

| bit 7 |     |     |     |     |     |         | bit 0   |

Legend:

R = Readable bit W = Writable bit U = Unimplemented bit, read as '0'

u = Bit is unchanged x = Bit is unknown -n/n = Value at POR and BOR/Value at all other Resets

'1' = Bit is set '0' = Bit is cleared

bit 7-2 Unimplemented: Read as '0'

bit 1 MLC2OUT: Mirror copy of LC2OUT bit bit 0 MLC1OUT: Mirror copy of LC1OUT bit

TABLE 27-3: ENHANCED MID-RANGE INSTRUCTION SET

| Mnen   | nonic, | Description                                          | Cualas                                       |       | 14-Bit | Opcode | )    | Status   | Natas |

|--------|--------|------------------------------------------------------|----------------------------------------------|-------|--------|--------|------|----------|-------|

| Oper   | ands   | Description                                          | Cycles                                       | MSb   |        |        | LSb  | Affected | Notes |

|        |        | BYTE-ORIENTED FILE REGIS                             | TER OPE                                      | RATIO | NS     |        |      |          |       |

| ADDWF  | f, d   | Add W and f                                          | 1                                            | 00    | 0111   | dfff   | ffff | C, DC, Z | 2     |

| ADDWFC | f, d   | Add with Carry W and f                               | 1                                            | 11    | 1101   | dfff   | ffff | C, DC, Z | 2     |

| ANDWF  | f, d   | AND W with f                                         | 1                                            | 0.0   | 0101   | dfff   | ffff | Z        | 2     |

| ASRF   | f, d   | Arithmetic Right Shift                               | 1                                            | 11    | 0111   | dfff   | ffff | C, Z     | 2     |

| LSLF   | f, d   | Logical Left Shift                                   | 1                                            | 11    | 0101   | dfff   | ffff | C, Z     | 2     |

| LSRF   | f, d   | Logical Right Shift                                  | 1                                            | 11    | 0110   | dfff   | ffff | C, Z     | 2     |

| CLRF   | f      | Clear f                                              | 1                                            | 00    | 0001   | lfff   | ffff | Z        | 2     |

| CLRW   | _      | Clear W                                              | 1                                            | 0.0   | 0001   | 0000   | 00xx | Z        |       |

| COMF   | f, d   | Complement f                                         | 1                                            | 0.0   | 1001   | dfff   | ffff | Z        | 2     |

| DECF   | f, d   | Decrement f                                          | 1                                            | 00    | 0011   | dfff   | ffff | z        | 2     |

| INCF   | f, d   | Increment f                                          | 1                                            | 00    | 1010   | dfff   | ffff | z        | 2     |

| IORWF  | f. d   | Inclusive OR W with f                                | 1                                            | 00    | 0100   | dfff   | ffff | z        | 2     |

| MOVF   | f, d   | Move f                                               | 1                                            | 0.0   | 1000   |        | ffff | z        | 2     |

| MOVWF  | f      | Move W to f                                          | 1                                            | 0.0   | 0000   | 1fff   |      | -        | 2     |

| RLF    | f, d   | Rotate Left f through Carry                          | 1                                            | 00    | 1101   | dfff   |      | С        | 2     |

| RRF    | f, d   | Rotate Right f through Carry                         | 1                                            | 00    | 1100   | dfff   |      | C        | 2     |

| SUBWF  | f, d   | Subtract W from f                                    | 1                                            | 00    | 0010   |        | ffff | C, DC, Z | 2     |

| SUBWFB | f, d   | Subtract with Borrow W from f                        |                                              | 11    | 1011   |        | ffff | C, DC, Z | 2     |

| SWAPF  | f, d   | Swap nibbles in f                                    |                                              | 00    | 1110   | dfff   |      | 0, 00, 2 | 2     |

| XORWF  | f. d   | Exclusive OR W with f                                | 1                                            | 0.0   | 0110   |        | ffff | z        | 2     |

| XOKWI  | 1, u   | BYTE ORIENTED SKIP O                                 | <u>.                                    </u> |       | 0110   | ulli   | TILL |          | 2     |

|        | f, d   | Decrement f, Skip if 0                               | 1(2)                                         | 00    | 1011   | dfff   | ffff |          | 1, 2  |

| DECFSZ | f, d   | Increment f, Skip if 0                               | 1(2)                                         | 00    | 1111   | dfff   | ffff |          | 1, 2  |

| INCFSZ | ı, u   | · '                                                  |                                              |       |        | alli   | TILL |          | 1, 2  |

|        |        | BIT-ORIENTED FILE REGIST                             | ER OPER                                      | ATION | IS     |        |      |          | _     |

| BCF    | f, b   | Bit Clear f                                          | 1                                            | 01    | 00bb   | bfff   | ffff |          | 2     |

| BSF    | f, b   | Bit Set f                                            | 1                                            | 01    | 01bb   | bfff   | ffff |          | 2     |

|        |        | BIT-ORIENTED SKIP O                                  | PERATIO                                      | NS    | •      | ,      |      | •        |       |

| BTFSC  | f, b   | Bit Test f, Skip if Clear                            | 1 (2)                                        | 01    | 10bb   | bfff   | ffff |          | 1, 2  |

| BTFSS  | f, b   | Bit Test f, Skip if Set                              | 1 (2)                                        | 01    | 11bb   | bfff   | ffff |          | 1, 2  |

|        |        | LITERAL OPERA                                        | TIONS                                        | I     |        |        |      | I        | I     |

| ADDLW  | k      | Add literal and W                                    | 1                                            | 11    | 1110   | kkkk   | kkkk | C, DC, Z |       |

| ANDLW  | k      | AND literal with W                                   | 1                                            | 11    | 1001   | kkkk   | kkkk | Z        |       |

| IORLW  | k      | Inclusive OR literal with W                          | 1                                            | 11    | 1000   | kkkk   | kkkk | Z        |       |

| MOVLB  | k      | Move literal to BSR                                  | 1                                            | 00    | 0000   | 001k   | kkkk |          |       |

| MOVLP  | k      | Move literal to PCLATH                               | 1                                            | 11    | 0001   | 1kkk   | kkkk |          |       |

| MOVLW  | k      | Move literal to W                                    | 1                                            | 11    | 0000   | kkkk   |      |          |       |

| SUBLW  | k      | Subtract W from literal                              | 1                                            | 11    | 1100   | kkkk   |      | C, DC, Z |       |

| XORLW  | k      | Exclusive OR literal with W                          | 1                                            | 11    |        | kkkk   |      | Z Z      |       |

|        |        | m Counter (PC) is modified, or a conditional test in | -                                            |       |        |        |      | l .      |       |

Note 1: If the Program Counter (PC) is modified, or a conditional test is true, the instruction requires two cycles. The second cycle is executed as a NOP.

<sup>2:</sup> If this instruction addresses an INDF register and the MSb of the corresponding FSR is set, this instruction will require one additional instruction cycle.

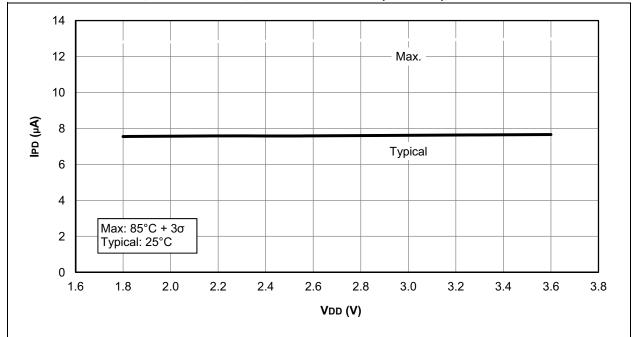

FIGURE 29-31: IPD, COMPARATOR, LOW-POWER MODE (CxSP = 0), PIC16LF1503 ONLY

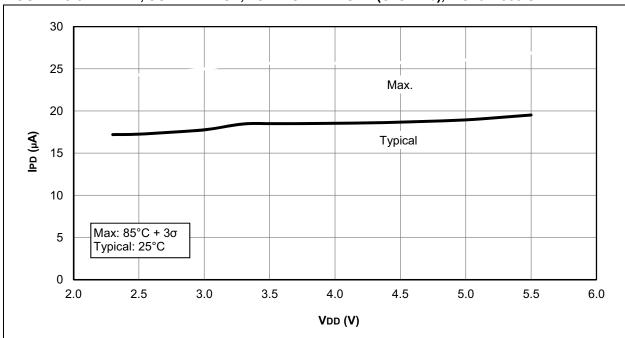

FIGURE 29-32: IPD, COMPARATOR, LOW-POWER MODE (CxSP = 0), PIC16F1503 ONLY

### 31.0 PACKAGING INFORMATION

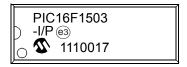

# 31.1 Package Marking Information

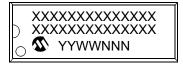

14-Lead PDIP

14-Lead SOIC (.150")

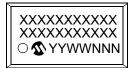

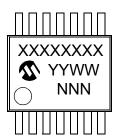

14-Lead TSSOP

Example

Example

Example

Legend: XX...X Customer-specific information

Y Year code (last digit of calendar year)

YY Year code (last 2 digits of calendar year)

WW Week code (week of January 1 is week '01')

NNN Alphanumeric traceability code

e3 Pb-free JEDEC<sup>®</sup> designator for Matte Tin (Sn)

This package is Pb-free. The Pb-free JEDEC designator (e3)

can be found on the outer packaging for this package.

**Note**: In the event the full Microchip part number cannot be marked on one line, it will be carried over to the next line, thus limiting the number of available characters for customer-specific information.

\* Standard PICmicro<sup>®</sup> device marking consists of Microchip part number, year code, week code and traceability code. For PICmicro device marking beyond this, certain price adders apply. Please check with your Microchip Sales Office. For QTP devices, any special marking adders are included in QTP price.

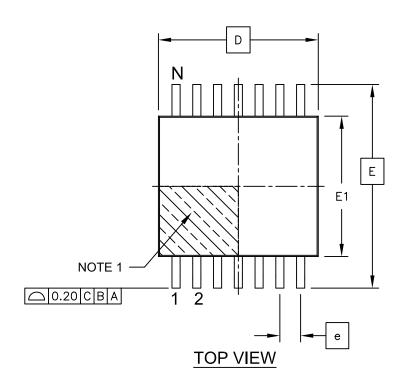

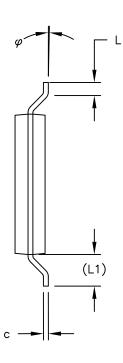

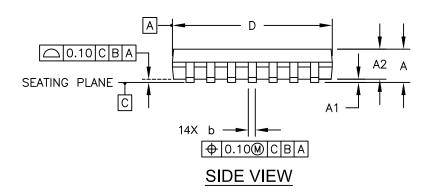

# 14-Lead Plastic Thin Shrink Small Outline (ST) - 4.4 mm Body [TSSOP]

**Note:** For the most current package drawings, please see the Microchip Packaging Specification located at http://www.microchip.com/packaging

Microchip Technology Drawing C04-087C Sheet 1 of 2