Welcome to **E-XFL.COM**

What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded - Microcontrollers</u>"

| _                          |                                                                           |

|----------------------------|---------------------------------------------------------------------------|

| Details                    |                                                                           |

| Product Status             | Active                                                                    |

| Core Processor             | PIC                                                                       |

| Core Size                  | 8-Bit                                                                     |

| Speed                      | 20MHz                                                                     |

| Connectivity               | I²C, SPI                                                                  |

| Peripherals                | Brown-out Detect/Reset, POR, PWM, WDT                                     |

| Number of I/O              | 11                                                                        |

| Program Memory Size        | 3.5KB (2K x 14)                                                           |

| Program Memory Type        | FLASH                                                                     |

| EEPROM Size                | -                                                                         |

| RAM Size                   | 128 x 8                                                                   |

| Voltage - Supply (Vcc/Vdd) | 1.8V ~ 3.6V                                                               |

| Data Converters            | A/D 8x10b                                                                 |

| Oscillator Type            | Internal                                                                  |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                         |

| Mounting Type              | Through Hole                                                              |

| Package / Case             | 14-DIP (0.300", 7.62mm)                                                   |

| Supplier Device Package    | 14-PDIP                                                                   |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic16lf1503-i-p |

### 3.3.1.1 STATUS Register

The STATUS register, shown in Register 3-1, contains:

- · the arithmetic status of the ALU

- · the Reset status

Legend:

R = Readable bit

'1' = Bit is set

u = Bit is unchanged

The STATUS register can be the destination for any instruction, like any other register. If the STATUS register is the destination for an instruction that affects the Z, DC or C bits, then the write to these three bits is disabled. These bits are set or cleared according to the device logic. Furthermore, the  $\overline{\text{TO}}$  and  $\overline{\text{PD}}$  bits are not writable. Therefore, the result of an instruction with the STATUS register as destination may be different than intended.

For example, CLRF STATUS will clear the upper three bits and set the Z bit. This leaves the STATUS register as '000u uluu' (where u = unchanged).

It is recommended, therefore, that only BCF, BSF, SWAPF and MOVWF instructions are used to alter the STATUS register, because these instructions do not affect any Status bits. For other instructions not affecting any Status bits (Refer to Section 27.0 "Instruction Set Summary").

Note 1: The <u>C and DC</u> bits operate as Borrow and <u>Digit Borrow</u> out bits, respectively, in subtraction.

REGISTER 3-1: STATUS: STATUS REGISTER

W = Writable bit

x = Bit is unknown '0' = Bit is cleared

| U-0         | U-0 | U-0 | R-1/q | R-1/q | R/W-0/u | R/W-0/u           | R/W-0/u          |

|-------------|-----|-----|-------|-------|---------|-------------------|------------------|

| <del></del> | _   | _   | TO    | PD    | Z       | DC <sup>(1)</sup> | C <sup>(1)</sup> |

| bit 7       |     |     |       |       |         |                   | bit 0            |

U = Unimplemented bit, read as '0'

q = Value depends on condition

-n/n = Value at POR and BOR/Value at all other Resets

| bit 7-5 | Unimplemented: Read as '0'                                                                                          |

|---------|---------------------------------------------------------------------------------------------------------------------|

| bit 4   | TO: Time-Out bit                                                                                                    |

|         | <ul><li>1 = After power-up, CLRWDT instruction or SLEEP instruction</li><li>0 = A WDT time-out occurred</li></ul>   |

| bit 3   | PD: Power-Down bit                                                                                                  |

|         | <ul><li>1 = After power-up or by the CLRWDT instruction</li><li>0 = By execution of the SLEEP instruction</li></ul> |

| bit 2   | Z: Zero bit                                                                                                         |

|         | 1 = The result of an arithmetic or logic operation is zero                                                          |

|         | 0 = The result of an arithmetic or logic operation is not zero                                                      |

| bit 1   | DC: Digit Carry/Digit Borrow bit (ADDWF, ADDLW, SUBLW, SUBWF instructions)(1)                                       |

|         | 1 = A carry-out from the 4th low-order bit of the result occurred                                                   |

|         | 0 = No carry-out from the 4th low-order bit of the result                                                           |

| bit 0   | C: Carry/Borrow bit(1) (ADDWF, ADDLW, SUBLW, SUBWF instructions)(1)                                                 |

1 = A carry-out from the Most Significant bit of the result occurred

0 = No carry-out from the Most Significant bit of the result occurred

Note 1: For Borrow, the polarity is reversed. A subtraction is executed by adding the two's complement of the second operand. For rotate (RRF, RLF) instructions, this bit is loaded with either the high-order or low-order bit of the source register.

## 5.2 Clock Source Types

Clock sources can be classified as external, internal or peripheral.

External clock sources rely on external circuitry for the clock source to function. Examples are: oscillator modules (ECH, ECM, ECL modes).

Internal clock sources are contained within the oscillator module. The internal oscillator block has two internal oscillators that are used to generate the internal system clock sources: the 16 MHz High-Frequency Internal Oscillator (HFINTOSC) and the 31 kHz Low-Frequency Internal Oscillator (LFINTOSC).

The peripheral clock source is a nominal 600 kHz internal RC oscillator, FRC. The FRC is traditionally used with the ADC module, but is sometimes available to other peripherals. See **Section 5.2.2.4** "**Peripheral Clock Sources**".

The system clock can be selected between external or internal clock sources via the System Clock Select (SCS) bits in the OSCCON register. See **Section 5.3 "Clock Switching"** for additional information.

#### 5.2.1 EXTERNAL CLOCK SOURCES

An external clock source can be used as the device system clock by performing one of the following actions:

- Program the FOSC<1:0> bits in the Configuration Words to select an external clock source that will be used as the default system clock upon a device Reset.

- Write the SCS<1:0> bits in the OSCCON register to switch the system clock source to:

- Secondary oscillator during run-time, or

- An external clock source determined by the value of the FOSC bits.

See Section 5.3 "Clock Switching" for more information.

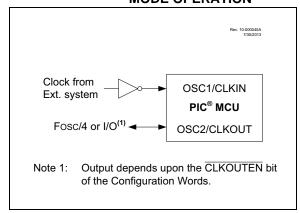

#### 5.2.1.1 EC Mode

The External Clock (EC) mode allows an externally generated logic level signal to be the system clock source. When operating in this mode, an external clock source is connected to the OSC1 input. OSC2/CLKOUT is available for general purpose I/O or CLKOUT. Figure 5-2 shows the pin connections for EC mode.

EC mode has three power modes to select from through the Fosc bits in the Configuration Words:

- ECH High power, 4-20 MHz

- ECM Medium power, 0.5-4 MHz

- ECL Low power, 0-0.5 MHz

# FIGURE 5-2: EXTERNAL CLOCK (EC) MODE OPERATION

## 6.12 Determining the Cause of a Reset

Upon any Reset, multiple bits in the STATUS and PCON registers are updated to indicate the cause of the Reset. Table 6-3 and Table 6-4 show the Reset conditions of these registers.

TABLE 6-3: RESET STATUS BITS AND THEIR SIGNIFICANCE

| STKOVF | STKUNF | RWDT | RMCLR | RI | POR | BOR | то | PD | Condition                          |

|--------|--------|------|-------|----|-----|-----|----|----|------------------------------------|

| 0      | 0      | 1    | 1     | 1  | 0   | Х   | 1  | 1  | Power-on Reset                     |

| 0      | 0      | 1    | 1     | 1  | 0   | х   | 0  | х  | Illegal, TO is set on POR          |

| 0      | 0      | 1    | 1     | 1  | 0   | х   | х  | 0  | Illegal, PD is set on POR          |

| 0      | 0      | u    | 1     | 1  | u   | 0   | 1  | 1  | Brown-out Reset                    |

| u      | u      | 0    | u     | u  | u   | u   | 0  | u  | WDT Reset                          |

| u      | u      | u    | u     | u  | u   | u   | 0  | 0  | WDT Wake-up from Sleep             |

| u      | u      | u    | u     | u  | u   | u   | 1  | 0  | Interrupt Wake-up from Sleep       |

| u      | u      | u    | 0     | u  | u   | u   | u  | u  | MCLR Reset during normal operation |

| u      | u      | u    | 0     | u  | u   | u   | 1  | 0  | MCLR Reset during Sleep            |

| u      | u      | u    | u     | 0  | u   | u   | u  | u  | RESET Instruction Executed         |

| 1      | u      | u    | u     | u  | u   | u   | u  | u  | Stack Overflow Reset (STVREN = 1)  |

| u      | 1      | u    | u     | u  | u   | u   | u  | u  | Stack Underflow Reset (STVREN = 1) |

TABLE 6-4: RESET CONDITION FOR SPECIAL REGISTERS

| Condition                          | Program<br>Counter    | STATUS<br>Register | PCON<br>Register |

|------------------------------------|-----------------------|--------------------|------------------|

| Power-on Reset                     | 0000h                 | 1 1000             | 00 110x          |

| MCLR Reset during normal operation | 0000h                 | u muumuu           | uu 0uuu          |

| MCLR Reset during Sleep            | 0000h                 | 1 0uuu             | uu 0uuu          |

| WDT Reset                          | 0000h                 | 0 muumuu           | uu uuuu          |

| WDT Wake-up from Sleep             | PC + 1                | 0 0uuu             | uu uuuu          |

| Brown-out Reset                    | 0000h                 | 1 1uuu             | 00 11u0          |

| Interrupt Wake-up from Sleep       | PC + 1 <sup>(1)</sup> | 1 Ouuu             | uu uuuu          |

| RESET Instruction Executed         | 0000h                 | u uuuu             | uu u0uu          |

| Stack Overflow Reset (STVREN = 1)  | 0000h                 | u uuuu             | 1u uuuu          |

| Stack Underflow Reset (STVREN = 1) | 0000h                 | u uuuu             | u1 uuuu          |

**Legend:** u = unchanged, x = unknown, - = unimplemented bit, reads as '0'.

**Note 1:** When the wake-up is due to an interrupt and the Global Interrupt Enable bit (GIE) is set, the return address is pushed on the stack and PC is loaded with the interrupt vector (0004h) after execution of PC + 1.

TABLE 6-5: SUMMARY OF REGISTERS ASSOCIATED WITH RESETS

| Name   | Bit 7  | Bit 6  | Bit 5 | Bit 4 | Bit 3 | Bit 2  | Bit 1 | Bit 0  | Register on Page |

|--------|--------|--------|-------|-------|-------|--------|-------|--------|------------------|

| BORCON | SBOREN | BORFS  |       | _     | _     | _      | _     | BORRDY | 53               |

| PCON   | STKOVF | STKUNF |       | RWDT  | RMCLR | RI     | POR   | BOR    | 57               |

| STATUS | _      | _      | _     | TO    | PD    | Z      | DC    | С      | 17               |

| WDTCON | _      | _      |       | V     |       | SWDTEN | 77    |        |                  |

**Legend:** — = unimplemented bit, reads as '0'. Shaded cells are not used by Resets.

## TABLE 6-6: SUMMARY OF CONFIGURATION WORD WITH RESETS

| Name    | Bits | Bit -/7 | Bit -/6 | Bit 13/5  | Bit 12/4 | Bit 11/3 | Bit 10/2     | Bit 9/1 | Bit 8/0 | Register on Page |

|---------|------|---------|---------|-----------|----------|----------|--------------|---------|---------|------------------|

| CONFICA | 13:8 | _       | _       | — — CLKOL |          | CLKOUTEN | BOREN<1:0> — |         |         | 20               |

| CONFIG1 | 7:0  | CP      | MCLRE   | PWRTE     | WD       | TE<1:0>  | _            | FOSC    | 38      |                  |

| CONFICA | 13:8 | _       | _       | LVP       | DEBUG    | LPBOR    | BORV         | STVREN  | _       | 20               |

| CONFIG2 | 7:0  | _       | _       | _         | _        | _        | _            | WRT-    | <1:0>   | 39               |

**Legend:** — = unimplemented location, read as '0'. Shaded cells are not used by Resets.

# 10.0 FLASH PROGRAM MEMORY CONTROL

The Flash program memory is readable and writable during normal operation over the full VDD range. Program memory is indirectly addressed using Special Function Registers (SFRs). The SFRs used to access program memory are:

- PMCON1

- PMCON2

- PMDATL

- PMDATH

- PMADRL

- PMADRH

When accessing the program memory, the PMDATH:PMDATL register pair forms a 2-byte word that holds the 14-bit data for read/write, and the PMADRH:PMADRL register pair forms a 2-byte word that holds the 15-bit address of the program memory location being read.

The write time is controlled by an on-chip timer. The write/erase voltages are generated by an on-chip charge pump rated to operate over the operating voltage range of the device.

The Flash program memory can be protected in two ways; by code protection (CP bit in Configuration Words) and write protection (WRT<1:0> bits in Configuration Words).

Code protection  $(\overline{CP} = 0)^{(1)}$ , disables access, reading and writing, to the Flash program memory via external device programmers. Code protection does not affect the self-write and erase functionality. Code protection can only be reset by a device programmer performing a Bulk Erase to the device, clearing all Flash program memory, Configuration bits and User IDs.

Write protection prohibits self-write and erase to a portion or all of the Flash program memory, as defined by the bits WRT<1:0>. Write protection does not affect a device programmers ability to read, write or erase the device.

**Note 1:** Code protection of the entire Flash program memory array is enabled by clearing the  $\overline{\mathsf{CP}}$  bit of Configuration Words.

## 10.1 PMADRL and PMADRH Registers

The PMADRH:PMADRL register pair can address up to a maximum of 32K words of program memory. When selecting a program address value, the MSB of the address is written to the PMADRH register and the LSB is written to the PMADRL register.

## 10.1.1 PMCON1 AND PMCON2 REGISTERS

PMCON1 is the control register for Flash program memory accesses.

Control bits RD and WR initiate read and write, respectively. These bits cannot be cleared, only set, in software. They are cleared by hardware at completion of the read or write operation. The inability to clear the WR bit in software prevents the accidental, premature termination of a write operation.

The WREN bit, when set, will allow a write operation to occur. On power-up, the WREN bit is clear. The WRERR bit is set when a write operation is interrupted by a Reset during normal operation. In these situations, following Reset, the user can check the WRERR bit and execute the appropriate error handling routine.

The PMCON2 register is a write-only register. Attempting to read the PMCON2 register will return all '0's.

To enable writes to the program memory, a specific pattern (the unlock sequence), must be written to the PMCON2 register. The required unlock sequence prevents inadvertent writes to the program memory write latches and Flash program memory.

## 10.2 Flash Program Memory Overview

It is important to understand the Flash program memory structure for erase and programming operations. Flash program memory is arranged in rows. A row consists of a fixed number of 14-bit program memory words. A row is the minimum size that can be erased by user software.

After a row has been erased, the user can reprogram all or a portion of this row. Data to be written into the program memory row is written to 14-bit wide data write latches. These write latches are not directly accessible to the user, but may be loaded via sequential writes to the PMDATH:PMDATL register pair.

Note: If the user wants to modify only a portion of a previously programmed row, then the contents of the entire row must be read and saved in RAM prior to the erase. Then, new data and retained data can be written into the write latches to reprogram the row of Flash program memory. However, any unprogrammed locations can be written without first erasing the row. In this case, it is not necessary to save and rewrite the other previously programmed locations.

See Table 10-1 for Erase Row size and the number of write latches for Flash program memory.

TABLE 10-1: FLASH MEMORY ORGANIZATION BY DEVICE

| Device        | Row Erase<br>(words) | Write<br>Latches<br>(words) |

|---------------|----------------------|-----------------------------|

| PIC16(L)F1503 | 16                   | 16                          |

## 12.6 Register Definitions: Interrupt-on-Change Control

#### REGISTER 12-1: IOCAP: INTERRUPT-ON-CHANGE PORTA POSITIVE EDGE REGISTER

| U-0   | U-0 | R/W-0/0 | R/W-0/0 | R/W-0/0 | R/W-0/0 | R/W-0/0 | R/W-0/0 |

|-------|-----|---------|---------|---------|---------|---------|---------|

| _     | _   | IOCAP5  | IOCAP4  | IOCAP3  | IOCAP2  | IOCAP1  | IOCAP0  |

| bit 7 |     |         |         |         |         |         | bit 0   |

Legend:

R = Readable bit W = Writable bit U = Unimplemented bit, read as '0'

u = Bit is unchanged x = Bit is unknown -n/n = Value at POR and BOR/Value at all other Resets

'1' = Bit is set '0' = Bit is cleared

bit 7-6 Unimplemented: Read as '0'

bit 5-0 **IOCAP<5:0>:** Interrupt-on-Change PORTA Positive Edge Enable bits

1 = Interrupt-on-Change enabled on the pin for a positive going edge. IOCAFx bit and IOCIF flag will be set upon detecting an edge.

0 = Interrupt-on-Change disabled for the associated pin.

#### REGISTER 12-2: IOCAN: INTERRUPT-ON-CHANGE PORTA NEGATIVE EDGE REGISTER

| U-0   | U-0 | R/W-0/0 | R/W-0/0 | R/W-0/0 | R/W-0/0 | R/W-0/0 | R/W-0/0 |

|-------|-----|---------|---------|---------|---------|---------|---------|

| _     | _   | IOCAN5  | IOCAN4  | IOCAN3  | IOCAN2  | IOCAN1  | IOCAN0  |

| bit 7 |     |         |         |         |         |         | bit 0   |

Legend:

R = Readable bit W = Writable bit U = Unimplemented bit, read as '0'

u = Bit is unknown -n/n = Value at POR and BOR/Value at all other Resets

'1' = Bit is set '0' = Bit is cleared

bit 7-6 Unimplemented: Read as '0'

bit 5-0 IOCAN<5:0>: Interrupt-on-Change PORTA Negative Edge Enable bits

1 = Interrupt-on-Change enabled on the pin for a negative going edge. IOCAFx bit and IOCIF flag will be set upon detecting an edge.

0 = Interrupt-on-Change disabled for the associated pin.

## REGISTER 12-3: IOCAF: INTERRUPT-ON-CHANGE PORTA FLAG REGISTER

| U-0   | U-0 | R/W/HS-0/0 | R/W/HS-0/0 | R/W/HS-0/0 | R/W/HS-0/0 | R/W/HS-0/0 | R/W/HS-0/0 |

|-------|-----|------------|------------|------------|------------|------------|------------|

| _     | _   | IOCAF5     | IOCAF4     | IOCAF3     | IOCAF2     | IOCAF1     | IOCAF0     |

| bit 7 |     |            |            |            |            |            | bit 0      |

Legend:

R = Readable bit W = Writable bit U = Unimplemented bit, read as '0'

u = Bit is unchanged x = Bit is unknown -n/n = Value at POR and BOR/Value at all other Resets

'1' = Bit is set '0' = Bit is cleared HS - Bit is set in hardware

bit 7-6 Unimplemented: Read as '0'

bit 5-0 **IOCAF<5:0>:** Interrupt-on-Change PORTA Flag bits

1 = An enabled change was detected on the associated pin.

Set when IOCAPx = 1 and a rising edge was detected on RAx, or when IOCANx = 1 and a falling edge was detected on RAx

0 = No change was detected, or the user cleared the detected change.

## 16.1 Output Voltage Selection

The DAC has 32 voltage level ranges. The 32 levels are set with the DACR<4:0> bits of the DACxCON1 register.

The DAC output voltage can be determined by using Equation 16-1.

## 16.2 Ratiometric Output Level

The DAC output value is derived using a resistor ladder with each end of the ladder tied to a positive and negative voltage reference input source. If the voltage of either input source fluctuates, a similar fluctuation will result in the DAC output value.

The value of the individual resistors within the ladder can be found in Table 28-14.

## 16.3 DAC Voltage Reference Output

The unbuffered DAC voltage can be output to the DACxOUTn pin(s) by setting the respective DACOEn bit(s) of the DACxCON0 register. Selecting the DAC reference voltage for output on either DACxOUTn pin automatically overrides the digital output buffer, the weak pull-up and digital input threshold detector functions of that pin.

Reading the DACxOUTn pin when it has been configured for DAC reference voltage output will always return a '0'.

**Note:** The unbuffered DAC output (DACxOUTn) is not intended to drive an external load.

## 16.4 Operation During Sleep

When the device wakes up from Sleep through an interrupt or a Watchdog Timer time-out, the contents of the DACxCON0 register are not affected. To minimize current consumption in Sleep mode, the voltage reference should be disabled.

### 16.5 Effects of a Reset

A device Reset affects the following:

- DACx is disabled.

- DACx output voltage is removed from the DACxOUTn pin(s).

- · The DACR<4:0> range select bits are cleared.

#### **EQUATION 16-1: DAC OUTPUT VOLTAGE**

#### IF DACEN = 1

$$DACx\_output = \left( (VSOURCE+ - VSOURCE-) \times \frac{DACR[4:0]}{2^5} \right) + VSOURCE-$$

**Note:** See the DACxCON0 register for the available Vsource+ and Vsource- selections.

#### 21.2.6 SPI OPERATION IN SLEEP MODE

In SPI Master mode, module clocks may be operating at a different speed than when in Full-Power mode; in the case of the Sleep mode, all clocks are halted.

Special care must be taken by the user when the MSSP clock is much faster than the system clock.

In Slave mode, when MSSP interrupts are enabled, after the master completes sending data, an MSSP interrupt will wake the controller from Sleep.

If an exit from Sleep mode is not desired, MSSP interrupts should be disabled.

In SPI Master mode, when the Sleep mode is selected, all module clocks are halted and the transmission/reception will remain in that state until the device wakes. After the device returns to Run mode, the module will resume transmitting and receiving data.

In SPI Slave mode, the SPI Transmit/Receive Shift register operates asynchronously to the device. This allows the device to be placed in Sleep mode and data to be shifted into the SPI Transmit/Receive Shift register. When all eight bits have been received, the MSSP interrupt flag bit will be set and if enabled, will wake the device.

TABLE 21-1: SUMMARY OF REGISTERS ASSOCIATED WITH SPI OPERATION

| Name     | Bit 7       | Bit 6           | Bit 5         | Bit 4         | Bit 3   | Bit 2  | Bit 1  | Bit 0  | Register on Page |

|----------|-------------|-----------------|---------------|---------------|---------|--------|--------|--------|------------------|

| ANSELA   | _           | 1               | 1             | ANSA4         | 1       | ANSA2  | ANSA1  | ANSA0  | 99               |

| INTCON   | GIE         | PEIE            | TMR0IE        | INTE          | IOCIE   | TMR0IF | INTF   | IOCIF  | 64               |

| PIE1     | TMR1GIE     | ADIE            | _             | _             | SSP1IE  | _      | TMR2IE | TMR1IE | 65               |

| PIR1     | TMR1GIF     | ADIF            | _             | _             | SSP1IF  | _      | TMR2IF | TMR1IF | 68               |

| SSP1BUF  | Synchronous | s Serial Port F | Receive Buffe | r/Transmit Re | egister |        |        |        | 158*             |

| SSP1CON1 | WCOL        | SSPOV           | SSPEN         | CKP           |         | SSPM   | <3:0>  |        | 204              |

| SSP1CON3 | ACKTIM      | PCIE            | SCIE          | BOEN          | SDAHT   | SBCDE  | AHEN   | DHEN   | 206              |

| SSP1STAT | SMP         | CKE             | D/A           | Р             | S       | R/W    | UA     | BF     | 203              |

| TRISA    | _           | _               | TRISA5        | TRISA4        | (1)     | TRISA2 | TRISA1 | TRISA0 | 98               |

| TRISC    | _           | _               | TRISC5        | TRISC4        | TRISC3  | TRISC2 | TRISC1 | TRISC0 | 102              |

**Legend:** — = Unimplemented location, read as '0'. Shaded cells are not used by the MSSP in SPI mode.

\* Page provides register information.

Note 1: Unimplemented, read as '1'.

#### 22.1.5 PWM RESOLUTION

The resolution determines the number of available duty cycles for a given period. For example, a 10-bit resolution will result in 1024 discrete duty cycles, whereas an 8-bit resolution will result in 256 discrete duty cycles.

The maximum PWM resolution is ten bits when PR2 is 255. The resolution is a function of the PR2 register value as shown by Equation 22-4.

#### **EQUATION 22-4: PWM RESOLUTION**

Resolution =

$$\frac{log[4(PR2 + 1)]}{log(2)}$$

bits

**Note:** If the pulse width value is greater than the period the assigned PWM pin(s) will

remain unchanged.

## TABLE 22-1: EXAMPLE PWM FREQUENCIES AND RESOLUTIONS (Fosc = 20 MHz)

| PWM Frequency             | 0.31 kHz | 4.88 kHz | 19.53 kHz | 78.12 kHz | 156.3 kHz | 208.3 kHz |

|---------------------------|----------|----------|-----------|-----------|-----------|-----------|

| Timer Prescale            | 64       | 4        | 1         | 1         | 1         | 1         |

| PR2 Value                 | 0xFF     | 0xFF     | 0xFF      | 0x3F      | 0x1F      | 0x17      |

| Maximum Resolution (bits) | 10       | 10       | 10        | 8         | 7         | 6.6       |

#### TABLE 22-2: EXAMPLE PWM FREQUENCIES AND RESOLUTIONS (Fosc = 8 MHz)

| PWM Frequency             | 0.31 kHz | 4.90 kHz | 19.61 kHz | 76.92 kHz | 153.85 kHz | 200.0 kHz |

|---------------------------|----------|----------|-----------|-----------|------------|-----------|

| Timer Prescale            | 64       | 4        | 1         | 1         | 1          | 1         |

| PR2 Value                 | 0x65     | 0x65     | 0x65      | 0x19      | 0x0C       | 0x09      |

| Maximum Resolution (bits) | 8        | 8        | 8         | 6         | 5          | 5         |

#### 22.1.6 OPERATION IN SLEEP MODE

In Sleep mode, the TMR2 register will not increment and the state of the module will not change. If the PWMx pin is driving a value, it will continue to drive that value. When the device wakes up, TMR2 will continue from its previous state.

# 22.1.7 CHANGES IN SYSTEM CLOCK FREQUENCY

The PWM frequency is derived from the system clock frequency (Fosc). Any changes in the system clock frequency will result in changes to the PWM frequency. Refer to **Section 5.0 "Oscillator Module"** for additional details.

#### 22.1.8 EFFECTS OF RESET

Any Reset will force all ports to Input mode and the PWM registers to their Reset states.

#### REGISTER 23-3: CLCxSeL0: MULTIPLEXER DATA 1 AND 2 SELECT REGISTER

| U-0   | R/W-x/u                    | R/W-x/u | R/W-x/u | U-0                        | R/W-x/u | R/W-x/u | R/W-x/u |

|-------|----------------------------|---------|---------|----------------------------|---------|---------|---------|

| _     | LCxD2S<2:0> <sup>(1)</sup> |         | _       | LCxD1S<2:0> <sup>(1)</sup> |         |         |         |

| bit 7 |                            |         |         |                            |         |         | bit 0   |

Legend:

R = Readable bit W = Writable bit U = Unimplemented bit, read as '0'

u = Bit is unchanged x = Bit is unknown -n/n = Value at POR and BOR/Value at all other Resets

'1' = Bit is set '0' = Bit is cleared

bit 7 Unimplemented: Read as '0'

bit 6-4 LCxD2S<2:0>: Input Data 2 Selection Control bits<sup>(1)</sup>

111 = LCx in[11] is selected for lcxd2

110 = LCx\_in[10] is selected for lcxd2

101 = LCx in[9] is selected for lcxd2

100 = LCx\_in[8] is selected for lcxd2

011 = LCx\_in[7] is selected for lcxd2

010 = LCx in[6] is selected for lcxd2

001 = LCx in[5] is selected for lcxd2

000 = LCx in[4] is selected for lcxd2

bit 3 Unimplemented: Read as '0'

bit 2-0 LCxD1S<2:0>: Input Data 1 Selection Control bits<sup>(1)</sup>

111 = LCx\_in[7] is selected for lcxd1

110 = LCx\_in[6] is selected for lcxd1

101 = LCx\_in[5] is selected for lcxd1

100 = LCx\_in[4] is selected for lcxd1

011 = LCx in[3] is selected for lcxd1

$010 = LCx_in[2]$  is selected for lcxd1

001 = LCx\_in[1] is selected for lcxd1

000 = LCx\_in[0] is selected for lcxd1

Note 1: See Table 23-1 for signal names associated with inputs.

DS40001607D-page 240

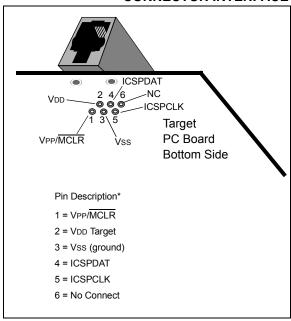

# 26.0 IN-CIRCUIT SERIAL PROGRAMMING™ (ICSP™)

ICSP<sup>TM</sup> programming allows customers to manufacture circuit boards with unprogrammed devices. Programming can be done after the assembly process allowing the device to be programmed with the most recent firmware or a custom firmware. Five pins are needed for ICSP<sup>TM</sup> programming:

- ICSPCLK

- ICSPDAT

- MCLR/VPP

- VDD

- Vss

In Program/Verify mode the program memory, user IDs and the Configuration Words are programmed through serial communications. The ICSPDAT pin is a bidirectional I/O used for transferring the serial data and the ICSPCLK pin is the clock input. For more information on ICSP $^{\text{TM}}$  refer to the "PIC12(L)F1501/PIC16(L)F150X Memory Programming Specification" (DS41573).

## 26.1 High-Voltage Programming Entry Mode

The device is placed into High-Voltage Programming Entry mode by holding the ICSPCLK and ICSPDAT pins low then raising the voltage on MCLR/VPP to VIHH.

## 26.2 Low-Voltage Programming Entry Mode

The Low-Voltage Programming Entry mode allows the PIC® Flash MCUs to be programmed using VDD only, without high voltage. When the LVP bit of Configuration Words is set to '1', the ICSP Low-Voltage Programming Entry mode is enabled. To disable the Low-Voltage ICSP mode, the LVP bit must be programmed to '0'.

Entry into the Low-Voltage Programming Entry mode requires the following steps:

- 1. MCLR is brought to VIL.

- A 32-bit key sequence is presented on ICSPDAT, while clocking ICSPCLK.

Once the key sequence is complete,  $\overline{\text{MCLR}}$  must be held at VIL for as long as Program/Verify mode is to be maintained.

If low-voltage programming is enabled (LVP = 1), the  $\overline{\text{MCLR}}$  Reset function is automatically enabled and cannot be disabled. See **Section 6.5 "MCLR"** for more information.

The LVP bit can only be reprogrammed to '0' by using the High-Voltage Programming mode.

## 26.3 Common Programming Interfaces

Connection to a target device is typically done through an ICSP™ header. A commonly found connector on development tools is the RJ-11 in the 6P6C (6-pin, 6-connector) configuration. See Figure 26-1.

FIGURE 26-1: ICD RJ-11 STYLE CONNECTOR INTERFACE

Another connector often found in use with the PICkit™ programmers is a standard 6-pin header with 0.1 inch spacing. Refer to Figure 26-2.

## RRF Rotate Right f through Carry

Syntax: [label] RRF f,d

Operands:  $0 \le f \le 127 \\ d \in [0,1]$

Operation: See description below

Status Affected: C

Description: The contents of register 'f' are rotated one bit to the right through the Carry

flag. If 'd' is '0', the result is placed in the W register. If 'd' is '1', the result is placed back in register 'f'.

### SUBLW Subtract W from literal

Syntax: [ label ] SUBLW k

Operands:  $0 \le k \le 255$ Operation:  $k - (W) \rightarrow (W)$ Status Affected: C, DC, Z

Description: The W register is subtracted (2's complement method) from the 8-bit literal

'k'. The result is placed in the W regis-

ter.

| C = 0  | W > k           |

|--------|-----------------|

| C = 1  | $W \leq k$      |

| DC = 0 | W<3:0> > k<3:0> |

| DC = 1 | W<3:0> ≤ k<3:0> |

#### SLEEP Enter Sleep mode

Syntax: [ label ] SLEEP

Operands: None

Operation:  $00h \rightarrow WDT$ ,

$0 \rightarrow WDT$  prescaler,

$1 \to \overline{\overline{10}}, \\ 0 \to \overline{PD}$

Status Affected: TO, PD

Description: The power-down Status bit,  $\overline{PD}$  is

cleared. Time-out Status bit,  $\overline{\text{TO}}$  is set. Watchdog Timer and its pres-

caler are cleared.

The processor is put into Sleep mode

with the oscillator stopped.

### SUBWF Subtract W from f

Syntax: [ label ] SUBWF f,d

$\begin{array}{ll} \text{Operands:} & 0 \leq f \leq 127 \\ & d \in [0,1] \end{array}$

Operation: (f) - (W)  $\rightarrow$  (destination)

Status Affected: C, DC, Z

Description: Subtract (2's complement method) W

register from register 'f'. If 'd' is '0', the

result is stored in the W

register. If 'd' is '1', the result is stored

back in register 'f.

| <b>C</b> = 0 | W > f           |

|--------------|-----------------|

| C = 1        | $W \leq f \\$   |

| DC = 0       | W<3:0> > f<3:0> |

| DC = 1       | W<3:0> ≤ f<3:0> |

### SUBWFB Subtract W from f with Borrow

Syntax: SUBWFB f {,d}

Operands:  $0 \le f \le 127$  $d \in [0,1]$

Operation:  $(f) - (W) - (\overline{B}) \rightarrow dest$

Status Affected: C, DC, Z

Description: Subtract W and the BORROW flag

(CARRY) from register 'f' (2's complement method). If 'd' is '0', the result is stored in W. If 'd' is '1', the result is

stored back in register 'f'.

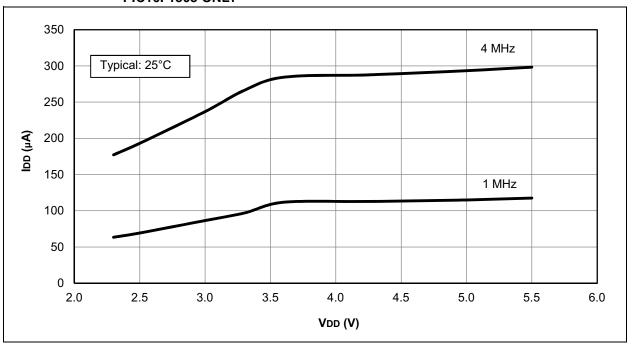

FIGURE 29-7: IDD TYPICAL, EXTERNAL CLOCK (ECM), MEDIUM POWER MODE, PIC16F1503 ONLY

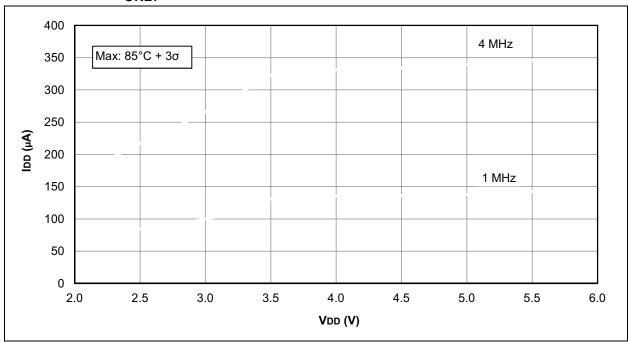

FIGURE 29-8: IDD MAXIMUM, EXTERNAL CLOCK (ECM), MEDIUM POWER MODE, PIC16F1503 ONLY

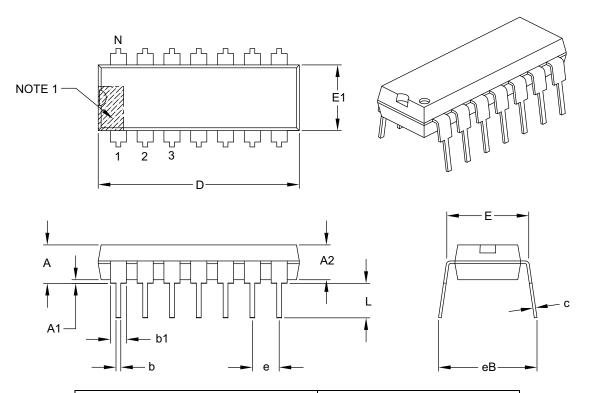

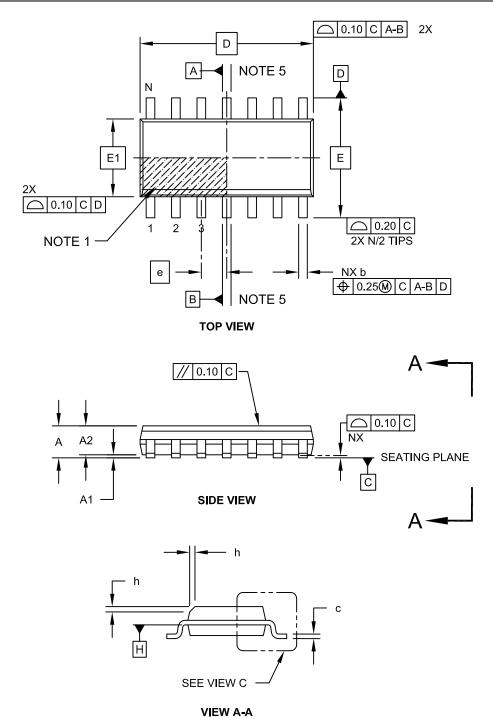

## 31.2 Package Details

The following sections give the technical details of the packages.

## 14-Lead Plastic Dual In-Line (P) – 300 mil Body [PDIP]

**Note:** For the most current package drawings, please see the Microchip Packaging Specification located at http://www.microchip.com/packaging

|                            | Units         |          | INCHES |      |  |

|----------------------------|---------------|----------|--------|------|--|

| Dim                        | ension Limits | MIN      | NOM    | MAX  |  |

| Number of Pins             | 14            |          |        |      |  |

| Pitch                      | е             | .100 BSC |        |      |  |

| Top to Seating Plane       | А             | -        | _      | .210 |  |

| Molded Package Thickness   | A2            | .115     | .130   | .195 |  |

| Base to Seating Plane      | A1            | .015     | _      | _    |  |

| Shoulder to Shoulder Width | E             | .290     | .310   | .325 |  |

| Molded Package Width       | E1            | .240     | .250   | .280 |  |

| Overall Length             | D             | .735     | .750   | .775 |  |

| Tip to Seating Plane       | L             | .115     | .130   | .150 |  |

| Lead Thickness             | С             | .008     | .010   | .015 |  |

| Upper Lead Width           | b1            | .045     | .060   | .070 |  |

| Lower Lead Width           | b             | .014     | .018   | .022 |  |

| Overall Row Spacing §      | eB            | _        | -      | .430 |  |

#### Notes.

- 1. Pin 1 visual index feature may vary, but must be located with the hatched area.

- 2. § Significant Characteristic.

- 3. Dimensions D and E1 do not include mold flash or protrusions. Mold flash or protrusions shall not exceed .010" per side.

- 4. Dimensioning and tolerancing per ASME Y14.5M.

BSC: Basic Dimension. Theoretically exact value shown without tolerances.

Microchip Technology Drawing C04-005B

## 14-Lead Plastic Small Outline (SL) - Narrow, 3.90 mm Body [SOIC]

**Note:** For the most current package drawings, please see the Microchip Packaging Specification located at http://www.microchip.com/packaging

Microchip Technology Drawing No. C04-065C Sheet 1 of 2

#### THE MICROCHIP WEBSITE

Microchip provides online support via our website at www.microchip.com. This website is used as a means to make files and information easily available to customers. Accessible by using your favorite Internet browser, the website contains the following information:

- Product Support Data sheets and errata, application notes and sample programs, design resources, user's guides and hardware support documents, latest software releases and archived software

- General Technical Support Frequently Asked Questions (FAQ), technical support requests, online discussion groups, Microchip consultant program member listing

- Business of Microchip Product selector and ordering guides, latest Microchip press releases, listing of seminars and events, listings of Microchip sales offices, distributors and factory representatives

# CUSTOMER CHANGE NOTIFICATION SERVICE

Microchip's customer notification service helps keep customers current on Microchip products. Subscribers will receive e-mail notification whenever there are changes, updates, revisions or errata related to a specified product family or development tool of interest.

To register, access the Microchip website at www.microchip.com. Under "Support", click on "Customer Change Notification" and follow the registration instructions.

#### **CUSTOMER SUPPORT**

Users of Microchip products can receive assistance through several channels:

- · Distributor or Representative

- · Local Sales Office

- · Field Application Engineer (FAE)

- · Technical Support

Customers should contact their distributor, representative or Field Application Engineer (FAE) for support. Local sales offices are also available to help customers. A listing of sales offices and locations is included in the back of this document.

Technical support is available through the website at: http://www.microchip.com/support