Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

#### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

E·XF

| Details                    |                                                                            |

|----------------------------|----------------------------------------------------------------------------|

| Product Status             | Active                                                                     |

| Core Processor             | PIC                                                                        |

| Core Size                  | 8-Bit                                                                      |

| Speed                      | 20MHz                                                                      |

| Connectivity               | I <sup>2</sup> C, SPI                                                      |

| Peripherals                | Brown-out Detect/Reset, POR, PWM, WDT                                      |

| Number of I/O              | 11                                                                         |

| Program Memory Size        | 3.5KB (2K x 14)                                                            |

| Program Memory Type        | FLASH                                                                      |

| EEPROM Size                | -                                                                          |

| RAM Size                   | 128 x 8                                                                    |

| Voltage - Supply (Vcc/Vdd) | 1.8V ~ 3.6V                                                                |

| Data Converters            | A/D 8x10b                                                                  |

| Oscillator Type            | Internal                                                                   |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                          |

| Mounting Type              | Surface Mount                                                              |

| Package / Case             | 14-TSSOP (0.173", 4.40mm Width)                                            |

| Supplier Device Package    | 14-TSSOP                                                                   |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic16lf1503-i-st |

|                            |                                                                            |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

### **Peripheral Features (Continued):**

- Two Configurable Logic Cell (CLC) modules:

- 16 selectable input source signals

- Four inputs per module

- Software control of combinational/sequential logic/state/clock functions

PIC12(L)F1501/PIC16(L)F150X FAMILY TYPES

- AND/OR/XOR/D Flop/D Latch/SR/JK

- Inputs from external and internal sources

- Output available to pins and peripherals

- Operation while in Sleep

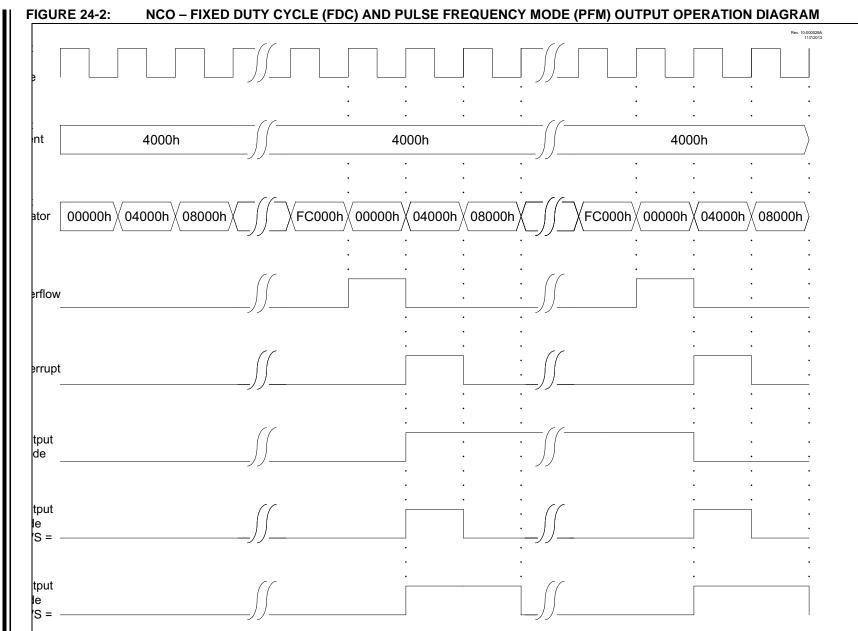

- Numerically Controlled Oscillator (NCO):

- 20-bit accumulator

- 16-bit increment

- True linear frequency control

- High-speed clock input

- Selectable Output modes

- Fixed Duty Cycle (FDC) mode

- Pulse Frequency (PF) mode

- Complementary Waveform Generator (CWG):

- Eight selectable signal sources

- Selectable falling and rising edge dead-band control

- Polarity control

- Four auto-shutdown sources

- Multiple input sources: PWM, CLC, NCO

| Device        | Data Sheet Index | Program Memory<br>Flash (words) | Data SRAM<br>(bytes) | I/O's <sup>(2)</sup> | 10-bit ADC (ch) | Comparators | DAC | Timers<br>(8/16-bit) | MWd | EUSART | MSSP (I <sup>2</sup> C/SPI) | CWG | CLC | NCO | Debug <sup>(1)</sup> | XLP |

|---------------|------------------|---------------------------------|----------------------|----------------------|-----------------|-------------|-----|----------------------|-----|--------|-----------------------------|-----|-----|-----|----------------------|-----|

| PIC12(L)F1501 | (1)              | 1024                            | 64                   | 6                    | 4               | 1           | 1   | 2/1                  | 4   | —      | -                           | 1   | 2   | 1   | Н                    |     |

| PIC16(L)F1503 | (2)              | 2048                            | 128                  | 12                   | 8               | 2           | 1   | 2/1                  | 4   | _      | 1                           | 1   | 2   | 1   | Н                    |     |

| PIC16(L)F1507 | (3)              | 2048                            | 128                  | 18                   | 12              |             |     | 2/1                  | 4   | _      |                             | 1   | 2   | 1   | Н                    | _   |

| PIC16(L)F1508 | (4)              | 4096                            | 256                  | 18                   | 12              | 2           | 1   | 2/1                  | 4   | 1      | 1                           | 1   | 4   | 1   | I/H                  | Y   |

| PIC16(L)F1509 | (4)              | 8192                            | 512                  | 18                   | 12              | 2           | 1   | 2/1                  | 4   | 1      | 1                           | 1   | 4   | 1   | I/H                  | Υ   |

Note 1: Debugging Methods: (I) - Integrated on Chip; (H) - using Debug Header; (E) - using Emulation Header.

2: One pin is input-only.

Data Sheet Index: (Unshaded devices are described in this document.)

1: DS40001615 PIC12(L)F1501 Data Sheet, 8-Pin Flash, 8-bit Microcontrollers.

- 2: DS40001607 PIC16(L)F1503 Data Sheet, 14-Pin Flash, 8-bit Microcontrollers.

- 3: DS40001586 PIC16(L)F1507 Data Sheet, 20-Pin Flash, 8-bit Microcontrollers.

- 4: DS40001609 PIC16(L)F1508/9 Data Sheet, 20-Pin Flash, 8-bit Microcontrollers.

**Note:** For other small form-factor package availability and marking information, please visit http://www.microchip.com/packaging or contact your local sales office.

#### 4.2 Register Definitions: Configuration Words

#### R/P-1 R/P-1 R/P-1 U-1 U-1 U-1 BOREN<1:0>(1) CLKOUTEN \_\_\_\_ \_ \_\_\_\_\_ bit 13 bit 8 R/P-1 R/P-1 R/P-1 **R/P-1** R/P-1 U-1 R/P-1 R/P-1 CP(2) PWRTE MCLRE WDTE<1:0> FOSC<1:0> bit 7 bit 0 Legend: R = Readable bit P = Programmable bit U = Unimplemented bit, read as '1' -n = Value when blank or after Bulk Erase 0' = Bit is cleared '1' = Bit is set bit 13-12 Unimplemented: Read as '1' bit 11 **CLKOUTEN:** Clock Out Enable bit 1 = CLKOUT function is disabled. I/O function on the CLKOUT pin 0 = CLKOUT function is enabled on the CLKOUT pin BOREN<1:0>: Brown-Out Reset Enable bits<sup>(1)</sup> bit 10-9 11 = BOR enabled 10 = BOR enabled during operation and disabled in Sleep 01 = BOR controlled by SBOREN bit of the BORCON register 00 = BOR disabled Unimplemented: Read as '1' bit 8 CP: Code Protection bit<sup>(2)</sup> bit 7 1 = Program memory code protection is disabled 0 = Program memory code protection is enabled MCLRE: MCLR/VPP Pin Function Select bit bit 6 If LVP bit = 1: This bit is ignored. If LVP bit = 0: $1 = \overline{MCLR}/VPP$ pin function is $\overline{MCLR}$ ; Weak pull-up enabled. 0 = MCLR/VPP pin function is digital input; MCLR internally disabled; Weak pull-up under control of WPUA3 bit. **PWRTE:** Power-Up Timer Enable bit bit 5 1 = PWRT disabled 0 = PWRT enabled WDTE<1:0>: Watchdog Timer Enable bits bit 4-3 11 = WDT enabled 10 = WDT enabled while running and disabled in Sleep 01 = WDT controlled by the SWDTEN bit in the WDTCON register 00 = WDT disabled bit 2 Unimplemented: Read as '1' bit 1-0 FOSC<1:0>: Oscillator Selection bits 11 = ECH: External Clock, High-Power mode: on CLKIN pin 10 = ECM: External Clock, Medium Power mode: on CLKIN pin 01 = ECL: External Clock, Low-Power mode: on CLKIN pin 00 = INTOSC oscillator: I/O function on CLKIN pin

#### REGISTER 4-1: CONFIG1: CONFIGURATION WORD 1

**Note 1:** Enabling Brown-out Reset does not automatically enable Power-up Timer.

2: Once enabled, code-protect can only be disabled by bulk erasing the device.

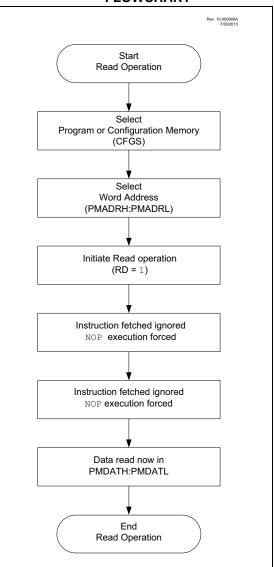

### 10.2.1 READING THE FLASH PROGRAM MEMORY

To read a program memory location, the user must:

- 1. Write the desired address to the PMADRH:PMADRL register pair.

- 2. Clear the CFGS bit of the PMCON1 register.

- 3. Then, set control bit RD of the PMCON1 register.

Once the read control bit is set, the program memory Flash controller will use the second instruction cycle to read the data. This causes the second instruction immediately following the "BSF PMCON1, RD" instruction to be ignored. The data is available in the very next cycle, in the PMDATH:PMDATL register pair; therefore, it can be read as two bytes in the following instructions.

PMDATH:PMDATL register pair will hold this value until another read or until it is written to by the user.

| Note: | The two instructions following a program    |  |  |  |  |  |  |

|-------|---------------------------------------------|--|--|--|--|--|--|

|       | memory read are required to be NOPs.        |  |  |  |  |  |  |

|       | This prevents the user from executing a     |  |  |  |  |  |  |

|       | 2-cycle instruction on the next instruction |  |  |  |  |  |  |

|       | after the RD bit is set.                    |  |  |  |  |  |  |

### FIGURE 10-1: FLASH PROGRAM MEMORY READ FLOWCHART

#### EXAMPLE 10-2: ERASING ONE ROW OF PROGRAM MEMORY

|                      |                                              |                                                      | s the following:<br>erase row is loaded in ADDRH:ADDRL                                                                                                                                                                                                                                                                                                         |

|----------------------|----------------------------------------------|------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| ; 2. A               | ADDRH and AI                                 | DDRL are located                                     | d in shared data memory 0x70 - 0x7F (common RAM)                                                                                                                                                                                                                                                                                                               |

|                      | BCF<br>BANKSEL<br>MOVF<br>MOVWF<br>MOVF      | INTCON,GIE<br>PMADRL<br>ADDRL,W<br>PMADRL<br>ADDRH,W | ; Disable ints so required sequences will execute properly<br>; Load lower 8 bits of erase address boundary<br>; Load upper 6 bits of erase address boundary                                                                                                                                                                                                   |

|                      | MOVWF<br>BCF<br>BSF<br>BSF                   | PMADRH<br>PMCON1,CFGS<br>PMCON1,FREE<br>PMCON1,WREN  | ; Not configuration space<br>; Specify an erase operation<br>; Enable writes                                                                                                                                                                                                                                                                                   |

| Required<br>Sequence | MOVLW<br>MOVWF<br>MOVWF<br>BSF<br>NOP<br>NOP | 55h<br>PMCON2<br>0AAh<br>PMCON2<br>PMCON1,WR         | <pre>; Start of required sequence to initiate erase<br/>; Write 55h<br/>;<br/>; Write AAh<br/>; Set WR bit to begin erase<br/>; NOP instructions are forced as processor starts<br/>; row erase of program memory.<br/>;<br/>;<br/>; The processor stalls until the erase process is complete<br/>; after erase processor continues with 3rd instruction</pre> |

|                      | BCF<br>BSF                                   | PMCON1,WREN<br>INTCON,GIE                            | ; Disable writes<br>; Enable interrupts                                                                                                                                                                                                                                                                                                                        |

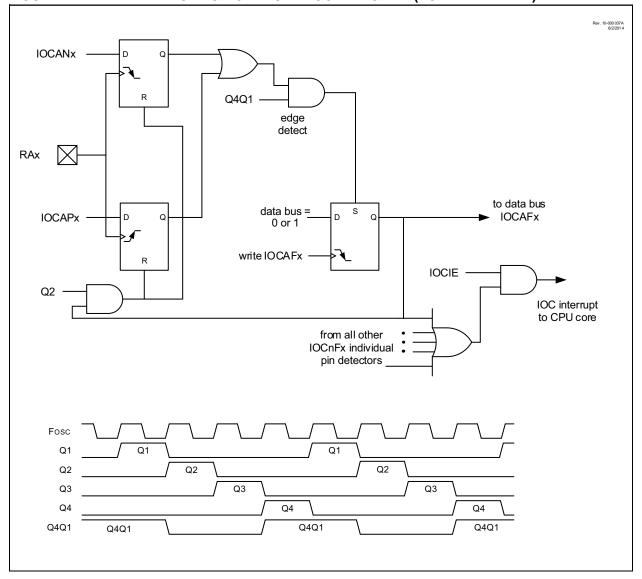

FIGURE 12-1: INTERRUPT-ON-CHANGE BLOCK DIAGRAM (PORTA EXAMPLE)

#### 19.5.2.1 T1G Pin Gate Operation

The T1G pin is one source for Timer1 gate control. It can be used to supply an external source to the Timer1 gate circuitry.

#### 19.5.2.2 Timer0 Overflow Gate Operation

When Timer0 increments from FFh to 00h, a low-tohigh pulse will automatically be generated and internally supplied to the Timer1 gate circuitry.

#### 19.5.3 TIMER1 GATE TOGGLE MODE

When Timer1 Gate Toggle mode is enabled, it is possible to measure the full-cycle length of a Timer1 gate signal, as opposed to the duration of a single level pulse.

The Timer1 gate source is routed through a flip-flop that changes state on every incrementing edge of the signal. See Figure 19-4 for timing details.

Timer1 Gate Toggle mode is enabled by setting the T1GTM bit of the T1GCON register. When the T1GTM bit is cleared, the flip-flop is cleared and held clear. This is necessary in order to control which edge is measured.

| Note: | Enabling Toggle mode at the same time       |  |  |  |  |  |  |  |

|-------|---------------------------------------------|--|--|--|--|--|--|--|

|       | as changing the gate polarity may result in |  |  |  |  |  |  |  |

|       | indeterminate operation.                    |  |  |  |  |  |  |  |

#### 19.5.4 TIMER1 GATE SINGLE-PULSE MODE

When Timer1 Gate Single-Pulse mode is enabled, it is possible to capture a single pulse gate event. Timer1 Gate Single-Pulse mode is first enabled by setting the T1GSPM bit in the T1GCON register. Next, the T1GGO/ DONE bit in the T1GCON register must be set. The Timer1 will be fully enabled on the next incrementing edge. On the next trailing edge of the pulse, the T1GGO/ DONE bit will automatically be cleared. No other gate events will be allowed to increment Timer1 until the T1GGO/DONE bit is once again set in software. See Figure 19-5 for timing details.

If the Single Pulse Gate mode is disabled by clearing the T1GSPM bit in the T1GCON register, the T1GGO/DONE bit should also be cleared.

Enabling the Toggle mode and the Single-Pulse mode simultaneously will permit both sections to work together. This allows the cycle times on the Timer1 gate source to be measured. See Figure 19-6 for timing details.

#### 19.5.5 TIMER1 GATE VALUE STATUS

When Timer1 Gate Value Status is utilized, it is possible to read the most current level of the gate control value. The value is stored in the T1GVAL bit in the T1GCON register. The T1GVAL bit is valid even when the Timer1 gate is not enabled (TMR1GE bit is cleared).

#### 19.5.6 TIMER1 GATE EVENT INTERRUPT

When Timer1 Gate Event Interrupt is enabled, it is possible to generate an interrupt upon the completion of a gate event. When the falling edge of T1GVAL occurs, the TMR1GIF flag bit in the PIR1 register will be set. If the TMR1GIE bit in the PIE1 register is set, then an interrupt will be recognized.

The TMR1GIF flag bit operates even when the Timer1 gate is not enabled (TMR1GE bit is cleared).

| Name   | Bit 7                                                                    | Bit 6          | Bit 5          | Bit 4         | Bit 3          | Bit 2  | Bit 1   | Bit 0   | Register<br>on Page |

|--------|--------------------------------------------------------------------------|----------------|----------------|---------------|----------------|--------|---------|---------|---------------------|

| ANSELA | _                                                                        | —              | —              | ANSA4         | —              | ANSA2  | ANSA1   | ANSA0   | 99                  |

| APFCON | -                                                                        | —              | SDOSEL         | SSSEL         | T1GSEL         | —      | CLC1SEL | NCO1SEL | 96                  |

| INTCON | GIE                                                                      | PEIE           | TMR0IE         | INTE          | IOCIE          | TMR0IF | INTF    | IOCIF   | 64                  |

| PIE1   | TMR1GIE                                                                  | ADIE           | _              | —             | SSP1IE         | —      | TMR2IE  | TMR1IE  | 65                  |

| PIR1   | TMR1GIF                                                                  | ADIF           | _              | —             | SSP1IF         | —      | TMR2IF  | TMR1IF  | 68                  |

| TMR1H  | Holding Regi                                                             | ster for the M | ost Significan | t Byte of the | 16-bit TMR1 (  | Count  |         |         | 144*                |

| TMR1L  | Holding Register for the Least Significant Byte of the 16-bit TMR1 Count |                |                |               |                |        |         |         |                     |

| TRISA  | _                                                                        | —              | TRISA5         | TRISA4        | (1)            | TRISA2 | TRISA1  | TRISA0  | 98                  |

| T1CON  | TMR1C                                                                    | S<1:0>         | T1CKP          | S<1:0>        | —              | T1SYNC | _       | TMR10N  | 148                 |

| T1GCON | TMR1GE                                                                   | T1GPOL         | T1GTM          | T1GSPM        | T1GGO/<br>DONE | T1GVAL | T1GS    | 149     |                     |

**Legend:** — = unimplemented location, read as '0'. Shaded cells are not used by the Timer1 module.

\* Page provides register information.

Note 1: Unimplemented, read as '1'.

#### 21.6.10 SLEEP OPERATION

While in Sleep mode, the I<sup>2</sup>C slave module can receive addresses or data and when an address match or complete byte transfer occurs, wake the processor from Sleep (if the MSSP interrupt is enabled).

#### 21.6.11 EFFECTS OF A RESET

A Reset disables the MSSP module and terminates the current transfer.

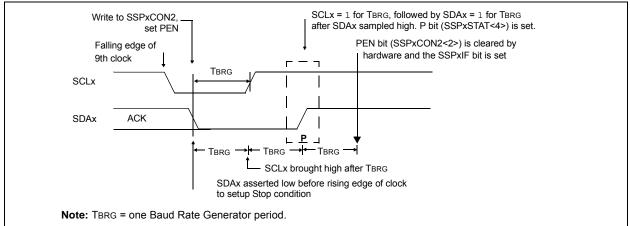

#### 21.6.12 MULTI-MASTER MODE

In Multi-Master mode, the interrupt generation on the detection of the Start and Stop conditions allows the determination of when the bus is free. The Stop (P) and Start (S) bits are cleared from a Reset or when the MSSP module is disabled. Control of the I<sup>2</sup>C bus may be taken when the P bit of the SSPxSTAT register is set, or the bus is idle, with both the S and P bits clear. When the bus is busy, enabling the SSP interrupt will generate the interrupt when the Stop condition occurs.

In Multi-Master mode, the SDAx line must be monitored for arbitration to see if the signal level is the expected output level. This check is performed by hardware with the result placed in the BCLxIF bit.

The states where arbitration can be lost are:

- · Address Transfer

- Data Transfer

- A Start Condition

- · A Repeated Start Condition

- An Acknowledge Condition

#### 21.6.13 MULTI -MASTER COMMUNICATION, BUS COLLISION AND BUS ARBITRATION

Multi-Master mode support is achieved by bus arbitration. When the master outputs address/data bits onto the SDAx pin, arbitration takes place when the master outputs a '1' on SDAx, by letting SDAx float high and another master asserts a '0'. When the SCLx pin floats high, data should be stable. If the expected data on SDAx is a '1' and the data sampled on the SDAx pin is '0', then a bus collision has taken place. The master will set the Bus Collision Interrupt Flag, BCLxIF and reset the I<sup>2</sup>C port to its Idle state (Figure 21-32).

If a transmit was in progress when the bus collision occurred, the transmission is halted, the BF flag is cleared, the SDAx and SCLx lines are deasserted and the SSPxBUF can be written to. When the user services the bus collision Interrupt Service Routine and if the  $l^2C$  bus is free, the user can resume communication by asserting a Start condition.

If a Start, Repeated Start, Stop or Acknowledge condition was in progress when the bus collision occurred, the condition is aborted, the SDAx and SCLx lines are deasserted and the respective control bits in the SSPxCON2 register are cleared. When the user services the bus collision Interrupt Service Routine and if the I<sup>2</sup>C bus is free, the user can resume communication by asserting a Start condition.

The master will continue to monitor the SDAx and SCLx pins. If a Stop condition occurs, the SSPxIF bit will be set.

A write to the SSPxBUF will start the transmission of data at the first data bit, regardless of where the transmitter left off when the bus collision occurred.

In Multi-Master mode, the interrupt generation on the detection of Start and Stop conditions allows the determination of when the bus is free. Control of the  $I^2C$  bus can be taken when the P bit is set in the SSPxSTAT register, or the bus is idle and the S and P bits are cleared.

#### REGISTER 21-2: SSPxCON1: SSP CONTROL REGISTER 1

| R/C/HS-0/0        | R/C/HS-0/0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | R/W-0/0                                                                                                                                               | R/W-0/0                                                                                                                                                                                     | R/W-0/0                                                                                                  | R/W-0/0                                  | R/W-0/0                                             | R/W-0/0                                     |  |

|-------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------|------------------------------------------|-----------------------------------------------------|---------------------------------------------|--|

| WCOL              | SSPOV <sup>(1)</sup>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | SSPEN                                                                                                                                                 | CKP                                                                                                                                                                                         |                                                                                                          | SSPI                                     | M<3:0>                                              |                                             |  |

| bit 7             | •                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | ·                                                                                                                                                     |                                                                                                                                                                                             | ·                                                                                                        |                                          |                                                     | bit                                         |  |

|                   |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |                                                                                                                                                       |                                                                                                                                                                                             |                                                                                                          |                                          |                                                     |                                             |  |

| Legend:           |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |                                                                                                                                                       |                                                                                                                                                                                             |                                                                                                          |                                          |                                                     |                                             |  |

| R = Readable bi   | t                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | W = Writable bit                                                                                                                                      |                                                                                                                                                                                             | U = Unimplement                                                                                          | ted bit, read as '0'                     |                                                     |                                             |  |

| u = Bit is unchar | nged                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | x = Bit is unknow                                                                                                                                     | 'n                                                                                                                                                                                          | -n/n = Value at Po                                                                                       | OR and BOR/Value                         | e at all other Resets                               |                                             |  |

| '1' = Bit is set  |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | '0' = Bit is cleared                                                                                                                                  | b                                                                                                                                                                                           | HS = Bit is set by                                                                                       | hardware                                 | C = User cleared                                    |                                             |  |

| bit 7             | 0 = No collisior<br>Slave mode:                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | he SSPxBUF regist<br>ו<br>UF register is writter                                                                                                      | ·                                                                                                                                                                                           | d while the I <sup>2</sup> C condi<br>smitting the previous                                              |                                          |                                                     | to be started                               |  |

| bit 6             | In SPI mode:<br>1 = A new byte<br>Overflow ca<br>setting over<br>SSPxBUF r<br>0 = No overflow<br>In I <sup>2</sup> C mode:<br>1 = A byte is re                                                                                                                                                                                                                                                                                                                                                                           | an only occur in Slav<br>flow. In Master mode<br>register (must be cle<br>w<br>eccived while the S<br>leared in software).                            | SSPxBUF register<br>re mode. In Slave<br>e, the overflow bit<br>ared in software).                                                                                                          | er is still holding the pr<br>mode, the user must<br>is not set since each r<br>r is still holding the p | read the SSPxBUF<br>new reception (and t | ; even if only transmit<br>ransmission) is initiate | ting data, to avoid<br>ed by writing to the |  |

| bit 5             | SSPEN: Synchro<br>In both modes, w<br>In <u>SPI mode:</u><br>1 = Enables set<br>0 = Disables set<br><u>In I<sup>2</sup>C mode:</u><br>1 = Enables the<br>0 = Disables set                                                                                                                                                                                                                                                                                                                                                |                                                                                                                                                       |                                                                                                                                                                                             |                                                                                                          |                                          |                                                     |                                             |  |

| bit 4             | <ul> <li>0 = Disables serial port and configures these pins as I/O port pins</li> <li>CKP: Clock Polarity Select bit <ul> <li>In SPI mode:</li> <li>1 = Idle state for clock is a high level</li> <li>0 = Idle state for clock is a low level</li> <li>In I<sup>2</sup>C Slave mode:</li> <li>SCLx release control</li> <li>1 = Enable clock</li> <li>0 = Holds clock low (clock stretch). (Used to ensure data setup time.)</li> <li>In I<sup>2</sup>C Master mode:</li> <li>Unused in this mode</li> </ul> </li> </ul> |                                                                                                                                                       |                                                                                                                                                                                             |                                                                                                          |                                          |                                                     |                                             |  |

| bit 3-0           | 0000 = SPI Mas<br>0001 = SPI Mas<br>0010 = SPI Mas<br>0010 = SPI Mas<br>0100 = SPI Slav<br>0101 = SPI Slav<br>0110 = I <sup>2</sup> C Slave<br>0110 = I <sup>2</sup> C Slave<br>1000 = I <sup>2</sup> C Mast<br>1001 = Reservee<br>1010 = SPI Mas<br>1011 = I <sup>2</sup> C firmw<br>1100 = Reservee<br>1101 = Reservee<br>1101 = Reservee<br>1101 = Reservee<br>1100 = Reservee                                                                                                                                        | e mode, 7-bit addre<br>e mode, 10-bit addr<br>er mode, clock = Fr<br>d<br>ter mode, clock = F<br>vare controlled Mas<br>d<br>d<br>e mode, 7-bit addre | osc/4<br>osc/16<br>osc/64<br>2_match/2<br>XKx pin, <u>SS</u> pin c<br>SKx pin, <u>SS</u> pin c<br>ss<br>ess<br>osc/(4 * (SSPxAl<br>osc/(4 * (SSPxAl<br>ter mode (Slave<br>ss with Start and | ontrol enabled<br>ontrol disabled, SSx<br>DD+1)) <sup>(4)</sup><br>DD+1)) <sup>(5)</sup>                 | nabled                                   | ) pin                                               |                                             |  |

| 2: W<br>3: W      | Master mode, the ov<br>hen enabled, these p<br>hen enabled, the SD/<br>SPXADD values of 0,                                                                                                                                                                                                                                                                                                                                                                                                                               | erflow bit is not set<br>ins must be proper<br>Ax and SCLx pins r                                                                                     | since each new<br>ly configured as i<br>nust be configure                                                                                                                                   | reception (and transi<br>input or output.<br>ed as inputs.                                               |                                          | I by writing to the SS                              | PxBUF register.                             |  |

- SSPxADD values of 0, 1 or 2 are not supported for I<sup>2</sup>C mode.

SSPxADD value of '0' is not supported. Use SSPM = 0000 instead.

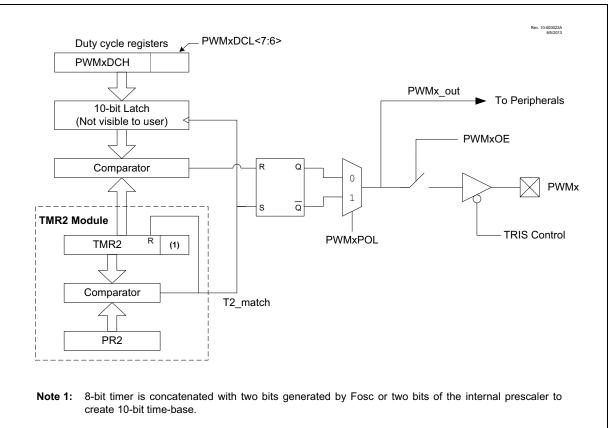

#### 22.0 PULSE-WIDTH MODULATION (PWM) MODULE

The PWM module generates a Pulse-Width Modulated signal determined by the duty cycle, period, and resolution that are configured by the following registers:

- PR2

- T2CON

- PWMxDCH

- PWMxDCL

- PWMxCON

Figure 22-1 shows a simplified block diagram of PWM operation.

For a step-by-step procedure on how to set up this module for PWM operation, refer to Section 22.1.9 "Setup for PWM Operation using PWMx Pins".

#### FIGURE 22-1: SIMPLIFIED PWM BLOCK DIAGRAM

| U-0             | R/W-x/u                               | R/W-x/u                                                                        | R/W-x/u      | U-0                        | R/W-x/u          | R/W-x/u                    | R/W-x/u     |  |  |  |  |  |

|-----------------|---------------------------------------|--------------------------------------------------------------------------------|--------------|----------------------------|------------------|----------------------------|-------------|--|--|--|--|--|

|                 |                                       | LCxD2S<2:0>(1)                                                                 |              | —                          | L                | _CxD1S<2:0> <sup>(1)</sup> |             |  |  |  |  |  |

| bit 7           | •                                     |                                                                                |              |                            |                  |                            | bit         |  |  |  |  |  |

|                 |                                       |                                                                                |              |                            |                  |                            |             |  |  |  |  |  |

| Legend:         |                                       |                                                                                |              |                            |                  |                            |             |  |  |  |  |  |

| R = Readabl     | le bit                                | W = Writable b                                                                 | bit          | U = Unimplei               | mented bit, read | d as '0'                   |             |  |  |  |  |  |

| u = Bit is und  | changed                               | x = Bit is unkn                                                                | own          | -n/n = Value               | at POR and BC    | R/Value at all o           | ther Resets |  |  |  |  |  |

| '1' = Bit is se | et                                    | '0' = Bit is clea                                                              | ired         |                            |                  |                            |             |  |  |  |  |  |

|                 |                                       |                                                                                |              |                            |                  |                            |             |  |  |  |  |  |

| bit 7           | Unimpleme                             | nted: Read as '0                                                               | ,            |                            |                  |                            |             |  |  |  |  |  |

| bit 6-4         | LCxD2S<2:                             | LCxD2S<2:0>: Input Data 2 Selection Control bits <sup>(1)</sup>                |              |                            |                  |                            |             |  |  |  |  |  |

|                 | 111 = LCx_                            | 111 = LCx_in[11] is selected for lcxd2                                         |              |                            |                  |                            |             |  |  |  |  |  |

|                 |                                       | 110 = LCx_in[10] is selected for lcxd2                                         |              |                            |                  |                            |             |  |  |  |  |  |

|                 |                                       | $101 = LCx_in[9]$ is selected for lcxd2                                        |              |                            |                  |                            |             |  |  |  |  |  |

|                 |                                       | in[8] is selected                                                              |              |                            |                  |                            |             |  |  |  |  |  |

|                 |                                       | $011 = LCx_in[7] \text{ is selected for } lcxd2$                               |              |                            |                  |                            |             |  |  |  |  |  |

|                 |                                       | 010 = LCx_in[6] is selected for lcxd2<br>001 = LCx_in[5] is selected for lcxd2 |              |                            |                  |                            |             |  |  |  |  |  |

|                 |                                       | = LCx_in[5] is selected for lcxd2<br>= LCx_in[4] is selected for lcxd2         |              |                            |                  |                            |             |  |  |  |  |  |

| bit 3           |                                       | nted: Read as '0                                                               |              |                            |                  |                            |             |  |  |  |  |  |

| bit 2-0         | LCxD1S<2:                             | <b>0&gt;:</b> Input Data 1                                                     | Selection Co | ontrol bits <sup>(1)</sup> |                  |                            |             |  |  |  |  |  |

|                 | 111 = LCx                             | in[7] is selected                                                              | for lcxd1    |                            |                  |                            |             |  |  |  |  |  |

|                 |                                       | 110 = LCx in[6] is selected for lcxd1                                          |              |                            |                  |                            |             |  |  |  |  |  |

|                 | 101 = LCx_                            | 101 = LCx_in[5] is selected for lcxd1                                          |              |                            |                  |                            |             |  |  |  |  |  |

|                 | 100 = LCx_                            | in[4] is selected                                                              | for lcxd1    |                            |                  |                            |             |  |  |  |  |  |

|                 |                                       | 011 = LCx_in[3] is selected for lcxd1                                          |              |                            |                  |                            |             |  |  |  |  |  |

|                 | 010 = LCx_in[2] is selected for lcxd1 |                                                                                |              |                            |                  |                            |             |  |  |  |  |  |

|                 |                                       | in[1] is selected i                                                            |              |                            |                  |                            |             |  |  |  |  |  |

|                 | $000 = LCx_{}$                        | in[0] is selected t                                                            | for Icxd1    |                            |                  |                            |             |  |  |  |  |  |

#### REGISTER 23-3: CLCxSEL0: MULTIPLEXER DATA 1 AND 2 SELECT REGISTER

**Note 1:** See Table 23-1 for signal names associated with inputs.

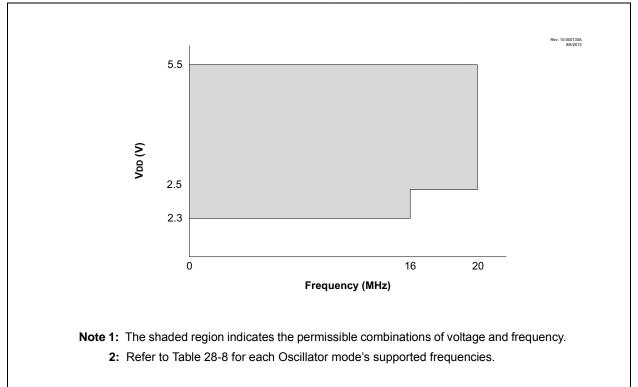

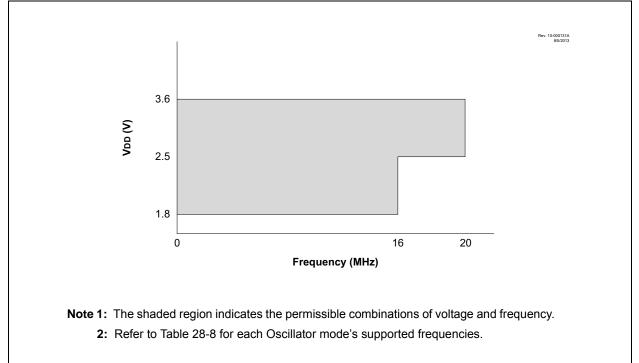

#### 28.2 Standard Operating Conditions

The standard operating conditions for any device are defined as:

|                                              | ······································ |        |

|----------------------------------------------|----------------------------------------|--------|

| Operating Voltage:<br>Operating Temperature: |                                        |        |

| VDD — Operating Supply                       | y Voltage <sup>(1)</sup>               |        |

| PIC16LF1503                                  |                                        |        |

| Vddmin (F                                    | Fosc $\leq$ 16 MHz)                    | +1.8V  |

| VDDMIN (1                                    | 16 MHz < Fosc $\leq$ 20 MHz)           | +2.5V  |

| VDDMAX                                       |                                        | +3.6V  |

| PIC16F1503                                   |                                        |        |

| Vddmin (F                                    | Fosc $\leq$ 16 MHz)                    |        |

| VDDMIN (1                                    | 16 MHz < Fosc $\leq$ 20 MHz)           | +2.5V  |

| VDDMAX                                       |                                        | +5.5V  |

| TA — Operating Ambien                        | t Temperature Range                    |        |

| Industrial Temperat                          | ture                                   |        |

| Та_міл                                       |                                        | 40°C   |

| Та_мах                                       |                                        | +85°C  |

| Extended Tempera                             | ture                                   |        |

| TA_MIN                                       |                                        | 40°C   |

| Та_мах                                       |                                        | +125°C |

| _                                            |                                        |        |

Note 1: See Parameter D001, DC Characteristics: Supply Voltage.

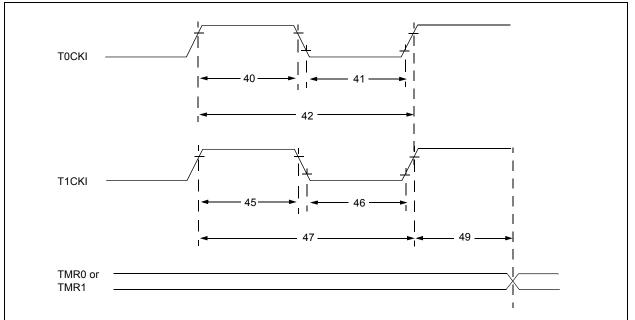

#### FIGURE 28-10: TIMER0 AND TIMER1 EXTERNAL CLOCK TIMINGS

| TABLE 28-11: | TIMER0 AND TIMER1 EXTERNAL CLOCK REQUIREMENTS |

|--------------|-----------------------------------------------|

|--------------|-----------------------------------------------|

| Standar       | rd Operating | Conditions (u             | nless otherwis              | e stated)      |                                           |      |        |       |                        |

|---------------|--------------|---------------------------|-----------------------------|----------------|-------------------------------------------|------|--------|-------|------------------------|

| Param.<br>No. | Sym.         |                           | Characteristi               | c              | Min.                                      | Тур† | Max.   | Units | Conditions             |

| 40*           | T⊤0H         | T0CKI High F              | Pulse Width                 | No Prescaler   | 0.5 Tcy + 20                              | _    |        | ns    |                        |

|               |              |                           |                             | With Prescaler | 10                                        | _    | _      | ns    |                        |

| 41*           | TT0L         | T0CKI Low F               | ulse Width                  | No Prescaler   | 0.5 Tcy + 20                              |      |        | ns    |                        |

|               |              |                           | With Prescaler              |                | 10                                        |      |        | ns    |                        |

| 42*           | Тт0Р         | T0CKI Period              | 1                           |                | Greater of:<br>20 or <u>Tcy + 40</u><br>N | _    | _      | ns    | N = prescale value     |

| 45*           | T⊤1H         | T1CKI High<br>Time        | Synchronous, No Prescaler   |                | 0.5 Tcy + 20                              |      |        | ns    |                        |

|               |              |                           | Synchronous, with Prescaler |                | 15                                        |      |        | ns    |                        |

|               |              |                           | Asynchronous                |                | 30                                        |      |        | ns    |                        |

| 46*           | TT1L         | T1CKI Low                 | Synchronous, N              | No Prescaler   | 0.5 Tcy + 20                              |      |        | ns    |                        |

|               |              | Time                      | Synchronous, with Prescaler |                | 15                                        |      |        | ns    |                        |

|               |              |                           | Asynchronous                |                | 30                                        |      |        | ns    |                        |

| 47*           | TT1P         | T1CKI Input<br>Period     | Synchronous                 |                | Greater of:<br>30 or <u>Tcy + 40</u><br>N | —    | _      | ns    | N = prescale value     |

|               |              |                           | Asynchronous                |                | 60                                        | _    | _      | ns    |                        |

| 49*           | TCKEZTMR1    | Delay from E<br>Increment | xternal Clock Ed            | dge to Timer   | 2 Tosc                                    |      | 7 Tosc | —     | Timers in Sync<br>mode |

These parameters are characterized but not tested.

† Data in "Typ" column is at 3.0V, 25°C unless otherwise stated. These parameters are for design guidance only and are not tested.

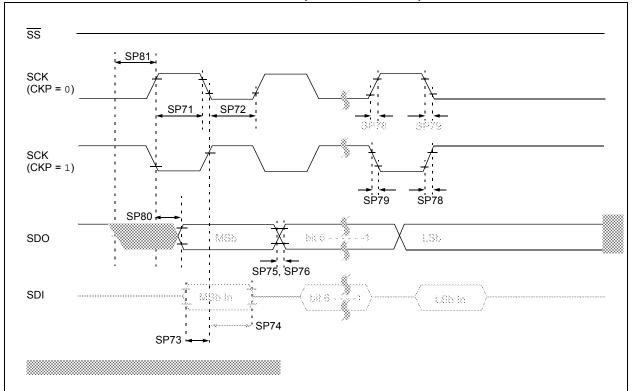

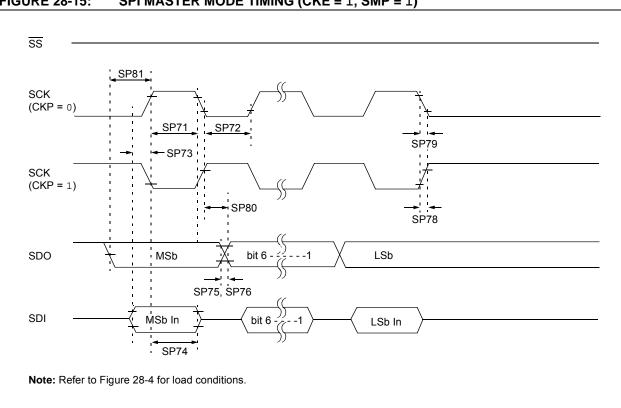

FIGURE 28-15: SPI MASTER MODE TIMING (CKE = 1, SMP = 1)

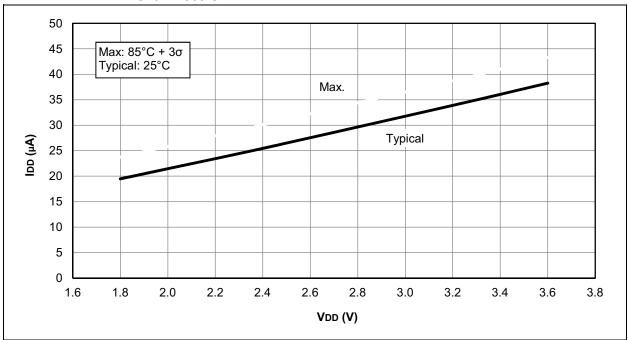

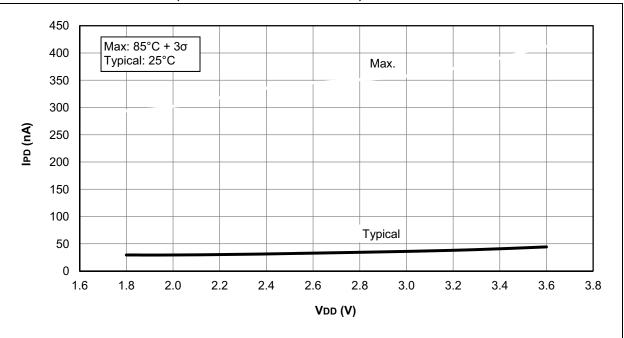

FIGURE 29-3: IDD, EXTERNAL CLOCK (ECL), LOW-POWER MODE, Fosc = 500 kHz, PIC16LF1503 ONLY

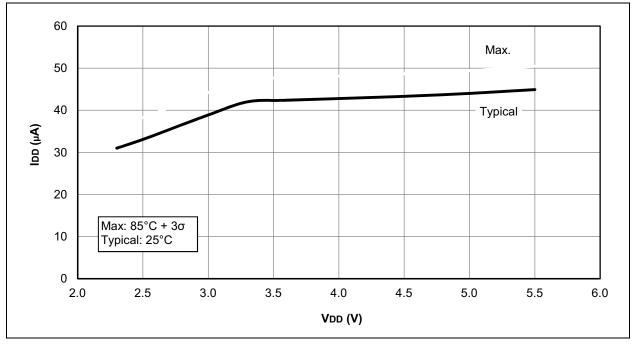

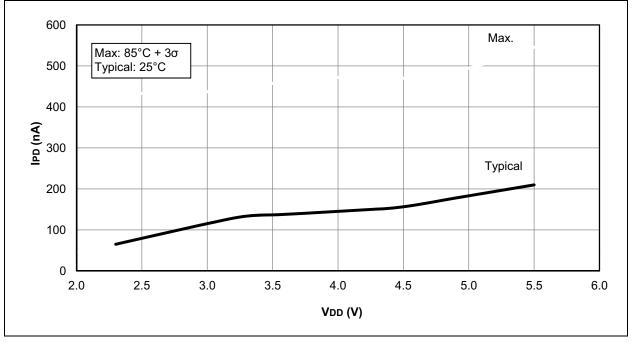

FIGURE 29-4: IDD, EXTERNAL CLOCK (ECL), LOW-POWER MODE, Fosc = 500 kHz, PIC16F1503 ONLY

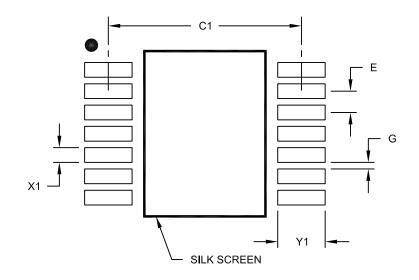

### 14-Lead Plastic Thin Shrink Small Outline (ST) - 4.4 mm Body [TSSOP]

**Note:** For the most current package drawings, please see the Microchip Packaging Specification located at http://www.microchip.com/packaging

#### RECOMMENDED LAND PATTERN

| Units                    |    | MILLIMETERS |      |      |

|--------------------------|----|-------------|------|------|

| Dimension Limits         |    | MIN         | NOM  | MAX  |

| Contact Pitch            | E  | 0.65 BSC    |      |      |

| Contact Pad Spacing      | C1 |             | 5.90 |      |

| Contact Pad Width (X14)  | X1 |             |      | 0.45 |

| Contact Pad Length (X14) | Y1 |             |      | 1.45 |

| Distance Between Pads    | G  | 0.20        |      |      |

Notes:

1. Dimensioning and tolerancing per ASME Y14.5M

BSC: Basic Dimension. Theoretically exact value shown without tolerances.

Microchip Technology Drawing No. C04-2087A