Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

#### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Details                    |                                                                             |

|----------------------------|-----------------------------------------------------------------------------|

| Product Status             | Active                                                                      |

| Core Processor             | PIC                                                                         |

| Core Size                  | 8-Bit                                                                       |

| Speed                      | 20MHz                                                                       |

| Connectivity               | I <sup>2</sup> C, SPI                                                       |

| Peripherals                | Brown-out Detect/Reset, POR, PWM, WDT                                       |

| Number of I/O              | 11                                                                          |

| Program Memory Size        | 3.5KB (2K x 14)                                                             |

| Program Memory Type        | FLASH                                                                       |

| EEPROM Size                | -                                                                           |

| RAM Size                   | 128 x 8                                                                     |

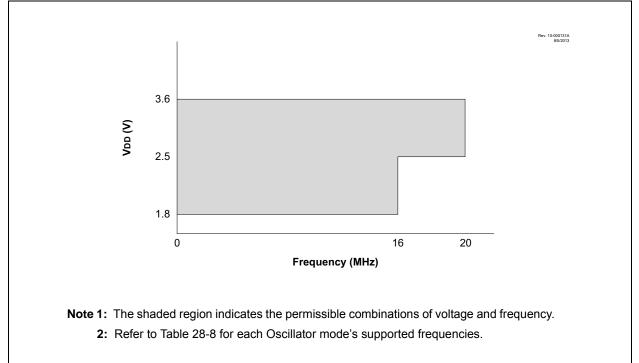

| Voltage - Supply (Vcc/Vdd) | 1.8V ~ 3.6V                                                                 |

| Data Converters            | A/D 8x10b                                                                   |

| Oscillator Type            | Internal                                                                    |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                           |

| Mounting Type              | Surface Mount                                                               |

| Package / Case             | 16-VFQFN Exposed Pad                                                        |

| Supplier Device Package    | 16-QFN (3x3)                                                                |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic16lf1503t-i-mg |

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

# TO OUR VALUED CUSTOMERS

It is our intention to provide our valued customers with the best documentation possible to ensure successful use of your Microchip products. To this end, we will continue to improve our publications to better suit your needs. Our publications will be refined and enhanced as new volumes and updates are introduced.

If you have any questions or comments regarding this publication, please contact the Marketing Communications Department via E-mail at **docerrors@microchip.com** or fax the **Reader Response Form** in the back of this data sheet to (480) 792-4150. We welcome your feedback.

#### Most Current Data Sheet

To obtain the most up-to-date version of this data sheet, please register at our Worldwide Website at:

#### http://www.microchip.com

You can determine the version of a data sheet by examining its literature number found on the bottom outside corner of any page. The last character of the literature number is the version number, (e.g., DS30000A is version A of document DS30000).

#### Errata

An errata sheet, describing minor operational differences from the data sheet and recommended workarounds, may exist for current devices. As device/documentation issues become known to us, we will publish an errata sheet. The errata will specify the revision of silicon and revision of document to which it applies.

To determine if an errata sheet exists for a particular device, please check with one of the following:

- Microchip's Worldwide Website; http://www.microchip.com

- Your local Microchip sales office (see last page)

When contacting a sales office, please specify which device, revision of silicon and data sheet (include literature number) you are using.

#### **Customer Notification System**

Register on our website at www.microchip.com to receive the most current information on all of our products.

# 4.0 DEVICE CONFIGURATION

Device configuration consists of Configuration Words, Code Protection and Device ID.

## 4.1 Configuration Words

There are several Configuration Word bits that allow different oscillator and memory protection options. These are implemented as Configuration Word 1 at 8007h and Configuration Word 2 at 8008h.

Note: The DEBUG bit in Configuration Words is managed automatically by device development tools including debuggers and programmers. For normal device operation, this bit should be maintained as a '1'.

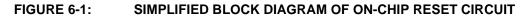

# 6.0 RESETS

There are multiple ways to reset this device:

- Power-on Reset (POR)

- Brown-out Reset (BOR)

- Low-Power Brown-out Reset (LPBOR)

- MCLR Reset

- WDT Reset

- RESET instruction

- Stack Overflow

- · Stack Underflow

- Programming mode exit

To allow VDD to stabilize, an optional power-up timer can be enabled to extend the Reset time after a BOR or POR event.

A simplified block diagram of the On-chip Reset Circuit is shown in Figure 6-1.

## 6.1 Power-On Reset (POR)

The POR circuit holds the device in Reset until VDD has reached an acceptable level for minimum operation. Slow rising VDD, fast operating speeds or analog performance may require greater than minimum VDD. The PWRT, BOR or MCLR features can be used to extend the start-up period until all device operation conditions have been met.

#### 6.1.1 POWER-UP TIMER (PWRT)

The Power-up Timer provides a nominal 64 ms time-out on POR or Brown-out Reset.

The device is held in Reset as long as PWRT is active. The PWRT delay allows additional time for the VDD to rise to an acceptable level. The Power-up Timer is enabled by clearing the PWRTE bit in Configuration Words.

The Power-up Timer starts after the release of the POR and BOR.

For additional information, refer to Application Note AN607, *"Power-up Trouble Shooting"* (DS00607).

## 6.2 Brown-Out Reset (BOR)

The BOR circuit holds the device in Reset when VDD reaches a selectable minimum level. Between the POR and BOR, complete voltage range coverage for execution protection can be implemented.

The Brown-out Reset module has four operating modes controlled by the BOREN<1:0> bits in Configuration Words. The four operating modes are:

- BOR is always on

- · BOR is off when in Sleep

- BOR is controlled by software

- · BOR is always off

Refer to Table 6-1 for more information.

The Brown-out Reset voltage level is selectable by configuring the BORV bit in Configuration Words.

A VDD noise rejection filter prevents the BOR from triggering on small events. If VDD falls below Vpor for a duration greater than parameter TBORDC, the device will reset. See Figure 6-2 for more information.

| BOREN<1:0> | SBOREN | Device Mode | BOR Mode | Instruction Execution upon:<br>Release of POR or Wake-up from Sleep |  |  |  |  |  |

|------------|--------|-------------|----------|---------------------------------------------------------------------|--|--|--|--|--|

| 11         | Х      | х           | Active   | Waits for BOR ready <sup>(1)</sup><br>(BORRDY = 1)                  |  |  |  |  |  |

| 1.0        |        | Awake       | Active   | Waits for BOR ready                                                 |  |  |  |  |  |

| 10         | Х      | Sleep       | Disabled | (BORRDY = 1)                                                        |  |  |  |  |  |

| 01         | 1      | х           | Active   | Waits for BOR ready <sup>(1)</sup><br>(BORRDY = 1)                  |  |  |  |  |  |

|            | 0      | х           | Disabled | Begins immediately                                                  |  |  |  |  |  |

| 00         | х      | х           | Disabled | (BORRDY = x)                                                        |  |  |  |  |  |

TABLE 6-1:BOR OPERATING MODES

Note 1: In these specific cases, "release of POR" and "wake-up from Sleep," there is no delay in start-up. The BOR ready flag, (BORRDY = 1), will be set before the CPU is ready to execute instructions because the BOR circuit is forced on by the BOREN<1:0> bits.

#### 6.2.1 BOR IS ALWAYS ON

When the BOREN bits of Configuration Words are programmed to '11', the BOR is always on. The device start-up will be delayed until the BOR is ready and VDD is higher than the BOR threshold.

BOR protection is active during Sleep. The BOR does not delay wake-up from Sleep.

### 6.2.2 BOR IS OFF IN SLEEP

When the BOREN bits of Configuration Words are programmed to '10', the BOR is on, except in Sleep. The device start-up will be delayed until the BOR is ready and VDD is higher than the BOR threshold. BOR protection is not active during Sleep. The device wake-up will be delayed until the BOR is ready.

### 6.2.3 BOR CONTROLLED BY SOFTWARE

When the BOREN bits of Configuration Words are programmed to '01', the BOR is controlled by the SBOREN bit of the BORCON register. The device start-up is not delayed by the BOR ready condition or the VDD level.

BOR protection begins as soon as the BOR circuit is ready. The status of the BOR circuit is reflected in the BORRDY bit of the BORCON register.

BOR protection is unchanged by Sleep.

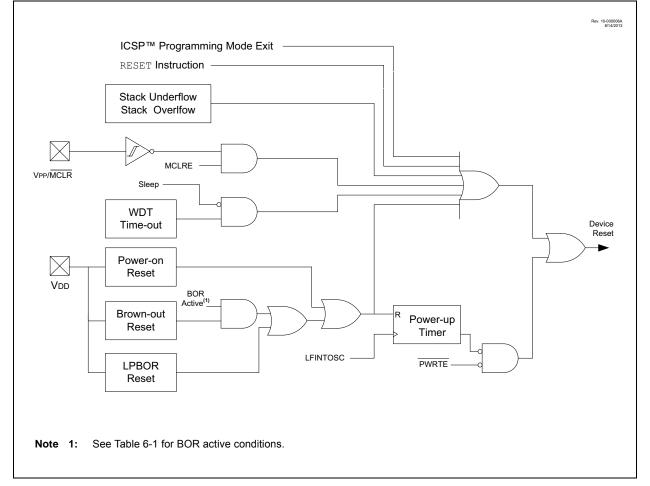

#### EXAMPLE 10-1: FLASH PROGRAM MEMORY READ

```

* This code block will read 1 word of program

* memory at the memory address:

PROG_ADDR_HI : PROG_ADDR_LO

data will be returned in the variables;

PROG_DATA_HI, PROG_DATA_LO

BANKSEL PMADRL

; Select Bank for PMCON registers

PROG_ADDR_LO

MOVLW

;

MOVWF

PMADRL

; Store LSB of address

PROG_ADDR_HI

MOVLW

;

MOVWF

PMADRH

; Store MSB of address

BCF

PMCON1,CFGS

; Do not select Configuration Space

BSF

PMCON1,RD

; Initiate read

NOP

; Ignored (Figure 10-2)

NOP

; Ignored (Figure 10-2)

MOVF

PMDATL,W

; Get LSB of word

MOVWF

PROG_DATA_LO

; Store in user location

; Get MSB of word

PMDATH,W

MOVF

MOVWF

PROG_DATA_HI

; Store in user location

```

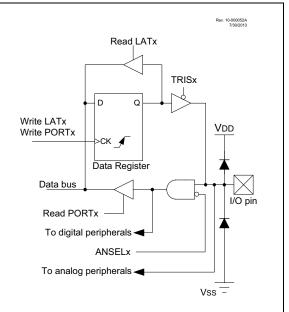

# 11.0 I/O PORTS

Each port has three standard registers for its operation. These registers are:

- · TRISx registers (data direction)

- PORTx registers (reads the levels on the pins of the device)

- LATx registers (output latch)

Some ports may have one or more of the following additional registers. These registers are:

- · ANSELx (analog select)

- · WPUx (weak pull-up)

In general, when a peripheral is enabled on a port pin, that pin cannot be used as a general purpose output. However, the pin can still be read.

# TABLE 11-1:PORT AVAILABILITY PER<br/>DEVICE

| Device        | РОКТА | РОКТВ | PORTC |

|---------------|-------|-------|-------|

| PIC16(L)F1503 | ٠     |       | ٠     |

The Data Latch (LATx registers) is useful for read-modify-write operations on the value that the I/O pins are driving.

A write operation to the LATx register has the same effect as a write to the corresponding PORTx register. A read of the LATx register reads of the values held in the I/O PORT latches, while a read of the PORTx register reads the actual I/O pin value.

Ports that support analog inputs have an associated ANSELx register. When an ANSEL bit is set, the digital input buffer associated with that bit is disabled. Disabling the input buffer prevents analog signal levels on the pin between a logic high and low from causing excessive current in the logic input circuitry. A simplified model of a generic I/O port, without the interfaces to other peripherals, is shown in Figure 11-1.

# FIGURE 11-1: GE

#### GENERIC I/O PORT OPERATION

# 15.3 Register Definitions: ADC Control

| U-0            | R/W-0/0             | R/W-0/0           | R/W-0/0             | R/W-0/0         | R/W-0/0         | R/W-0/0           | R/W-0/0      |  |  |  |

|----------------|---------------------|-------------------|---------------------|-----------------|-----------------|-------------------|--------------|--|--|--|

| _              |                     |                   | CHS<4:0>            |                 |                 | GO/DONE           | ADON         |  |  |  |

| oit 7          | ·                   |                   |                     |                 |                 |                   | bit          |  |  |  |

|                |                     |                   |                     |                 |                 |                   |              |  |  |  |

| Legend:        |                     |                   |                     |                 |                 |                   |              |  |  |  |

| R = Readat     | ole bit             | W = Writable      | bit                 | U = Unimpler    | nented bit, rea | id as '0'         |              |  |  |  |

| u = Bit is ur  | nchanged            | x = Bit is unk    | nown                | -n/n = Value a  | at POR and BO   | OR/Value at all o | other Resets |  |  |  |

| '1' = Bit is s | et                  | '0' = Bit is cle  | ared                |                 |                 |                   |              |  |  |  |

| bit 7          | Unimpleme           | nted: Read as     | 0'                  |                 |                 |                   |              |  |  |  |

| bit 6-2        | -                   | Analog Channe     |                     |                 |                 |                   |              |  |  |  |

| DIL 0-2        | 00000 = AN          | -                 | I Select bits       |                 |                 |                   |              |  |  |  |

|                | 00000 = AN          |                   |                     |                 |                 |                   |              |  |  |  |

|                | 00010 = AN          |                   |                     |                 |                 |                   |              |  |  |  |

|                | 00011 = AN          | 13                |                     |                 |                 |                   |              |  |  |  |

|                | 00100 = AN          | 00100 = AN4       |                     |                 |                 |                   |              |  |  |  |

|                | 00101 = AN          | -                 |                     |                 |                 |                   |              |  |  |  |

|                | 00110 = AN          |                   |                     |                 |                 |                   |              |  |  |  |

|                | 00111 = AN          |                   | nnal anna ata       | 4               |                 |                   |              |  |  |  |

|                | 01000 = Re          | eserved. No cha   | nnei connecte       | α.              |                 |                   |              |  |  |  |

|                | •                   |                   |                     |                 |                 |                   |              |  |  |  |

|                | •                   |                   |                     |                 |                 |                   |              |  |  |  |

|                | 11100 <b>= Re</b>   | served. No cha    | nnel connecte       | d.              |                 |                   |              |  |  |  |

|                | 11101 <b>= Te</b> r | mperature Indic   | ator <sup>(1)</sup> |                 |                 |                   |              |  |  |  |

|                |                     | C (Digital-to-An  |                     |                 |                 |                   |              |  |  |  |

|                | 11111 <b>= FV</b>   | R (Fixed Voltage  | e Reference) E      | Buffer 1 Output | 2)              |                   |              |  |  |  |

| bit 1          | GO/DONE:            | ADC Conversio     | n Status bit        |                 |                 |                   |              |  |  |  |

|                |                     | nversion cycle ii |                     |                 |                 |                   |              |  |  |  |

|                |                     |                   |                     |                 | e ADC conver    | sion has comple   | eted.        |  |  |  |

|                | 0 = ADC cor         | nversion comple   | eted/not in proo    | gress           |                 |                   |              |  |  |  |

| bit 0          | ADON: ADO           |                   |                     |                 |                 |                   |              |  |  |  |

|                | 1 = ADC is e        |                   |                     |                 |                 |                   |              |  |  |  |

|                |                     | disabled and co   | -                   | -               |                 |                   |              |  |  |  |

|                | See Section 14.     | -                 |                     |                 |                 |                   |              |  |  |  |

| 2: 3           | See Section 13.     | 0 "Fixed Voltag   | e Reference         | (FVR)" for more | e information.  |                   |              |  |  |  |

| 3: 5           | See Section 16.     | 6 "E Dit Digital  | to Anolog Co        |                 | Madula? for     | a a sa infansatio | _            |  |  |  |

# REGISTER 15-1: ADCON0: ADC CONTROL REGISTER 0

#### 21.2.4 SPI SLAVE MODE

In Slave mode, the data is transmitted and received as external clock pulses appear on SCKx. When the last bit is latched, the SSPxIF interrupt flag bit is set.

Before enabling the module in SPI Slave mode, the clock line must match the proper Idle state. The clock line can be observed by reading the SCKx pin. The Idle state is determined by the CKP bit of the SSPxCON1 register.

While in Slave mode, the external clock is supplied by the external clock source on the SCKx pin. This external clock must meet the minimum high and low times as specified in the electrical specifications.

While in Sleep mode, the slave can transmit/receive data. The shift register is clocked from the SCKx pin input and when a byte is received, the device will generate an interrupt. If enabled, the device will wake-up from Sleep.

#### 21.2.4.1 Daisy-Chain Configuration

The SPI bus can sometimes be connected in a daisy-chain configuration. The first slave output is connected to the second slave input, the second slave output is connected to the third slave input, and so on. The final slave output is connected to the master input. Each slave sends out, during a second group of clock pulses, an exact copy of what was received during the first group of clock pulses. The whole chain acts as one large communication shift register. The daisy-chain feature only requires a single Slave Select line from the master device.

Figure 21-7 shows the block diagram of a typical daisy-chain connection when operating in SPI mode.

In a daisy-chain configuration, only the most recent byte on the bus is required by the slave. Setting the BOEN bit of the SSPxCON3 register will enable writes to the SSPxBUF register, even if the previous byte has not been read. This allows the software to ignore data that may not apply to it.

## 21.2.5 SLAVE SELECT SYNCHRONIZATION

The Slave Select can also be used to synchronize communication. The Slave Select line is held high until the master device is ready to communicate. When the Slave Select line is pulled low, the slave knows that a new transmission is starting.

If the slave fails to receive the communication properly, it will be reset at the end of the transmission, when the Slave Select line returns to a high state. The slave is then ready to receive a new transmission when the Slave Select line is pulled low again. If the Slave Select line is not used, there is a risk that the slave will eventually become out of sync with the master. If the slave misses a bit, it will always be one bit off in future transmissions. Use of the Slave Select line allows the slave and master to align themselves at the beginning of each transmission.

The  $\overline{SSx}$  pin allows a Synchronous Slave mode. The SPI must be in Slave mode with  $\overline{SSx}$  pin control enabled (SSPxCON1<3:0> = 0100).

When the  $\overline{SSx}$  pin is low, transmission and reception are enabled and the SDOx pin is driven.

When the  $\overline{\text{SSx}}$  pin goes high, the SDOx pin is no longer driven, even if in the middle of a transmitted byte and becomes a floating output. External pull-up/pull-down resistors may be desirable depending on the application.

| Note 1: | When the SPI is in Slave mode with $\overline{SSx}$ pin control enabled (SSPxCON1<3:0> = 0100), the SPI module will reset if the $\overline{SSx}$ pin is set to VDD. |

|---------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 2:      | When the SPI is used in Slave mode with CKE set; the user must enable $\overline{SSx}$ pin control.                                                                  |

| 3:      | While operated in SPI Slave mode the SMP bit of the SSPxSTAT register must remain clear.                                                                             |

When the SPI module resets, the bit counter is forced to '0'. This can be done by either forcing the SSx pin to a high level or clearing the SSPEN bit.

# 21.4 I<sup>2</sup>C MODE OPERATION

All MSSP I<sup>2</sup>C communication is byte oriented and shifted out MSb first. Six SFR registers and two interrupt flags interface the module with the PIC<sup>®</sup> microcontroller and user software. Two pins, SDAx and SCLx, are exercised by the module to communicate with other external I<sup>2</sup>C devices.

#### 21.4.1 BYTE FORMAT

All communication in  $I^2C$  is done in 9-bit segments. A byte is sent from a master to a slave or vice-versa, followed by an Acknowledge bit sent back. After the eighth falling edge of the SCLx line, the device outputting data on the SDAx changes that pin to an input and reads in an acknowledge value on the next clock pulse.

The clock signal, SCLx, is provided by the master. Data is valid to change while the SCLx signal is low, and sampled on the rising edge of the clock. Changes on the SDAx line while the SCLx line is high define special conditions on the bus, explained below.

## 21.4.2 DEFINITION OF I<sup>2</sup>C TERMINOLOGY

There is language and terminology in the description of I<sup>2</sup>C communication that have definitions specific to I<sup>2</sup>C. That word usage is defined below and may be used in the rest of this document without explanation. This table was adapted from the Philips I<sup>2</sup>C<sup>TM</sup> specification.

## 21.4.3 SDAX AND SCLX PINS

Selection of any I<sup>2</sup>C mode with the SSPEN bit set, forces the SCLx and SDAx pins to be open-drain. These pins should be set by the user to inputs by setting the appropriate TRIS bits.

Note: Data is tied to output zero when an I<sup>2</sup>C mode is enabled.

#### 21.4.4 SDAX HOLD TIME

The hold time of the SDAx pin is selected by the SDAHT bit of the SSPxCON3 register. Hold time is the time SDAx is held valid after the falling edge of SCLx. Setting the SDAHT bit selects a longer 300 ns minimum hold time and may help on buses with large capacitance.

## TABLE 21-2: I<sup>2</sup>C BUS TERMS

| TADLE ZT-Z:         |                                                                                                                                                                                                  |

|---------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| TERM                | Description                                                                                                                                                                                      |

| Transmitter         | The device which shifts data out onto the bus.                                                                                                                                                   |

| Receiver            | The device which shifts data in from the bus.                                                                                                                                                    |

| Master              | The device that initiates a transfer, generates clock signals and termi-<br>nates a transfer.                                                                                                    |

| Slave               | The device addressed by the master.                                                                                                                                                              |

| Multi-master        | A bus with more than one device that can initiate data transfers.                                                                                                                                |

| Arbitration         | Procedure to ensure that only one master at a time controls the bus. Winning arbitration ensures that the message is not corrupted.                                                              |

| Synchronization     | Procedure to synchronize the clocks of two or more devices on the bus.                                                                                                                           |

| Idle                | No master is controlling the bus,<br>and both SDAx and SCLx lines are<br>high.                                                                                                                   |

| Active              | Any time one or more master devices are controlling the bus.                                                                                                                                     |

| Addressed<br>Slave  | Slave device that has received a matching address and is actively being clocked by a master.                                                                                                     |

| Matching<br>Address | Address byte that is clocked into a slave that matches the value stored in SSPxADD.                                                                                                              |

| Write Request       | Slave receives a matching address with R/W bit clear, and is ready to clock in data.                                                                                                             |

| Read Request        | Master sends an address byte with the $R/\overline{W}$ bit set, indicating that it wishes to clock data out of the Slave. This data is the next and all following bytes until a Restart or Stop. |

| Clock Stretching    | When a device on the bus hold SCLx low to stall communication.                                                                                                                                   |

| Bus Collision       | Any time the SDAx line is sampled<br>low by the module while it is out-<br>putting and expected high state.                                                                                      |

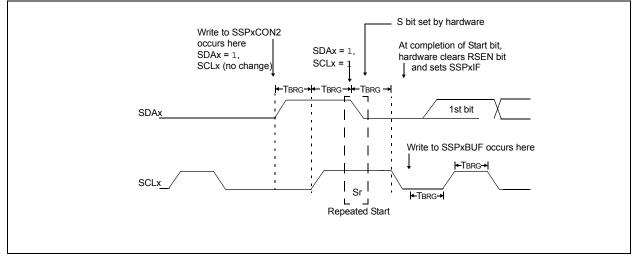

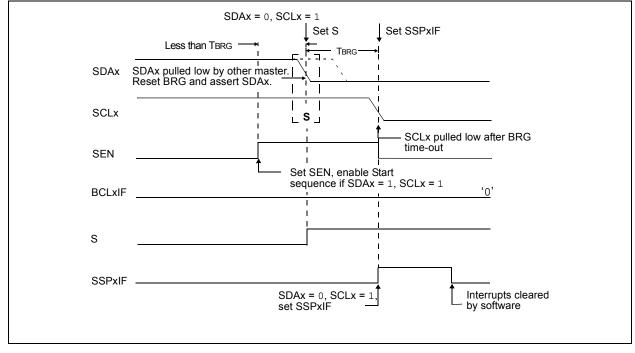

#### 21.6.5 I<sup>2</sup>C MASTER MODE REPEATED START CONDITION TIMING

A Repeated Start condition (Figure 21-27) occurs when the RSEN bit of the SSPxCON2 register is programmed high and the master state machine is no longer active. When the RSEN bit is set, the SCLx pin is asserted low. When the SCLx pin is sampled low, the Baud Rate Generator is loaded and begins counting. The SDAx pin is released (brought high) for one Baud Rate Generator count (TBRG). When the Baud Rate Generator times out, if SDAx is sampled high, the SCLx pin will be deasserted (brought high). When SCLx is sampled high, the Baud Rate Generator is reloaded and begins counting. SDAx and SCLx must be sampled high for one TBRG. This action is then followed by assertion of the SDAx pin (SDAx = 0) for one TBRG while SCLx is high. SCLx is asserted low. Following this, the RSEN bit of the SSPxCON2 register will be automatically cleared and the Baud Rate Generator will not be reloaded, leaving the SDAx pin held low. As soon as a Start condition is detected on the SDAx and SCLx pins, the S bit of the SSPxSTAT register will be set. The SSPxIF bit will not be set until the Baud Rate Generator has timed out.

- Note 1: If RSEN is programmed while any other event is in progress, it will not take effect.

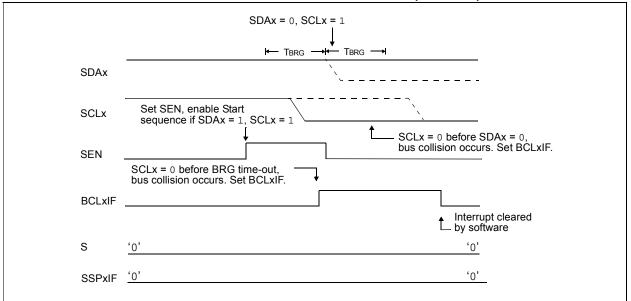

- **2:** A bus collision during the Repeated Start condition occurs if:

- SDAx is sampled low when SCLx goes from low-to-high.

- SCLx goes low before SDAx is asserted low. This may indicate that another master is attempting to transmit a data '1'.

#### FIGURE 21-27: REPEAT START CONDITION WAVEFORM

#### 21.6.6 I<sup>2</sup>C MASTER MODE TRANSMISSION

Transmission of a data byte, a 7-bit address or the other half of a 10-bit address is accomplished by simply writing a value to the SSPxBUF register. This action will set the Buffer Full flag bit, BF, and allow the Baud Rate Generator to begin counting and start the next transmission. Each bit of address/data will be shifted out onto the SDAx pin after the falling edge of SCLx is asserted. SCLx is held low for one Baud Rate Generator rollover count (TBRG). Data should be valid before SCLx is released high. When the SCLx pin is released high, it is held that way for TBRG. The data on the SDAx pin must remain stable for that duration and some hold time after the next falling edge of SCLx. After the eighth bit is shifted out (the falling edge of the eighth clock), the BF flag is cleared and the master releases SDAx. This allows the slave device being addressed to respond with an ACK bit during the ninth bit time if an address match occurred, or if data was received properly. The status of ACK is written into the ACKSTAT bit on the rising edge of the ninth clock. If the master receives an Acknowledge, the Acknowledge Status bit, ACKSTAT, is cleared. If not, the bit is set. After the ninth clock, the SSPxIF bit is set and the master clock (Baud Rate Generator) is suspended until the next data byte is loaded into the SSPxBUF, leaving SCLx low and SDAx unchanged (Figure 21-28).

After the write to the SSPxBUF, each bit of the address will be shifted out on the falling edge of SCLx until all seven address bits and the R/W bit are completed. On the falling edge of the eighth clock, the master will release the SDAx pin, allowing the slave to respond with an Acknowledge. On the falling edge of the ninth clock, the master will sample the SDAx pin to see if the address was recognized by a slave. The status of the ACK bit is loaded into the ACKSTAT Status bit of the SSPxCON2 register. Following the falling edge of the ninth clock transmission of the address, the SSPxIF is set, the BF flag is cleared and the Baud Rate Generator is turned off until another write to the SSPxBUF takes place, holding SCLx low and allowing SDAx to float.

#### 21.6.6.1 BF Status Flag

In Transmit mode, the BF bit of the SSPxSTAT register is set when the CPU writes to SSPxBUF and is cleared when all eight bits are shifted out.

### 21.6.6.2 WCOL Status Flag

If the user writes the SSPxBUF when a transmit is already in progress (i.e., SSPxSR is still shifting out a data byte), the WCOL bit is set and the contents of the buffer are unchanged (the write does not occur).

WCOL must be cleared by software before the next transmission.

### 21.6.6.3 ACKSTAT Status Flag

In Transmit mode, the ACKSTAT bit of the SSPxCON2 register is cleared when the slave has sent an Acknowledge ( $\overrightarrow{ACK} = 0$ ) and is set when the slave does not Acknowledge ( $\overrightarrow{ACK} = 1$ ). A slave sends an Acknowledge when it has recognized its address (including a general call), or when the slave has properly received its data.

21.6.6.4 Typical transmit sequence:

- 1. The user generates a Start condition by setting the SEN bit of the SSPxCON2 register.

- 2. SSPxIF is set by hardware on completion of the Start.

- 3. SSPxIF is cleared by software.

- 4. The MSSPx module will wait the required start time before any other operation takes place.

- 5. The user loads the SSPxBUF with the slave address to transmit.

- Address is shifted out the SDAx pin until all eight bits are transmitted. Transmission begins as soon as SSPxBUF is written to.

- 7. The MSSPx module shifts in the ACK bit from the slave device and writes its value into the ACKSTAT bit of the SSPxCON2 register.

- The MSSPx module generates an interrupt at the end of the ninth clock cycle by setting the SSPxIF bit.

- 9. The user loads the SSPxBUF with eight bits of data.

- 10. Data is shifted out the SDAx pin until all eight bits are transmitted.

- 11. The MSSPx module shifts in the ACK bit from the slave device and writes its value into the ACKSTAT bit of the SSPxCON2 register.

- 12. Steps 8-11 are repeated for all transmitted data bytes.

- 13. The user generates a Stop or Restart condition by setting the PEN or RSEN bits of the SSPxCON2 register. Interrupt is generated once the Stop/Restart condition is complete.

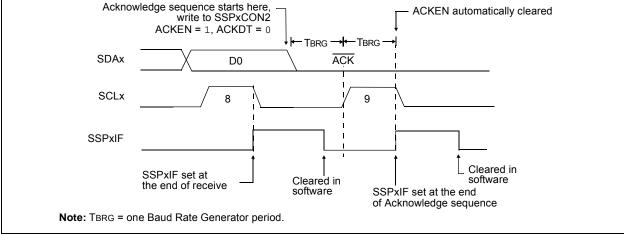

#### 21.6.8 ACKNOWLEDGE SEQUENCE TIMING

An Acknowledge sequence is enabled by setting the Acknowledge Sequence Enable bit, ACKEN bit of the SSPxCON2 register. When this bit is set, the SCLx pin is pulled low and the contents of the Acknowledge data bit are presented on the SDAx pin. If the user wishes to generate an Acknowledge, then the ACKDT bit should be cleared. If not, the user should set the ACKDT bit before starting an Acknowledge sequence. The Baud Rate Generator then counts for one rollover period (TBRG) and the SCLx pin is deasserted (pulled high). When the SCLx pin is sampled high (clock arbitration), the Baud Rate Generator counts for TBRG. The SCLx pin is then pulled low. Following this, the ACKEN bit is automatically cleared, the Baud Rate Generator is turned off and the MSSP module then goes into Idle mode (Figure 21-30).

### 21.6.8.1 WCOL Status Flag

If the user writes the SSPxBUF when an Acknowledge sequence is in progress, then the WCOL bit is set and the contents of the buffer are unchanged (the write does not occur).

### 21.6.9 STOP CONDITION TIMING

A Stop bit is asserted on the SDAx pin at the end of a receive/transmit by setting the Stop Sequence Enable bit, PEN bit of the SSPxCON2 register. At the end of a receive/transmit, the SCLx line is held low after the falling edge of the ninth clock. When the PEN bit is set, the master will assert the SDAx line low. When the SDAx line is sampled low, the Baud Rate Generator is reloaded and counts down to '0'. When the Baud Rate Generator times out, the SCLx pin will be brought high and one TBRG (Baud Rate Generator rollover count) later, the SDAx pin will be deasserted. When the SDAx pin is sampled high while SCLx is high, the P bit of the SSPxSTAT register is set. A TBRG later, the PEN bit is cleared and the SSPxIF bit is set (Figure 21-31).

#### 21.6.9.1 WCOL Status Flag

If the user writes the SSPxBUF when a Stop sequence is in progress, then the WCOL bit is set and the contents of the buffer are unchanged (the write does not occur).

## REGISTER 23-9: CLCDATA: CLC DATA OUTPUT

| U-0             | U-0                               | U-0               | U-0      | U-0                                                   | U-0                                | R-0     | R-0     |  |  |  |  |

|-----------------|-----------------------------------|-------------------|----------|-------------------------------------------------------|------------------------------------|---------|---------|--|--|--|--|

|                 | —                                 | —                 | _        | _                                                     | —                                  | MLC2OUT | MLC10UT |  |  |  |  |

| bit 7           |                                   |                   |          |                                                       |                                    |         | bit 0   |  |  |  |  |

| r               |                                   |                   |          |                                                       |                                    |         |         |  |  |  |  |

| Legend:         |                                   |                   |          |                                                       |                                    |         |         |  |  |  |  |

| R = Readabl     | R = Readable bit W = Writable bit |                   |          |                                                       | U = Unimplemented bit, read as '0' |         |         |  |  |  |  |

| u = Bit is und  | changed                           | x = Bit is unkn   | own      | -n/n = Value at POR and BOR/Value at all other Resets |                                    |         |         |  |  |  |  |

| '1' = Bit is se | et                                | '0' = Bit is clea | ared     |                                                       |                                    |         |         |  |  |  |  |

|                 |                                   |                   |          |                                                       |                                    |         |         |  |  |  |  |

| bit 7-2         | Unimplement                       | ed: Read as '0'   |          |                                                       |                                    |         |         |  |  |  |  |

| bit 1           | MLC2OUT: M                        | irror copy of LC  | 20UT bit |                                                       |                                    |         |         |  |  |  |  |

bit 0 MLC1OUT: Mirror copy of LC1OUT bit

#### TABLE 25-2: SUMMARY OF REGISTERS ASSOCIATED WITH CWG

| Name     | Bit 7 | Bit 6   | Bit 5                  | Bit 4  | Bit 3    | Bit 2       | Bit 1     | Bit 0      | Register<br>on Page |

|----------|-------|---------|------------------------|--------|----------|-------------|-----------|------------|---------------------|

| ANSELA   | _     | —       | -                      | ANSA4  | —        | ANSA2       | ANSA1     | ANSA0      | 99                  |

| CWG1CON0 | G1EN  | G10EB   | G10EA                  | G1POLB | G1POLA   |             |           | G1CS0      | 244                 |

| CWG1CON1 | G1ASD | LB<1:0> | G1ASDLA<1:0> G1IS<1:0> |        |          |             | 245       |            |                     |

| CWG1CON2 | G1ASE | G1ARSEN | _                      | —      | G1ASDSC2 | G1ASDSC1    | G1ASDSFLT | G1ASDSCLC2 | 246                 |

| CWG1DBF  | _     | _       |                        |        | CV       | VG1DBF<5:0> |           |            | 247                 |

| CWG1DBR  | _     | —       |                        |        | CV       | VG1DBR<5:0> |           |            | 247                 |

| TRISA    | _     | —       | TRISA5                 | TRISA4 | _(1)     | TRISA2      | TRISA1    | TRISA0     | 98                  |

| TRISC    | _     | _       | TRISC5                 | TRISC4 | TRISC3   | TRISC2      | TRISC1    | TRISC0     | 102                 |

Legend: x = unknown, u = unchanged, - = unimplemented locations read as '0'. Shaded cells are not used by CWG.

Note 1: Unimplemented, read as '1'.

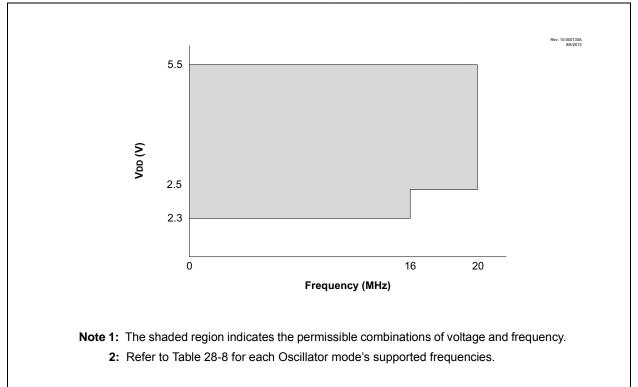

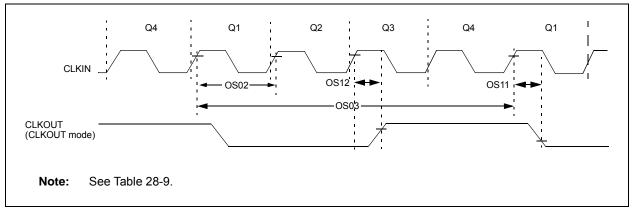

FIGURE 28-5: CLOCK TIMING

# TABLE 28-7: CLOCK OSCILLATOR TIMING REQUIREMENTS

| Param.<br>No. | Sym. | Characteristic                          | Min. | Тур† | Max.     | Units | Conditions           |  |  |

|---------------|------|-----------------------------------------|------|------|----------|-------|----------------------|--|--|

| OS01          | Fosc | External CLKIN Frequency <sup>(1)</sup> | DC   | —    | 0.5      | MHz   | External Clock (ECL) |  |  |

|               |      |                                         | DC   | —    | 4        | MHz   | External Clock (ECM) |  |  |

|               |      |                                         | DC   | —    | 20       | MHz   | External Clock (ECH) |  |  |

| OS02          | Tosc | External CLKIN Period <sup>(1)</sup>    | 50   | _    | $\infty$ | ns    | External Clock (EC)  |  |  |

| OS03          | Тсү  | Instruction Cycle Time <sup>(1)</sup>   | 200  | TCY  | DC       | ns    | Tcy = 4/Fosc         |  |  |

#### Standard Operating Conditions (unless otherwise stated)

\* These parameters are characterized but not tested.

† Data in "Typ" column is at 3.0V, 25°C unless otherwise stated. These parameters are for design guidance only and are not tested.

Note 1: Instruction cycle period (TCY) equals four times the input oscillator time base period. All specified values are based on characterization data for that particular oscillator type under standard operating conditions with the device executing code. Exceeding these specified limits may result in an unstable oscillator operation and/or higher than expected current consumption. All devices are tested to operate at "min" values with an external clock applied to CLKIN pin. When an external clock input is used, the "max" cycle time limit is "DC" (no clock) for all devices.

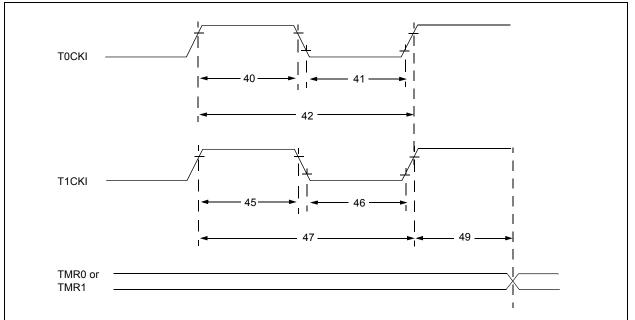

#### FIGURE 28-10: TIMER0 AND TIMER1 EXTERNAL CLOCK TIMINGS

| TABLE 28-11: | TIMER0 AND TIMER1 EXTERNAL CLOCK REQUIREMENTS |

|--------------|-----------------------------------------------|

|--------------|-----------------------------------------------|

| Standard Operating Conditions (unless otherwise stated) |           |                           |                             |                |                                           |      |        |       |                        |

|---------------------------------------------------------|-----------|---------------------------|-----------------------------|----------------|-------------------------------------------|------|--------|-------|------------------------|

| Param.<br>No.                                           | Sym.      |                           | Characteristi               | c              | Min.                                      | Тур† | Max.   | Units | Conditions             |

| 40*                                                     | T⊤0H      | T0CKI High F              | Pulse Width No Prescaler    |                | 0.5 Tcy + 20                              | _    |        | ns    |                        |

|                                                         |           |                           |                             | With Prescaler | 10                                        | _    | _      | ns    |                        |

| 41*                                                     | TT0L      | T0CKI Low F               | ulse Width                  | No Prescaler   | 0.5 Tcy + 20                              |      | _      | ns    |                        |

|                                                         |           |                           |                             | With Prescaler | 10                                        |      |        | ns    |                        |

| 42*                                                     | Тт0Р      | T0CKI Period              | 1                           |                | Greater of:<br>20 or <u>Tcy + 40</u><br>N | _    | _      | ns    | N = prescale value     |

| 45*                                                     | T⊤1H      | T1CKI High                | Synchronous, No Prescaler   |                | 0.5 Tcy + 20                              |      |        | ns    |                        |

|                                                         |           | Time                      | Synchronous, v              | with Prescaler | 15                                        | _    |        | ns    |                        |

|                                                         |           |                           | Asynchronous                |                | 30                                        |      |        | ns    |                        |

| 46*                                                     | TT1L      | T1CKI Low                 | Synchronous, N              | No Prescaler   | 0.5 Tcy + 20                              |      |        | ns    |                        |

|                                                         |           | Time                      | Synchronous, with Prescaler |                | 15                                        |      |        | ns    |                        |

|                                                         |           |                           | Asynchronous                |                | 30                                        |      |        | ns    |                        |

| 47*                                                     | TT1P      | T1CKI Input<br>Period     | Synchronous                 |                | Greater of:<br>30 or <u>Tcy + 40</u><br>N | —    | _      | ns    | N = prescale value     |

|                                                         |           |                           | Asynchronous                |                | 60                                        | _    | —      | ns    |                        |

| 49*                                                     | TCKEZTMR1 | Delay from E<br>Increment | xternal Clock Ed            | dge to Timer   | 2 Tosc                                    |      | 7 Tosc | —     | Timers in Sync<br>mode |

These parameters are characterized but not tested.

† Data in "Typ" column is at 3.0V, 25°C unless otherwise stated. These parameters are for design guidance only and are not tested.

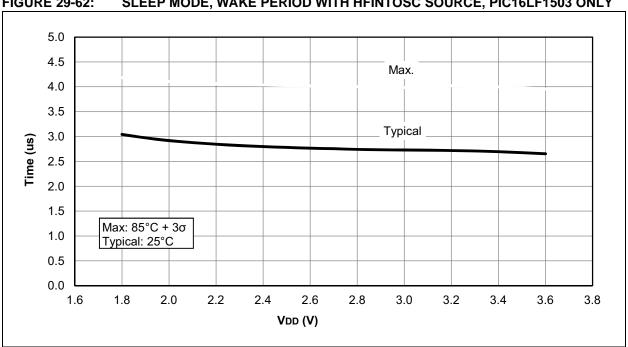

SLEEP MODE, WAKE PERIOD WITH HFINTOSC SOURCE, PIC16LF1503 ONLY FIGURE 29-62: