Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Product Status             | Active                                                                      |

|----------------------------|-----------------------------------------------------------------------------|

| Core Processor             | PIC                                                                         |

| Core Size                  | 8-Bit                                                                       |

| Speed                      | 20MHz                                                                       |

| Connectivity               | I <sup>2</sup> C, SPI                                                       |

| Peripherals                | Brown-out Detect/Reset, POR, PWM, WDT                                       |

| Number of I/O              | 11                                                                          |

| Program Memory Size        | 3.5KB (2K x 14)                                                             |

| Program Memory Type        | FLASH                                                                       |

| EEPROM Size                | -                                                                           |

| RAM Size                   | 128 x 8                                                                     |

| Voltage - Supply (Vcc/Vdd) | 1.8V ~ 3.6V                                                                 |

| Data Converters            | A/D 8x10b                                                                   |

| Oscillator Type            | Internal                                                                    |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                           |

| Mounting Type              | Surface Mount                                                               |

| Package / Case             | 16-UFQFN Exposed Pad                                                        |

| Supplier Device Package    | 16-UQFN (3x3)                                                               |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic16lf1503t-i-mv |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

#### 3.2.1.2 Indirect Read with FSR

The program memory can be accessed as data by setting bit 7 of the FSRxH register and reading the matching INDFx register. The MOVIW instruction will place the lower eight bits of the addressed word in the W register. Writes to the program memory cannot be performed via the INDF registers. Instructions that access the program memory via the FSR require one extra instruction cycle to complete. Example 3-2 demonstrates accessing the program memory via an FSR.

The HIGH operator will set bit<7> if a label points to a location in program memory.

| EXAMPLE 3-2: | ACCESSING PROGRAM |

|--------------|-------------------|

|              | MEMORY VIA FSR    |

| constants                |                    |

|--------------------------|--------------------|

| DW DATA0                 | ;First constant    |

| DW DATA1                 | ;Second constant   |

| DW DATA2                 |                    |

| DW DATA3                 |                    |

| my_function              |                    |

| ; LOTS OF CODE           |                    |

| MOVLW DATA_INDEX         |                    |

| ADDLW LOW constants      |                    |

| MOVWF FSR1L              |                    |

| MOVLW HIGH constants     | ;MSb sets          |

|                          | automatically      |

| MOVWF FSR1H              |                    |

| BTFSC STATUS, C          | ;carry from ADDLW? |

| INCF FSR1h, f            | ;yes               |

| MOVIW 0[FSR1]            |                    |

| ;THE PROGRAM MEMORY IS 1 | IN W               |

|                          |                    |

### 3.3 Data Memory Organization

The data memory is partitioned in 32 memory banks with 128 bytes in a bank. Each bank consists of (Figure 3-2):

- 12 core registers

- 20 Special Function Registers (SFR)

- Up to 80 bytes of General Purpose RAM (GPR)

- 16 bytes of common RAM

The active bank is selected by writing the bank number into the Bank Select Register (BSR). Unimplemented memory will read as '0'. All data memory can be accessed either directly (via instructions that use the file registers) or indirectly via the two File Select Registers (FSR). See **Section 3.6 "Indirect Addressing"** for more information.

Data memory uses a 12-bit address. The upper five bits of the address define the Bank address and the lower seven bits select the registers/RAM in that bank.

#### 3.3.1 CORE REGISTERS

The core registers contain the registers that directly affect the basic operation. The core registers occupy the first 12 addresses of every data memory bank (addresses x00h/x08h through x0Bh/x8Bh). These registers are listed below in Table 3-2. For detailed information, see Table 3-4.

| TABLE 3-2: | CORE REGISTERS |

|------------|----------------|

|            |                |

| Addresses    | BANKx  |

|--------------|--------|

| x00h or x80h | INDF0  |

| x01h or x81h | INDF1  |

| x02h or x82h | PCL    |

| x03h or x83h | STATUS |

| x04h or x84h | FSR0L  |

| x05h or x85h | FSR0H  |

| x06h or x86h | FSR1L  |

| x07h or x87h | FSR1H  |

| x08h or x88h | BSR    |

| x09h or x89h | WREG   |

| x0Ah or x8Ah | PCLATH |

| x0Bh or x8Bh | INTCON |

## TABLE 3-3: PIC16(L)F1503 MEMORY MAP (CONTINUED)

|              | BANK 24                               |              | BANK 25                               |              | BANK 26                               |              | BANK 27                               |              | BANK 28                               |              | BANK 29                               |              | BANK 30                               |              | BANK 31                               |

|--------------|---------------------------------------|--------------|---------------------------------------|--------------|---------------------------------------|--------------|---------------------------------------|--------------|---------------------------------------|--------------|---------------------------------------|--------------|---------------------------------------|--------------|---------------------------------------|

| C00h         | Core Registers<br>(Table 3-2)         | C80h         | Core Registers<br>(Table 3-2)         | D00h         | Core Registers<br>(Table 3-2)         | D80h         | Core Registers<br>(Table 3-2)         | E00h         | Core Registers<br>(Table 3-2)         | E80h         | Core Registers<br>(Table 3-2)         | F00h         | Core Registers<br>(Table 3-2)         | F80h         | Core Registers<br>(Table 3-2)         |

| C0Bh         |                                       | C8Bh         |                                       | D0Bh         |                                       | D8Bh         |                                       | E0Bh         |                                       | E8Bh         |                                       | F0Bh         |                                       | F8Bh         |                                       |

| C0Ch         | _                                     | C8Ch         | -                                     | D0Ch         | —                                     | D8Ch         | _                                     | E0Ch         | —                                     | E8Ch         | —                                     | F0Ch         |                                       | F8Ch         |                                       |

| C0Dh         | —                                     | C8Dh         | —                                     | D0Dh         | —                                     | D8Dh         | —                                     | E0Dh         | —                                     | E8Dh         |                                       | F0Dh         |                                       | F8Dh         |                                       |

| C0Eh         | —                                     | C8Eh         | _                                     | D0Eh         | —                                     | D8Eh         | —                                     | E0Eh         | _                                     | E8Eh         | _                                     | F0Eh         |                                       | F8Eh         |                                       |

| C0Fh         | —                                     | C8Fh         | —                                     | D0Fh         | —                                     | D8Fh         | —                                     | E0Fh         | —                                     | E8Fh         | —                                     | F0Fh         |                                       | F8Fh         |                                       |

| C10h         | —                                     | C90h         | _                                     | D10h         | —                                     | D90h         | —                                     | E10h         | _                                     | E90h         | _                                     | F10h         |                                       | F90h         |                                       |

| C11h         | _                                     | C91h         | —                                     | D11h         | —                                     | D91h         | _                                     | E11h         | —                                     | E91h         | _                                     | F11h         |                                       | F91h         |                                       |

| C12h         | _                                     | C92h         | —                                     | D12h         | —                                     | D92h         | _                                     | E12h         | —                                     | E92h         | —                                     | F12h         |                                       | F92h         |                                       |

| C13h         | _                                     | C93h         | —                                     | D13h         | —                                     | D93h         | _                                     | E13h         | —                                     | E93h         | —                                     | F13h         |                                       | F93h         |                                       |

| C14h         | _                                     | C94h         | —                                     | D14h         | _                                     | D94h         | _                                     | E14h         | —                                     | E94h         | —                                     | F14h         |                                       | F94h         |                                       |

| C15h         | _                                     | C95h         | —                                     | D15h         | _                                     | D95h         | _                                     | E15h         | —                                     | E95h         |                                       | F15h         |                                       | F95h         |                                       |

| C16h         | _                                     | C96h         | —                                     | D16h         | —                                     | D96h         | _                                     | E16h         | —                                     | E96h         | —                                     | F16h         |                                       | F96h         |                                       |

| C17h         | _                                     | C97h         | —                                     | D17h         | —                                     | D97h         | _                                     | E17h         | —                                     | E97h         | —                                     | F17h         | See Table 3-3 for                     | F97h         | See Table 3-3 for                     |

| C18h         | —                                     | C98h         | —                                     | D18h         | —                                     | D98h         | _                                     | E18h         | —                                     | E98h         |                                       | F18h         | register mapping                      | F98h         | register mapping                      |

| C19h         | —                                     | C99h         | —                                     | D19h         | _                                     | D99h         | _                                     | E19h         | —                                     | E99h         | _                                     | F19h         | details                               | F99h         | details                               |

| C1Ah         | —                                     | C9Ah         | —                                     | D1Ah         | —                                     | D9Ah         | _                                     | E1Ah         | —                                     | E9Ah         | —                                     | F1Ah         |                                       | F9Ah         |                                       |

| C1Bh         | _                                     | C9Bh         | —                                     | D1Bh         | _                                     | D9Bh         | _                                     | E1Bh         | —                                     | E9Bh         |                                       | F1Bh         |                                       | F9Bh         |                                       |

| C1Ch         | —                                     | C9Ch         | —                                     | D1Ch         | —                                     | D9Ch         | _                                     | E1Ch         | —                                     | E9Ch         | —                                     | F1Ch         |                                       | F9Ch         |                                       |

| C1Dh         | —                                     | C9Dh         | —                                     | D1Dh         | _                                     | D9Dh         | _                                     | E1Dh         | —                                     | E9Dh         | _                                     | F1Dh         |                                       | F9Dh         |                                       |

| C1Eh         | —                                     | C9Eh         | —                                     | D1Eh         | —                                     | D9Eh         | _                                     | E1Eh         | —                                     | E9Eh         | —                                     | F1Eh         |                                       | F9Eh         |                                       |

| C1Fh         | —                                     | C9Fh         | —                                     | D1Fh         | —                                     | D9Fh         | _                                     | E1Fh         | —                                     | E9Fh         | —                                     | F1Fh         |                                       | F9Fh         |                                       |

| C20h         |                                       | CA0h         |                                       | D20h         |                                       | DA0h         |                                       | E20h         |                                       | EA0h         |                                       | F20h         |                                       | FA0h         |                                       |

|              | Unimplemented<br>Read as '0'          |              |                                       |              |                                       |

| C6Fh         |                                       | CEFh         |                                       | D6Fh         |                                       | DEFh         |                                       | E6Fh         |                                       | EEFh         |                                       | F6Fh         |                                       | FEFh         |                                       |

| C70h<br>CFFh | Common RAM<br>(Accesses<br>70h – 7Fh) | CF0h<br>CFFh | Common RAM<br>(Accesses<br>70h – 7Fh) | D70h<br>D7Fh | Common RAM<br>(Accesses<br>70h – 7Fh) | DF0h<br>DFFh | Common RAM<br>(Accesses<br>70h – 7Fh) | E70h<br>E7Fh | Common RAM<br>(Accesses<br>70h – 7Fh) | EF0h<br>EFFh | Common RAM<br>(Accesses<br>70h – 7Fh) | F70h<br>F7Fh | Common RAM<br>(Accesses<br>70h – 7Fh) | FF0h<br>FFFh | Common RAM<br>(Accesses<br>70h – 7Fh) |

Legend: = Unimplemented data memory locations, read as '0'.

#### **TABLE 3-5:** SPECIAL FUNCTION REGISTER SUMMARY (CONTINUED)

| Address            | Name     | Bit 7      | Bit 6       | Bit 5  | Bit 4  | Bit 3     | Bit 2  | Bit 1   | Bit 0  | Value on<br>POR, BOR | Value on all<br>other<br>Resets |

|--------------------|----------|------------|-------------|--------|--------|-----------|--------|---------|--------|----------------------|---------------------------------|

| Bank 4             |          | •          |             | •      |        |           |        | •       | •      | •                    | •                               |

| 20Ch               | WPUA     | —          | —           | WPUA5  | WPUA4  | WPUA3     | WPUA2  | WPUA1   | WPUA0  | 11 1111              | 11 1111                         |

| 20Dh<br>to<br>212h | _        | Unimplemen | implemented |        |        |           |        |         |        |                      | _                               |

| 213h               | SSP1MSK  |            |             |        | MS     | K<7:0>    |        |         |        | 1111 1111            | 1111 1111                       |

| 214h               | SSP1STAT | SMP        | CKE         | D/A    | Р      | S         | R/W    | UA      | BF     | 0000 0000            | 0000 0000                       |

| 215h               | SSP1CON1 | WCOL       | SSPOV       | SSPEN  | CKP    |           | SSF    | PM<3:0> |        | 0000 0000            | 0000 0000                       |

| 216h               | SSP1CON2 | GCEN       | ACKSTAT     | ACKDT  | ACKEN  | RCEN      | PEN    | RSEN    | SEN    | 0000 0000            | 0000 0000                       |

| 217h               | SSP1CON3 | ACKTIM     | PCIE        | SCIE   | BOEN   | SDAHT     | SBCDE  | AHEN    | DHEN   | 0000 0000            | 0000 0000                       |

| 218h<br>to<br>21Fh | _        | Unimplemen | ted         |        |        |           |        |         |        | -                    | _                               |

| Bank 5             |          |            |             |        |        |           |        |         |        |                      |                                 |

| 28Ch<br>to<br>29Fh | _        | Unimplemen | ted         |        |        |           |        |         |        | -                    | _                               |

| Bank 6             |          |            |             |        |        |           |        |         |        |                      |                                 |

| 30Ch<br>to<br>31Fh | _        | Unimplemen | ted         |        |        |           |        |         |        | -                    | _                               |

| Bank 7             |          |            |             |        |        |           |        |         |        |                      |                                 |

| 38Ch<br>to<br>390h | _        | Unimplemen | ted         |        |        |           |        |         |        | -                    | _                               |

| 391h               | IOCAP    | —          | —           | IOCAP5 | IOCAP4 | IOCAP3    | IOCAP2 | IOCAP1  | IOCAP0 | 00 0000              | 00 0000                         |

| 392h               | IOCAN    | —          | —           | IOCAN5 | IOCAN4 | IOCAN3    | IOCAN2 | IOCAN1  | IOCAN0 | 00 0000              | 00 0000                         |

| 393h               | IOCAF    | —          | _           | IOCAF5 | IOCAF4 | IOCAF3    | IOCAF2 | IOCAF1  | IOCAF0 | 00 0000              | 00 0000                         |

| 394h<br>to<br>39Fh | _        | Unimplemen | ted         |        |        |           |        |         |        | -                    | _                               |

| Bank 8             |          | _          |             |        |        |           |        |         |        |                      |                                 |

| 40Ch<br>to<br>41Fh | _        | Unimplemen | ted         |        |        |           |        |         |        | -                    | -                               |

| Bank 9             |          |            |             |        |        |           |        |         |        |                      |                                 |

| 48Ch<br>to<br>497h | _        | Unimplemen | ted         |        |        |           |        |         |        | -                    | _                               |

| 498h               | NCO1ACCL |            |             |        | NCO1/  | ACC<7:0>  |        |         |        | 0000 0000            | 0000 0000                       |

| 499h               | NCO1ACCH |            |             |        |        |           |        |         |        | 0000 0000            | 0000 0000                       |

| 49Ah               | NCO1ACCU |            |             |        | NCO1A  | CC<19:16> |        |         |        | 0000 0000            | 0000 0000                       |

| 49Bh               | NCO1INCL |            |             |        |        |           |        |         |        | 0000 0001            |                                 |

| 49Ch               | NCO1INCH |            |             |        | NCO1I  | NC<15:8>  |        |         |        | 0000 0000            | 0000 0000                       |

| 49Dh               | —        | Unimplemen | ted         |        |        |           |        |         |        | _                    | _                               |

| 49Eh               | NCO1CON  | N1EN       | N1OE        | N1OUT  | N1POL  | _         | _      | _       | N1PFM  | 00000                | 00000                           |

|                    |          |            |             | •      | 1      |           |        |         |        |                      | 1                               |

Legend:

x = unknown, u = unchanged, g = value depends on condition, - = unimplemented, r = reserved. Shaded locations are unimplemented, read as '0'.

Note

1:

PIC16F1503 only.

2:

Unimplemented, read as '1'.

| W-0/0            | W-0/0    | W-0/0             | W-0/0      | W-0/0           | W-0/0            | W-0/0            | W-0/0       |

|------------------|----------|-------------------|------------|-----------------|------------------|------------------|-------------|

|                  |          | Prog              | ram Memory | / Control Regis | ter 2            |                  |             |

| bit 7            |          |                   |            |                 |                  |                  | bit 0       |

|                  |          |                   |            |                 |                  |                  |             |

| Legend:          |          |                   |            |                 |                  |                  |             |

| R = Readable     | bit      | W = Writable b    | oit        | U = Unimple     | mented bit, read | 1 as '0'         |             |

| S = Bit can onl  | y be set | x = Bit is unkn   | own        | -n/n = Value    | at POR and BO    | R/Value at all c | ther Resets |

| '1' = Bit is set |          | '0' = Bit is clea | ared       |                 |                  |                  |             |

## REGISTER 10-6: PMCON2: PROGRAM MEMORY CONTROL 2 REGISTER

#### bit 7-0 Flash Memory Unlock Pattern bits

To unlock writes, a 55h must be written first, followed by an AAh, before setting the WR bit of the PMCON1 register. The value written to this register is used to unlock the writes. There are specific timing requirements on these writes.

#### TABLE 10-3: SUMMARY OF REGISTERS ASSOCIATED WITH FLASH PROGRAM MEMORY

| Name   | Bit 7                             | Bit 6           | Bit 5  | Bit 4 | Bit 3     | Bit 2  | Bit 1 | Bit 0 | Register on<br>Page |

|--------|-----------------------------------|-----------------|--------|-------|-----------|--------|-------|-------|---------------------|

| INTCON | GIE                               | PEIE            | TMR0IE | INTE  | IOCIE     | TMR0IF | INTF  | IOCIF | 64                  |

| PMCON1 | _(1)                              | CFGS            | LWLO   | FREE  | WRERR     | WREN   | WR    | RD    | 93                  |

| PMCON2 | Program Memory Control Register 2 |                 |        |       |           |        |       |       | 94                  |

| PMADRL |                                   |                 |        | PMAD  | RL<7:0>   |        |       |       | 92                  |

| PMADRH | _(1)                              |                 |        | F     | MADRH<6:0 | >      |       |       | 92                  |

| PMDATL | PMDATL<7:0>                       |                 |        |       |           |        |       | 92    |                     |

| PMDATH | —                                 | — — PMDATH<5:0> |        |       |           |        |       |       | 92                  |

Legend: — = unimplemented location, read as '0'. Shaded cells are not used by Flash program memory.

**Note 1:** Unimplemented, read as '1'.

#### TABLE 10-4: SUMMARY OF CONFIGURATION WORD WITH RESETS

| Name    | Bits | Bit -/7 | Bit -/6 | Bit 13/5 | Bit 12/4   | Bit 11/3 | Bit 10/2            | Bit 9/1   | Bit 8/0 | Register<br>on Page |

|---------|------|---------|---------|----------|------------|----------|---------------------|-----------|---------|---------------------|

|         | 13:8 |         | _       | _        | - CLKOUTEN |          | KOUTEN BOREN<1:0> — |           | _       | 20                  |

| CONFIG1 | 7:0  | CP      | MCLRE   | PWRTE    | WE         | )TE<1:0> | —                   | FOSC<1:0> |         | 38                  |

|         | 13:8 | _       | _       | LVP      | DEBUG      | LPBOR    | BORV                | STVREN    | _       |                     |

| CONFIG2 | 7:0  | _       | _       | _        | _          | _        | _                   | WRT       | <1:0>   | 39                  |

**Legend:** — = unimplemented location, read as '0'. Shaded cells are not used by Resets.

| Name   | Bit 7      | Bit 6        | Bit 5     | Bit 4    | Bit 3  | Bit 2   | Bit 1   | Bit 0  | Register<br>on Page |

|--------|------------|--------------|-----------|----------|--------|---------|---------|--------|---------------------|

| ADCON0 |            |              |           | CHS<4:0> |        |         | GO/DONE | ADON   | 119                 |

| ADCON1 | ADFM       |              | ADCS<2:0> |          | —      | —       | ADPRE   | F<1:0> | 120                 |

| ADCON2 |            | TRIGSE       | EL<3:0>   |          | —      | —       | _       | _      | 121                 |

| ADRESH | ADC Result | Register Hig | h         |          |        |         |         |        | 122, 123            |

| ADRESL | ADC Result | Register Lov | v         |          |        |         |         |        | 122, 123            |

| ANSELA | _          | _            | -         | ANSA4    | —      | ANSA2   | ANSA1   | ANSA0  | 99                  |

| ANSELC | _          | _            | -         | —        | ANSC3  | ANSC2   | ANSC1   | ANSC0  | 103                 |

| INTCON | GIE        | PEIE         | TMR0IE    | INTE     | IOCIE  | TMR0IF  | INTF    | IOCIF  | 64                  |

| PIE1   | TMR1GIE    | ADIE         | _         | —        | SSP1IE | —       | TMR2IE  | TMR1IE | 65                  |

| PIR1   | TMR1GIF    | ADIF         | -         | —        | SSP1IF | —       | TMR2IF  | TMR1IF | 68                  |

| TRISA  |            | _            | TRISA5    | TRISA4   | —(1)   | TRISA2  | TRISA1  | TRISA0 | 98                  |

| TRISC  |            | _            | TRISC5    | TRISC4   | TRISC3 | TRISC2  | TRISC1  | TRISC0 | 102                 |

| FVRCON | FVREN      | FVRRDY       | TSEN      | TSRNG    | CDAFV  | /R<1:0> | ADFVF   | २<1:0> | 110                 |

#### TABLE 15-3: SUMMARY OF REGISTERS ASSOCIATED WITH ADC

Legend: x = unknown, u = unchanged, - = unimplemented read as '0', q = value depends on condition. Shaded cells are not used for ADC module.

Note 1: Unimplemented, read as '1'.

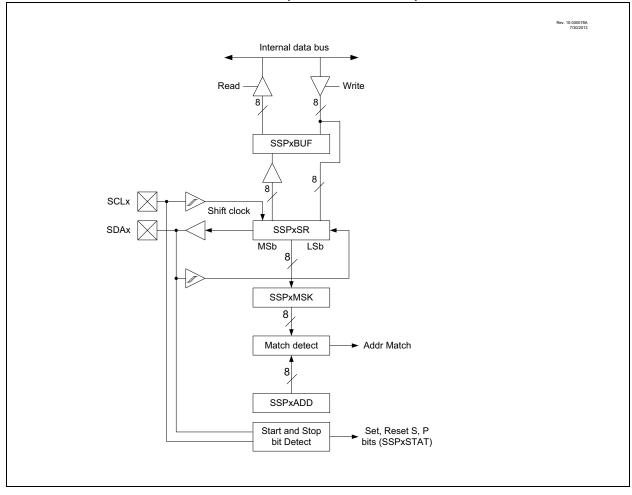

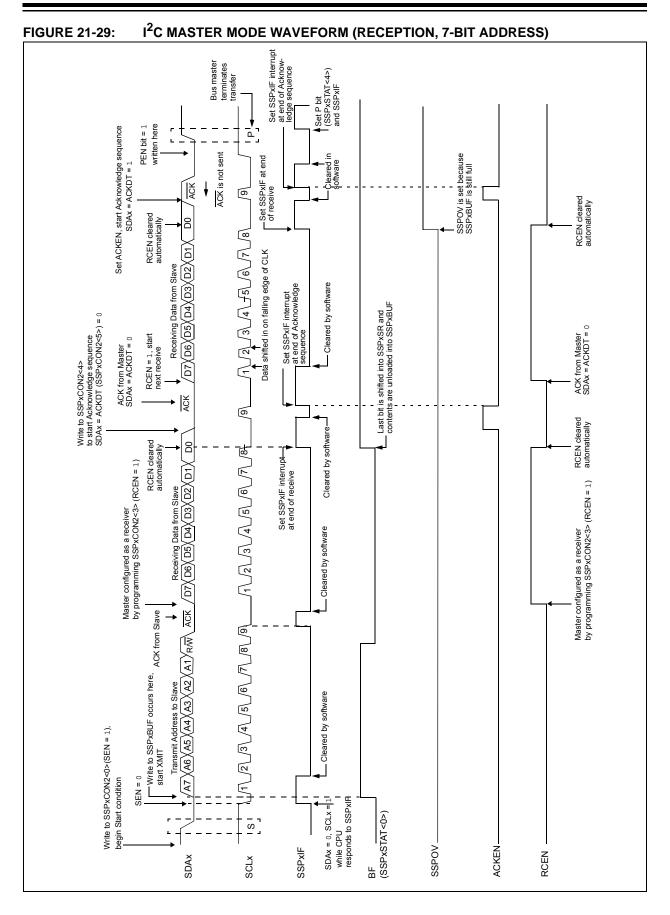

The  $I^2C$  interface supports the following modes and features:

- Master mode

- Slave mode

- Byte NACKing (Slave mode)

- · Limited Multi-master support

- · 7-bit and 10-bit addressing

- Start and Stop interrupts

- · Interrupt masking

- Clock stretching

- · Bus collision detection

- General call address matching

- · Address masking

- Address Hold and Data Hold modes

- Selectable SDAx hold times

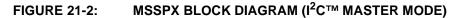

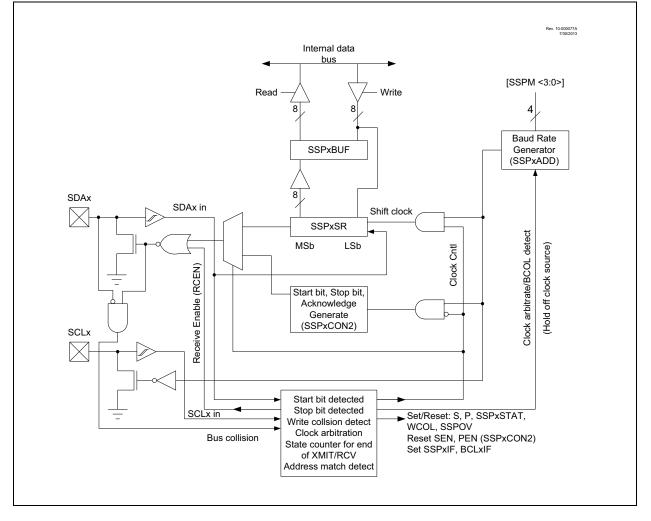

Figure 21-2 is a block diagram of the  $I^2C$  interface module in Master mode. Figure 21-3 is a diagram of the  $I^2C$  interface module in Slave mode.

Note 1: In devices with more than one MSSP module, it is very important to pay close attention to SSPxCONx register names. SSPxCON1 and SSPxCON2 registers control different operational aspects of the same module, while SSPxCON1 and SSP2CON1 control the same features for two different modules.

2: Throughout this section, generic references to an MSSPx module in any of its operating modes may be interpreted as being equally applicable to MSSPx or MSSP2. Register names, module I/O signals, and bit names may use the generic designator 'x' to indicate the use of a numeral to distinguish a particular module when required.

# FIGURE 21-3: MSSP BLOCK DIAGRAM (I<sup>2</sup>C<sup>™</sup> SLAVE MODE)

#### 21.2.4 SPI SLAVE MODE

In Slave mode, the data is transmitted and received as external clock pulses appear on SCKx. When the last bit is latched, the SSPxIF interrupt flag bit is set.

Before enabling the module in SPI Slave mode, the clock line must match the proper Idle state. The clock line can be observed by reading the SCKx pin. The Idle state is determined by the CKP bit of the SSPxCON1 register.

While in Slave mode, the external clock is supplied by the external clock source on the SCKx pin. This external clock must meet the minimum high and low times as specified in the electrical specifications.

While in Sleep mode, the slave can transmit/receive data. The shift register is clocked from the SCKx pin input and when a byte is received, the device will generate an interrupt. If enabled, the device will wake-up from Sleep.

#### 21.2.4.1 Daisy-Chain Configuration

The SPI bus can sometimes be connected in a daisy-chain configuration. The first slave output is connected to the second slave input, the second slave output is connected to the third slave input, and so on. The final slave output is connected to the master input. Each slave sends out, during a second group of clock pulses, an exact copy of what was received during the first group of clock pulses. The whole chain acts as one large communication shift register. The daisy-chain feature only requires a single Slave Select line from the master device.

Figure 21-7 shows the block diagram of a typical daisy-chain connection when operating in SPI mode.

In a daisy-chain configuration, only the most recent byte on the bus is required by the slave. Setting the BOEN bit of the SSPxCON3 register will enable writes to the SSPxBUF register, even if the previous byte has not been read. This allows the software to ignore data that may not apply to it.

### 21.2.5 SLAVE SELECT SYNCHRONIZATION

The Slave Select can also be used to synchronize communication. The Slave Select line is held high until the master device is ready to communicate. When the Slave Select line is pulled low, the slave knows that a new transmission is starting.

If the slave fails to receive the communication properly, it will be reset at the end of the transmission, when the Slave Select line returns to a high state. The slave is then ready to receive a new transmission when the Slave Select line is pulled low again. If the Slave Select line is not used, there is a risk that the slave will eventually become out of sync with the master. If the slave misses a bit, it will always be one bit off in future transmissions. Use of the Slave Select line allows the slave and master to align themselves at the beginning of each transmission.

The  $\overline{SSx}$  pin allows a Synchronous Slave mode. The SPI must be in Slave mode with  $\overline{SSx}$  pin control enabled (SSPxCON1<3:0> = 0100).

When the  $\overline{SSx}$  pin is low, transmission and reception are enabled and the SDOx pin is driven.

When the  $\overline{\text{SSx}}$  pin goes high, the SDOx pin is no longer driven, even if in the middle of a transmitted byte and becomes a floating output. External pull-up/pull-down resistors may be desirable depending on the application.

| Note 1: | When the SPI is in Slave mode with $\overline{SSx}$ pin control enabled (SSPxCON1<3:0> = 0100), the SPI module will reset if the $\overline{SSx}$ pin is set to VDD. |

|---------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 2:      | When the SPI is used in Slave mode with CKE set; the user must enable $\overline{SSx}$ pin control.                                                                  |

| 3:      | While operated in SPI Slave mode the SMP bit of the SSPxSTAT register must remain clear.                                                                             |

When the SPI module resets, the bit counter is forced to '0'. This can be done by either forcing the SSx pin to a high level or clearing the SSPEN bit.

#### 21.5.3.3 7-bit Transmission with Address Hold Enabled

Setting the AHEN bit of the SSPxCON3 register enables additional clock stretching and interrupt generation after the eighth falling edge of a received matching address. Once a matching address has been clocked in, CKP is cleared and the SSPxIF interrupt is set.

Figure 21-19 displays a standard waveform of a 7-bit Address Slave Transmission with AHEN enabled.

- 1. Bus starts idle.

- Master sends Start condition; the S bit of SSPxSTAT is set; SSPxIF is set if interrupt on Start detect is enabled.

- Master sends matching address with R/W bit set. After the eighth falling edge of the SCLx line the CKP bit is cleared and SSPxIF interrupt is generated.

- 4. Slave software clears SSPxIF.

- 5. Slave software reads ACKTIM bit of SSPxCON3 register, and  $R/\overline{W}$  and  $D/\overline{A}$  of the SSPxSTAT register to determine the source of the interrupt.

- 6. Slave reads the address value from the SSPxBUF register clearing the BF bit.

- Slave software decides from this information if it wishes to ACK or not ACK and sets the ACKDT bit of the SSPxCON2 register accordingly.

- 8. Slave sets the CKP bit releasing SCLx.

- 9. Master clocks in the  $\overline{ACK}$  value from the slave.

- 10. Slave hardware automatically clears the CKP bit and sets SSPxIF after the ACK if the R/W bit is set.

- 11. Slave software clears SSPxIF.

- 12. Slave loads value to transmit to the master into SSPxBUF setting the BF bit.

Note: SSPxBUF cannot be loaded until after the ACK.

- 13. Slave sets the CKP bit, releasing the clock.

- 14. Master clocks out the data from the slave and sends an ACK value on the ninth SCLx pulse.

- 15. Slave hardware copies the ACK value into the ACKSTAT bit of the SSPxCON2 register.

- 16. Steps 10-15 are repeated for each byte transmitted to the master from the slave.

- 17. If the master sends a not ACK the slave releases the bus allowing the master to send a Stop and end the communication.

**Note:** Master must send a not ACK on the last byte to ensure that the slave releases the SCLx line to receive a Stop.

### REGISTER 21-2: SSPxCON1: SSP CONTROL REGISTER 1

| R/C/HS-0/0        | R/C/HS-0/0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | R/W-0/0                                                                                                                                               | R/W-0/0                                                                                                                                                                                     | R/W-0/0                                                                                  | R/W-0/0              | R/W-0/0                                     | R/W-0/0         |

|-------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------|----------------------|---------------------------------------------|-----------------|

| WCOL              | SSPOV <sup>(1)</sup>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | SSPEN                                                                                                                                                 | CKP                                                                                                                                                                                         |                                                                                          | SSPI                 | M<3:0>                                      |                 |

| bit 7             | •                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | ·                                                                                                                                                     |                                                                                                                                                                                             | ·                                                                                        |                      |                                             | bit             |

|                   |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |                                                                                                                                                       |                                                                                                                                                                                             |                                                                                          |                      |                                             |                 |

| Legend:           |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |                                                                                                                                                       |                                                                                                                                                                                             |                                                                                          |                      |                                             |                 |

| R = Readable bi   | t                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | W = Writable bit                                                                                                                                      |                                                                                                                                                                                             | U = Unimplement                                                                          | ted bit, read as '0' |                                             |                 |

| u = Bit is unchar | nged                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | x = Bit is unknow                                                                                                                                     | 'n                                                                                                                                                                                          | -n/n = Value at Po                                                                       | OR and BOR/Value     | e at all other Resets                       |                 |

| '1' = Bit is set  |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | '0' = Bit is cleared                                                                                                                                  | d                                                                                                                                                                                           | HS = Bit is set by                                                                       | hardware             | C = User cleared                            |                 |

| bit 7             | 0 = No collisior<br>Slave mode:                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | he SSPxBUF regist<br>ו<br>UF register is writter                                                                                                      | ·                                                                                                                                                                                           | d while the I <sup>2</sup> C condi<br>smitting the previous                              |                      |                                             | to be started   |

| bit 6             | <ul> <li>SSPOV: Receive Overflow Indicator bit<sup>(1)</sup>         In SPI mode:         <ul> <li>I = A new byte is received while the SSPxBUF register is still holding the previous data. In case of overflow, the data in SSPxSR is Overflow can only occur in Slave mode. In Slave mode, the user must read the SSPxBUF, even if only transmitting data, to setting overflow. In Master mode, the overflow bit is not set since each new reception (and transmission) is initiated by writing SSPxBUF register (must be cleared in software).</li> <li>O = No overflow</li> <li>In I<sup>2</sup>C mode:</li> <li>I = A byte is received while the SSPxBUF register is still holding the previous byte. SSPOV is a "don't care" in Transmit (must be cleared in software).</li> <li>No overflow</li> </ul> </li> </ul> |                                                                                                                                                       |                                                                                                                                                                                             |                                                                                          |                      | ting data, to avoid<br>ed by writing to the |                 |

| bit 5             | In both modes, w<br>In <u>SPI mode:</u><br>1 = Enables set<br>0 = Disables set<br>In I <sup>2</sup> C mode:<br>1 = Enables the                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | rial port and configu<br>erial port and config                                                                                                        | e pins must be pr<br>res SCKx, SDOx,<br>jures these pins<br>igures the SDAx a                                                                                                               | and SCLx pins as the                                                                     | source of the seria  |                                             |                 |

| bit 4             | 0 = Idle state for<br>In I <sup>2</sup> C Slave mod<br>SCLx release co<br>1 = Enable clock                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | clock is a high leve<br>clock is a low level<br>le:<br>ntrol<br>ow (clock stretch).                                                                   |                                                                                                                                                                                             | data setup time.)                                                                        |                      |                                             |                 |

| bit 3-0           | 0000 = SPI Mas<br>0001 = SPI Mas<br>0010 = SPI Mas<br>0010 = SPI Mas<br>0100 = SPI Slav<br>0101 = SPI Slav<br>0110 = I <sup>2</sup> C Slave<br>0110 = I <sup>2</sup> C Slave<br>1000 = I <sup>2</sup> C Mast<br>1001 = Reservee<br>1010 = SPI Mas<br>1011 = I <sup>2</sup> C firmw<br>1100 = Reservee<br>1101 = Reservee<br>1101 = Reservee<br>1101 = Reservee<br>1100 = Reservee                                                                                                                                                                                                                                                                                                                                                                                                                                          | e mode, 7-bit addre<br>e mode, 10-bit addr<br>er mode, clock = Fr<br>d<br>ter mode, clock = F<br>vare controlled Mas<br>d<br>d<br>e mode, 7-bit addre | osc/4<br>osc/16<br>osc/64<br>2_match/2<br>XKx pin, <u>SS</u> pin c<br>SKx pin, <u>SS</u> pin c<br>ss<br>ess<br>osc/(4 * (SSPxAl<br>osc/(4 * (SSPxAl<br>ter mode (Slave<br>ss with Start and | ontrol enabled<br>ontrol disabled, SSx<br>DD+1)) <sup>(4)</sup><br>DD+1)) <sup>(5)</sup> | nabled               | ) pin                                       |                 |

| 2: W<br>3: W      | Master mode, the ov<br>hen enabled, these p<br>hen enabled, the SD/<br>SPXADD values of 0,                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | erflow bit is not set<br>ins must be proper<br>Ax and SCLx pins r                                                                                     | since each new<br>ly configured as i<br>nust be configure                                                                                                                                   | reception (and transi<br>input or output.<br>ed as inputs.                               |                      | l by writing to the SS                      | PxBUF register. |

- SSPxADD values of 0, 1 or 2 are not supported for I<sup>2</sup>C mode.

SSPxADD value of '0' is not supported. Use SSPM = 0000 instead.

# 27.0 INSTRUCTION SET SUMMARY

Each instruction is a 14-bit word containing the operation code (opcode) and all required operands. The opcodes are broken into three broad categories.

- Byte Oriented

- · Bit Oriented

- · Literal and Control

The literal and control category contains the most varied instruction word format.

Table 27-3 lists the instructions recognized by the MPASM  $^{\rm TM}$  assembler.

All instructions are executed within a single instruction cycle, with the following exceptions, which may take two or three cycles:

- Subroutine takes two cycles (CALL, CALLW)

- Returns from interrupts or subroutines take two cycles (RETURN, RETLW, RETFIE)

- Program branching takes two cycles (GOTO, BRA, BRW, BTFSS, BTFSC, DECFSZ, INCSFZ)

- One additional instruction cycle will be used when any instruction references an indirect file register and the file select register is pointing to program memory.

One instruction cycle consists of 4 oscillator cycles; for an oscillator frequency of 4 MHz, this gives a nominal instruction execution rate of 1 MHz.

All instruction examples use the format '0xhh' to represent a hexadecimal number, where 'h' signifies a hexadecimal digit.

## 27.1 Read-Modify-Write Operations

Any instruction that specifies a file register as part of the instruction performs a Read-Modify-Write (R-M-W) operation. The register is read, the data is modified, and the result is stored according to either the instruction, or the destination designator 'd'. A read operation is performed on a register even if the instruction writes to that register.

| DESCRIPTIONS |                                                                                                                                                                                   |  |  |  |  |

|--------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|

| Field        | Description                                                                                                                                                                       |  |  |  |  |

| f            | Register file address (0x00 to 0x7F)                                                                                                                                              |  |  |  |  |

| W            | Working register (accumulator)                                                                                                                                                    |  |  |  |  |

| b            | Bit address within an 8-bit file register                                                                                                                                         |  |  |  |  |

| k            | Literal field, constant data or label                                                                                                                                             |  |  |  |  |

| x            | Don't care location (= $0$ or 1).<br>The assembler will generate code with x = $0$ .<br>It is the recommended form of use for<br>compatibility with all Microchip software tools. |  |  |  |  |

| d            | Destination select; d = 0: store result in W,<br>d = 1: store result in file register f.<br>Default is d = 1.                                                                     |  |  |  |  |

| n            | FSR or INDF number. (0-1)                                                                                                                                                         |  |  |  |  |

| mm           | Pre-post increment-decrement mode selection                                                                                                                                       |  |  |  |  |

### TABLE 27-1: OPCODE FIELD DESCRIPTIONS

# TABLE 27-2:ABBREVIATIONDESCRIPTIONS

| Field | Description     |  |

|-------|-----------------|--|

| PC    | Program Counter |  |

| TO    | Time-Out bit    |  |

| С     | Carry bit       |  |

| DC    | Digit Carry bit |  |

| Z     | Zero bit        |  |

| PD    | Power-Down bit  |  |

| <b>TABLE 27-3</b> : | ENHANCED MID-RANGE INSTRUCTION SET ( | CONTINUED) |  |

|---------------------|--------------------------------------|------------|--|

|                     |                                      |            |  |

| TABLE 27-3. ENHANCED  |      |                                               |                                         |     | ,             |      |      |          |       |

|-----------------------|------|-----------------------------------------------|-----------------------------------------|-----|---------------|------|------|----------|-------|

| Mnemonic,<br>Operands |      | Description                                   | Cycles                                  |     | 14-Bit Opcode |      |      | Status   | Notes |

|                       |      |                                               | • • • • • • • • • • • • • • • • • • • • | MSb |               |      | LSb  | Affected |       |

|                       |      | CONTROL OPERA                                 | TIONS                                   |     |               |      |      |          |       |

| BRA                   | k    | Relative Branch                               | 2                                       | 11  | 001k          | kkkk | kkkk |          |       |

| BRW                   | -    | Relative Branch with W                        | 2                                       | 00  | 0000          | 0000 | 1011 |          |       |

| CALL                  | k    | Call Subroutine                               | 2                                       | 10  | 0kkk          | kkkk | kkkk |          |       |

| CALLW                 | -    | Call Subroutine with W                        | 2                                       | 00  | 0000          | 0000 | 1010 |          |       |

| GOTO                  | k    | Go to address                                 | 2                                       | 10  | 1kkk          | kkkk | kkkk |          |       |

| RETFIE                | k    | Return from interrupt                         | 2                                       | 00  | 0000          | 0000 | 1001 |          |       |

| RETLW                 | k    | Return with literal in W                      | 2                                       | 11  | 0100          | kkkk | kkkk |          |       |

| RETURN                | -    | Return from Subroutine                        | 2                                       | 00  | 0000          | 0000 | 1000 |          |       |

|                       |      | INHERENT OPER                                 | ATIONS                                  |     |               |      |      |          |       |

| CLRWDT                | -    | Clear Watchdog Timer                          | 1                                       | 00  | 0000          | 0110 | 0100 | TO, PD   |       |

| NOP                   | -    | No Operation                                  | 1                                       | 00  | 0000          | 0000 | 0000 |          |       |

| OPTION                | -    | Load OPTION_REG register with W               | 1                                       | 00  | 0000          | 0110 | 0010 |          |       |

| RESET                 | -    | Software device Reset                         | 1                                       | 00  | 0000          | 0000 | 0001 |          |       |

| SLEEP                 | -    | Go into Standby mode                          | 1                                       | 00  | 0000          | 0110 | 0011 | TO, PD   |       |

| TRIS                  | f    | Load TRIS register with W                     | 1                                       | 00  | 0000          | 0110 | Offf |          |       |

|                       |      | C-COMPILER OPT                                | IMIZED                                  |     |               |      |      |          |       |

| ADDFSR                | n, k | Add Literal k to FSRn                         | 1                                       | 11  | 0001          | 0nkk | kkkk |          |       |

| MOVIW                 | n mm | Move Indirect FSRn to W with pre/post inc/dec | 1                                       | 00  | 0000          | 0001 | 0nmm | Z        | 2, 3  |

|                       |      | modifier, mm                                  |                                         |     |               |      | kkkk |          |       |

|                       | k[n] | Move INDFn to W, Indexed Indirect.            | 1                                       | 11  | 1111          | 0nkk | lnmm | Z        | 2     |

| MOVWI                 | n mm | Move W to Indirect FSRn with pre/post inc/dec | 1                                       | 00  | 0000          | 0001 | kkkk |          | 2, 3  |

|                       |      | modifier, mm                                  |                                         |     |               |      |      |          |       |

|                       | k[n] | Move W to INDFn, Indexed Indirect.            | 1                                       | 11  | 1111          | 1nkk |      |          | 2     |

Note 1: If the Program Counter (PC) is modified, or a conditional test is true, the instruction requires two cycles. The second cycle is executed as a NOP.

2: If this instruction addresses an INDF register and the MSb of the corresponding FSR is set, this instruction will require one additional instruction cycle.

**3:** See Table in the MOVIW and MOVWI instruction descriptions.

| TABLE 28-5: MEMORY PRO | <b>GRAMMING SPECIFICATIONS</b> |

|------------------------|--------------------------------|

|------------------------|--------------------------------|

| Standard Operating Con | ditions (unless otherwise stated) |

|------------------------|-----------------------------------|

|------------------------|-----------------------------------|

| Param.<br>No. | Sym.   | Characteristic                               | Min.   | Тур† | Max.   | Units | Conditions                                                           |

|---------------|--------|----------------------------------------------|--------|------|--------|-------|----------------------------------------------------------------------|

|               |        | Program Memory<br>Programming Specifications |        |      |        |       |                                                                      |

| D110          | VIHH   | Voltage on MCLR/VPP pin                      | 8.0    | _    | 9.0    | V     | (Note 2)                                                             |

| D112          | VPBE   | VDD for Bulk Erase                           | 2.7    | _    | VDDMAX | V     |                                                                      |

| D113          | VPEW   | VDD for Write or Row Erase                   | VDDMIN |      | VDDMAX | V     |                                                                      |

| D114          | IPPPGM | Current on MCLR/VPP during<br>Erase/Write    | _      | 1.0  | _      | mA    |                                                                      |

| D115          | IDDPGM | Current on VDD during<br>Erase/Write         | —      | 5.0  | —      | mA    |                                                                      |

| D121          | Ер     | Program Flash Memory<br>Cell Endurance       | 10K    | _    | _      | E/W   | -40°C ≤ TA ≤ +85°C<br>(Note 1)                                       |

| D122          | VPRW   | VDD for Read/Write                           | VDDMIN | _    | VDDMAX | V     |                                                                      |

| D123          | Tiw    | Self-timed Write Cycle Time                  | —      | 2    | 2.5    | ms    |                                                                      |

| D124          | Tretd  | Characteristic Retention                     | —      | 40   | —      | Year  | Provided no other specifications are violated                        |

| D125          | EHEFC  | High-Endurance Flash Cell                    | 100K   |      | —      | E/W   | $0^{\circ}C \le TA \le +60^{\circ}C$ , lower byte last 128 addresses |

† Data in "Typ" column is at 3.0V, 25°C unless otherwise stated. These parameters are for design guidance only and are not tested.

**Note 1:** Self-write and Block Erase.

**2:** Required only if single-supply programming is disabled.

### TABLE 28-6: THERMAL CONSIDERATIONS

| Standard Operating Conditions (unless otherwise stated)<br>Operating temperature $-40^{\circ}C \le TA \le +125^{\circ}C$ |           |                                        |       |       |                                                          |  |  |

|--------------------------------------------------------------------------------------------------------------------------|-----------|----------------------------------------|-------|-------|----------------------------------------------------------|--|--|

| Param<br>No.                                                                                                             | Sym.      | Characteristic                         | Тур.  | Units | Conditions                                               |  |  |

| TH01                                                                                                                     | θJA       | Thermal Resistance Junction to Ambient | 70    | °C/W  | 14-pin PDIP package                                      |  |  |

|                                                                                                                          |           |                                        | 95.3  | °C/W  | 14-pin SOIC package                                      |  |  |

|                                                                                                                          |           |                                        | 100   | °C/W  | 14-pin TSSOP package                                     |  |  |

|                                                                                                                          |           |                                        | 55.3  | °C/W  | 16-pin QFN 3X3X0.9mm package                             |  |  |

|                                                                                                                          |           |                                        | 52.3  | °C/W  | 16-pin UQFN 3X3X0.5mm package                            |  |  |

| TH02                                                                                                                     | θJC       | Thermal Resistance Junction to Case    | 32.75 | °C/W  | 14-pin PDIP package                                      |  |  |

|                                                                                                                          |           |                                        | 31    | °C/W  | 14-pin SOIC package                                      |  |  |

|                                                                                                                          |           |                                        | 24.4  | °C/W  | 14-pin TSSOP package                                     |  |  |

|                                                                                                                          |           |                                        | 10    | °C/W  | 16-pin QFN 3X3X0.9mm package                             |  |  |

|                                                                                                                          |           |                                        | 11    | °C/W  | 16-pin UQFN 3X3X0.5mm package                            |  |  |

| TH03                                                                                                                     | TJMAX     | Maximum Junction Temperature           | 150   | °C    |                                                          |  |  |

| TH04                                                                                                                     | PD        | Power Dissipation                      | _     | W     | PD = PINTERNAL + PI/O                                    |  |  |

| TH05                                                                                                                     | PINTERNAL | Internal Power Dissipation             | _     | W     | PINTERNAL = IDD x VDD <sup>(1)</sup>                     |  |  |

| TH06                                                                                                                     | Pi/o      | I/O Power Dissipation                  | _     | W     | $PI/O = \Sigma (IOL * VOL) + \Sigma (IOH * (VDD - VOH))$ |  |  |

| TH07                                                                                                                     | Pder      | Derated Power                          | _     | W     | Pder = PDmax (Tj - Ta)/θja <sup>(2)</sup>                |  |  |

**Note 1:**IDD is current to run the chip alone without driving any load on the output pins.

**2:** TA = Ambient Temperature.

**3:** T<sub>J</sub> = Junction Temperature.

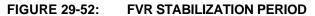

# 29.0 DC AND AC CHARACTERISTICS GRAPHS AND CHARTS

The graphs and tables provided in this section are for design guidance and are not tested.

In some graphs or tables, the data presented are **outside specified operating range** (i.e., outside specified VDD range). This is for **information only** and devices are ensured to operate properly only within the specified range.

**Note:** The graphs and tables provided following this note are a statistical summary based on a limited number of samples and are provided for informational purposes only. The performance characteristics listed herein are not tested or guaranteed. In some graphs or tables, the data presented may be outside the specified operating range (e.g., outside specified power supply range) and therefore, outside the warranted range.

"Typical" represents the mean of the distribution at 25°C. "MAXIMUM", "Max.", "MINIMUM" or "Min." represents (mean +  $3\sigma$ ) or (mean -  $3\sigma$ ) respectively, where  $\sigma$  is a standard deviation, over each temperature range.

# **PRODUCT IDENTIFICATION SYSTEM**

To order or obtain information, e.g., on pricing or delivery, refer to the factory or the listed sales office.

| PART NO.                 | [X] <sup>(1)</sup> - X /XX XXX<br>T Tape and Reel Temperature Package Pattern<br>Option Range                                        | Examples:<br>a) PIC16LF1503T - I/SL<br>Tape and Reel,<br>Industrial temperature,<br>SOIC package                                                                                                                                            |