Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

#### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

E·><Fl

| Detuils                    |                                                                             |

|----------------------------|-----------------------------------------------------------------------------|

| Product Status             | Active                                                                      |

| Core Processor             | PIC                                                                         |

| Core Size                  | 8-Bit                                                                       |

| Speed                      | 20MHz                                                                       |

| Connectivity               | I <sup>2</sup> C, SPI                                                       |

| Peripherals                | Brown-out Detect/Reset, POR, PWM, WDT                                       |

| Number of I/O              | 11                                                                          |

| Program Memory Size        | 3.5KB (2K x 14)                                                             |

| Program Memory Type        | FLASH                                                                       |

| EEPROM Size                | -                                                                           |

| RAM Size                   | 128 x 8                                                                     |

| Voltage - Supply (Vcc/Vdd) | 1.8V ~ 3.6V                                                                 |

| Data Converters            | A/D 8x10b                                                                   |

| Oscillator Type            | Internal                                                                    |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                           |

| Mounting Type              | Surface Mount                                                               |

| Package / Case             | 14-SOIC (0.154", 3.90mm Width)                                              |

| Supplier Device Package    | 14-SOIC                                                                     |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic16lf1503t-i-sl |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

# TO OUR VALUED CUSTOMERS

It is our intention to provide our valued customers with the best documentation possible to ensure successful use of your Microchip products. To this end, we will continue to improve our publications to better suit your needs. Our publications will be refined and enhanced as new volumes and updates are introduced.

If you have any questions or comments regarding this publication, please contact the Marketing Communications Department via E-mail at **docerrors@microchip.com** or fax the **Reader Response Form** in the back of this data sheet to (480) 792-4150. We welcome your feedback.

#### Most Current Data Sheet

To obtain the most up-to-date version of this data sheet, please register at our Worldwide Website at:

#### http://www.microchip.com

You can determine the version of a data sheet by examining its literature number found on the bottom outside corner of any page. The last character of the literature number is the version number, (e.g., DS30000A is version A of document DS30000).

#### Errata

An errata sheet, describing minor operational differences from the data sheet and recommended workarounds, may exist for current devices. As device/documentation issues become known to us, we will publish an errata sheet. The errata will specify the revision of silicon and revision of document to which it applies.

To determine if an errata sheet exists for a particular device, please check with one of the following:

- Microchip's Worldwide Website; http://www.microchip.com

- Your local Microchip sales office (see last page)

When contacting a sales office, please specify which device, revision of silicon and data sheet (include literature number) you are using.

#### **Customer Notification System**

Register on our website at www.microchip.com to receive the most current information on all of our products.

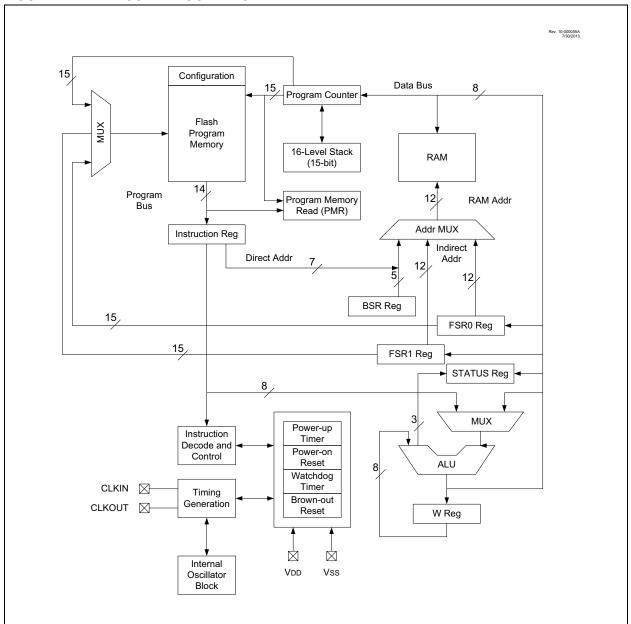

# 2.0 ENHANCED MID-RANGE CPU

This family of devices contain an enhanced mid-range 8-bit CPU core. The CPU has 49 instructions. Interrupt capability includes automatic context saving. The hardware stack is 16 levels deep and has Overflow and Underflow Reset capability. Direct, Indirect, and Relative addressing modes are available. Two File Select Registers (FSRs) provide the ability to read program and data memory.

- · Automatic Interrupt Context Saving

- · 16-level Stack with Overflow and Underflow

- · File Select Registers

- Instruction Set

#### FIGURE 2-1: CORE BLOCK DIAGRAM

### 3.3.5 DEVICE MEMORY MAPS

The memory maps for Bank 0 through Bank 31 are shown in the tables in this section.

#### TABLE 3-3: PIC16(L)F1503 MEMORY MAP

| IADI  | BANK 0                        |              | BANK 1                                |       | BANK 2                                |       | BANK 3                                |              | BANK 4                                |              | BANK 5                                |              | BANK 6                                |              | BANK 7                                |

|-------|-------------------------------|--------------|---------------------------------------|-------|---------------------------------------|-------|---------------------------------------|--------------|---------------------------------------|--------------|---------------------------------------|--------------|---------------------------------------|--------------|---------------------------------------|

| 000h  |                               | 080h         |                                       | 100h  |                                       | 180h  |                                       | 200h         |                                       | 280h         |                                       | 300h         |                                       | 380h         |                                       |

| 00011 | Core Registers<br>(Table 3-2) | 00011        | Core Registers<br>(Table 3-2)         | 10011 | Core Registers<br>(Table 3-2)         | Tooli | Core Registers<br>(Table 3-2)         | 20011        | Core Registers<br>(Table 3-2)         | 20011        | Core Registers<br>(Table 3-2)         | 00011        | Core Registers<br>(Table 3-2)         | 00011        | Core Registers<br>(Table 3-2)         |

| 00Bh  |                               | 08Bh         |                                       | 10Bh  |                                       | 18Bh  |                                       | 20Bh         |                                       | 28Bh         |                                       | 30Bh         |                                       | 38Bh         |                                       |

| 00Ch  | PORTA                         | 08Ch         | TRISA                                 | 10Ch  | LATA                                  | 18Ch  | ANSELA                                | 20Ch         | WPUA                                  | 28Ch         | _                                     | 30Ch         | _                                     | 38Ch         | _                                     |

| 00Dh  | _                             | 08Dh         | _                                     | 10Dh  | _                                     | 18Dh  | _                                     | 20Dh         | —                                     | 28Dh         | _                                     | 30Dh         | —                                     | 38Dh         | _                                     |

| 00Eh  | PORTC                         | 08Eh         | TRISC                                 | 10Eh  | LATC                                  | 18Eh  | ANSELC                                | 20Eh         |                                       | 28Eh         | —                                     | 30Eh         | _                                     | 38Eh         | _                                     |

| 00Fh  | _                             | 08Fh         | —                                     | 10Fh  |                                       | 18Fh  |                                       | 20Fh         |                                       | 28Fh         |                                       | 30Fh         | —                                     | 38Fh         | —                                     |

| 010h  | —                             | 090h         | —                                     | 110h  | —                                     | 190h  | —                                     | 210h         | —                                     | 290h         | _                                     | 310h         | _                                     | 390h         | _                                     |

| 011h  | PIR1                          | 091h         | PIE1                                  | 111h  | CM1CON0                               | 191h  | PMADRL                                | 211h         | SSP1BUF                               | 291h         | _                                     | 311h         | _                                     | 391h         | IOCAP                                 |

| 012h  | PIR2                          | 092h         | PIE2                                  | 112h  | CM1CON1                               | 192h  | PMADRH                                | 212h         | SSP1ADD                               | 292h         | _                                     | 312h         | _                                     | 392h         | IOCAN                                 |

| 013h  | PIR3                          | 093h         | PIE3                                  | 113h  | CM2CON0                               | 193h  | PMDATL                                | 213h         | SSP1MSK                               | 293h         | —                                     | 313h         | _                                     | 393h         | IOCAF                                 |

| 014h  | _                             | 094h         | —                                     | 114h  | CM2CON1                               | 194h  | PMDATH                                | 214h         | SSP1STAT                              | 294h         | —                                     | 314h         | —                                     | 394h         | _                                     |

| 015h  | TMR0                          | 095h         | OPTION_REG                            | 115h  | CMOUT                                 | 195h  | PMCON1                                | 215h         | SSP1CON1                              | 295h         | _                                     | 315h         | _                                     | 395h         | _                                     |

| 016h  | TMR1L                         | 096h         | PCON                                  | 116h  | BORCON                                | 196h  | PMCON2                                | 216h         | SSP1CON2                              | 296h         | _                                     | 316h         | —                                     | 396h         | _                                     |

| 017h  | TMR1H                         | 097h         | WDTCON                                | 117h  | FVRCON                                | 197h  | VREGCON                               | 217h         | SSP1CON3                              | 297h         | _                                     | 317h         | _                                     | 397h         | —                                     |

| 018h  | T1CON                         | 098h         |                                       | 118h  | DACCON0                               | 198h  | —                                     | 218h         | _                                     | 298h         | —                                     | 318h         | _                                     | 398h         | —                                     |

| 019h  | T1GCON                        | 099h         | OSCCON                                | 119h  | DACCON1                               | 199h  | —                                     | 219h         | —                                     | 299h         | —                                     | 319h         | _                                     | 399h         | —                                     |

| 01Ah  | TMR2                          | 09Ah         | OSCSTAT                               | 11Ah  | —                                     | 19Ah  | _                                     | 21Ah         | _                                     | 29Ah         | —                                     | 31Ah         | _                                     | 39Ah         | _                                     |

| 01Bh  | PR2                           | 09Bh         | ADRESL                                | 11Bh  | —                                     | 19Bh  | _                                     | 21Bh         | —                                     | 29Bh         | —                                     | 31Bh         | _                                     | 39Bh         | —                                     |

| 01Ch  | T2CON                         | 09Ch         | ADRESH                                | 11Ch  | _                                     | 19Ch  | _                                     | 21Ch         | _                                     | 29Ch         | —                                     | 31Ch         | _                                     | 39Ch         | _                                     |

| 01Dh  | _                             | 09Dh         | ADCON0                                | 11Dh  | APFCON                                | 19Dh  | _                                     | 21Dh         | —                                     | 29Dh         | —                                     | 31Dh         | _                                     | 39Dh         | _                                     |

| 01Eh  | _                             | 09Eh         | ADCON1                                | 11Eh  | _                                     | 19Eh  | _                                     | 21Eh         | _                                     | 29Eh         | _                                     | 31Eh         | _                                     | 39Eh         | _                                     |

| 01Fh  | _                             | 09Fh         | ADCON2                                | 11Fh  | _                                     | 19Fh  | _                                     | 21Fh         | _                                     | 29Fh         | _                                     | 31Fh         | _                                     | 39Fh         | _                                     |

| 020h  |                               | 0A0h         | General                               | 120h  |                                       | 1A0h  |                                       | 220h         |                                       | 2A0h         |                                       | 320h         |                                       | 3A0h         |                                       |

|       | General<br>Purpose            | 0BFh         | Purpose<br>Register<br>32 Bytes       |       | Unimplemented                         |       | Unimplemented                         |              | Unimplemented                         |              | Unimplemented                         |              | Unimplemented                         |              | Unimplemented                         |

|       | Register<br>80 Bytes          | 0C0h         | Unimplemented<br>Read as '0'          |       | Read as '0'                           |       | Read as '0'                           |              | Read as '0'                           |              | Read as '0'                           |              | Read as '0'                           |              | Read as '0'                           |

| 06Fh  |                               | 0EFh         |                                       | 16Fh  |                                       | 1EFh  |                                       | 26Fh         |                                       | 2EFh         |                                       | 36Fh         |                                       | 3EFh         |                                       |

| 070h  | Common RAM                    | 0F0h<br>0FFh | Common RAM<br>(Accesses<br>70h – 7Fh) | 170h  | Common RAM<br>(Accesses<br>70h – 7Fh) | 1F0h  | Common RAM<br>(Accesses<br>70h – 7Fh) | 270h<br>27Fh | Common RAM<br>(Accesses<br>70h – 7Fh) | 2F0h<br>2FFh | Common RAM<br>(Accesses<br>70h – 7Fh) | 370h<br>37Fh | Common RAM<br>(Accesses<br>70h – 7Fh) | 3F0h<br>3FFh | Common RAM<br>(Accesses<br>70h – 7Fh) |

| VI 11 |                               |              |                                       |       |                                       |       |                                       |              |                                       |              |                                       | 51111        |                                       |              |                                       |

Legend: = Unimplemented data memory locations, read as '0'

| Address            | Name       | Bit 7        | Bit 6            | Bit 5          | Bit 4           | Bit 3                   | Bit 2   | Bit 1      | Bit 0   | Value on<br>POR, BOR | Value on all<br>other<br>Resets |

|--------------------|------------|--------------|------------------|----------------|-----------------|-------------------------|---------|------------|---------|----------------------|---------------------------------|

| Bank 0             | )          |              |                  |                |                 |                         |         |            | •       |                      |                                 |

| 00Ch               | PORTA      | —            | —                | RA5            | RA4             | RA3                     | RA2     | RA1        | RA0     | xx xxxx              | xx xxxx                         |

| 00Dh               | —          | Unimplemen   | ted              |                |                 |                         |         |            |         | _                    | _                               |

| 00Eh               | PORTC      | _            | —                | RC5            | RC4             | RC3                     | RC2     | RC1        | RC0     | xx xxxx              | xx xxxx                         |

| 00Fh               | —          | Unimplemen   | ted              |                |                 |                         |         |            |         | _                    | _                               |

| 010h               |            | Unimplemen   | ted              |                |                 |                         |         |            |         | —                    | —                               |

| 011h               | PIR1       | TMR1GIF      | ADIF             | —              | —               | SSP1IF                  | —       | TMR2IF     | TMR1IF  | 00 0-00              | 00 0-00                         |

| 012h               | PIR2       | —            | C2IF             | C1IF           | —               | BCL1IF                  | NCO1IF  |            | _       | -00- 00              | -00- 00                         |

| 013h               | PIR3       | —            | —                | —              | —               |                         | —       | CLC2IF     | CLC1IF  | 00                   | 00                              |

| 014h               |            | Unimplemen   | ted              |                |                 |                         |         |            |         | —                    | —                               |

| 015h               | TMR0       | Holding Reg  | ister for the 8- | bit Timer0 C   | ount            |                         |         |            |         | xxxx xxxx            | uuuu uuuu                       |

| 016h               | TMR1L      | Holding Reg  | ister for the Le | east Significa | int Byte of the | e 16-bit TMR            | 1 Count |            |         | xxxx xxxx            | uuuu uuuu                       |

| 017h               | TMR1H      | Holding Reg  | ister for the M  | ost Significa  | nt Byte of the  | 16-bit TMR1             | Count   |            |         | xxxx xxxx            | uuuu uuuu                       |

| 018h               | T1CON      | TMR1C        | CS<1:0>          | T1CKP          | °S<1:0>         |                         | T1SYNC  |            | TMR10N  | 0000 -0-0            | uuuu -u-u                       |

| 019h               | T1GCON     | TMR1GE       | T1GPOL           | T1GTM          | T1GSPM          | T <u>1GGO</u> /<br>DONE | T1GVAL  | T1GSS<1:0> |         | 0000 0x00            | uuuu uxuu                       |

| 01Ah               | TMR2       | Timer2 Modu  | ule Register     |                |                 |                         |         |            |         | 0000 0000            | 0000 0000                       |

| 01Bh               | PR2        | Timer2 Perio | od Register      |                |                 |                         |         |            |         | 1111 1111            | 1111 1111                       |

| 01Ch               | T2CON      | _            |                  | T2OUTF         | PS<3:0>         |                         | TMR2ON  | T2CK       | PS<1:0> | -000 0000            | -000 0000                       |

| 01Dh<br>to<br>01Fh | _          | Unimplemen   | ted              |                |                 |                         |         |            |         | _                    | _                               |

| Bank 1             |            |              |                  | 1              |                 |                         |         |            |         | 1                    |                                 |

| 08Ch               | TRISA      | -            | —                | TRISA5         | TRISA4          | (2)                     | TRISA2  | TRISA1     | TRISA0  | 11 1111              | 11 1111                         |

| 08Dh               | —          | Unimplemen   | ted              |                | 1               |                         | 1       |            |         | —                    | —                               |

| 08Eh               | TRISC      | _            | —                | TRISC5         | TRISC4          | TRISC3                  | TRISC2  | TRISC1     | TRISC0  | 11 1111              | 11 1111                         |

| 08Fh               | —          | Unimplemen   | ted              |                |                 |                         |         |            |         |                      | —                               |

| 090h               | —          | Unimplemen   | ted              |                |                 |                         | 1       | -          | r       | _                    | —                               |

| 091h               | PIE1       | TMR1GIE      | ADIE             | —              | —               | SSP1IE                  | —       | TMR2IE     | TMR1IE  | 0000 0-00            | 0000 0-00                       |

| 092h               | PIE2       | —            | C2IE             | C1IE           |                 | BCL1IE                  | NCO1IE  | _          | _       | 000- 00              | 000- 00                         |

| 093h               | PIE3       | _            | —                | _              | —               | _                       | _       | CLC2IE     | CLC1IE  | 00                   | 00                              |

| 094h               | —          | Unimplemen   | ted              | -              |                 |                         |         |            |         | _                    | —                               |

| 095h               | OPTION_REG | WPUEN        | INTEDG           | TMR0CS         | TMR0SE          | PSA                     |         | PS<2:0>    | -       | 1111 1111            | 1111 1111                       |

| 096h               | PCON       | STKOVF       | STKUNF           | —              | RWDT            | RMCLR                   | RI      | POR        | BOR     | 00-1 11qq            | qq-q qquu                       |

| 097h               | WDTCON     | —            | —                |                |                 | WDTPS<4:0               | >       |            | SWDTEN  | 01 0110              | 01 0110                         |

| 098h               | _          | Unimplemen   | ted              |                |                 |                         |         |            |         | —                    | —                               |

| 099h               | OSCCON     | —            |                  | IRCF           | <3:0>           |                         | _       | SCS        | S<1:0>  | -011 1-00            | -011 1-00                       |

| 09Ah               | OSCSTAT    | —            | —                | —              | HFIOFR          |                         | —       | LFIOFR     | HFIOFS  | 000                  | ddd                             |

| 09Bh               | ADRESL     | ADC Result   | Register Low     |                |                 |                         |         |            |         | xxxx xxxx            | uuuu uuuu                       |

| 09Ch               | ADRESH     | ADC Result   | Register High    |                |                 |                         |         |            |         | xxxx xxxx            | uuuu uuuu                       |

| 09Dh               | ADCON0     | _            |                  |                | CHS<4:0>        |                         |         | GO/DONE    | ADON    | -000 0000            | -000 0000                       |

| 09Eh               | ADCON1     | ADFM         |                  | ADCS<2:0>      |                 | —                       |         | ADPR       | EF<1:0> | 000000               | 000000                          |

| 09Fh               | ADCON2     |              | TRIGSE           | L<3:0>         |                 | _                       | _       | _          | _       | 0000                 | 0000                            |

#### SPECIAL FUNCTION REGISTER SUMMARY **TABLE 3-5:**

Legend:

x = unknown, u = unchanged, g = value depends on condition, - = unimplemented, r = reserved. Shaded locations are unimplemented, read as '0'.

Note

1:

PIC16F1503 only.

2:

Unimplemented, read as '1'.

#### 4.6 Device ID and Revision ID

The memory location 8006h is where the Device ID and Revision ID are stored. The upper nine bits hold the Device ID. The lower five bits hold the Revision ID. See **Section 10.4 "User ID, Device ID and Configuration Word Access**" for more information on accessing these memory locations.

Development tools, such as device programmers and debuggers, may be used to read the Device ID and Revision ID.

## 4.7 Register Definitions: Device ID

#### REGISTER 4-3: DEVID: DEVICE ID REGISTER

|       |          | R      | R | R   | R        | R | R     |

|-------|----------|--------|---|-----|----------|---|-------|

|       |          |        |   | DEV | <8:3>    |   |       |

|       |          | bit 13 |   |     |          |   | bit 8 |

|       |          |        |   |     |          |   |       |

| R     | R        | R      | R | R   | R        | R | R     |

|       | DEV<2:0> |        |   |     | REV<4:0> |   |       |

| bit 7 |          |        |   |     |          |   | bit 0 |

# Legend:

bit 13-5

R = Readable bit

'1' = Bit is set

| D | DEV<8:0>: Device ID | bits               |          |  |  |  |  |  |

|---|---------------------|--------------------|----------|--|--|--|--|--|

|   | Device              | DEVID<13:0> Values |          |  |  |  |  |  |

|   | Device              | DEV<8:0>           | REV<4:0> |  |  |  |  |  |

|   | PIC16LF1503         | 10 1101 101        | x xxxx   |  |  |  |  |  |

|   | PIC16F1503          | 10 1100 111        | x xxxx   |  |  |  |  |  |

'0' = Bit is cleared

#### bit 4-0 **REV<4:0>:** Revision ID bits

These bits are used to identify the revision (see Table under DEV<8:0> above).

# 10.2.4 WRITING TO FLASH PROGRAM MEMORY

Program memory is programmed using the following steps:

- 1. Load the address in PMADRH:PMADRL of the row to be programmed.

- 2. Load each write latch with data.

- 3. Initiate a programming operation.

- 4. Repeat steps 1 through 3 until all data is written.

Before writing to program memory, the word(s) to be written must be erased or previously unwritten. Program memory can only be erased one row at a time. No automatic erase occurs upon the initiation of the write.

Program memory can be written one or more words at a time. The maximum number of words written at one time is equal to the number of write latches. See Figure 10-5 (row writes to program memory with 16 write latches) for more details.

The write latches are aligned to the Flash row address boundary defined by the upper 10-bits of PMADRH:PMADRL, (PMADRH<6:0>:PMADRL<7:5>) with the lower five bits of PMADRL, (PMADRL<7:0>) determining the write latch being loaded. Write operations do not cross these boundaries. At the completion of a program memory write operation, the data in the write latches is reset to contain 0x3FFF. The following steps should be completed to load the write latches and program a row of program memory. These steps are divided into two parts. First, each write latch is loaded with data from the PMDATH:PMDATL using the unlock sequence with LWLO = 1. When the last word to be loaded into the write latch is ready, the LWLO bit is cleared and the unlock sequence executed. This initiates the programming operation, writing all the latches into Flash program memory.

| Note: | The special unlock sequence is required<br>to load a write latch with data or initiate a<br>Flash programming operation. If the |

|-------|---------------------------------------------------------------------------------------------------------------------------------|

|       | unlock sequence is interrupted, writing to the latches or program memory will not be initiated.                                 |

- 1. Set the WREN bit of the PMCON1 register.

- 2. Clear the CFGS bit of the PMCON1 register.

- 3. Set the LWLO bit of the PMCON1 register. When the LWLO bit of the PMCON1 register is '1', the write sequence will only load the write latches and will not initiate the write to Flash program memory.

- 4. Load the PMADRH:PMADRL register pair with the address of the location to be written.

- 5. Load the PMDATH:PMDATL register pair with the program memory data to be written.

- Execute the unlock sequence (Section 10.2.2 "Flash Memory Unlock Sequence"). The write latch is now loaded.

- 7. Increment the PMADRH:PMADRL register pair to point to the next location.

- 8. Repeat steps 5 through 7 until all but the last write latch has been loaded.

- Clear the LWLO bit of the PMCON1 register. When the LWLO bit of the PMCON1 register is '0', the write sequence will initiate the write to Flash program memory.

- 10. Load the PMDATH:PMDATL register pair with the program memory data to be written.

- Execute the unlock sequence (Section 10.2.2 "Flash Memory Unlock Sequence"). The entire program memory latch content is now written to Flash program memory.

- Note: The program memory write latches are reset to the blank state (0x3FFF) at the completion of every write or erase operation. As a result, it is not necessary to load all the program memory write latches. Unloaded latches will remain in the blank state.

An example of the complete write sequence is shown in Example 10-3. The initial address is loaded into the PMADRH:PMADRL register pair; the data is loaded using indirect addressing.

#### REGISTER 11-10: ANSELC: PORTC ANALOG SELECT REGISTER

| U-0              | U-0   | U-0               | U-0  | R/W-1/1                            | R/W-1/1                                        | R/W-1/1 | R/W-1/1 |  |  |

|------------------|-------|-------------------|------|------------------------------------|------------------------------------------------|---------|---------|--|--|

| _                | _     | —                 | _    | ANSC3                              | ANSC2                                          | ANSC1   | ANSC0   |  |  |

| bit 7            |       |                   |      | ·                                  | •                                              | •       | bit 0   |  |  |

|                  |       |                   |      |                                    |                                                |         |         |  |  |

| Legend:          |       |                   |      |                                    |                                                |         |         |  |  |

| R = Readable I   | bit   | W = Writable      | bit  | U = Unimplemented bit, read as '0' |                                                |         |         |  |  |

| u = Bit is uncha | anged | x = Bit is unkr   | nown | -n/n = Value a                     | /alue at POR and BOR/Value at all other Resets |         |         |  |  |

| '1' = Bit is set |       | '0' = Bit is clea | ared |                                    |                                                |         |         |  |  |

|                  |       |                   |      |                                    |                                                |         |         |  |  |

bit 7-4 Unimplemented: Read as '0'

bit 3-0

ANSC<3:0>: Analog Select between Analog or Digital Function on pins RC<3:0>, respectively

- 1 = Analog input. Pin is assigned as analog input<sup>(1)</sup>. Digital input buffer disabled.

- 0 = Digital I/O. Pin is assigned to port or digital special function.

- **Note 1:** When setting a pin to an analog input, the corresponding TRIS bit must be set to Input mode in order to allow external control of the voltage on the pin.

#### TABLE 11-6: SUMMARY OF REGISTERS ASSOCIATED WITH PORTC

| Name   | Bit 7 | Bit 6 | Bit 5  | Bit 4  | Bit 3  | Bit 2  | Bit 1  | Bit 0  | Register<br>on Page |

|--------|-------|-------|--------|--------|--------|--------|--------|--------|---------------------|

| ANSELC | —     |       |        | —      | ANSC3  | ANSC2  | ANSC1  | ANSC0  | 103                 |

| LATC   | _     | —     | LATC5  | LATC4  | LATC3  | LATC2  | LATC1  | LATC0  | 102                 |

| PORTC  | _     | —     | RC5    | RC4    | RC3    | RC2    | RC1    | RC0    | 102                 |

| TRISC  |       |       | TRISC5 | TRISC4 | TRISC3 | TRISC2 | TRISC1 | TRISC0 | 102                 |

Legend: x = unknown, u = unchanged, - = unimplemented locations read as '0'. Shaded cells are not used by PORTC.

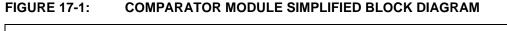

# 17.0 COMPARATOR MODULE

Comparators are used to interface analog circuits to a digital circuit by comparing two analog voltages and providing a digital indication of their relative magnitudes. Comparators are very useful mixed signal building blocks because they provide analog functionality independent of program execution. The analog comparator module includes the following features:

- Independent comparator control

- · Programmable input selection

- · Comparator output is available internally/externally

- · Programmable output polarity

- · Interrupt-on-change

- · Wake-up from Sleep

- · Programmable Speed/Power optimization

- PWM shutdown

- · Programmable and fixed voltage reference

# 17.1 Comparator Overview

A single comparator is shown in Figure 17-2 along with the relationship between the analog input levels and the digital output. When the analog voltage at VIN+ is less than the analog voltage at VIN-, the output of the comparator is a digital low level. When the analog voltage at VIN+ is greater than the analog voltage at VIN-, the output of the comparator is a digital high level.

The comparators available for this device are listed in Table 17-1.

#### TABLE 17-1: AVAILABLE COMPARATORS

| Device        | C1 | C2 |

|---------------|----|----|

| PIC16(L)F1503 | •  | •  |

# 21.2.2 SPI MODE OPERATION

When initializing the SPI, several options need to be specified. This is done by programming the appropriate control bits (SSPxCON1<5:0> and SSPxSTAT<7:6>). These control bits allow the following to be specified:

- Master mode (SCKx is the clock output)

- Slave mode (SCKx is the clock input)

- Clock Polarity (Idle state of SCKx)

- Data Input Sample Phase (middle or end of data output time)

- Clock Edge (output data on rising/falling edge of SCKx)

- Clock Rate (Master mode only)

- Slave Select mode (Slave mode only)

To enable the serial port, SSP Enable bit, SSPEN of the SSPxCON1 register, must be set. To reset or reconfigure SPI mode, clear the SSPEN bit, re-initialize the SSPxCONx registers and then set the SSPEN bit. This configures the SDI, SDO, SCK and SS pins as serial port pins. For the pins to behave as the serial port function, some must have their data direction bits (in the TRIS register) appropriately programmed as follows:

- SDIx must have corresponding TRIS bit set

- SDOx must have corresponding TRIS bit cleared

- SCKx (Master mode) must have corresponding

TRIS bit cleared

- SCKx (Slave mode) must have corresponding TRIS bit set

- SSx must have corresponding TRIS bit set

Any serial port function that is not desired may be overridden by programming the corresponding data direction (TRIS) register to the opposite value.

The MSSP consists of a transmit/receive shift register (SSPxSR) and a buffer register (SSPxBUF). The SSPxSR shifts the data in and out of the device, MSb first. The SSPxBUF holds the data that was written to the SSPxSR until the received data is ready. Once the eight bits of data have been received, that byte is moved to the SSPxBUF register. Then, the Buffer Full Detect bit, BF of the SSPxSTAT register, and the interrupt flag bit, SSPxIF, are set. This double-buffering of the received data (SSPxBUF) allows the next byte to start reception before reading the data that was just received. Any write to the SSPxBUF register during transmission/reception of data will be ignored and the write collision detect bit, WCOL of the SSPxCON1 register, will be set. User software must clear the WCOL bit to allow the following write(s) to the SSPxBUF register to complete successfully.

When the application software is expecting to receive valid data, the SSPxBUF should be read before the next byte of data to transfer is written to the SSPxBUF. The Buffer Full bit, BF of the SSPxSTAT register, indicates when SSPxBUF has been loaded with the received data (transmission is complete). When the SSPxBUF is read, the BF bit is cleared. This data may be irrelevant if the SPI is only a transmitter. Generally, the MSSP interrupt is used to determine when the transmission/reception has completed. If the interrupt method is not going to be used, then software polling can be done to ensure that a write collision does not occur.

The SSPxSR is not directly readable or writable and can only be accessed by addressing the SSPxBUF register. Additionally, the SSPxSTAT register indicates the various Status conditions. When one device is transmitting a logical one, or letting the line float, and a second device is transmitting a logical zero, or holding the line low, the first device can detect that the line is not a logical one. This detection, when used on the SCLx line, is called clock stretching. Clock stretching gives slave devices a mechanism to control the flow of data. When this detection is used on the SDAx line, it is called arbitration. Arbitration ensures that there is only one master device communicating at any single time.

# 21.3.1 CLOCK STRETCHING

When a slave device has not completed processing data, it can delay the transfer of more data through the process of clock stretching. An addressed slave device may hold the SCLx clock line low after receiving or sending a bit, indicating that it is not yet ready to continue. The master that is communicating with the slave will attempt to raise the SCLx line in order to transfer the next bit, but will detect that the clock line has not yet been released. Because the SCLx connection is open-drain, the slave has the ability to hold that line low until it is ready to continue communicating.

Clock stretching allows receivers that cannot keep up with a transmitter to control the flow of incoming data.

#### 21.3.2 ARBITRATION

Each master device must monitor the bus for Start and Stop bits. If the device detects that the bus is busy, it cannot begin a new message until the bus returns to an Idle state.

However, two master devices may try to initiate a transmission on or about the same time. When this occurs, the process of arbitration begins. Each transmitter checks the level of the SDAx data line and compares it to the level that it expects to find. The first transmitter to observe that the two levels do not match, loses arbitration, and must stop transmitting on the SDAx line.

For example, if one transmitter holds the SDAx line to a logical one (lets it float) and a second transmitter holds it to a logical zero (pulls it low), the result is that the SDAx line will be low. The first transmitter then observes that the level of the line is different than expected and concludes that another transmitter is communicating.

The first transmitter to notice this difference is the one that loses arbitration and must stop driving the SDAx line. If this transmitter is also a master device, it also must stop driving the SCLx line. It then can monitor the lines for a Stop condition before trying to reissue its transmission. In the meantime, the other device that has not noticed any difference between the expected and actual levels on the SDAx line continues with its original transmission. It can do so without any complications, because so far, the transmission appears exactly as expected with no other transmitter disturbing the message.

Slave Transmit mode can also be arbitrated, when a master addresses multiple slaves, but this is less common.

If two master devices are sending a message to two different slave devices at the address stage, the master sending the lower slave address always wins arbitration. When two master devices send messages to the same slave address, and addresses can sometimes refer to multiple slaves, the arbitration process must continue into the data stage.

Arbitration usually occurs very rarely, but it is a necessary process for proper multi-master support.

# 21.4 I<sup>2</sup>C MODE OPERATION

All MSSP I<sup>2</sup>C communication is byte oriented and shifted out MSb first. Six SFR registers and two interrupt flags interface the module with the PIC<sup>®</sup> microcontroller and user software. Two pins, SDAx and SCLx, are exercised by the module to communicate with other external I<sup>2</sup>C devices.

#### 21.4.1 BYTE FORMAT

All communication in  $I^2C$  is done in 9-bit segments. A byte is sent from a master to a slave or vice-versa, followed by an Acknowledge bit sent back. After the eighth falling edge of the SCLx line, the device outputting data on the SDAx changes that pin to an input and reads in an acknowledge value on the next clock pulse.

The clock signal, SCLx, is provided by the master. Data is valid to change while the SCLx signal is low, and sampled on the rising edge of the clock. Changes on the SDAx line while the SCLx line is high define special conditions on the bus, explained below.

# 21.4.2 DEFINITION OF I<sup>2</sup>C TERMINOLOGY

There is language and terminology in the description of I<sup>2</sup>C communication that have definitions specific to I<sup>2</sup>C. That word usage is defined below and may be used in the rest of this document without explanation. This table was adapted from the Philips I<sup>2</sup>C<sup>TM</sup> specification.

### 21.4.3 SDAX AND SCLX PINS

Selection of any I<sup>2</sup>C mode with the SSPEN bit set, forces the SCLx and SDAx pins to be open-drain. These pins should be set by the user to inputs by setting the appropriate TRIS bits.

Note: Data is tied to output zero when an I<sup>2</sup>C mode is enabled.

#### 21.4.4 SDAX HOLD TIME

The hold time of the SDAx pin is selected by the SDAHT bit of the SSPxCON3 register. Hold time is the time SDAx is held valid after the falling edge of SCLx. Setting the SDAHT bit selects a longer 300 ns minimum hold time and may help on buses with large capacitance.

### TABLE 21-2: I<sup>2</sup>C BUS TERMS

| TADLE ZT-Z:         |                                                                                                                                                                                                  |

|---------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| TERM                | Description                                                                                                                                                                                      |

| Transmitter         | The device which shifts data out onto the bus.                                                                                                                                                   |

| Receiver            | The device which shifts data in from the bus.                                                                                                                                                    |

| Master              | The device that initiates a transfer, generates clock signals and termi-<br>nates a transfer.                                                                                                    |

| Slave               | The device addressed by the master.                                                                                                                                                              |

| Multi-master        | A bus with more than one device that can initiate data transfers.                                                                                                                                |

| Arbitration         | Procedure to ensure that only one master at a time controls the bus. Winning arbitration ensures that the message is not corrupted.                                                              |

| Synchronization     | Procedure to synchronize the clocks of two or more devices on the bus.                                                                                                                           |

| Idle                | No master is controlling the bus,<br>and both SDAx and SCLx lines are<br>high.                                                                                                                   |

| Active              | Any time one or more master devices are controlling the bus.                                                                                                                                     |

| Addressed<br>Slave  | Slave device that has received a matching address and is actively being clocked by a master.                                                                                                     |

| Matching<br>Address | Address byte that is clocked into a slave that matches the value stored in SSPxADD.                                                                                                              |

| Write Request       | Slave receives a matching address with R/W bit clear, and is ready to clock in data.                                                                                                             |

| Read Request        | Master sends an address byte with the $R/\overline{W}$ bit set, indicating that it wishes to clock data out of the Slave. This data is the next and all following bytes until a Restart or Stop. |

| Clock Stretching    | When a device on the bus hold SCLx low to stall communication.                                                                                                                                   |

| Bus Collision       | Any time the SDAx line is sampled<br>low by the module while it is out-<br>putting and expected high state.                                                                                      |

# 21.6 I<sup>2</sup>C MASTER MODE

Master mode is enabled by setting and clearing the appropriate SSPM bits in the SSPxCON1 register and by setting the SSPEN bit. In Master mode, the SDAx and SCKx pins must be configured as inputs. The MSSP peripheral hardware will override the output driver TRIS controls when necessary to drive the pins low.

Master mode of operation is supported by interrupt generation on the detection of the Start and Stop conditions. The Stop (P) and Start (S) bits are cleared from a Reset or when the MSSPx module is disabled. Control of the I<sup>2</sup>C bus may be taken when the P bit is set, or the bus is idle.

In Firmware Controlled Master mode, user code conducts all I<sup>2</sup>C bus operations based on Start and Stop bit condition detection. Start and Stop condition detection is the only active circuitry in this mode. All other communication is done by the user software directly manipulating the SDAx and SCLx lines.

The following events will cause the SSPx Interrupt Flag bit, SSPxIF, to be set (SSPx interrupt, if enabled):

- · Start condition detected

- Stop condition detected

- · Data transfer byte transmitted/received

- Acknowledge transmitted/received

- · Repeated Start generated

- Note 1: The MSSPx module, when configured in I<sup>2</sup>C Master mode, does not allow queueing of events. For instance, the user is not allowed to initiate a Start condition and immediately write the SSPxBUF register to initiate transmission before the Start condition is complete. In this case, the SSPxBUF will not be written to and the WCOL bit will be set, indicating that a write to the SSPxBUF did not occur

- 2: When in Master mode, Start/Stop detection is masked and an interrupt is generated when the SEN/PEN bit is cleared and the generation is complete.

#### 21.6.1 I<sup>2</sup>C MASTER MODE OPERATION

The master device generates all of the serial clock pulses and the Start and Stop conditions. A transfer is ended with a Stop condition or with a Repeated Start condition. Since the Repeated Start condition is also the beginning of the next serial transfer, the I<sup>2</sup>C bus will not be released.

In Master Transmitter mode, serial data is output through SDAx, while SCLx outputs the serial clock. The first byte transmitted contains the slave address of the receiving device (seven bits) and the Read/Write (R/W) bit. In this case, the R/W bit will be logic '0'. Serial data is transmitted eight bits at a time. After each byte is transmitted, an Acknowledge bit is received. Start and Stop conditions are output to indicate the beginning and the end of a serial transfer.

In Master Receive mode, the first byte transmitted contains the slave address of the transmitting device (seven bits) and the  $R/\overline{W}$  bit. In this case, the  $R/\overline{W}$  bit will be logic '1'. Thus, the first byte transmitted is a 7-bit slave address followed by a '1' to indicate the receive bit. Serial data is received via SDAx, while SCLx outputs the serial clock. Serial data is received eight bits at a time. After each byte is received, an Acknowledge bit is transmitted. Start and Stop conditions indicate the beginning and end of transmission.

A Baud Rate Generator is used to set the clock frequency output on SCLx. See **Section21.7 "Baud Rate Generator"** for more detail.

# 21.8 Register Definitions: MSSP Control

| R/W-0/0          | R/W-0/0                                                                                                                                               | R-0/0                                                                                                                                     | R-0/0                                                           | R-0/0                                 | R-0/0                                    | R-0/0               | R-0/0           |

|------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------|---------------------------------------|------------------------------------------|---------------------|-----------------|

| SMP              | CKE                                                                                                                                                   | D/A                                                                                                                                       | Р                                                               | S                                     | R/W                                      | UA                  | BF              |

| bit 7            |                                                                                                                                                       |                                                                                                                                           | 1                                                               |                                       |                                          |                     | bit (           |

|                  |                                                                                                                                                       |                                                                                                                                           |                                                                 |                                       |                                          |                     |                 |

| Legend:          |                                                                                                                                                       |                                                                                                                                           |                                                                 |                                       |                                          |                     |                 |

| R = Readable b   |                                                                                                                                                       | W = Writable b                                                                                                                            | it                                                              | U = Unimplem                          | nented bit, read as                      | ʻ0'                 |                 |

| u = Bit is uncha | inged                                                                                                                                                 | x = Bit is unkno                                                                                                                          |                                                                 | -n/n = Value a                        | t POR and BOR/V                          | alue at all other l | Resets          |

| '1' = Bit is set |                                                                                                                                                       | '0' = Bit is clea                                                                                                                         | red                                                             |                                       |                                          |                     |                 |

| bit 7            | <u>SPI Master mo</u><br>1 = Input data                                                                                                                | a Input Sample b<br>o <u>de:</u><br>sampled at end o<br>sampled at midd                                                                   | of data output ti                                               |                                       |                                          |                     |                 |

|                  | In I <sup>2</sup> C Master of<br>1 = Slew rate                                                                                                        | cleared when SP<br>or Slave mode:<br>control disabled                                                                                     | I is used in Slav                                               | ve mode                               |                                          |                     |                 |

|                  |                                                                                                                                                       | control enabled                                                                                                                           |                                                                 |                                       |                                          |                     |                 |

| bit 6            | In SPI Master<br>1 = Transmit o<br>0 = Transmit o<br>In I <sup>2</sup> C™ mode<br>1 = Enable inp                                                      | ck Edge Select bi<br>or Slave mode:<br>occurs on transitio<br>occurs on transitio<br>conly:<br>out logic so that the<br>MBus specific inp | on from active to<br>on from Idle to a<br>nresholds are co      | Idle clock state<br>ctive clock state |                                          |                     |                 |

| bit 5            | <b>D/A:</b> Data/Add<br>1 = Indicates t                                                                                                               | Iress bit (I <sup>2</sup> C moo<br>hat the last byte i<br>hat the last byte i                                                             | le only)<br>received or tran                                    |                                       |                                          |                     |                 |

| bit 4            | 1 = Indicates t                                                                                                                                       | y. This bit is clear<br>hat a Stop bit has<br>as not detected la                                                                          | been detected                                                   |                                       | disabled, SSPEN is<br>0' on Reset)       | s cleared.)         |                 |

| bit 3            | 1 = Indicates t                                                                                                                                       | y. This bit is clear<br>hat a Start bit has<br>as not detected la                                                                         | s been detected                                                 |                                       | disabled, SSPEN is<br>0' on Reset)       | s cleared.)         |                 |

| bit 2            | This bit holds t<br>to the next Sta<br><u>In I<sup>2</sup>C Slave m</u><br>1 = Read<br>0 = Write<br><u>In I<sup>2</sup>C Master 1</u><br>1 = Transmit | nt bit, Stop bit, or<br>10de:<br>mode:                                                                                                    | atio <u>n foll</u> owing f<br>not ACK bit.                      |                                       | match. This bit is c                     | only valid from the | e address match |

| bit 1            | OR-ing tl<br>UA: Update A<br>1 = Indicates t                                                                                                          | his bit with SEN,<br>ddress bit (10-bit                                                                                                   | RSEN, PEN, R<br>I <sup>2</sup> C mode only)<br>is to update the |                                       | will indicate if the<br>SSPxADD register |                     | node.           |

| bit 0            | <b>BF:</b> Buffer Ful<br><u>Receive (SPI a</u><br>1 = Receive co<br>0 = Receive no<br><u>Transmit (l<sup>2</sup>C<br/>1 = Data trans</u>              | I Status bit<br>and I <sup>2</sup> C modes):<br>omplete, SSPxBL<br>ot complete, SSP<br>mode only):<br>mit in progress (o                  | JF is full<br>xBUF is empty<br>loes not include                 |                                       | Stop bits), SSPxBU<br>p bits), SSPxBUF   |                     |                 |

# REGISTER 21-1: SSPxSTAT: SSP STATUS REGISTER

PIC16(L)F1503

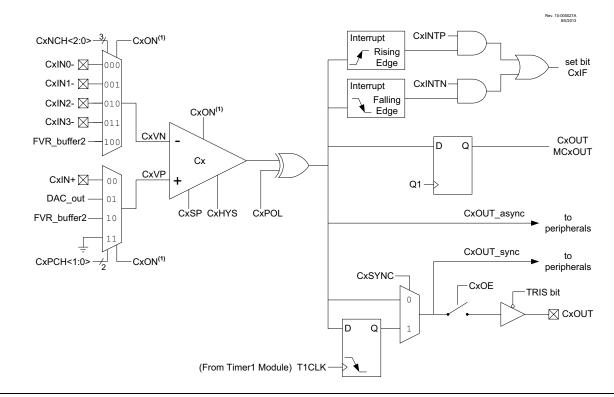

# 24.2 Fixed Duty Cycle (FDC) Mode

In Fixed Duty Cycle (FDC) mode, every time the accumulator overflows (NCO\_overflow), the output is toggled. This provides a 50% duty cycle, provided that the increment value remains constant. For more information, see Figure 24-2.

The FDC mode is selected by clearing the NxPFM bit in the NCOxCON register.

# 24.3 Pulse Frequency (PF) Mode

In Pulse Frequency (PF) mode, every time the accumulator overflows (NCO\_overflow), the output becomes active for one or more clock periods. Once the clock period expires, the output returns to an inactive state. This provides a pulsed output.

The output becomes active on the rising clock edge immediately following the overflow event. For more information, see Figure 24-2.

The value of the active and inactive states depends on the polarity bit, NxPOL in the NCOxCON register.

The PF mode is selected by setting the NxPFM bit in the NCOxCON register.

#### 24.3.1 OUTPUT PULSE WIDTH CONTROL

When operating in PF mode, the active state of the output can vary in width by multiple clock periods. Various pulse widths are selected with the NxPWS<2:0> bits in the NCOxCLK register.

When the selected pulse width is greater than the accumulator overflow time frame, the output of the NCOx operation is indeterminate.

# 24.4 Output Polarity Control

The last stage in the NCOx module is the output polarity. The NxPOL bit in the NCOxCON register selects the output polarity. Changing the polarity while the interrupts are enabled will cause an interrupt for the resulting output transition.

The NCOx output can be used internally by source code or other peripherals. Accomplish this by reading the NxOUT (read-only) bit of the NCOxCON register.

The NCOx output signal is available to the following peripherals:

- CLC

- CWG

# 24.5 Interrupts

When the accumulator overflows (NCO\_overflow), the NCOx Interrupt Flag bit, NCOxIF, of the PIRx register is set. To enable the interrupt event (NCO\_interrupt), the following bits must be set:

- NxEN bit of the NCOxCON register

- NCOxIE bit of the PIEx register

- PEIE bit of the INTCON register

- · GIE bit of the INTCON register

The interrupt must be cleared by software by clearing the NCOxIF bit in the Interrupt Service Routine.

# 24.6 Effects of a Reset

All of the NCOx registers are cleared to zero as the result of a Reset.

# 24.7 Operation In Sleep

The NCO module operates independently from the system clock and will continue to run during Sleep, provided that the clock source selected remains active.

The HFINTOSC remains active during Sleep when the NCO module is enabled and the HFINTOSC is selected as the clock source, regardless of the system clock source selected.

In other words, if the HFINTOSC is simultaneously selected as the system clock and the NCO clock source, when the NCO is enabled, the CPU will go idle during Sleep, but the NCO will continue to operate and the HFINTOSC will remain active.

This will have a direct effect on the Sleep mode current.

# 24.8 Alternate Pin Locations

This module incorporates I/O pins that can be moved to other locations with the use of the alternate pin function register, APFCON. To determine which pins can be moved and what their default locations are upon a Reset, see **Section 11.1 "Alternate Pin Function**" for more information.

# REGISTER 25-4: CWGxDBR: COMPLEMENTARY WAVEFORM GENERATOR (CWGx) RISING DEAD-BAND COUNT REGISTER

| U-0   | U-0 | R/W-x/u | R/W-x/u | R/W-x/u        | R/W-x/u | R/W-x/u | R/W-x/u |

|-------|-----|---------|---------|----------------|---------|---------|---------|

| _     | —   |         |         | CWG <b>x</b> D | BR<5:0> |         |         |

| bit 7 |     |         |         |                |         |         | bit 0   |

| Legend:              |                      |                                                       |

|----------------------|----------------------|-------------------------------------------------------|

| R = Readable bit     | W = Writable bit     | U = Unimplemented bit, read as '0'                    |

| u = Bit is unchanged | x = Bit is unknown   | -n/n = Value at POR and BOR/Value at all other Resets |

| '1' = Bit is set     | '0' = Bit is cleared | q = Value depends on condition                        |

| Dit 7-6 Unimplemented: Read as "0" | bit 7-6 | Unimplemented: Read as '0' |

|------------------------------------|---------|----------------------------|

|------------------------------------|---------|----------------------------|

bit 5-0 **CWGxDBR<5:0>:** Complementary Waveform Generator (CWGx) Rising Counts 11 1111 = 63-64 counts of dead band

11 1110 = 62-63 counts of dead band

- ٠

- •

- •

00 0010 = 2-3 counts of dead band

- 00 0001 = 1-2 counts of dead band

- 00 0000 = 0 counts of dead band

# REGISTER 25-5: CWGxDBF: COMPLEMENTARY WAVEFORM GENERATOR (CWGx) FALLING DEAD-BAND COUNT REGISTER

| U-0   | U-0 | R/W-x/u      | R/W-x/u | R/W-x/u | R/W-x/u | R/W-x/u | R/W-x/u |

|-------|-----|--------------|---------|---------|---------|---------|---------|

| —     | —   | CWGxDBF<5:0> |         |         |         |         |         |

| bit 7 |     |              |         |         |         |         | bit 0   |

| Legend:              |                      |                                                       |

|----------------------|----------------------|-------------------------------------------------------|

| R = Readable bit     | W = Writable bit     | U = Unimplemented bit, read as '0'                    |

| u = Bit is unchanged | x = Bit is unknown   | -n/n = Value at POR and BOR/Value at all other Resets |

| '1' = Bit is set     | '0' = Bit is cleared | q = Value depends on condition                        |

bit 7-6 Unimplemented: Read as '0'

bit 5-0 CWGxDBF<5:0>: Complementary Waveform Generator (CWGx) Falling Counts

11 1111 = 63-64 counts of dead band

- 11 1110 = 62-63 counts of dead band

- •

- •

- 00 0010 = 2-3 counts of dead band

- 00 0001 = 1-2 counts of dead band

- 00 0000 = 0 counts of dead band. Dead-band generation is bypassed.

# PIC16(L)F1503

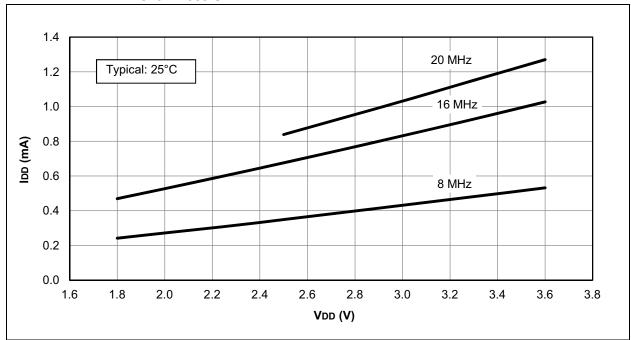

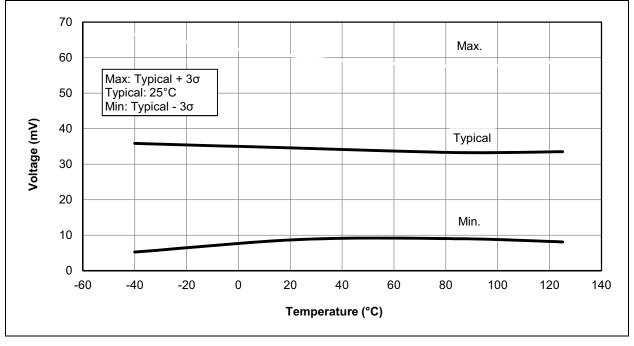

FIGURE 29-9: IDD TYPICAL, EXTERNAL CLOCK (ECH), HIGH-POWER MODE, PIC16LF1503 ONLY

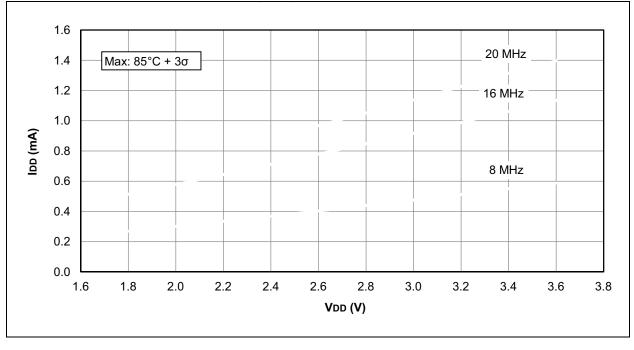

FIGURE 29-10: IDD MAXIMUM, EXTERNAL CLOCK (ECH), HIGH-POWER MODE, PIC16LF1503 ONLY

# PIC16(L)F1503

# 30.0 DEVELOPMENT SUPPORT

The PIC<sup>®</sup> microcontrollers (MCU) and dsPIC<sup>®</sup> digital signal controllers (DSC) are supported with a full range of software and hardware development tools:

- Integrated Development Environment

- MPLAB<sup>®</sup> X IDE Software

- Compilers/Assemblers/Linkers

- MPLAB XC Compiler

- MPASM<sup>™</sup> Assembler

- MPLINK<sup>™</sup> Object Linker/ MPLIB<sup>™</sup> Object Librarian

- MPLAB Assembler/Linker/Librarian for Various Device Families

- Simulators

- MPLAB X SIM Software Simulator

- Emulators

- MPLAB REAL ICE™ In-Circuit Emulator

- In-Circuit Debuggers/Programmers

- MPLAB ICD 3

- PICkit™ 3

- Device Programmers

- MPLAB PM3 Device Programmer

- Low-Cost Demonstration/Development Boards, Evaluation Kits and Starter Kits

- Third-party development tools

# 30.1 MPLAB X Integrated Development Environment Software

The MPLAB X IDE is a single, unified graphical user interface for Microchip and third-party software, and hardware development tool that runs on Windows<sup>®</sup>, Linux and Mac OS<sup>®</sup> X. Based on the NetBeans IDE, MPLAB X IDE is an entirely new IDE with a host of free software components and plug-ins for high-performance application development and debugging. Moving between tools and upgrading from software simulators to hardware debugging and programming tools is simple with the seamless user interface.

With complete project management, visual call graphs, a configurable watch window and a feature-rich editor that includes code completion and context menus, MPLAB X IDE is flexible and friendly enough for new users. With the ability to support multiple tools on multiple projects with simultaneous debugging, MPLAB X IDE is also suitable for the needs of experienced users.

Feature-Rich Editor:

- · Color syntax highlighting

- Smart code completion makes suggestions and provides hints as you type

- Automatic code formatting based on user-defined rules

- · Live parsing

User-Friendly, Customizable Interface:

- Fully customizable interface: toolbars, toolbar buttons, windows, window placement, etc.

- · Call graph window

Project-Based Workspaces:

- Multiple projects

- · Multiple tools

- Multiple configurations

- Simultaneous debugging sessions

File History and Bug Tracking:

- Local file history feature

- · Built-in support for Bugzilla issue tracker

#### 14-Lead Plastic Thin Shrink Small Outline (ST) - 4.4 mm Body [TSSOP]

**Note:** For the most current package drawings, please see the Microchip Packaging Specification located at http://www.microchip.com/packaging

|                          | Units         | N        | <b>IILLIMETER</b> | S    |  |

|--------------------------|---------------|----------|-------------------|------|--|

| Dimension                | Limits        | MIN      | NOM               | MAX  |  |

| Number of Pins           | N             | 14       |                   |      |  |

| Pitch                    | е             | 0.65 BSC |                   |      |  |

| Overall Height           | Α             | -        | -                 | 1.20 |  |

| Molded Package Thickness | A2            | 0.80     | 1.00              | 1.05 |  |

| Standoff                 | A1            | 0.05     | -                 | 0.15 |  |

| Overall Width            | th E 6.40 BSC |          |                   |      |  |

| Molded Package Width     | E1            | 4.30     | 4.40              | 4.50 |  |

| Molded Package Length    | D             | 4.90     | 5.00              | 5.10 |  |

| Foot Length              | L             | 0.45     | 0.60              | 0.75 |  |

| Footprint                | (L1)          | 1.00 REF |                   |      |  |

| Foot Angle               | φ             | 0°       | -                 | 8°   |  |

| Lead Thickness           | С             | 0.09     | -                 | 0.20 |  |

| Lead Width               | b             | 0.19     | -                 | 0.30 |  |

Notes:

1. Pin 1 visual index feature may vary, but must be located within the hatched area.

- 2. Dimensions D and E1 do not include mold flash or protrusions. Mold flash or protrusions shall not exceed 0.15mm per side.

- 3. Dimensioning and tolerancing per ASME Y14.5M

BSC: Basic Dimension. Theoretically exact value shown without tolerances. REF: Reference Dimension, usually without tolerance, for information purposes only.

Microchip Technology Drawing No. C04-087C Sheet 2 of 2