Welcome to **E-XFL.COM**

What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded - Microcontrollers</u>"

| Details                    |                                                                          |

|----------------------------|--------------------------------------------------------------------------|

| Product Status             | Obsolete                                                                 |

| Core Processor             | 8051                                                                     |

| Core Size                  | 8-Bit                                                                    |

| Speed                      | 12MHz                                                                    |

| Connectivity               | I <sup>2</sup> C, SPI, UART/USART                                        |

| Peripherals                | Brown-out Detect/Reset, LED, POR, PWM, WDT                               |

| Number of I/O              | 26                                                                       |

| Program Memory Size        | 4KB (4K x 8)                                                             |

| Program Memory Type        | FLASH                                                                    |

| EEPROM Size                | -                                                                        |

| RAM Size                   | 256 x 8                                                                  |

| Voltage - Supply (Vcc/Vdd) | 2.4V ~ 3.6V                                                              |

| Data Converters            | -                                                                        |

| Oscillator Type            | Internal                                                                 |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                        |

| Mounting Type              | Surface Mount                                                            |

| Package / Case             | 28-TSSOP (0.173", 4.40mm Width)                                          |

| Supplier Device Package    | 28-TSSOP                                                                 |

| Purchase URL               | https://www.e-xfl.com/product-detail/nxp-semiconductors/p89lpc930fdh-129 |

# 3. Ordering information

**Table 1: Ordering information**

| Type number  | Package | Package                                                                   |          |  |  |  |  |  |  |  |

|--------------|---------|---------------------------------------------------------------------------|----------|--|--|--|--|--|--|--|

|              | Name    | Description                                                               | Version  |  |  |  |  |  |  |  |

| P89LPC930FDH | TSSOP28 | plastic thin shrink small outline package;<br>28 leads; body width 4.4 mm | SOT361-1 |  |  |  |  |  |  |  |

| P89LPC931FDH | TSSOP28 | plastic thin shrink small outline package;<br>28 leads; body width 4.4 mm | SOT361-1 |  |  |  |  |  |  |  |

## 3.1 Ordering options

**Table 2: Part options**

| Type number  | Program memory | Temperature range | Frequency       |

|--------------|----------------|-------------------|-----------------|

| P89LPC930FDH | 4 kB           | –45 °C to +85 °C  | 0 MHz to 18 MHz |

| P89LPC931FDH | 8 kB           | –45 °C to +85 °C  | 0 MHz to 18 MHz |

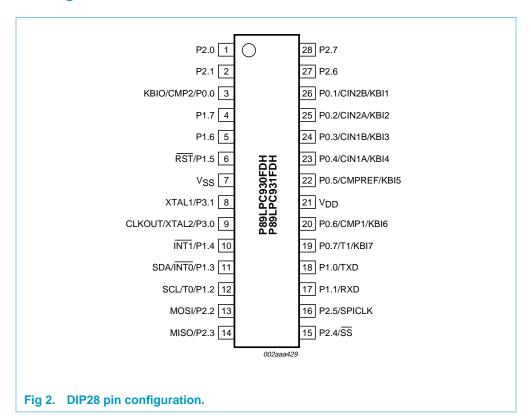

## 5. Pinning information

## 5.1 Pinning

## 5.2 Pin description

Table 3: Pin description

| 0 1 1       | D'                                  | -    |                                                                                                                                                                                                                                                                                                                                                                                                                                           |

|-------------|-------------------------------------|------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Symbol      | Pin                                 | Туре | Description                                                                                                                                                                                                                                                                                                                                                                                                                               |

| P0.0 - P0.7 | 3, 26, 25,<br>24, 23, 22,<br>20, 19 | I/O  | <b>Port 0:</b> Port 0 is an 8-bit I/O port with a user-configurable output type. During reset Port 0 latches are configured in the input only mode with the internal pull-up disabled. The operation of Port 0 pins as inputs and outputs depends upon the port configuration selected. Each port pin is configured independently. Refer to Section 8.11.1 "Port configurations" and Table 7 "DC electrical characteristics" for details. |

|             |                                     |      | The Keypad Interrupt feature operates with Port 0 pins.                                                                                                                                                                                                                                                                                                                                                                                   |

|             |                                     |      | All pins have Schmitt triggered inputs.                                                                                                                                                                                                                                                                                                                                                                                                   |

|             |                                     |      | Port 0 also provides various special functions as described below:                                                                                                                                                                                                                                                                                                                                                                        |

|             | 3                                   | I/O  | <b>P0.0</b> — Port 0 bit 0.                                                                                                                                                                                                                                                                                                                                                                                                               |

|             |                                     | 0    | CMP2 — Comparator 2 output.                                                                                                                                                                                                                                                                                                                                                                                                               |

|             |                                     | 1    | KBI0 — Keyboard input 0.                                                                                                                                                                                                                                                                                                                                                                                                                  |

|             | 26                                  | I/O  | <b>P0.1</b> — Port 0 bit 1.                                                                                                                                                                                                                                                                                                                                                                                                               |

|             |                                     | I    | CIN2B — Comparator 2 positive input B.                                                                                                                                                                                                                                                                                                                                                                                                    |

|             |                                     | 1    | KBI1 — Keyboard input 1.                                                                                                                                                                                                                                                                                                                                                                                                                  |

|             | 25                                  | I/O  | <b>P0.2</b> — Port 0 bit 2.                                                                                                                                                                                                                                                                                                                                                                                                               |

|             |                                     | 1    | CIN2A — Comparator 2 positive input A.                                                                                                                                                                                                                                                                                                                                                                                                    |

|             |                                     | 1    | KBI2 — Keyboard input 2.                                                                                                                                                                                                                                                                                                                                                                                                                  |

|             | 24                                  | I/O  | <b>P0.3</b> — Port 0 bit 3.                                                                                                                                                                                                                                                                                                                                                                                                               |

|             |                                     | I    | CIN1B — Comparator 1 positive input B.                                                                                                                                                                                                                                                                                                                                                                                                    |

|             |                                     | I    | KBI3 — Keyboard input 3.                                                                                                                                                                                                                                                                                                                                                                                                                  |

|             | 23                                  | I/O  | <b>P0.4</b> — Port 0 bit 4.                                                                                                                                                                                                                                                                                                                                                                                                               |

|             |                                     | I    | CIN1A — Comparator 1 positive input A.                                                                                                                                                                                                                                                                                                                                                                                                    |

|             |                                     | 1    | KBI4 — Keyboard input 4.                                                                                                                                                                                                                                                                                                                                                                                                                  |

|             | 22                                  | I/O  | <b>P0.5</b> — Port 0 bit 5.                                                                                                                                                                                                                                                                                                                                                                                                               |

|             |                                     | I    | CMPREF — Comparator reference (negative) input.                                                                                                                                                                                                                                                                                                                                                                                           |

|             |                                     | 1    | KBI5 — Keyboard input 5.                                                                                                                                                                                                                                                                                                                                                                                                                  |

|             | 20                                  | I/O  | <b>P0.6</b> — Port 0 bit 6.                                                                                                                                                                                                                                                                                                                                                                                                               |

|             |                                     | 0    | CMP1 — Comparator 1 output.                                                                                                                                                                                                                                                                                                                                                                                                               |

|             |                                     | I    | KBI6 — Keyboard input 6.                                                                                                                                                                                                                                                                                                                                                                                                                  |

|             | 19                                  | I/O  | <b>P0.7</b> — Port 0 bit 7.                                                                                                                                                                                                                                                                                                                                                                                                               |

|             |                                     | I/O  | T1 — Timer/counter 1 external count input or overflow output.                                                                                                                                                                                                                                                                                                                                                                             |

|             |                                     | I    | KBI7 — Keyboard input 7.                                                                                                                                                                                                                                                                                                                                                                                                                  |

Table 3:

Pin description...continued

| Symbol      | Pin                                | Туре | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

|-------------|------------------------------------|------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| P2.0 - P2.7 | 1, 2, 13,<br>14, 15, 16,<br>27, 28 | I/O  | Port 2: Port 2 is a 8-bit I/O port with a user-configurable output type. During reset Port 2 latches are configured in the input only mode with the internal pull-up disabled. The operation of port 2 pins as inputs and outputs depends upon the port configuration selected. Each port pin is configured independently. Refer to the section on I/O port configuration and the DC Electrical Characteristics for details. This port is not available in 20-pin package and is configured automatically as outputs to conserve power. The alternate functions for these pins must not be enabled. |

|             |                                    |      | All pins have Schmitt triggered inputs.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

|             |                                    |      | Port 2 also provides various special functions as described below.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

|             | 1                                  | I/O  | <b>P2.0</b> — Port 2 bit 0.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

| _           | 2                                  | I/O  | <b>P2.1</b> — Port 2 bit 1.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

|             | 13                                 | I/O  | <b>P2.2</b> — Port 2 bit 2.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

|             |                                    | I/O  | <b>MOSI</b> — SPI master out slave in. When configured as master, this pin is output, when configured as slave, this pin is input.                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

|             | 14                                 | I/O  | <b>P2.3</b> — Port 2 bit 3.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

|             |                                    | I/O  | <b>MISO</b> — SPI master in slave out. When configured as master, this pin is input, when configured as slave, this pin is output.                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

|             | 15                                 | I/O  | <b>P2.4</b> — Port 2 bit 4.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

|             |                                    | I    | SS — SPI Slave select.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

|             | 16                                 | I/O  | <b>P2.5</b> — Port 2 bit 5.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

|             |                                    | I/O  | <b>SPICLK</b> — SPI clock. When configured as master, this pin is output, when configured as slave, this pin is input.                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

|             | 27                                 | I/O  | <b>P2.6</b> — Port 2 bit 6.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

|             | 28                                 | I/O  | <b>P2.7</b> — Port 2 bit 7.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

Table 3:

Pin description...continued

| Symbol          | Pin  | Type | Description                                                                                                                                                                                                                                                                                                                                                                                                                               |

|-----------------|------|------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| P3.0 - P3.1     | 9, 8 | I/O  | <b>Port 3:</b> Port 3 is an 2-bit I/O port with a user-configurable output type. During reset Port 3 latches are configured in the input only mode with the internal pull-up disabled. The operation of Port 3 pins as inputs and outputs depends upon the port configuration selected. Each port pin is configured independently. Refer to Section 8.11.1 "Port configurations" and Table 7 "DC electrical characteristics" for details. |

|                 |      |      | All pins have Schmitt triggered inputs.                                                                                                                                                                                                                                                                                                                                                                                                   |

|                 |      |      | Port 3 also provides various special functions as described below:                                                                                                                                                                                                                                                                                                                                                                        |

|                 | 9    | I/O  | <b>P3.0</b> — Port 3 bit 0.                                                                                                                                                                                                                                                                                                                                                                                                               |

|                 |      | 0    | <b>XTAL2</b> — Output from the oscillator amplifier (when a crystal oscillator option is selected via the FLASH configuration).                                                                                                                                                                                                                                                                                                           |

|                 |      | 0    | <b>CLKOUT</b> — CPU clock divided by 2 when enabled via SFR bit (ENCLK - TRIM.6). It can be used if the CPU clock is the internal RC oscillator, Watchdog oscillator or external clock input, except when XTAL1/XTAL2 are used to generate clock source for the real time clock/system timer.                                                                                                                                             |

|                 | 8    | I/O  | <b>P3.1</b> — Port 3 bit 1.                                                                                                                                                                                                                                                                                                                                                                                                               |

|                 |      | I    | XTAL1 — Input to the oscillator circuit and internal clock generator circuits (when selected via the FLASH configuration). It can be a port pin if internal RC oscillator or Watchdog oscillator is used as the CPU clock source, and if XTAL1/XTAL2 are not used to generate the clock for the real time clock/system timer.                                                                                                             |

| V <sub>SS</sub> | 7    | I    | Ground: 0 V reference.                                                                                                                                                                                                                                                                                                                                                                                                                    |

| $V_{DD}$        | 21   | I    | <b>Power Supply:</b> This is the power supply voltage for normal operation as well as Idle and Power Down modes.                                                                                                                                                                                                                                                                                                                          |

<sup>[1]</sup> Input/Output for P1.0-P1.4, P1.6, P1.7. Input for P1.5.

## 7. Special function registers

**Remark:** Special Function Registers (SFRs) accesses are restricted in the following ways:

- User must **not** attempt to access any SFR locations not defined.

- Accesses to any defined SFR locations must be strictly for the functions for the SFRs.

- SFR bits labeled '-', '0' or '1' can **only** be written and read as follows:

- '-' Unless otherwise specified, must be written with '0', but can return any value when read (even if it was written with '0'). It is a reserved bit and may be used in future derivatives.

- '0' must be written with '0', and will return a '0' when read.

- '1' must be written with '1', and will return a '1' when read.

Product data

**Table 4: Special function registers** \* *indicates SFRs that are bit addressable.*

| Name                 | Description                             | SFR    | Bit function | ons and ad | dresses     |         |            |         |         |        | Rese  | value    |

|----------------------|-----------------------------------------|--------|--------------|------------|-------------|---------|------------|---------|---------|--------|-------|----------|

|                      |                                         | addr.  | MSB          |            |             |         |            |         |         | LSB    | Hex   | Binary   |

|                      | Bit a                                   | ddress | E7           | <b>E</b> 6 | <b>E</b> 5  | E4      | <b>E</b> 3 | E2      | E1      | E0     |       |          |

| ACC*                 | Accumulator                             | E0H    |              |            |             |         |            |         |         |        | 00    | 00000000 |

| AUXR1                | Auxiliary function register             | A2H    | CLKLP        | EBRR       | ENT1        | ENT0    | SRST       | 0       | -       | DPS    | 00[1] | 000000x0 |

|                      | Bit a                                   | ddress | F7           | F6         | F5          | F4      | F3         | F2      | F1      | F0     |       |          |

| B*                   | B register                              | F0H    |              |            |             |         |            |         |         |        | 00    | 00000000 |

| BRGR0 <sup>[2]</sup> | Baud rate generator rate LOW            | BEH    |              |            |             |         |            |         |         |        | 00    | 00000000 |

| BRGR1 <sup>[2]</sup> | Baud rate generator rate HIGH           | BFH    |              |            |             |         |            |         |         |        | 00    | 00000000 |

| BRGCON               | Baud rate generator control             | BDH    | -            | -          | -           | -       | -          | -       | SBRGS   | BRGEN  | 00[6] | xxxxxx00 |

| CMP1                 | Comparator 1 control register           | ACH    | -            | -          | CE1         | CP1     | CN1        | OE1     | CO1     | CMF1   | 00[1] | xx000000 |

| CMP2                 | Comparator 2 control register           | ADH    | -            | -          | CE2         | CP2     | CN2        | OE2     | CO2     | CMF2   | 00[1] | xx000000 |

| DIVM                 | CPU clock divide-by-M control           | 95H    |              |            |             |         |            |         |         |        | 00    | 00000000 |

| DPTR                 | Data pointer (2 bytes)                  |        |              |            |             |         |            |         |         |        |       |          |

| DPH                  | Data pointer HIGH                       | 83H    |              |            |             |         |            |         |         |        | 00    | 00000000 |

| DPL                  | Data pointer LOW                        | 82H    |              |            |             |         |            |         |         |        | 00    | 00000000 |

| FMADRH               | Program Flash address HIGH              | E7H    | -            | -          | -           | -       | -          | -       |         |        | 00    | 00000000 |

| FMADRL               | Program Flash address LOW               | E6H    |              |            |             |         |            |         |         |        | 00    | 00000000 |

| FMCON                | Program Flash Control (Read)            | E4H    | BUSY         | -          | -           | -       | HVA        | HVE     | SV      | OI     | 70    | 01110000 |

|                      | Program Flash Control (Write)           |        | FMCMD.       | FMCMD.     | FMCMD.<br>5 | FMCMD.  | FMCMD.     | FMCMD.  | FMCMD.  | FMCMD. |       |          |

| FMDATA               | Program Flash data                      | E5H    |              |            |             |         |            |         |         |        | 00    | 00000000 |

| I2ADR                | I <sup>2</sup> C slave address register | DBH    | I2ADR.6      | I2ADR.5    | I2ADR.4     | I2ADR.3 | I2ADR.2    | I2ADR.1 | I2ADR.0 | GC     | 00    | 00000000 |

|                      | Bit a                                   | ddress | DF           | DE         | DD          | DC      | DB         | DA      | D9      | D8     |       |          |

| I2CON*               | I <sup>2</sup> C control register       | D8H    | -            | I2EN       | STA         | STO     | SI         | AA      | -       | CRSEL  | 00    | x00000x0 |

| I2DAT                | I <sup>2</sup> C data register          | DAH    |              |            |             |         |            |         |         |        |       |          |

Product data

8-bit microcontrollers with two-clock 80C51 core

Table 4:

Special function registers...continued

\* indicates SFRs that are bit addressable.

| Name   | Description                       | SFR    | Bit functions and addresses |       |        |        |        |        |        |        |     | t value  |

|--------|-----------------------------------|--------|-----------------------------|-------|--------|--------|--------|--------|--------|--------|-----|----------|

|        |                                   | addr.  | MSB                         |       |        |        |        |        |        | LSB    | Hex | Binary   |

| TAMOD  | Timer 0 and 1 auxiliary mode      | 8FH    | -                           | -     | -      | T1M2   | -      | -      | -      | T0M2   | 00  | xxx0xxx0 |

|        | Bit a                             | ddress | 8F                          | 8E    | 8D     | 8C     | 8B     | 8A     | 89     | 88     |     |          |

| TCON*  | Timer 0 and 1 control             | 88H    | TF1                         | TR1   | TF0    | TR0    | IE1    | IT1    | IE0    | IT0    | 00  | 00000000 |

| TH0    | Timer 0 HIGH                      | 8CH    |                             |       |        |        |        |        |        |        | 00  | 00000000 |

| TH1    | Timer 1 HIGH                      | 8DH    |                             |       |        |        |        |        |        |        | 00  | 00000000 |

| TL0    | Timer 0 LOW                       | 8AH    |                             |       |        |        |        |        |        |        | 00  | 00000000 |

| TL1    | Timer 1 LOW                       | 8BH    |                             |       |        |        |        |        |        |        | 00  | 00000000 |

| TMOD   | Timer 0 and 1 mode                | 89H    | T1GATE                      | T1C/T | T1M1   | T1M0   | T0GATE | T0C/T  | T0M1   | TOMO   | 00  | 00000000 |

| TRIM   | Internal oscillator trim register | 96H    | -                           | ENCLK | TRIM.5 | TRIM.4 | TRIM.3 | TRIM.2 | TRIM.1 | TRIM.0 |     | [5] [6]  |

| WDCON  | Watchdog control register         | A7H    | PRE2                        | PRE1  | PRE0   | -      | -      | WDRUN  | WDTOF  | WDCLK  |     | [4] [6]  |

| WDL    | Watchdog load                     | C1H    |                             |       |        |        |        |        |        |        | FF  | 11111111 |

| WFEED1 | Watchdog feed 1                   | C2H    |                             |       |        |        |        |        |        |        |     |          |

| WFEED2 | Watchdog feed 2                   | СЗН    |                             |       |        |        |        |        |        |        |     |          |

- [1] All ports are in input only (high impedance) state after power-up.

- [2] BRGR1 and BRGR0 must only be written if BRGEN in BRGCON SFR is '0'. If any are written while BRGEN = 1, the result is unpredictable.

Unimplemented bits in SFRs (labeled '-') are X (unknown) at all times. Unless otherwise specified, ones should not be written to these bits since they may be used for other purposes in future derivatives. The reset values shown for these bits are '0's although they are unknown when read.

- [3] The RSTSRC register reflects the cause of the P89LPC930/931 reset. Upon a power-up reset, all reset source flags are cleared except POF and BOF; the power-on reset value is xx110000.

- [4] After reset, the value is 111001x1, i.e., PRE2-PRE0 are all '1', WDRUN = 1 and WDCLK = 1. WDTOF bit is '1' after Watchdog reset and is '0' after power-on reset. Other resets will not affect WDTOF.

- [5] On power-on reset, the TRIM SFR is initialized with a factory preprogrammed value. Other resets will not cause initialization of the TRIM register.

- [6] The only reset source that affects these SFRs is power-on reset.

© Koninklijke Philips Electronics N.V. 2004. All rights reserved

the minimum specified operating voltage. When using an oscillator frequency above 12 MHz, in some applications, an external brownout detect circuit may be required to hold the device in reset when  $V_{DD}$  falls below the minimum specified operating voltage.

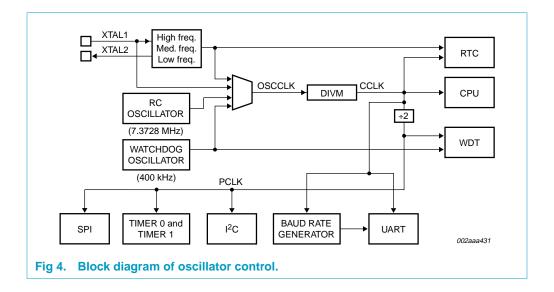

#### 8.2.6 Clock output

The P89LPC930/931 supports a user-selectable clock output function on the XTAL2/CLKOUT pin when crystal oscillator is not being used. This condition occurs if another clock source has been selected (on-chip RC oscillator, Watchdog oscillator, external clock input on X1) and if the Real-Time clock is not using the crystal oscillator as its clock source. This allows external devices to synchronize to the P89LPC930/931. This output is enabled by the ENCLK bit in the TRIM register. The frequency of this clock output is 1/2 that of the CCLK. If the clock output is not needed in Idle mode, it may be turned off prior to entering Idle, saving additional power.

## 8.3 On-chip RC oscillator option

The P89LPC930/931 has a 6-bit TRIM register that can be used to tune the frequency of the RC oscillator. During reset, the TRIM value is initialized to a factory pre-programmed value to adjust the oscillator frequency to 7.373 MHz,  $\pm 1\%$  at room temperature. End-user applications can write to the Trim register to adjust the on-chip RC oscillator to other frequencies.

## 8.4 Watchdog oscillator option

The watchdog has a separate oscillator which has a frequency of 400 kHz. This oscillator can be used to save power when a high clock frequency is not needed.

#### 8.5 External clock input option

In this configuration, the processor clock is derived from an external source driving the XTAL1/P3.1 pin. The rate may be from 0 Hz up to 18 MHz. The XTAL2/P3.0 pin may be used as a standard port pin or a clock output. When using an oscillator frequency above 12 MHz, the reset input function of P1.5 must be enabled. An external circuit is required to hold the device in reset at power-up until  $V_{DD}$  has reached its specified level. When system power is removed  $V_{DD}$  will fall below the minimum specified operating voltage. When using an oscillator frequency above 12 MHz, in some applications, an external brownout detect circuit may be required to hold the device in reset when  $V_{DD}$  falls below the minimum specified operating voltage.

- External reset pin (during power-up or if user configured via UCFG1. This option must be used for an oscillator frequency above 12 MHz.)

- Power-on detect

- Brownout detect

- Watchdog Timer

- Software reset

- UART break character detect reset

For every reset source, there is a flag in the Reset Register, RSTSRC. The user can read this register to determine the most recent reset source. These flag bits can be cleared in software by writing a '0' to the corresponding bit. More than one flag bit may be set:

- During a power-on reset, both POF and BOF are set but the other flag bits are cleared.

- For any other reset, previously set flag bits that have not been cleared will remain set.

#### 8.14.1 Reset vector

Following reset, the P89LPC930/931 will fetch instructions from either address 0000h or the Boot address. The Boot address is formed by using the Boot Vector as the high byte of the address and the low byte of the address = 00h.

The Boot address will be used if a UART break reset occurs, or the non-volatile Boot Status bit (BOOTSTAT.0) = 1, or the device is forced into ISP mode during power-on (see *P89LPC930/931 User's Manual*). Otherwise, instructions will be fetched from address 0000H.

#### 8.15 Timers/counters 0 and 1

The P89LPC930/931 has two general purpose counter/timers which are upward compatible with the standard 80C51 Timer 0 and Timer 1. Both can be configured to operate either as timers or event counter. An option to automatically toggle the T0 and/or T1 pins upon timer overflow has been added.

In the 'Timer' function, the register is incremented every machine cycle.

In the 'Counter' function, the register is incremented in response to a 1-to-0 transition at its corresponding external input pin, T0 or T1. In this function, the external input is sampled once during every machine cycle.

Timer 0 and Timer 1 have five operating modes (modes 0, 1, 2, 3 and 6). Modes 0, 1, 2 and 6 are the same for both Timers/Counters. Mode 3 is different.

#### 8.15.1 Mode 0

Putting either Timer into Mode 0 makes it look like an 8048 Timer, which is an 8-bit Counter with a divide-by-32 prescaler. In this mode, the Timer register is configured as a 13-bit register. Mode 0 operation is the same for Timer 0 and Timer 1.

#### 8.15.2 Mode 1

Mode 1 is the same as Mode 0, except that all 16 bits of the timer register are used.

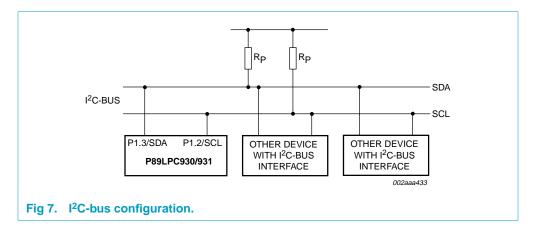

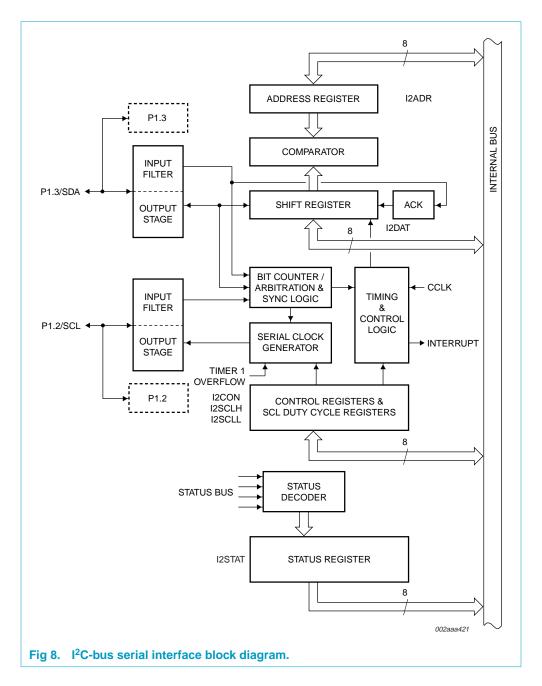

### 8.18 I<sup>2</sup>C-bus serial interface

I<sup>2</sup>C-bus uses two wires (SDA and SCL) to transfer information between devices connected to the bus, and it has the following features:

- Bidirectional data transfer between masters and slaves.

- Multimaster bus (no central master).

- Arbitration between simultaneously transmitting masters without corruption of serial data on the bus.

- Serial clock synchronization allows devices with different bit rates to communicate via one serial bus.

- Serial clock synchronization can be used as a handshake mechanism to suspend and resume serial transfer.

- The I<sup>2</sup>C-bus may be used for test and diagnostic purposes.

A typical I<sup>2</sup>C-bus configuration is shown in Figure 7. The P89LPC930/931 device provides a byte-oriented I<sup>2</sup>C-bus interface that supports data transfers up to 400 kHz.

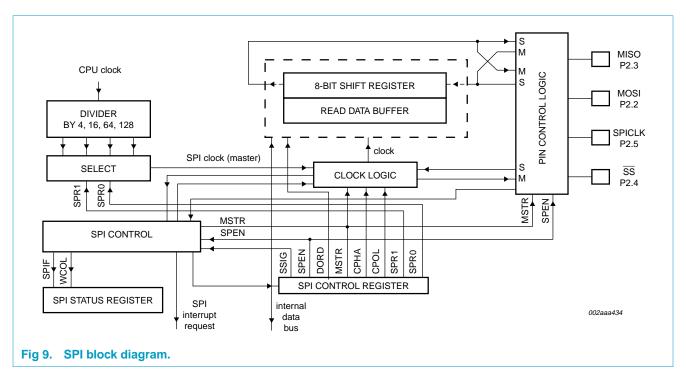

## 8.19 Serial Peripheral Interface (SPI)

LPC930/931 provides another high-speed serial communication interface - the SPI interface. SPI is a full-duplex, high-speed, synchronous communication bus with two operation modes: Master mode and Slave mode. Up to 4.5 Mbit/s can be supported in Master or 3.0 Mbit/s in Slave mode. It has a Transfer Completion Flag and Write Collision Flag Protection.

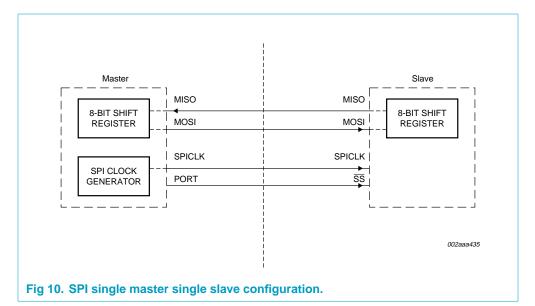

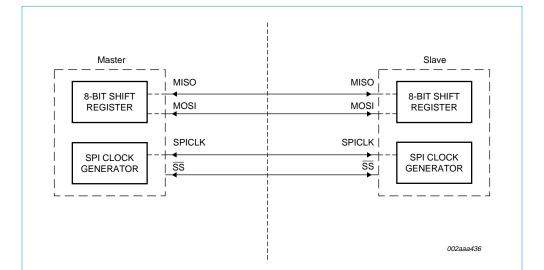

The SPI interface has four pins: SPICLK, MOSI, MISO, and SS:

- SPICLK, MOSI and MISO are typically tied together between two or more SPI devices. Data flows from master to slave on MOSI (Master Out Slave In) pin and flows from slave to master on MISO (Master In Slave Out) pin. The SPICLK signal is output in the master mode and is input in the slave mode. If the SPI system is disabled, i.e. SPEN (SPCTL.6) = 0 (reset value), these pins are configured for port functions.

- SS is the optional slave select pin. In a typical configuration, an SPI master asserts

one of its port pins to select one SPI device as the current slave. An SPI slave

device uses its SS pin to determine whether it is selected.

Typical connections are shown in Figures 10, 11, and 12.

## 8.19.1 Typical SPI configurations

**Table 9: AC characteristics**

$V_{DD}$  = 3.0 V to 3.6 V, unless otherwise specified.

$T_{amb} = -40 \,^{\circ}C$  to +85  $^{\circ}C$  for industrial, unless otherwise specified. [1]

| Symbol              | Parameter                                  | Conditions                    | Variable             | clock                                 | f <sub>osc</sub> = 1 | 8 MHz | Unit |

|---------------------|--------------------------------------------|-------------------------------|----------------------|---------------------------------------|----------------------|-------|------|

|                     |                                            |                               | Min                  | Max                                   | Min                  | Max   |      |

| f <sub>RCOSC</sub>  | internal RC oscillator frequency           |                               | 7.189                | 7.557                                 | 7.189                | 7.557 | MHz  |

| f <sub>WDOSC</sub>  | internal Watchdog oscillator frequency     |                               | 320                  | 520                                   | 320                  | 520   | kHz  |

| f <sub>osc</sub>    | oscillator frequency                       | ]                             | 2] 0                 | 18                                    | -                    | -     | MHz  |

| t <sub>CLCL</sub>   | clock cycle                                | see Figure 20                 | 55                   | -                                     | -                    | -     | ns   |

| f <sub>CLKP</sub>   | CLKLP active frequency                     |                               | 0                    | 8                                     | -                    | -     | MHz  |

| Glitch filte        | er                                         |                               |                      |                                       |                      |       |      |

|                     | glitch rejection, P1.5/RST pin             |                               | -                    | 50                                    | -                    | 50    | ns   |

|                     | signal acceptance, P1.5/RST pin            |                               | 125                  | -                                     | 125                  | -     | ns   |

|                     | glitch rejection, any pin except P1.5/RST  |                               | -                    | 15                                    | -                    | 15    | ns   |

|                     | signal acceptance, any pin except P1.5/RST |                               | 50                   | -                                     | 50                   | -     | ns   |

| External c          | lock                                       |                               |                      |                                       |                      |       |      |

| t <sub>CHCX</sub>   | HIGH time                                  | see Figure 20                 | 22                   | t <sub>CLCL</sub> - t <sub>CLCX</sub> | 22                   | -     | ns   |

| t <sub>CLCX</sub>   | LOW time                                   | see Figure 20                 | 22                   | t <sub>CLCL</sub> – t <sub>CHCX</sub> | 22                   | -     | ns   |

| t <sub>CLCH</sub>   | rise time                                  | see Figure 20                 | -                    | 5                                     | -                    | 5     | ns   |

| t <sub>CHCL</sub>   | fall time                                  | see Figure 20                 | -                    | 5                                     | -                    | 5     | ns   |

| Shift regis         | ster (UART mode 0)                         |                               |                      |                                       |                      |       |      |

| t <sub>XLXL</sub>   | serial port clock cycle time               |                               | 16 t <sub>CLCL</sub> | -                                     | 888                  | -     | ns   |

| t <sub>QVXH</sub>   | output data set-up to clock rising edge    |                               | 13 t <sub>CLCL</sub> | -                                     | 722                  | -     | ns   |

| t <sub>XHQX</sub>   | output data hold after clock rising edge   |                               | -                    | t <sub>CLCL</sub> + 20                | -                    | 75    | ns   |

| t <sub>XHDX</sub>   | input data hold after clock rising edge    |                               | -                    | 0                                     | -                    | 0     | ns   |

| t <sub>DVXH</sub>   | input data valid to clock rising edge      |                               | 150                  | -                                     | 150                  | -     | ns   |

| SPI interfa         | nce                                        |                               |                      |                                       |                      |       |      |

| f <sub>SPI</sub>    | Operating frequency                        |                               |                      |                                       |                      |       |      |

|                     | 3.0 MHz (Slave)                            |                               | 0                    | cclk/6                                | 0                    | 3     | MHz  |

|                     | 4.5 MHz (Master)                           |                               | -                    | CCLK/4                                | -                    | 4.5   | MHz  |

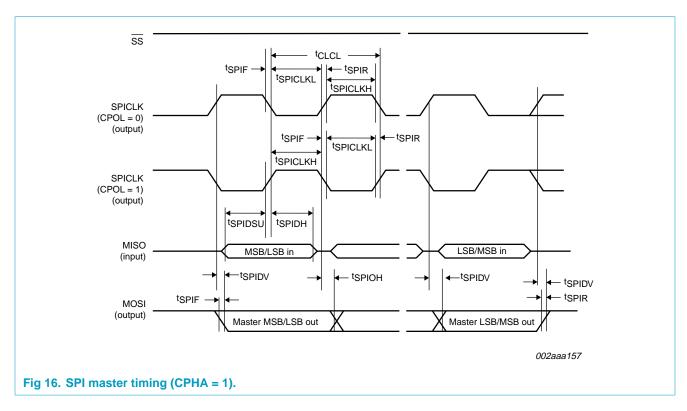

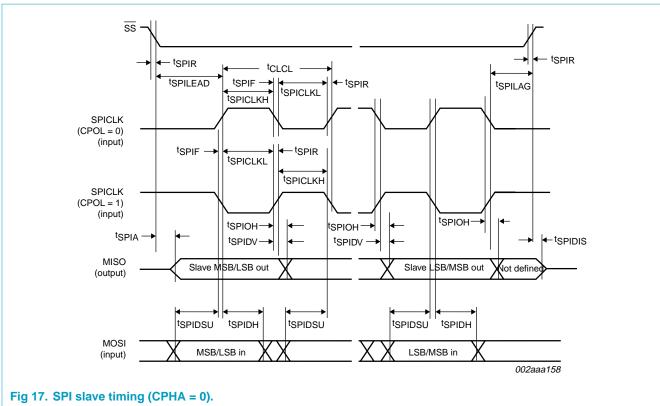

| t <sub>SPICYC</sub> | Cycle time                                 | see Figures<br>15, 16, 17, 18 |                      |                                       |                      |       |      |

|                     | 3.0 MHz (Slave)                            |                               | <sup>6</sup> /CCLK   | -                                     | 333                  | -     | ns   |

|                     | 4.5 MHz (Master)                           |                               | <sup>4</sup> /CCLK   | -                                     | 222                  | -     | ns   |

**Product data**

Table 9:

AC characteristics...continued

$V_{DD}$  = 3.0 V to 3.6 V, unless otherwise specified.

$T_{amb} = -40 \,^{\circ}C$  to +85  $^{\circ}C$  for industrial, unless otherwise specified.[1]

| Symbol               | Parameter                                         | Conditions                    | Variable           | clock | f <sub>osc</sub> = | 18 MHz | Unit |

|----------------------|---------------------------------------------------|-------------------------------|--------------------|-------|--------------------|--------|------|

|                      |                                                   |                               | Min                | Max   | Min                | Max    |      |

| t <sub>SPILEAD</sub> | Enable lead time (Slave)                          | see Figures<br>17, 18         | '                  |       |                    | '      |      |

|                      | 3.0 MHz                                           |                               | 250                | -     | 250                | -      | ns   |

| t <sub>SPILAG</sub>  | Enable lag time (Slave)                           | see Figures<br>17, 18         |                    |       |                    |        |      |

|                      | 3.0 MHz                                           |                               | 250                | -     | 250                | -      | ns   |

| t <sub>SPICLKH</sub> | SPICLK high time                                  | see Figures<br>15, 16, 17, 18 |                    |       |                    |        |      |

|                      | Master                                            |                               | <sup>2</sup> /cclk | -     | 111                | -      | ns   |

|                      | Slave                                             |                               | <sup>3</sup> /cclk | -     | 167                | -      | ns   |

| t <sub>SPICLKL</sub> | SPICLK low time                                   | see Figures<br>15, 16, 17, 18 |                    |       |                    |        |      |

|                      | Master                                            |                               | <sup>2</sup> /cclk | -     | 111                | -      | ns   |

|                      | Slave                                             |                               | <sup>3</sup> ∕cclk | -     | 167                | -      | ns   |

| t <sub>SPIDSU</sub>  | Data set-up time (Master or Slave)                | see Figures<br>15, 16, 17, 18 | 100                | -     | 100                | -      | ns   |

| t <sub>SPIDH</sub>   | Data hold time (Master or Slave)                  | see Figures<br>15, 16, 17, 18 | 100                | -     | 100                | -      | ns   |

| t <sub>SPIA</sub>    | Access time (Slave)                               | see Figures<br>17, 18         | 0                  | 80    | 0                  | 80     | ns   |

| t <sub>SPIDIS</sub>  | Disable time (Slave)                              | see Figures<br>17, 18         |                    |       |                    |        |      |

|                      | 3.0 MHz                                           |                               | 0                  | 160   | -                  | 160    | ns   |

| t <sub>SPIDV</sub>   | Enable to output data valid                       | see Figures<br>15, 16, 17, 18 |                    |       |                    |        |      |

|                      | 3.0 MHz                                           |                               | 0                  | 160   | -                  | 160    | ns   |

|                      | 4.5 MHz                                           |                               | 0                  | 111   | -                  | 111    | ns   |

| t <sub>SPIOH</sub>   | Output data hold time                             | see Figures<br>15, 16, 17, 18 | 0                  | -     | 0                  | -      | ns   |

| t <sub>SPIR</sub>    | Rise time                                         | see Figures<br>15, 16, 17, 18 |                    |       |                    |        |      |

|                      | SPI outputs (SPICLK, MOSI, MISO)                  |                               | -                  | 100   | -                  | 100    | ns   |

|                      | SPI inputs (SPICLK, MOSI, MISO, $\overline{SS}$ ) |                               | -                  | 2000  | -                  | 2000   | ns   |

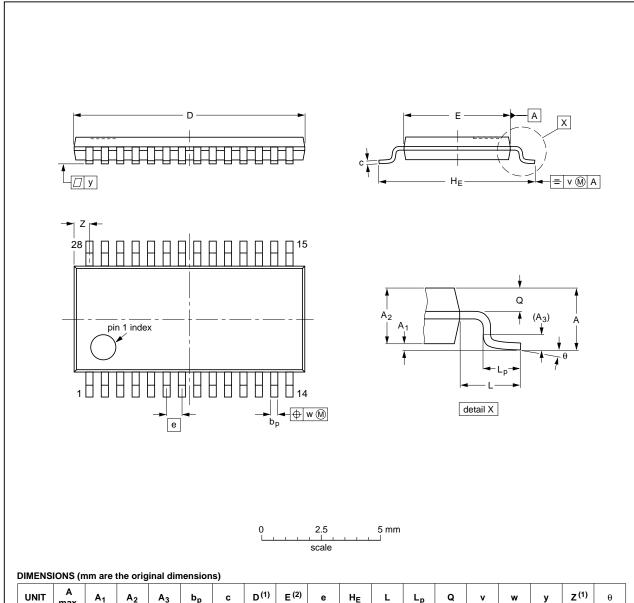

## 13. Package outline

TSSOP28: plastic thin shrink small outline package; 28 leads; body width 4.4 mm

SOT361-1

| UNIT | A<br>max. | A <sub>1</sub> | A <sub>2</sub> | A <sub>3</sub> | bp           | С          | D <sup>(1)</sup> | E <sup>(2)</sup> | е    | HE         | L | Lp           | Q          | v   | w    | у   | Z <sup>(1)</sup> | θ        |

|------|-----------|----------------|----------------|----------------|--------------|------------|------------------|------------------|------|------------|---|--------------|------------|-----|------|-----|------------------|----------|

| mm   | 1.1       | 0.15<br>0.05   | 0.95<br>0.80   | 0.25           | 0.30<br>0.19 | 0.2<br>0.1 | 9.8<br>9.6       | 4.5<br>4.3       | 0.65 | 6.6<br>6.2 | 1 | 0.75<br>0.50 | 0.4<br>0.3 | 0.2 | 0.13 | 0.1 | 0.8<br>0.5       | 8°<br>0° |

#### Notes

- 1. Plastic or metal protrusions of 0.15 mm maximum per side are not included.

- 2. Plastic interlead protrusions of 0.25 mm maximum per side are not included.

| OUTLINE  | OUTLINE REFERENCES |        |       |  | EUROPEAN   | ISSUE DATE                      |

|----------|--------------------|--------|-------|--|------------|---------------------------------|

| VERSION  | IEC                | JEDEC  | JEITA |  | PROJECTION | ISSUE DATE                      |

| SOT361-1 |                    | MO-153 |       |  |            | <del>99-12-27</del><br>03-02-19 |

Fig 22. SOT361-1 (TSSOP28).

### 15. Data sheet status

| Level | Data sheet status <sup>[1]</sup> | Product status <sup>[2][3]</sup> | Definition                                                                                                                                                                                                                                                                                     |

|-------|----------------------------------|----------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| I     | Objective data                   | Development                      | This data sheet contains data from the objective specification for product development. Philips Semiconductors reserves the right to change the specification in any manner without notice.                                                                                                    |

| II    | Preliminary data                 | Qualification                    | This data sheet contains data from the preliminary specification. Supplementary data will be published at a later date. Philips Semiconductors reserves the right to change the specification without notice, in order to improve the design and supply the best possible product.             |

| III   | Product data                     | Production                       | This data sheet contains data from the product specification. Philips Semiconductors reserves the right to make changes at any time in order to improve the design, manufacturing and supply. Relevant changes will be communicated via a Customer Product/Process Change Notification (CPCN). |

- [1] Please consult the most recently issued data sheet before initiating or completing a design.

- [2] The product status of the device(s) described in this data sheet may have changed since this data sheet was published. The latest information is available on the Internet at URL http://www.semiconductors.philips.com.

- [3] For data sheets describing multiple type numbers, the highest-level product status determines the data sheet status.

## 16. Definitions

**Short-form specification** — The data in a short-form specification is extracted from a full data sheet with the same type number and title. For detailed information see the relevant data sheet or data handbook.

Limiting values definition — Limiting values given are in accordance with the Absolute Maximum Rating System (IEC 60134). Stress above one or more of the limiting values may cause permanent damage to the device. These are stress ratings only and operation of the device at these or at any other conditions above those given in the Characteristics sections of the specification is not implied. Exposure to limiting values for extended periods may affect device reliability.

**Application information** — Applications that are described herein for any of these products are for illustrative purposes only. Philips Semiconductors make no representation or warranty that such applications will be suitable for the specified use without further testing or modification.

### 17. Disclaimers

**Life support** — These products are not designed for use in life support appliances, devices, or systems where malfunction of these products can reasonably be expected to result in personal injury. Philips Semiconductors

customers using or selling these products for use in such applications do so at their own risk and agree to fully indemnify Philips Semiconductors for any damages resulting from such application.

Right to make changes — Philips Semiconductors reserves the right to make changes in the products - including circuits, standard cells, and/or software - described or contained herein in order to improve design and/or performance. When the product is in full production (status 'Production'), relevant changes will be communicated via a Customer Product/Process Change Notification (CPCN). Philips Semiconductors assumes no responsibility or liability for the use of any of these products, conveys no licence or title under any patent, copyright, or mask work right to these products, and makes no representations or warranties that these products are free from patent, copyright, or mask work right infringement, unless otherwise specified.

### 18. Licenses

#### Purchase of Philips I<sup>2</sup>C components

Purchase of Philips I<sup>2</sup>C components conveys a license under the Philips' I<sup>2</sup>C patent to use the components in the I<sup>2</sup>C system provided the system conforms to the I<sup>2</sup>C specification defined by Philips. This specification can be ordered using the code 9398 393 40011.

## **Contact information**

For additional information, please visit http://www.semiconductors.philips.com.

For sales office addresses, send e-mail to: sales.addresses@www.semiconductors.philips.com.

Fax: +31 40 27 24825

© Koninklijke Philips Electronics N.V. 2004. All rights reserved.