Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Details                    |                                                                                 |

|----------------------------|---------------------------------------------------------------------------------|

| Product Status             | Active                                                                          |

| Core Processor             | RL78                                                                            |

| Core Size                  | 16-Bit                                                                          |

| Speed                      | 24MHz                                                                           |

| Connectivity               | CSI, I <sup>2</sup> C, LINbus, UART/USART                                       |

| Peripherals                | DMA, LCD, LVD, POR, PWM, WDT                                                    |

| Number of I/O              | 20                                                                              |

| Program Memory Size        | 8KB (8K x 8)                                                                    |

| Program Memory Type        | FLASH                                                                           |

| EEPROM Size                | 2K x 8                                                                          |

| RAM Size                   | 1K x 8                                                                          |

| Voltage - Supply (Vcc/Vdd) | 1.6V ~ 5.5V                                                                     |

| Data Converters            | A/D 4x8/10b                                                                     |

| Oscillator Type            | Internal                                                                        |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                               |

| Mounting Type              | Surface Mount                                                                   |

| Package / Case             | 32-LQFP                                                                         |

| Supplier Device Package    | 32-LQFP (7x7)                                                                   |

| Purchase URL               | https://www.e-xfl.com/product-detail/renesas-electronics-america/r5f10rb8afp-30 |

|                            |                                                                                 |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

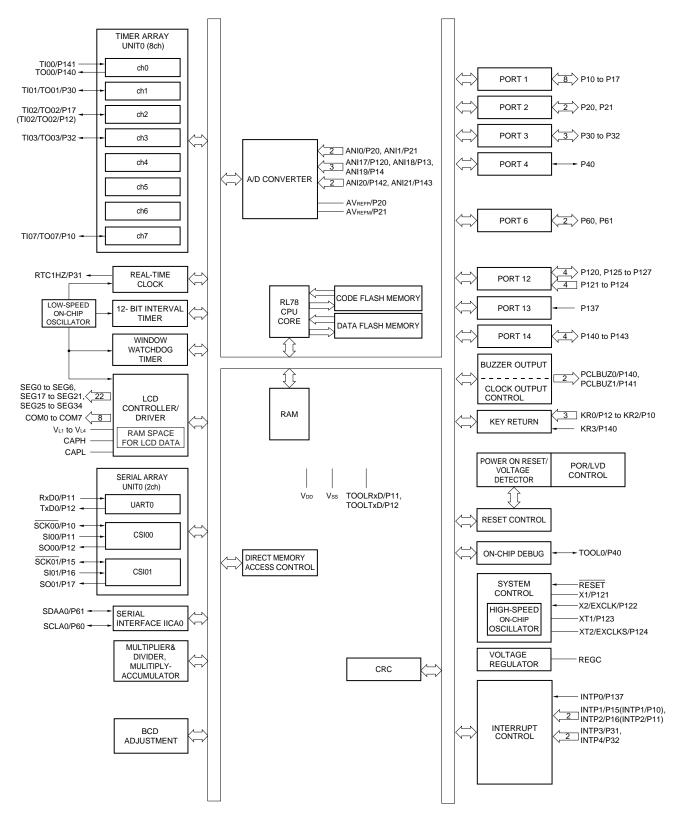

### O ROM, RAM capacities

| Flash ROM | Data flash | RAM                    |          |          | RL78/L12 |          |          |

|-----------|------------|------------------------|----------|----------|----------|----------|----------|

|           |            |                        | 32 pins  | 44 pins  | 48 pins  | 52 pins  | 64 pins  |

| 32 KB     | 2 KB       | 1.5 KB <sup>Note</sup> | R5F10RBC | R5F10RFC | R5F10RGC | R5F10RJC | R5F10RLC |

| 16 KB     |            | 1 KB <sup>Note</sup>   |          | R5F10RFA | R5F10RGA | R5F10RJA | R5F10RLA |

| 8KB       | 2 KB       | 1 KB <sup>Note</sup>   | R5F10RB8 | R5F10RF8 | R5F10RG8 | R5F10RJ8 | -        |

**Note** In the case of the 1 KB, and 1.5 KB, this is 630 bytes when the self-programming function and data flash function is used.

Remark The functions mounted depend on the product. See 1.6 Outline of Functions.

- 64-pin plastic LQFP (fine pitch)  $(10 \times 10)$

- 64-pin plastic LQFP (12 × 12)

<R>

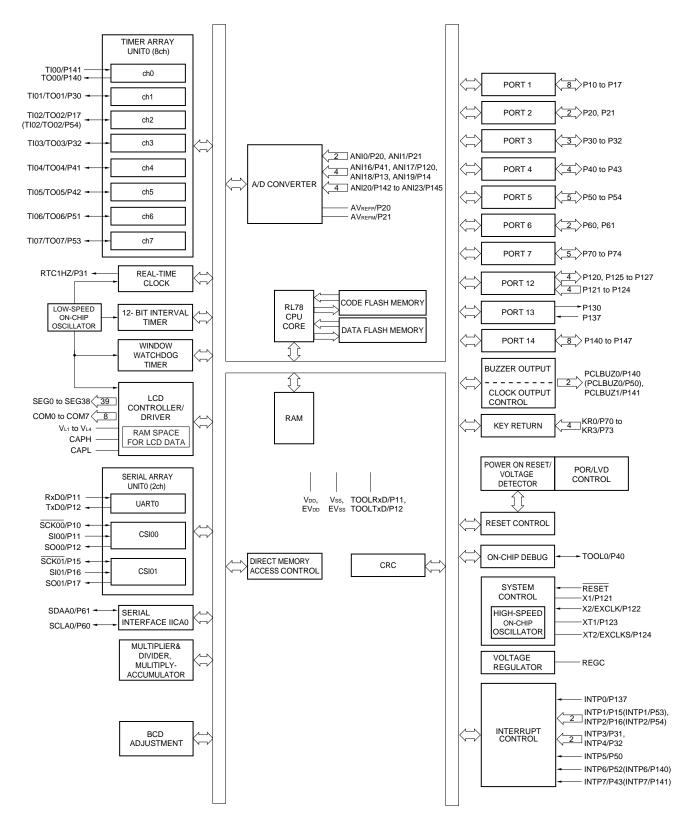

Cautions 1. Make EVss pin the same potential as Vss pin.

- 2. Make VDD pin the same potential as EVDD pin.

- 3. Connect the REGC pin to Vss via a capacitor (0.47 to 1  $\mu$ F).

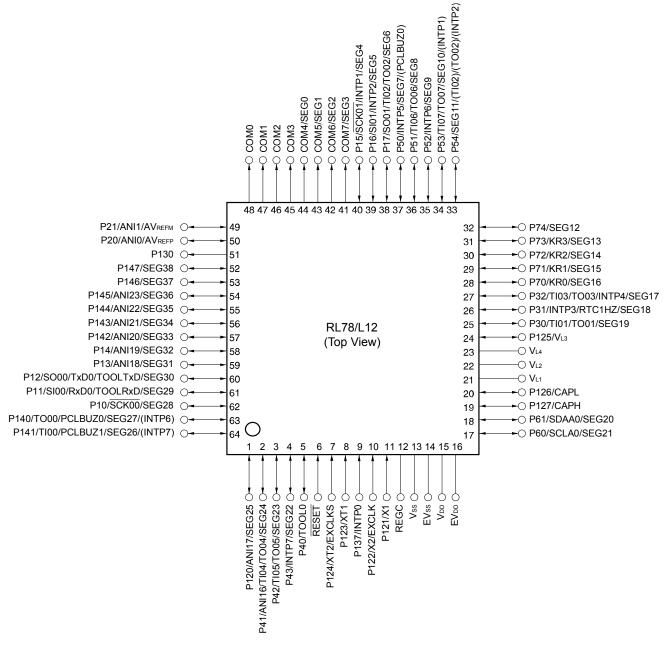

- Remarks 1. For pin identification, see 1.4 Pin Identification.

- 2. When using the microcontroller for an application where the noise generated inside the microcontroller must be reduced, it is recommended to supply separate powers to the V<sub>DD</sub> and EV<sub>DD</sub> pins and connect the V<sub>SS</sub> and EV<sub>SS</sub> pins to separate ground lines.

- **3.** Functions in parentheses in the above figure can be assigned via settings in the peripheral I/O redirection register (PIOR).

RENESAS

# 1.4 Pin Identification

| ANI0, ANI1,     |                        | P130, P137:       | Port 13                                |

|-----------------|------------------------|-------------------|----------------------------------------|

| ANI16 to ANI23: | Analog Input           | P140 to P147:     | Port 14                                |

| AVREFM:         | Analog Reference       | PCLBUZ0, PCLBUZ1: | Programmable Clock                     |

|                 | Voltage Minus          |                   | Output/Buzzer Output                   |

| AVREFP:         | Analog Reference       | REGC:             | Regulator Capacitance                  |

|                 | Voltage Plus           | RESET:            | Reset                                  |

| CAPH, CAPL:     | Capacitor for LCD      | RTC1HZ:           | Real-time Clock Correction Clock       |

| COM0 to COM7,   |                        |                   | (1 Hz) Output                          |

| EVDD:           | Power Supply for Port  | RxD0:             | Receive Data                           |

| EVss:           | Ground for Port        | SCK00, SCK01:     | Serial Clock Input/Output              |

| EXCLK:          | External Clock Input   | SCLA0:            | Serial Clock Input/Output              |

|                 | (Main System Clock)    | SDAA0:            | Serial Data Input/Output               |

| EXCLKS:         | External Clock Input   | SEG0 to SEG38:    | LCD Segment Output                     |

|                 | (Subsystem Clock)      | SI00, SI01:       | Serial Data Input                      |

| INTP0 to INTP7: | Interrupt Request From | SO00, SO01:       | Serial Data Output                     |

|                 | Peripheral             | TI00 to TI07:     | Timer Input                            |

| KR0 to KR3:     | Key Return             | TO00 to TO07:     | Timer Output                           |

| P10 to P17:     | Port 1                 | TOOL0:            | Data Input/Output for Tool             |

| P20, P21:       | Port 2                 | TOOLRxD, TOOLTxD: | Data Input/Output for External Device  |

| P30 to P32:     | Port 3                 | TxD0:             | Transmit Data                          |

| P40 to P43:     | Port 4                 | VDD:              | Power Supply                           |

| P50 to P54:     | Port 5                 | VL1 to VL4:       | LCD Power Supply                       |

| P60, P61:       | Port 6                 | Vss:              | Ground                                 |

| P70 to P74:     | Port 7                 | X1, X2:           | Crystal Oscillator (Main System Clock) |

| P120 to P127:   | Port 12                | XT1, XT2:         | Crystal Oscillator (Subsystem Clock)   |

## 1.5.2 44-pin products

**Remark** Functions in parentheses in the above figure can be assigned via settings in the peripheral I/O redirection register (PIOR)

RENESAS

# 1.5.5 64-pin products

**Remark** Functions in parentheses in the above figure can be assigned via settings in the peripheral I/O redirection register (PIOR)

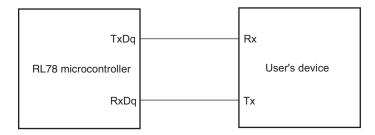

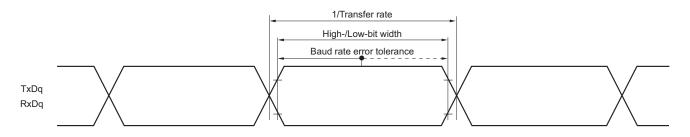

### UART mode connection diagram (during communication at same potential)

### UART mode bit width (during communication at same potential) (reference)

**Remarks 1.** q: UART number (q = 0), g: PIM and POM number (g = 1)

fMCK: Serial array unit operation clock frequency (Operation clock to be set by the serial clock select register m (SPSm) and the CKSmn bit of serial mode register mn (SMRmn). m: Unit number, n: Channel number (mn = 00, 01))

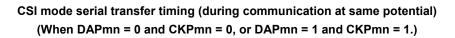

### (2) During communication at same potential (CSI mode) (master mode, SCKp... internal clock output) (T<sub>A</sub> = -40 to +85°C, 1.6 V ≤ EV<sub>DD</sub> = V<sub>DD</sub> ≤ 5.5 V, V<sub>SS</sub> = EV<sub>SS</sub> = 0 V)

| Parameter                               | Symbol        | (                                      | Conditions                             | • •             | h-speed<br>Mode |                 | v-speed<br>Mode |                  | -voltage<br>Mode | Unit |

|-----------------------------------------|---------------|----------------------------------------|----------------------------------------|-----------------|-----------------|-----------------|-----------------|------------------|------------------|------|

|                                         |               |                                        |                                        | MIN.            | MAX.            | MIN.            | MAX.            | MIN.             | MAX.             |      |

| SCKp cycle time                         | tkcy1         | 2.7 V ≤ EV                             | $V_{\text{DD}} \leq 5.5 \text{ V}$     | 167<br>Note 1   |                 | 500<br>Note 1   |                 | 1000<br>Note 1   |                  | ns   |

|                                         |               | 2.4 V ≤ EV                             | $I_{\text{DD}} \leq 5.5 \text{ V}$     | 250<br>Note 1   |                 | 500<br>Note 1   |                 | 1000<br>Note 1   |                  | ns   |

|                                         |               | 1.8 V ≤ EV                             | $V_{\text{DD}} \leq 5.5 \text{ V}$     |                 |                 | 500<br>Note 1   |                 | 1000<br>Note 1   |                  | ns   |

|                                         |               | 1.6 V ≤ EV                             | $V_{\text{DD}} \leq 5.5 \text{ V}$     |                 |                 |                 |                 | 1000<br>Note 1   |                  | ns   |

| SCKp high-/low-level width              | tкн1,<br>tк∟1 | 4.0 V ≤ EV                             | $V_{\text{DD}} \leq 5.5 \text{ V}$     | tксү1/2<br>– 12 |                 | tксү1/2<br>- 50 |                 | tксү1/2<br>- 50  |                  | ns   |

|                                         |               | 2.7 V ≤ EV                             | $V_{\text{DD}} \leq 5.5 \text{ V}$     | tксү1/2<br>– 18 |                 | tксү1/2<br>- 50 |                 | tксү1/2<br>- 50  |                  | ns   |

|                                         |               | 2.4 V ≤ E\                             | $V_{\text{DD}} \leq 5.5 \text{ V}$     | tксү1/2<br>– 38 |                 | tксү1/2<br>– 50 |                 | tксү1/2<br>- 50  |                  | ns   |

|                                         |               | 1.8 V ≤ E\                             | $V_{\text{DD}} \leq 5.5 \text{ V}$     |                 |                 | tксү1/2<br>– 50 |                 | tксү1/2<br>- 50  |                  | ns   |

|                                         |               | $1.6~V \leq EV_{\text{DD}} \leq 5.5~V$ |                                        |                 |                 |                 |                 | tксү1/2<br>- 100 |                  | ns   |

| SIp setup time (to SCKp↑)<br>Note 2     | tsik1         | 2.7 V ≤ EV                             | $I_{\text{DD}} \leq 5.5 \text{ V}$     | 44              |                 | 110             |                 | 110              |                  | ns   |

| Note 2                                  |               | 2.4 V ≤ EV                             | $I_{\text{DD}} \leq 5.5 \text{ V}$     | 75              |                 | 110             |                 | 110              |                  | ns   |

|                                         |               | 1.8 V ≤ EV                             | $I_{DD} \leq 5.5 \text{ V}$            |                 |                 | 110             |                 | 110              |                  | ns   |

|                                         |               | 1.6 V ≤ EV                             | $V_{\text{DD}} \leq 5.5 \text{ V}$     |                 |                 |                 |                 | 220              |                  | ns   |

| SIp hold time (from SCKp <sup>↑</sup> ) | <b>t</b> KSI1 | $2.4 \text{ V} \le \text{EV}$          | $I_{\text{DD}} \leq 5.5 \text{ V}$     | 19              |                 | 19              |                 | 19               |                  | ns   |

| NOLE J                                  |               | 1.8 V ≤ EV                             | $I_{\text{DD}} \leq 5.5 \text{ V}$     |                 |                 | 19              |                 | 19               |                  |      |

|                                         |               | 1.6 V ≤ EV                             | $V_{DD} \leq 5.5 \text{ V}$            |                 |                 |                 |                 | 19               |                  |      |

| Delay time from SCKp↓ to                | <b>t</b> KSO1 |                                        | $2.4~V \leq EV_{\text{DD}} \leq 5.5~V$ |                 | 25              |                 | 25              |                  | 25               | ns   |

| SOp output Note 4                       |               | Note 5                                 | $1.8~V \le EV_{\text{DD}} \le 5.5~V$   |                 |                 |                 | 25              |                  | 25               |      |

|                                         |               |                                        | $1.6~V \le EV_{\text{DD}} \le 5.5~V$   |                 |                 |                 |                 |                  | 25               |      |

Notes 1. For CSI00, set a cycle of 2/fмск or longer. For CSI01, set a cycle of 4/fмск or longer.

- **2.** When DAPmn = 0 and CKPmn = 0, or DAPmn = 1 and CKPmn = 1. The SIp setup time becomes "to SCKp↓" when DAPmn = 0 and CKPmn = 1, or DAPmn = 1 and CKPmn = 0.

- **3.** When DAPmn = 0 and CKPmn = 0, or DAPmn = 1 and CKPmn = 1. The SIp hold time becomes "from SCKp↓" when DAPmn = 0 and CKPmn = 1, or DAPmn = 1 and CKPmn = 0.

- **4.** When DAPmn = 0 and CKPmn = 0, or DAPmn = 1 and CKPmn = 1. The delay time to SOp output becomes "from SCKp<sup>↑</sup>" when DAPmn = 0 and CKPmn = 1, or DAPmn = 1 and CKPmn = 0.

- **5.** C is the load capacitance of the SCKp and SOp output lines.

- Caution Select the normal input buffer for the SIp pin and the normal output mode for the SOp pin and SCKp pin by using port input mode register g (PIMg) and port output mode register g (POMg).

(Remarks are listed on the next page.)

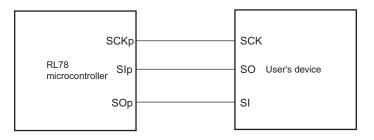

CSI mode connection diagram (during communication at same potential)

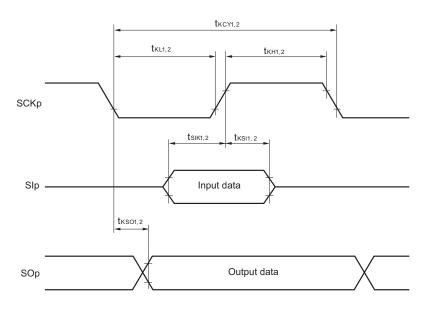

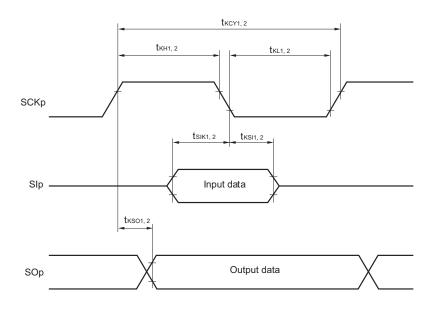

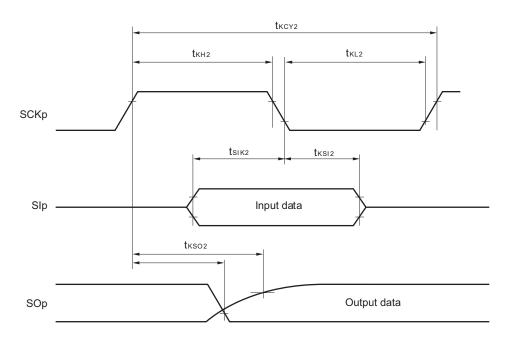

CSI mode serial transfer timing (during communication at same potential) (When DAPmn = 0 and CKPmn = 1, or DAPmn = 1 and CKPmn = 0.)

**2.** m: Unit number, n: Channel number (mn = 00, 01)

## (4) Communication at different potential (1.8 V, 2.5 V, 3 V) (UART mode)

$(T_A = -40 \text{ to } +85^{\circ}C, 1.8 \text{ V} \le EV_{DD} = V_{DD} \le 5.5 \text{ V}, \text{ Vss} = EV_{SS} = 0 \text{ V})$

(2/2)

| Parameter     | Symbol |                  | Conditions                                                   |                                                                                                                                                                                                                           |  | h-speed<br>Mode        | -    | w-speed<br>) Mode      | -    | v-voltage<br>) Mode    | Unit |

|---------------|--------|------------------|--------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|------------------------|------|------------------------|------|------------------------|------|

|               |        |                  |                                                              |                                                                                                                                                                                                                           |  | MAX.                   | MIN. | MAX.                   | MIN. | MAX.                   |      |

| Transfer rate |        | Transmissio<br>n | $4.0 V \le EV_{DD} \le 5.5 V$ ,<br>$2.7 V \le V_b \le 4.0 V$ |                                                                                                                                                                                                                           |  | Note 1                 |      | Note 1                 |      | Note 1                 | bps  |

|               |        |                  |                                                              | $\label{eq:constraint} \begin{array}{l} Theoretical value of the \\ maximum transfer rate \\ C_b = 50 \ pF, \ R_b = 1.4 \ k\Omega, \\ V_b = 2.7 \ V \end{array}$                                                          |  | 2.8 <sup>Note 2</sup>  |      | 2.8 <sup>Note 2</sup>  |      | 2.8 <sup>Note 2</sup>  | Mbps |

|               |        |                  |                                                              | EVdd < 4.0 V,<br>∕⊳≤2.7 V                                                                                                                                                                                                 |  | Note 3                 |      | Note 3                 |      | Note 3                 | bps  |

|               |        |                  |                                                              | $\label{eq:constraint} \begin{array}{l} \mbox{Theoretical value of the} \\ \mbox{maximum transfer rate} \\ \mbox{C}_{b} = 50 \mbox{ pF}, \mbox{ R}_{b} = 2.7 \mbox{ k}\Omega \\ \mbox{V}_{b} = 2.3 \mbox{ V} \end{array}$ |  | 1.2 <sup>Note 4</sup>  |      | 1.2 <sup>Note 4</sup>  |      | 1.2 <sup>Note 4</sup>  | Mbps |

|               |        |                  |                                                              | EVdd < 3.3 V,<br>/₅≤2.0 V                                                                                                                                                                                                 |  | Note 6                 |      | Note 6                 |      | Note 6                 | bps  |

|               |        |                  |                                                              | Theoretical value of the maximum transfer rate $C_b$ = 50 pF, $R_b$ = 5.5 k $\Omega$ $V_b$ = 1.6 V                                                                                                                        |  | 0.43 <sup>Note 7</sup> |      | 0.43 <sup>Note 7</sup> |      | 0.43 <sup>Note 7</sup> | Mbps |

|               |        |                  |                                                              | EVdd < 3.3 V,<br>/b ≤ 2.0 V                                                                                                                                                                                               |  |                        |      | Notes<br>5, 6          |      | Notes<br>5, 6          | bps  |

|               |        |                  |                                                              | Theoretical value of the maximum transfer rate $C_b$ = 50 pF, $R_b$ = 5.5 k $\Omega$ , $V_b$ = 1.6 V                                                                                                                      |  |                        |      | 0.43 <sup>Note 7</sup> |      | 0.43 <sup>Note 7</sup> | Mbps |

**Notes 1.** The smaller maximum transfer rate derived by using fMCK/6 or the following expression is the valid maximum transfer rate.

Expression for calculating the transfer rate when 4.0 V  $\leq$  EV\_{DD}  $\leq$  5.5 V and 2.7 V  $\leq$  V\_b  $\leq$  4.0 V

Maximum transfer rate =

$$\frac{1}{\{-C_b \times R_b \times \ln (1 - \frac{2.2}{V_b})\} \times 3}$$

[bps]

Baud rate error (theoretical value) =

$$\frac{\frac{1}{\text{Transfer rate} \times 2} - \{-C_b \times R_b \times \ln(1 - \frac{2.2}{V_b})\}}{(\frac{1}{\text{Transfer rate}}) \times \text{Number of transferred bits}} \times 100 [\%]$$

\* This value is the theoretical value of the relative difference between the transmission and reception sides.

**2.** This value as an example is calculated when the conditions described in the "Conditions" column are met. Refer to Note 1 above to calculate the maximum transfer rate under conditions of the customer.

| Parameter                                       | Symbol        | Con                                                                                                                        | Conditions                                                                                                                       |                  |                 | main)           | /-speed<br>mode | voltage<br>mo   | (low-<br>e main)<br>ode | Unit |

|-------------------------------------------------|---------------|----------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------|------------------|-----------------|-----------------|-----------------|-----------------|-------------------------|------|

|                                                 |               |                                                                                                                            |                                                                                                                                  | MIN.             | MAX.            | MIN.            | MAX.            | MIN.            | MAX.                    |      |

| SCKp cycle time Note 1                          | <b>t</b> ксү2 | $4.0 V \le EV_{DD} \le 5.5 V$ ,                                                                                            | 20 MHz < fмск ≤ 24 MHz                                                                                                           | 12/fмск          |                 |                 |                 |                 |                         | ns   |

|                                                 |               | $2.7 V \le V_b \le 4.0 V$                                                                                                  | 8 MHz < fмск ≤ 20 MHz                                                                                                            | 10/ <b>f</b> мск |                 |                 |                 |                 |                         | ns   |

|                                                 |               |                                                                                                                            | 4 MHz < fмск ≤ 8 MHz                                                                                                             | 8/fмск           |                 | 16/fмск         |                 |                 |                         | ns   |

|                                                 |               |                                                                                                                            | fмск≤4 MHz                                                                                                                       | 6/fмск           |                 | <b>10/f</b> мск |                 | 10/fмск         |                         | ns   |

|                                                 |               | $2.7 \text{ V} \le \text{EV}_{\text{DD}} < 4.0 \text{ V},$                                                                 | $20 \text{ MHz} < f_{MCK} \le 24 \text{ MHz}$                                                                                    | 16/ <b>f</b> мск |                 |                 |                 |                 |                         | ns   |

|                                                 |               | $2.3 V \le V_b \le 2.7 V$                                                                                                  | $16 \text{ MHz} < f_{\text{MCK}} \le 20 \text{ MHz}$                                                                             | 14/ <b>f</b> мск |                 |                 |                 |                 |                         | ns   |

|                                                 |               |                                                                                                                            | $8 \text{ MHz} < f_{\text{MCK}} \le 16 \text{ MHz}$                                                                              | 12/fмск          |                 |                 |                 |                 |                         | ns   |

|                                                 |               |                                                                                                                            | 4 MHz < fмск ≤ 8 MHz                                                                                                             | 8/fмск           |                 | 16/fмск         |                 |                 |                         | ns   |

|                                                 |               |                                                                                                                            | fмск ≤4 MHz                                                                                                                      | 6/ <b>f</b> мск  |                 | 10/fмск         |                 | 10/fмск         |                         | ns   |

|                                                 |               | $2.4 \text{ V} \le \text{EV}_{\text{DD}} < 3.3 \text{ V},$                                                                 | 20 MHz < fмск ≤ 24 MHz                                                                                                           | 36/fмск          |                 |                 |                 |                 |                         | ns   |

|                                                 |               | $1.6  V {\leq} V_b {\leq} 2.0  V$                                                                                          | 16 MHz < fмск ≤ 20 MHz                                                                                                           | 32/fмск          |                 |                 |                 |                 |                         | ns   |

|                                                 |               |                                                                                                                            | 8 MHz < fмск ≤ 16 MHz                                                                                                            | 26/fмск          |                 |                 |                 |                 |                         | ns   |

|                                                 |               |                                                                                                                            | 4 MHz < fмск ≤ 8 MHz                                                                                                             | 16/fмск          |                 | 16/fмск         |                 |                 |                         | ns   |

|                                                 |               | $\begin{array}{l} 1.8 \ V \leq E V_{DD} < 3.3 \ V, \\ 1.6 \ V \leq V_b \leq 2.0 \ V^{\text{Note 2}} \end{array}$           | fмcк≤4 MHz                                                                                                                       | 10/fмск          |                 | 10/fмск         |                 | <b>10/f</b> мск |                         | ns   |

|                                                 |               |                                                                                                                            | 4 MHz < fмск ≤ 8 MHz                                                                                                             |                  |                 | <b>16/f</b> мск |                 |                 |                         | ns   |

|                                                 |               |                                                                                                                            | fмск≤4 MHz                                                                                                                       |                  |                 | 10/fмск         |                 | 10/fмск         |                         | ns   |

| SCKp high-/low-level width                      | tкн2,<br>tкL2 | $4.0 \ V \leq EV_{DD} \leq 5.5 \ V, \ 2.7 \ V \leq V_b \leq 4.0 \ V$                                                       |                                                                                                                                  |                  |                 | tксү2/2<br>- 50 |                 | tксү2/2<br>- 50 |                         | ns   |

|                                                 |               | $2.7 \text{ V} \le \text{EV}_{\text{DD}} < 4.0 \text{ V}$                                                                  | tксү2/2<br>– 18                                                                                                                  |                  | tксү2/2<br>- 50 |                 | tксү2/2<br>- 50 |                 | ns                      |      |

|                                                 |               | $2.4 \text{ V} \le \text{EV}_{\text{DD}} < 3.3 \text{ V}$                                                                  | tксү2/2<br>- 50                                                                                                                  |                  | tксү2/2<br>- 50 |                 | tксү2/2<br>- 50 |                 | ns                      |      |

|                                                 |               | $1.8 V \le EV_{DD} < 3.3 V$<br>$1.6 V \le V_b \le 2.0 V^{No}$                                                              | $1.8 \text{ V} \le \text{EV}_{\text{DD}} < 3.3 \text{ V},$<br>$1.6 \text{ V} \le V_{\text{b}} \le 2.0 \text{ V}^{\text{Note 2}}$ |                  |                 | tксү2/2<br>- 50 |                 | tксү2/2<br>- 50 |                         | ns   |

| SIp setup time<br>(to SCKp↑) <sup>Note 3</sup>  | tsık2         | $4.0 \text{ V} \le \text{EV}_{\text{DD}} < 5.5 \text{ V}$                                                                  | $V, 2.7 V \le V_b \le 4.0 V$                                                                                                     | 1/fмск +<br>20   |                 | 1/fмск +<br>30  |                 | 1/fмск +<br>30  |                         | ns   |

|                                                 |               | $2.7 \text{ V} \le \text{EV}_{\text{DD}} < 4.0 \text{ V}$                                                                  | $V, 2.3 V \le V_b \le 2.7 V$                                                                                                     | 1/fмск +<br>20   |                 | 1/fмск +<br>30  |                 | 1/fмск +<br>30  |                         | ns   |

|                                                 |               | $2.4 \text{ V} \le \text{EV}_{\text{DD}} < 3.3 \text{ V}$                                                                  | $V_{\rm r}, 1.6 \ V \le V_{\rm b} \le 2.0 \ V_{\rm b}$                                                                           | 1/fмск +<br>30   |                 | 1/fмск +<br>30  |                 | 1/fмск +<br>30  |                         | ns   |

|                                                 |               | $\begin{array}{l} 1.8 \ V \leq EV_{\text{DD}} < 3.3 \ V \\ 1.6 \ V \leq V_{\text{b}} \leq 2.0 \ V^{\text{No}} \end{array}$ |                                                                                                                                  |                  |                 | 1/fмск +<br>30  |                 | 1/fмск +<br>30  |                         | ns   |

| SIp hold time<br>(from SCKp↑) <sup>Note 4</sup> | tksi2         | $4.0 \text{ V} \le \text{EV}_{\text{DD}} < 5.5 \text{ V}$                                                                  | $V, 2.7 V \le V_b \le 4.0 V$                                                                                                     | 1/fмск +<br>31   |                 | 1/fмск +<br>31  |                 | 1/fмск +<br>31  |                         | ns   |

|                                                 |               | $2.7 \text{ V} \le \text{EV}_{\text{DD}} < 4.0 \text{ V}$                                                                  | $V, 2.3 V \le V_b \le 2.7 V$                                                                                                     | 1/fмск +<br>31   |                 | 1/fмск +<br>31  |                 | 1/fмск +<br>31  |                         | ns   |

|                                                 |               | $2.4 \text{ V} \le \text{EV}_{\text{DD}} < 3.3 \text{ V}$                                                                  | $V, 1.6 V \le V_b \le 2.0 V$                                                                                                     | 1/fмск +<br>31   |                 | 1/fмск +<br>31  |                 | 1/fмск +<br>31  |                         | ns   |

|                                                 |               | $\begin{array}{l} 1.8 \ V \leq EV_{DD} < 3.3 \ V \\ 1.6 \ V \leq V_b \leq 2.0 \ V^{\text{No}} \end{array}$                 |                                                                                                                                  |                  |                 | 1/fмск +<br>31  |                 | 1/fмск +<br>31  |                         | ns   |

(7) Communication at different potential (1.8 V, 2.5 V, 3 V) (CSI mode) (slave mode, SCKp... external clock input)

(Notes, Caution and Remarks are listed on the next page.)

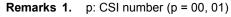

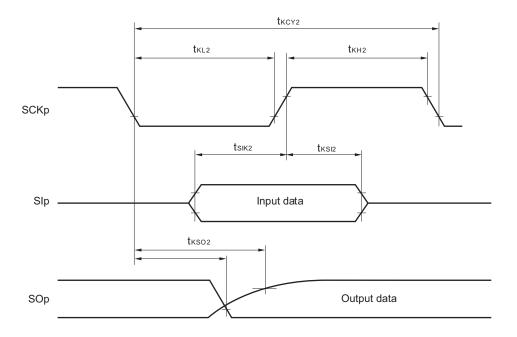

## CSI mode serial transfer timing (slave mode) (during communication at different potential) (When DAPmn = 0 and CKPmn = 0, or DAPmn = 1 and CKPmn = 1.)

**Remark** p: CSI number (p = 00, 01), m: Unit number (m = 0), n: Channel number (n = 0, 1), g: PIM and POM number (g = 1)

## (2) I<sup>2</sup>C fast mode

### (TA = -40 to +85°C, 1.6 V $\leq$ EV<sub>DD</sub> = V<sub>DD</sub> $\leq$ 5.5 V, V<sub>SS</sub> = EV<sub>SS</sub> = 0 V)

| Parameter                                       | Symbol        | (                                          | Conditions                             |      |      |      | /-speed<br>Mode | voltage | low-<br>e main)<br>ode | Unit |

|-------------------------------------------------|---------------|--------------------------------------------|----------------------------------------|------|------|------|-----------------|---------|------------------------|------|

|                                                 |               |                                            |                                        | MIN. | MAX. | MIN. | MIN.            | MAX.    | MIN.                   |      |

| SCLA0 clock frequency                           | fscl          | Fast mode:                                 | $2.7~V \leq EV_{\text{DD}} \leq 5.5~V$ | 0    | 400  | 0    | 400             | 0       | 400                    | kHz  |

|                                                 |               | fclк≥ 3.5                                  | $2.4~V \le EV_{\text{DD}} \le 5.5~V$   | 0    | 400  | 0    | 400             | 0       | 400                    |      |

|                                                 |               | MHz                                        | $1.8~V \le EV_{\text{DD}} \le 5.5~V$   |      |      | 0    | 400             | 0       | 400                    |      |

| Setup time of restart condition                 | tsu:sta       | $2.7 \; V \leq EV_{\text{DD}}$             | ≤ 5.5 V                                | 0.6  |      | 0.6  |                 | 0.6     |                        | μs   |

|                                                 |               | $2.4~V \leq EV_{\text{DD}}$                | ≤ 5.5 V                                | 0.6  |      | 0.6  |                 | 0.6     |                        |      |

|                                                 |               | $1.8 \text{ V} \leq EV_{\text{DD}}$        | ≤ 5.5 V                                |      |      | 0.6  |                 | 0.6     |                        |      |

| Hold time Note 1                                | thd:sta       | $2.7~V \leq EV_{\text{DD}}$                | ≤ 5.5 V                                | 0.6  |      | 0.6  |                 | 0.6     |                        | μs   |

|                                                 |               | $2.4 \text{ V} \leq EV_{\text{DD}}$        | ≤ 5.5 V                                | 0.6  |      | 0.6  |                 | 0.6     |                        |      |

|                                                 |               | $1.8 \text{ V} \leq EV_{\text{DD}}$        | ≤ 5.5 V                                |      |      | 0.6  |                 | 0.6     |                        |      |

| Hold time when SCLA0 = "L"                      | tLOW          | $2.7 \text{ V} \leq EV_{\text{DD}}$        | ≤ 5.5 V                                | 1.3  |      | 1.3  |                 | 1.3     |                        | μs   |

|                                                 |               | $2.4~V \leq EV_{\text{DD}}$                | ≤ 5.5 V                                | 1.3  |      | 1.3  |                 | 1.3     |                        |      |

|                                                 |               | $1.8 \ V \leq EV_{\text{DD}}$              | ≤ 5.5 V                                |      |      | 1.3  |                 | 1.3     |                        |      |

| Hold time when SCLA0 = "H"                      | <b>t</b> HIGH | $2.7 \; V \leq EV_{\text{DD}}$             | ≤ 5.5 V                                | 0.6  |      | 0.6  |                 | 0.6     |                        | μs   |

|                                                 |               | $2.4~V \leq EV_{\text{DD}}$                | ≤ 5.5 V                                | 0.6  |      | 0.6  |                 | 0.6     |                        |      |

|                                                 |               | $1.8 \ V \leq EV_{\text{DD}}$              | ≤ 5.5 V                                |      |      | 0.6  |                 | 0.6     |                        |      |

| Data setup time (reception)                     | tsu:dat       | $2.7 \text{ V} \leq \text{EV}_{\text{DD}}$ | ≤ 5.5 V                                | 100  |      | 100  |                 | 100     |                        | ns   |

|                                                 |               | $2.4~V \leq EV_{\text{DD}}$                | ≤ 5.5 V                                | 100  |      | 100  |                 | 100     |                        |      |

|                                                 |               | $1.8 \ V \leq EV_{\text{DD}}$              | ≤ 5.5 V                                |      |      | 100  |                 | 100     |                        |      |

| Data hold time (transmission) <sup>Note 2</sup> | thd:dat       | $2.7 \text{ V} \leq \text{EV}_{\text{DD}}$ | ≤ 5.5 V                                | 0    | 0.9  | 0    | 0.9             | 0       | 0.9                    | μs   |

|                                                 |               | $2.4~V \leq EV_{\text{DD}}$                | ≤ 5.5 V                                | 0    | 0.9  | 0    | 0.9             | 0       | 0.9                    |      |

|                                                 |               | $1.8 \text{ V} \leq EV_{DD}$               | ≤ 5.5 V                                |      |      | 0    | 0.9             | 0       | 0.9                    |      |

| Setup time of stop condition                    | tsu:sto       | $2.7 \; V \leq EV_{\text{DD}}$             | ≤ 5.5 V                                | 0.6  |      | 0.6  |                 | 0.6     |                        | μs   |

|                                                 |               | $2.4~V \leq EV_{\text{DD}}$                | ≤ 5.5 V                                | 0.6  |      | 0.6  |                 | 0.6     |                        |      |

|                                                 |               | $1.8 \text{ V} \leq EV_{\text{DD}}$        | ≤ 5.5 V                                |      |      | 0.6  |                 | 0.6     |                        |      |

| Bus-free time                                   | <b>t</b> BUF  | $2.7 \text{ V} \leq EV_{\text{DD}}$        | ≤ 5.5 V                                | 1.3  |      | 1.3  |                 | 1.3     |                        | μs   |

|                                                 |               | $2.4~V \leq EV_{\text{DD}}$                | ≤ 5.5 V                                | 1.3  |      | 1.3  |                 | 1.3     |                        |      |

|                                                 |               | $1.8 \text{ V} \leq EV_{DD}$               | ≤ 5.5 V                                |      |      | 1.3  |                 | 1.3     |                        |      |

**Notes 1.** The first clock pulse is generated after this period when the start/restart condition is detected.

2. The maximum value (MAX.) of the is during normal transfer and a wait state is inserted in the ACK (acknowledge) timing.

RemarkThe maximum value of Cb (communication line capacitance) and the value of Rb (communication line pull-up<br/>resistor) at that time in each mode are as follows.Fast mode: $C_b = 320 \text{ pF}, R_b = 1.1 \text{ k}\Omega$

(3) When reference voltage (+) = V<sub>DD</sub> (ADREFP1 = 0, ADREFP0 = 0), reference voltage (−) = V<sub>ss</sub> (ADREFM = 0), target pin : ANI0, ANI1, ANI16 to ANI23, internal reference voltage, and temperature sensor output voltage

| $(T_A = -40 \text{ to } +85^{\circ}C, 1.6 \text{ V} \le \text{EV}_{\text{DD}} = \text{V}_{\text{DD}} \le 5.5 \text{ V}, \text{ V}_{\text{SS}} = \text{EV}_{\text{SS}} = 0 \text{ V}, \text{ Reference voltage (+)} = \text{V}_{\text{DD}},$ | Reference voltage (-) |

|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------|

| = Vss)                                                                                                                                                                                                                                      |                       |

| Parameter                              | Symbol        | Conditio                                                                                      | ns                                                                                               | MIN.   | TYP.                    | MAX.  | Unit |

|----------------------------------------|---------------|-----------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------|--------|-------------------------|-------|------|

| Resolution                             | RES           |                                                                                               |                                                                                                  | 8      |                         | 10    | bit  |

| Overall error <sup>Note 1</sup>        | AINL          | 10-bit resolution                                                                             | $1.8~V \leq V_{DD} \leq 5.5~V$                                                                   |        | 1.2                     | ±7.0  | LSB  |

|                                        |               |                                                                                               | $\begin{array}{l} 1.6 \text{ V} \leq \text{VDD} \leq 5.5 \text{ V} \\ \text{Note 3} \end{array}$ |        | 1.2                     | ±10.5 | LSB  |

| Conversion time                        | <b>t</b> CONV | 10-bit resolution                                                                             | $3.6~V \le V_{DD} \le 5.5~V$                                                                     | 2.125  |                         | 39    | μs   |

|                                        |               |                                                                                               | $2.7~V \leq V \text{DD} \leq 5.5~V$                                                              | 3.1875 |                         | 39    | μs   |

|                                        |               |                                                                                               | $1.8~V \leq V \text{DD} \leq 5.5~V$                                                              | 17     |                         | 39    | μs   |

|                                        |               |                                                                                               | $1.6~V \leq V \text{DD} \leq 5.5~V$                                                              | 57     |                         | 95    | μs   |

|                                        |               | 10-bit resolution                                                                             | $3.6~V \leq V_{DD} \leq 5.5~V$                                                                   | 2.375  |                         | 39    | μs   |

|                                        |               | Target pin: Internal                                                                          | $2.7~V \leq V_{DD} \leq 5.5~V$                                                                   | 3.5625 |                         | 39    | μs   |

|                                        |               | reference voltage, and<br>temperature sensor output<br>voltage (HS (high-speed<br>main) mode) | $2.4 \text{ V} \leq \text{Vdd} \leq 5.5 \text{ V}$                                               | 17     |                         | 39    | μs   |

| Zero-scale error <sup>Notes 1, 2</sup> | Ezs           | 10-bit resolution                                                                             | $1.8~V \le V \text{DD} \le 5.5~V$                                                                |        |                         | ±0.60 | %FSR |

|                                        |               |                                                                                               | $\begin{array}{l} 1.6 \text{ V} \leq \text{VDD} \leq 5.5 \text{ V} \\ \text{Note 3} \end{array}$ |        |                         | ±0.85 | %FSR |

| Full-scale error <sup>Notes 1, 2</sup> | Ers           | 10-bit resolution                                                                             | $1.8~V \le V_{DD} \le 5.5~V$                                                                     |        |                         | ±0.60 | %FSR |

|                                        |               |                                                                                               | $\begin{array}{l} 1.6 \text{ V} \leq \text{VDD} \leq 5.5 \text{ V} \\ \text{Note 3} \end{array}$ |        |                         | ±0.85 | %FSR |

| Integral linearity error Note 1        | ILE           | 10-bit resolution                                                                             | $1.8~V \le V \text{DD} \le 5.5~V$                                                                |        |                         | ±4.0  | LSB  |

|                                        |               |                                                                                               | $\begin{array}{l} 1.6 \text{ V} \leq \text{VDD} \leq 5.5 \text{ V} \\ \text{Note 3} \end{array}$ |        |                         | ±6.5  | LSB  |

| Differential linearity error Note 1    | DLE           | 10-bit resolution                                                                             | $1.8~V \le V_{DD} \le 5.5~V$                                                                     |        |                         | ±2.0  | LSB  |

|                                        |               |                                                                                               | $\begin{array}{l} 1.6 \text{ V} \leq \text{VDD} \leq 5.5 \text{ V} \\ \text{Note 3} \end{array}$ |        |                         | ±2.5  | LSB  |

| Analog input voltage                   | VAIN          | ANIO, ANI1                                                                                    |                                                                                                  | 0      |                         | VDD   | V    |

|                                        |               | ANI16 to ANI23                                                                                |                                                                                                  | 0      |                         | EVDD  | V    |

|                                        |               | Internal reference voltage<br>(2.4 V ≤ VDD ≤ 5.5 V, HS (hig                                   | gh-speed main) mode)                                                                             |        | V <sub>BGR</sub> Note 4 |       | V    |

|                                        |               | Temperature sensor output (2.4 V $\leq$ VDD $\leq$ 5.5 V, HS (high                            | 0                                                                                                |        | VTMPS25 Note 4          |       | V    |

**Notes 1.** Excludes quantization error ( $\pm 1/2$  LSB).

- 2. This value is indicated as a ratio (%FSR) to the full-scale value.

- 3. When the conversion time is set to 57  $\mu$ s (min.) and 95  $\mu$ s (max.).

- 4. Refer to 2.6.2 Temperature sensor/internal reference voltage characteristics.

## LVD Detection Voltage of Interrupt & Reset Mode

(TA = -40 to +85°C, VPDR  $\leq$  EVDD = VDD  $\leq$  5.5 V, Vss = EVss = 0 V)

| Parameter           | Symbol |        | Conc                   | litions                      | MIN. | TYP. | MAX. | Unit |

|---------------------|--------|--------|------------------------|------------------------------|------|------|------|------|

| Interrupt and reset | VLVDA0 | VPOC2, | VPOC1, VPOC0 = 0, 0, 0 | , falling reset voltage      | 1.60 | 1.63 | 1.66 | V    |

| mode                | VLVDA1 |        | LVIS1, LVIS0 = 1, 0    | Rising release reset voltage | 1.74 | 1.77 | 1.81 | V    |

|                     |        |        |                        | Falling interrupt voltage    | 1.70 | 1.73 | 1.77 | V    |

|                     | VLVDA2 |        | LVIS1, LVIS0 = 0, 1    | Rising release reset voltage | 1.84 | 1.88 | 1.91 | V    |

|                     |        |        |                        | Falling interrupt voltage    | 1.80 | 1.84 | 1.87 | V    |

|                     | VLVDA3 |        | LVIS1, LVIS0 = 0, 0    | Rising release reset voltage | 2.86 | 2.92 | 2.97 | V    |

|                     |        |        |                        | Falling interrupt voltage    | 2.80 | 2.86 | 2.91 | V    |

|                     | VLVDB1 | VPOC2, | VPOC1, VPOC0 = 0, 0, 1 | 1.80                         | 1.84 | 1.87 | V    |      |

|                     | VLVDB2 |        | LVIS1, LVIS0 = 1, 0    | Rising release reset voltage | 1.94 | 1.98 | 2.02 | V    |

|                     |        |        |                        | Falling interrupt voltage    | 1.90 | 1.94 | 1.98 | V    |

|                     | VLVDB3 |        | LVIS1, LVIS0 = 0, 1    | Rising release reset voltage | 2.05 | 2.09 | 2.13 | V    |

|                     |        |        |                        | Falling interrupt voltage    | 2.00 | 2.04 | 2.08 | V    |

| VLVE                | VLVDB4 |        | LVIS1, LVIS0 = 0, 0    | Rising release reset voltage | 3.07 | 3.13 | 3.19 | V    |

|                     |        |        |                        | Falling interrupt voltage    | 3.00 | 3.06 | 3.12 | V    |

|                     | VLVDC0 | VPOC2, | VPOC1, VPOC0 = 0, 1, 0 | , falling reset voltage      | 2.40 | 2.45 | 2.50 | V    |

|                     | VLVDC1 |        | LVIS1, LVIS0 = 1, 0    | Rising release reset voltage | 2.56 | 2.61 | 2.66 | V    |

|                     |        |        |                        | Falling interrupt voltage    | 2.50 | 2.55 | 2.60 | V    |

|                     | VLVDC2 |        | LVIS1, LVIS0 = 0, 1    | Rising release reset voltage | 2.66 | 2.71 | 2.76 | V    |

|                     |        |        |                        | Falling interrupt voltage    | 2.60 | 2.65 | 2.70 | V    |

|                     | VLVDC3 |        | LVIS1, LVIS0 = 0, 0    | Rising release reset voltage | 3.68 | 3.75 | 3.82 | V    |

|                     |        |        |                        | Falling interrupt voltage    | 3.60 | 3.67 | 3.74 | V    |

|                     | VLVDD0 | VPOC2, | VPOC1, VPOC0 = 0, 1, 1 | , falling reset voltage      | 2.70 | 2.75 | 2.81 | V    |

|                     | VLVDD1 |        | LVIS1, LVIS0 = 1, 0    | Rising release reset voltage | 2.86 | 2.92 | 2.97 | V    |

|                     |        |        |                        | Falling interrupt voltage    | 2.80 | 2.86 | 2.91 | V    |

|                     | VLVDD2 |        | LVIS1, LVIS0 = 0, 1    | Rising release reset voltage | 2.96 | 3.02 | 3.08 | V    |

|                     |        |        |                        | Falling interrupt voltage    | 2.90 | 2.96 | 3.02 | V    |

|                     | VLVDD3 |        | LVIS1, LVIS0 = 0, 0    | Rising release reset voltage | 3.98 | 4.06 | 4.14 | V    |

|                     |        |        |                        | Falling interrupt voltage    | 3.90 | 3.98 | 4.06 | V    |

## 2.6.5 Supply voltage rise time

### (T<sub>A</sub> = -40 to +85°C, Vss = 0 V)

| Parameter                         | Symbol | Conditions | MIN. | TYP. | MAX. | Unit |

|-----------------------------------|--------|------------|------|------|------|------|

| Power supply voltage rising slope | SVDD   |            |      |      | 54   | V/ms |

Caution Make sure to keep the internal reset state by the LVD circuit or an external reset until V<sub>DD</sub> reaches the operating voltage range shown in 30.4 AC Characteristics.

# 3. ELECTRICAL SPECIFICATIONS (G: $T_A = -40$ to $+105^{\circ}$ C)

This chapter describes the electrical specifications for the products "G: Industrial applications ( $T_A = -40$  to +105°C)".

- Cautions 1. The RL78 microcontrollers have an on-chip debug function, which is provided for development and evaluation. Do not use the on-chip debug function in products designated for mass production, because the guaranteed number of rewritable times of the flash memory may be exceeded when this function is used, and product reliability therefore cannot be guaranteed. Renesas Electronics is not liable for problems occurring when the on-chip debug function is used.

- 2. With products not provided with an EVDD or EVss pin, replace EVDD with VDD, or replace EVss with Vss.

- For derating with T<sub>A</sub> = +85 to +105°C, contact our Sales Division or the vender's sales division. Derating means the specified reduction in an operating parameter to improve reliability.

|                      |                        | •, =:= • =                          |                                       | $0 \leq 5.5 \text{ V}, \text{ VSS} = \text{EVS}$ |                         |      |      |       | (Z/S) |

|----------------------|------------------------|-------------------------------------|---------------------------------------|--------------------------------------------------|-------------------------|------|------|-------|-------|

| Parameter            | Symbol                 |                                     |                                       | Conditions                                       |                         | MIN. | TYP. | MAX.  | Unit  |

| Supply               | IDD2                   | HALT                                | HS (high-                             | f⊪ = 24 MHz <sup>Note 4</sup>                    | V <sub>DD</sub> = 5.0 V |      | 0.44 | 2.3   | mA    |

| Current<br>Note 1    | Note 2                 | mode                                | speed main)<br>mode <sup>Note 7</sup> |                                                  | V <sub>DD</sub> = 3.0 V |      | 0.44 | 2.3   | mA    |

|                      |                        |                                     |                                       | fi⊢ = 16 MHz <sup>Note 4</sup>                   | V <sub>DD</sub> = 5.0 V |      | 0.40 | 1.7   | mA    |

|                      |                        |                                     |                                       |                                                  | V <sub>DD</sub> = 3.0 V |      | 0.40 | 1.7   | mA    |

|                      |                        |                                     | HS (high-                             | f <sub>MX</sub> = 20 MHz <sup>Note 3</sup> ,     | Square wave input       |      | 0.28 | 1.9   | mA    |

|                      |                        |                                     | speed main)<br>mode <sup>Note 7</sup> | V <sub>DD</sub> = 5.0 V                          | Resonator connection    |      | 0.45 | 2.0   | mA    |

|                      |                        |                                     |                                       | f <sub>MX</sub> = 20 MHz <sup>Note 3</sup> ,     | Square wave input       |      | 0.28 | 1.9   | mA    |

|                      |                        |                                     |                                       | V <sub>DD</sub> = 3.0 V                          | Resonator connection    |      | 0.45 | 2.0   | mA    |

|                      |                        |                                     |                                       | $f_{MX} = 10 \text{ MHz}^{\text{Note 3}},$       | Square wave input       |      | 0.19 | 1.02  | mA    |

|                      |                        |                                     |                                       | V <sub>DD</sub> = 5.0 V                          | Resonator connection    |      | 0.26 | 1.10  | mA    |

|                      |                        |                                     |                                       | $f_{MX} = 10 \text{ MHz}^{\text{Note 3}},$       | Square wave input       |      | 0.19 | 1.02  | mA    |

|                      |                        |                                     |                                       | V <sub>DD</sub> = 3.0 V                          | Resonator connection    |      | 0.26 | 1.10  | mA    |

|                      | Subsystem              | fsue = 32.768 kHz <sup>Note 5</sup> | Square wave input                     |                                                  | 0.31                    | 0.57 | μA   |       |       |

|                      |                        | clock                               | T <sub>A</sub> = −40°C                | Resonator connection                             |                         | 0.50 | 0.76 | μA    |       |

|                      |                        |                                     | operation                             | fsue = 32.768 kHz <sup>Note 5</sup>              | Square wave input       |      | 0.37 | 0.57  | μA    |

|                      |                        |                                     |                                       | T <sub>A</sub> = +25°C                           | Resonator connection    |      | 0.56 | 0.76  | μA    |

|                      |                        |                                     |                                       | fsue = 32.768 kHz <sup>Note 5</sup>              | Square wave input       |      | 0.46 | 1.17  | μA    |

|                      |                        |                                     |                                       | T <sub>A</sub> = +50°C                           | Resonator connection    |      | 0.65 | 1.36  | μA    |

|                      |                        |                                     |                                       | fsub = 32.768 kHz <sup>Note 5</sup>              | Square wave input       |      | 0.57 | 1.97  | μA    |

|                      |                        |                                     |                                       | T <sub>A</sub> = +70°C                           | Resonator connection    |      | 0.76 | 2.16  | μA    |

|                      |                        |                                     |                                       | f <sub>SUB</sub> = 32.768 kHz <sup>Note 5</sup>  | Square wave input       |      | 0.85 | 3.37  | μA    |

|                      |                        |                                     |                                       | T <sub>A</sub> = +85°C                           | Resonator connection    |      | 1.04 | 3.56  | μA    |

|                      |                        |                                     |                                       | f <sub>SUB</sub> = 32.768 kHz <sup>Note 5</sup>  | Square wave input       |      | 3.04 | 15.37 | μA    |

|                      |                        |                                     |                                       | T <sub>A</sub> = +105°C                          | Resonator connection    |      | 3.23 | 15.56 | μA    |

|                      | IDD3 <sup>Note 6</sup> | STOP                                | T <sub>A</sub> = -40°C                |                                                  |                         |      | 0.17 | 0.50  | μA    |

| mode <sup>Note</sup> | mode <sup>Note 8</sup> | T <sub>A</sub> = +25°C              |                                       |                                                  |                         | 0.23 | 0.50 | μA    |       |

|                      |                        | T <sub>A</sub> = +50°C              |                                       |                                                  |                         | 0.32 | 1.10 | μA    |       |

|                      |                        | T <sub>A</sub> = +70°C              |                                       |                                                  |                         | 0.43 | 1.90 | μA    |       |

|                      |                        | T <sub>A</sub> = +85°C              |                                       |                                                  |                         | 0.71 | 3.30 | μA    |       |

|                      |                        |                                     | T <sub>A</sub> = +105°C               |                                                  |                         |      | 2.90 | 15.30 | μA    |

## (TA = -40 to +105°C, 2.4 V $\leq$ EVDD = VDD $\leq$ 5.5 V, Vss = EVss = 0 V)

(2/3)

(Notes and  $\ensuremath{\textit{Remarks}}$  are listed on the next page.)

- **Notes 1.** Total current flowing into V<sub>DD</sub> and EV<sub>DD</sub>, including the input leakage current flowing when the level of the input pin is fixed to V<sub>DD</sub>, EV<sub>DD</sub> or V<sub>SS</sub>, EV<sub>SS</sub>. The values below the MAX. column include the peripheral operation current. However, not including the current flowing into the A/D converter, LVD circuit, I/O port, and on-chip pull-up/pull-down resistors and the current flowing during data flash rewrite.

- 2. During HALT instruction execution by flash memory.

- **3.** When high-speed on-chip oscillator and subsystem clock are stopped.

- 4. When high-speed system clock and subsystem clock are stopped.

- 5. When high-speed on-chip oscillator and high-speed system clock are stopped. When RTCLPC = 1 and setting ultra-low current consumption (AMPHS1 = 1). The current flowing into the RTC is included. However, not including the current flowing into the 12-bit interval timer, watchdog timer, and LCD controller/driver.

- 6. Not including the current flowing into the RTC, 12-bit interval timer, and watchdog timer.

- 7. Relationship between operation voltage width, operation frequency of CPU and operation mode is as below. HS (high-speed main) mode:  $2.7 \text{ V} \le V_{\text{DD}} \le 5.5 \text{ V}$ @1 MHz to 24 MHz

- 2.4 V  $\leq$  VDD  $\leq$  5.5 V@1 MHz to 16 MHz

- 8. Regarding the value for current operate the subsystem clock in STOP mode, refer to that in HALT mode.

- Remarks 1. fmx: High-speed system clock frequency (X1 clock oscillation frequency or external main system clock frequency)

- 2. fin: High-speed on-chip oscillator clock frequency

- **3.** fsub: Subsystem clock frequency (XT1 clock oscillation frequency)

- 4. Except subsystem clock operation and STOP mode, temperature condition of the TYP. value is TA = 25°C

## 3.7 LCD Characteristics

### 3.7.1 Resistance division method

### (1) Static display mode

## $(T_A = -40 \text{ to } +105^{\circ}C, V_{L4} \text{ (MIN.)} \le V_{DD}^{Note} \le 5.5 \text{ V}, \text{Vss} = 0 \text{ V})$

| Parameter         | Symbol | Conditions | MIN. | TYP. | MAX. | Unit |

|-------------------|--------|------------|------|------|------|------|

| LCD drive voltage | VL4    |            | 2.0  |      | Vdd  | V    |

Note Must be 2.4 V or higher.

### (2) 1/2 bias method, 1/4 bias method

### (TA = -40 to +105°C, VL4 (MIN.) $\leq$ VDD $\leq$ 5.5 V, Vss = 0 V)

| Parameter         | Symbol | Conditions | MIN. | TYP. | MAX. | Unit |

|-------------------|--------|------------|------|------|------|------|

| LCD drive voltage | VL4    |            | 2.7  |      | VDD  | V    |

#### (3) 1/3 bias method

### (T\_A = -40 to +105°C, V\_L4 (MIN.) $\leq$ V\_DD $\leq$ 5.5 V, V\_SS = 0 V)

| Parameter         | Symbol | Conditions | MIN. | TYP. | MAX. | Unit |

|-------------------|--------|------------|------|------|------|------|

| LCD drive voltage | VL4    |            | 2.5  |      | Vdd  | V    |

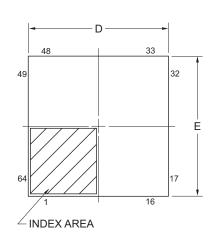

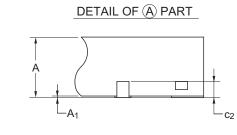

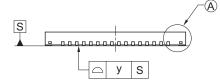

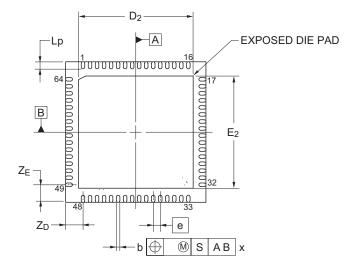

## R5F10RLAANB, R5F10RLCANB R5F10RLAGNB, R5F10RLCGNB

| <r></r> | JEITA Package Code | RENESAS Code | Previous Code  | MASS (Typ) [g] |

|---------|--------------------|--------------|----------------|----------------|

|         | P-HWQFN64-8x8-0.40 | PWQN0064LA-A | P64K8-40-9B5-4 | 0.16           |

\_\_\_\_\_\_

Unit: mm

| Reference      | Dimensions in millimeters |      |      |  |  |

|----------------|---------------------------|------|------|--|--|

| Symbol         | Min                       | Nom  | Max  |  |  |

| D              | 7.95                      | 8.00 | 8.05 |  |  |

| E              | 7.95                      | 8.00 | 8.05 |  |  |

| A              | _                         |      | 0.80 |  |  |

| A <sub>1</sub> | 0.00                      |      | —    |  |  |

| b              | 0.17                      | 0.20 | 0.23 |  |  |

| е              | _                         | 0.40 | —    |  |  |

| Lp             | 0.30                      | 0.40 | 0.50 |  |  |

| x              | —                         | _    | 0.05 |  |  |

| У              | _                         |      | 0.05 |  |  |

| ZD             | _                         | 1.00 | —    |  |  |

| ZE             | _                         | 1.00 | _    |  |  |

| C2             | 0.15                      | 0.20 | 0.25 |  |  |

| D <sub>2</sub> | _                         | 6.50 | —    |  |  |

| E <sub>2</sub> | _                         | 6.50 | —    |  |  |

© 2015 Renesas Electronics Corporation. All rights reserved.

|      |              | Description |                                                                                                                                                            |  |

|------|--------------|-------------|------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| Rev. | Date         | Page        | Summary                                                                                                                                                    |  |

| 2.00 | Jan 10, 2014 | 35          | Modification of table in 2.4 AC Characteristics                                                                                                            |  |

|      |              | 36          | Addition of Minimum Instruction Execution Time during Main System Clock<br>Operation                                                                       |  |

|      |              | 37          | Modification of AC Timing Test Points and External System Clock Timing                                                                                     |  |

|      |              | 39          | Modification of AC Timing Test Points                                                                                                                      |  |

|      |              | 39          | Modification of description, notes 1 and 2 in (1) During communication at same potential (UART mode)                                                       |  |

|      |              | 41, 42      | Modification of description, remark 2 in (2) During communication at same potential (CSI mode)                                                             |  |

|      |              | 42, 43      | Modification of description in (3) During communication at same potential (CSI mode)                                                                       |  |

|      |              | 45          | Modification of description, notes 1 and 3, and remark 3 in (4) Communication at different potential (1.8 V, 2.5 V, 3 V) (UART mode) (1/2)                 |  |

|      |              | 46, 48      | Modification of description, and remark 3 in (4) Communication at different potential (1.8 V, 2.5 V, 3 V) (UART mode) (2/2)                                |  |

|      |              | 49, 50      | Modification of table, and note 1, caution, and remark 3 in (5) Communication at different potential (2.5 V, 3 V) (CSI mode)                               |  |

|      |              | 51          | Modification of table and note in (6) Communication at different potential (1.8 V, 2.5 V, 3 V) (1/3)                                                       |  |

|      |              | 52          | Modification of table and notes 1 to 3 in (6) Communication at different potential (1.8 V, 2.5 V, 3 V) (2/3)                                               |  |

|      |              | 53, 54      | Modification of table, note 3, and remark 3 in (6) Communication at different potential (1.8 V, 2.5 V, 3 V) (3/3)                                          |  |

|      |              | 56          | Modification of table in (7) Communication at different potential (1.8 V, 2.5 V, 3 V) (CSI mode) (1/2)                                                     |  |

|      |              | 57          | Modification of table in (7) Communication at different potential (1.8 V, 2.5 V, 3 V) (CSI mode) (2/2)                                                     |  |

|      |              | 59, 60      | Addition of (1) I <sup>2</sup> C standard mode                                                                                                             |  |

|      |              | 61          | Addition of (2) I <sup>2</sup> C fast mode                                                                                                                 |  |

|      |              | 62          | Addition of (3) I <sup>2</sup> C fast mode plus                                                                                                            |  |

|      |              | 63          | Addition of table in 2.6.1 A/D converter characteristics                                                                                                   |  |

|      |              | 63, 64      | Modification of description and notes 3 to 5 in 2.6.1 (1)                                                                                                  |  |

|      |              | 65          | Modification of description, notes 3 and 4 in 2.6.1 (2)                                                                                                    |  |

|      |              | 66          | Modification of description, notes 3 and 4 in 2.6.1 (3)                                                                                                    |  |

|      |              | 67          | Modification of description, notes 3 and 4 in 2.6.1 (4)                                                                                                    |  |

|      |              | 67          | Modification of the table in 2.6.2 Temperature sensor/internal reference voltage<br>characteristics                                                        |  |

|      |              | 68          | Modification of the table and note in 2.6.3 POR circuit characteristics                                                                                    |  |

|      |              | 70          | Modification of the table of LVD Detection Voltage of Interrupt & Reset Mode                                                                               |  |

|      |              | 70          | Modification from VDD rise slope to Power supply voltage rising slope in 2.6.5<br>Supply voltage rise time                                                 |  |

|      |              | 75          | Modification of description in 2.10 Dedicated Flash Memory Programmer<br>Communication (UART)                                                              |  |

|      |              | 76          | Modification of the figure in 2.11 Timing Specifications for Switching Flash<br>Memory Programming Modes                                                   |  |

|      |              | 77 to 126   | Addition of products for industrial applications (G: T <sub>A</sub> = -40 to +105°C)                                                                       |  |

|      |              | 127 to 133  | Addition of product names for industrial applications (G: $T_A = -40$ to $+105^{\circ}C$ )                                                                 |  |

| 2.10 | Sep 30, 2016 | 5           | Modification of pin configuration in 1.3.1 32-pin products                                                                                                 |  |

|      |              | 6           | Modification of pin configuration in 1.3.2 44-pin products                                                                                                 |  |

|      |              | 7           | Modification of pin configuration in 1.3.3 48-pin products                                                                                                 |  |

|      |              | 8           | Modification of pin configuration in 1.3.4 52-pin products                                                                                                 |  |

|      |              | 9, 10<br>17 | Modification of pin configuration in 1.3.5 64-pin products                                                                                                 |  |