# E·XFL

Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Product Status             | Active                                                    |

|----------------------------|-----------------------------------------------------------|

| Core Processor             | eZ8                                                       |

| Core Size                  | 8-Bit                                                     |

| Speed                      | 20MHz                                                     |

| Connectivity               | I <sup>2</sup> C, IrDA, SPI, UART/USART                   |

| Peripherals                | Brown-out Detect/Reset, DMA, POR, PWM, WDT                |

| Number of I/O              | 31                                                        |

| Program Memory Size        | 16KB (16K x 8)                                            |

| Program Memory Type        | FLASH                                                     |

| EEPROM Size                | -                                                         |

| RAM Size                   | 2K x 8                                                    |

| Voltage - Supply (Vcc/Vdd) | 3V ~ 3.6V                                                 |

| Data Converters            | A/D 8x10b                                                 |

| Oscillator Type            | Internal                                                  |

| Operating Temperature      | -40°C ~ 105°C (TA)                                        |

| Mounting Type              | Surface Mount                                             |

| Package / Case             | 44-LQFP                                                   |

| Supplier Device Package    | 44-LQFP (10x10)                                           |

| Purchase URL               | https://www.e-xfl.com/product-detail/zilog/z8f1621an020eg |

|                            |                                                           |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

# Z8 Encore! XP<sup>®</sup> F64xx Series Product Specification

| Table 177. | UART Baud Rate High Byte Register (UxBRH)                | 258 |

|------------|----------------------------------------------------------|-----|

| Table 178. | UART Baud Rate Low Byte Register (UxBRL)                 | 259 |

| Table 179. | UART Transmit Data Register (UxTXD)                      | 259 |

| Table 180. | UART Receive Data Register (UxRXD)                       | 259 |

| Table 181. | UART Status 0 Register (UxSTAT0)                         | 259 |

| Table 182. | UART Control 0 Register (UxCTL0)                         | 260 |

| Table 183. | UART Control 1 Register (UxCTL1)                         | 260 |

| Table 184. | UART Status 1 Register (UxSTAT1)                         | 260 |

| Table 185. | UART Address Compare Register (UxADDR)                   | 260 |

| Table 186. | UART Baud Rate High Byte Register (UxBRH)                | 261 |

| Table 187. | UART Baud Rate Low Byte Register (UxBRL)                 | 261 |

| Table 188. | I <sup>2</sup> C Data Register (I2CDATA)                 | 261 |

| Table 189. | I <sup>2</sup> C Status Register (I2CSTAT)               | 262 |

| Table 190. | I <sup>2</sup> C Control Register (I2CCTL)               | 262 |

| Table 191. | I <sup>2</sup> C Baud Rate High Byte Register (I2CBRH)   | 262 |

| Table 192. | I <sup>2</sup> C Baud Rate Low Byte Register (I2CBRL)    | 262 |

| Table 193. | I <sup>2</sup> C Diagnostic State Register (I2CDST)      | 263 |

| Table 194. | I <sup>2</sup> C Diagnostic Control Register (I2CDIAG)   | 263 |

| Table 195. | SPI Data Register (SPIDATA)                              | 263 |

| Table 196. | SPI Control Register (SPICTL)                            | 264 |

| Table 197. | SPI Status Register (SPISTAT)                            | 264 |

| Table 198. | SPI Mode Register (SPIMODE)                              | 264 |

| Table 199. | SPI Diagnostic State Register (SPIDST)                   | 265 |

| Table 200. | SPI Baud Rate High Byte Register (SPIBRH)                | 265 |

| Table 201. | SPI Baud Rate Low Byte Register (SPIBRL)                 | 265 |

| Table 202. | ADC Data High Byte Register (ADCD_H)                     | 266 |

| Table 203. | ADC Data Low Bits Register (ADCD_L)                      | 266 |

| Table 204. | DMAx Control Register (DMAxCTL)                          | 267 |

| Table 205. | DMAx I/O Address Register (DMAxIO)                       | 267 |

| Table 206. | DMAx Address High Nibble Register (DMAxH)                | 267 |

| Table 207. | DMAx Start/Current Address Low Byte Register (DMAxSTART) | 267 |

| Table 208. | DMAx End Address Low Byte Register (DMAxEND)             | 268 |

| Table 209. | DMAx Control Register (DMAxCTL)                          | 268 |

|            | DMAx I/O Address Register (DMAxIO)                       |     |

|            | DMAx Address High Nibble Register (DMAxH)                |     |

|            | DMAx Start/Current Address Low Byte Register (DMAxSTART) |     |

|            | · · · · · · · · · · · · · · · · · · ·                    |     |

| Signal<br>Mnemonic | I/O    | Description                                                                                                                                                                                                                                                                                                                          |

|--------------------|--------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Oscillators        |        |                                                                                                                                                                                                                                                                                                                                      |

| X <sub>IN</sub>    | I      | External Crystal Input. This is the input pin to the crystal oscillator. A crystal can be connected between it and the $X_{OUT}$ pin to form the oscillator. This signal is usable with external RC networks and an external clock driver.                                                                                           |

| X <sub>OUT</sub>   | 0      | External Crystal Output. This pin is the output of the crystal oscillator. A crystal can be connected between it and the $X_{IN}$ pin to form the oscillator. When the system clock is referred to in this manual, it refers to the frequency of the signal at this pin. This pin must be left unconnected when not using a crystal. |

| RC <sub>OUT</sub>  | 0      | RC Oscillator Output. This signal is the output of the RC oscillator. It is multi-<br>plexed with a general-purpose I/O pin. This signal must be left unconnected<br>when not using a crystal.                                                                                                                                       |

| On-Chip Deb        | ougger |                                                                                                                                                                                                                                                                                                                                      |

| DBG                | I/O    | Debug. This pin is the control and data input and output to and from the On-<br>Chip Debugger. This pin is open-drain.                                                                                                                                                                                                               |

|                    |        | <b>Caution:</b> For operation of the On-Chip Debugger, all power pins ( $V_{DD}$ and $AV_{DD}$ ) must be supplied with power and all ground pins ( $V_{SS}$ and $AV_{SS}$ ) must be properly grounded. The DBG pin is open-drain and must have an external pull-up resistor to ensure proper operation.                              |

| Reset              |        |                                                                                                                                                                                                                                                                                                                                      |

| RESET              | Ι      | RESET. Generates a Reset when asserted (driven Low).                                                                                                                                                                                                                                                                                 |

| Power Supp         | ly     |                                                                                                                                                                                                                                                                                                                                      |

| V <sub>DD</sub>    | I      | Power Supply.                                                                                                                                                                                                                                                                                                                        |

| AV <sub>DD</sub>   | Ι      | Analog Power Supply.                                                                                                                                                                                                                                                                                                                 |

| V <sub>SS</sub>    | Ι      | Ground.                                                                                                                                                                                                                                                                                                                              |

| AV <sub>SS</sub>   | Ι      | Analog Ground.                                                                                                                                                                                                                                                                                                                       |

### Table 3. Signal Descriptions (Continued)

# **Address Space**

The eZ8 CPU can access three distinct address spaces:

- The Register File contains addresses for the general-purpose registers and the eZ8 CPU, peripheral and general-purpose I/O port control registers

- The program memory contains addresses for all memory locations having executable code and/or data

- The Data Memory consists of the addresses for all memory locations that hold only data

These three address spaces are covered briefly in the following sections. For more information about the eZ8 CPU and its address space, refer to the <u>eZ8 CPU Core User Manual</u> (<u>UM0128</u>), which is available for download on <u>www.zilog.com</u>.

# **Register File**

The Register File address space in the Z8 Encore! XP F64xx Series is 4KB (4096 bytes). The Register File is composed of two sections: control registers and general-purpose registers. When instructions are executed, registers are read from when defined as sources and written to when defined as destinations. The architecture of the eZ8 CPU allows all general-purpose registers to function as accumulators, address pointers, index registers, stack areas, or scratch pad memory.

The upper 256 bytes of the 4KB Register File address space are reserved for control of the eZ8 CPU, the on-chip peripherals, and the I/O ports. These registers are located at addresses from F00H to FFFH. Some of the addresses within the 256-byte control register section are reserved (unavailable). Reading from an reserved Register File addresses returns an undefined value. Writing to reserved Register File addresses is not recommended and can produce unpredictable results.

The on-chip RAM always begins at address 000H in the Register File address space. The Z8 Encore! XP F64xx Series provide 2KB to 4KB of on-chip RAM depending upon the device. Reading from Register File addresses outside the available RAM addresses (and not within the control register address space) returns an undefined value. Writing to these Register File addresses produces no effect. To determine the amount of RAM available for the specific Z8 Encore! XP F64xx Series device, see the <u>Part Selection Guide</u> section on page 2.

# **Register File Address Map**

Table 7 provides the address map for the Register File of the Z8 Encore! XP F64xx Series products. Not all devices and package styles in the Z8 Encore! XP F64xx Series support Timer 3 and all of the GPIO ports. Consider registers for unimplemented peripherals to be reserved.

| Address (H | ex) Register Description          | Mnemonic | Reset (Hex) | Page      |

|------------|-----------------------------------|----------|-------------|-----------|

| General-Pu | rpose RAM                         |          |             |           |

| 000-EFF    | General-Purpose Register File RAM |          | XX          |           |

| Timer 0    |                                   |          |             |           |

| F00        | Timer 0 High Byte                 | T0H      | 00          | <u>72</u> |

| F01        | Timer 0 Low Byte                  | TOL      | 01          | <u>72</u> |

| F02        | Timer 0 Reload High Byte          | TORH     | FF          | <u>74</u> |

| F03        | Timer 0 Reload Low Byte           | TORL     | FF          | <u>74</u> |

| F04        | Timer 0 PWM High Byte             | TOPWMH   | 00          | <u>75</u> |

| F05        | Timer 0 PWM Low Byte              | TOPWML   | 00          | <u>75</u> |

| F06        | Timer 0 Control 0                 | TOCTLO   | 00          | <u>76</u> |

| F07        | Timer 0 Control 1                 | T0CTL1   | 00          | <u>77</u> |

| Timer 1    |                                   |          |             |           |

| F08        | Timer 1 High Byte                 | T1H      | 00          | <u>72</u> |

| F09        | Timer 1 Low Byte                  | T1L      | 01          | <u>72</u> |

| F0A        | Timer 1 Reload High Byte          | T1RH     | FF          | <u>74</u> |

| F0B        | Timer 1 Reload Low Byte           | T1RL     | FF          | <u>74</u> |

| F0C        | Timer 1 PWM High Byte             | T1PWMH   | 00          | <u>75</u> |

| F0D        | Timer 1 PWM Low Byte              | T1PWML   | 00          | <u>75</u> |

| F0E        | Timer 1 Control 0                 | T1CTL0   | 00          | <u>76</u> |

| F0F        | Timer 1 Control 1                 | T1CTL1   | 00          | <u>77</u> |

| Timer 2    |                                   |          |             |           |

| F10        | Timer 2 High Byte                 | T2H      | 00          | <u>72</u> |

| F11        | Timer 2 Low Byte                  | T2L      | 01          | <u>72</u> |

| F12        | Timer 2 Reload High Byte          | T2RH     | FF          | <u>74</u> |

| F13        | Timer 2 Reload Low Byte           | T2RL     | FF          | <u>74</u> |

#### Table 7. Z8 Encore! XP F64xx Series Register File Address Map

Note: XX = Undefined.

| Address (He      | ex) Register Description             | Mnemonic | Reset (Hex) | Page       |

|------------------|--------------------------------------|----------|-------------|------------|

| UART 1 (coi      | ntinued)                             |          |             |            |

| F4D              | UART1 Address Compare Register       | U1ADDR   | 00          | <u>105</u> |

| F4E              | UART1 Baud Rate High Byte            | U1BRH    | FF          | <u>105</u> |

| F4F              | UART1 Baud Rate Low Byte             | U1BRL    | FF          | <u>105</u> |

| l <sup>2</sup> C |                                      |          |             |            |

| F50              | I <sup>2</sup> C Data                | I2CDATA  | 00          | <u>141</u> |

| F51              | I <sup>2</sup> C Status              | I2CSTAT  | 80          | <u>142</u> |

| F52              | I <sup>2</sup> C Control             | I2CCTL   | 00          | <u>144</u> |

| F53              | I <sup>2</sup> C Baud Rate High Byte | I2CBRH   | FF          | <u>145</u> |

| F54              | I <sup>2</sup> C Baud Rate Low Byte  | I2CBRL   | FF          | <u>145</u> |

| F55              | I <sup>2</sup> C Diagnostic State    | I2CDST   | CO          | <u>147</u> |

| F56              | I <sup>2</sup> C Diagnostic Control  | I2CDIAG  | 00          | <u>149</u> |

| F57–F5F          | Reserved                             | _        | XX          |            |

| Serial Perip     | heral Interface (SPI)                |          |             |            |

| F60              | SPI Data                             | SPIDATA  | XX          | <u>121</u> |

| F61              | SPI Control                          | SPICTL   | 00          | <u>122</u> |

| F62              | SPI Status                           | SPISTAT  | 01          | <u>123</u> |

| F63              | SPI Mode                             | SPIMODE  | 00          | <u>125</u> |

| F64              | SPI Diagnostic State                 | SPIDST   | 00          | <u>126</u> |

| F65              | Reserved                             | _        | XX          |            |

| F66              | SPI Baud Rate High Byte              | SPIBRH   | FF          | <u>126</u> |

| F67              | SPI Baud Rate Low Byte               | SPIBRL   | FF          | <u>126</u> |

| F68–F6F          | Reserved                             |          | XX          |            |

| Analog-to-D      | igital Converter                     |          |             |            |

| F70              | ADC Control                          | ADCCTL   | 20          | <u>165</u> |

| F71              | Reserved                             |          | XX          |            |

| F72              | ADC Data High Byte                   | ADCD_H   | XX          | <u>167</u> |

| F73              | ADC Data Low Bits                    | ADCD_L   | XX          | <u>168</u> |

| F74–FAF          | Reserved                             |          | XX          |            |

| DMA 0            |                                      |          |             |            |

| FB0              | DMA0 Control                         | DMA0CTL  | 00          | <u>153</u> |

| FB1              | DMA0 I/O Address                     | DMA0IO   | XX          | 154        |

Table 7. Z8 Encore! XP F64xx Series Register File Address Map (Continued)

Note: XX = Undefined.

# Interrupt Controller

The interrupt controller on the Z8 Encore! XP F64xx Series products prioritizes the interrupt requests from the on-chip peripherals and the GPIO port pins. The features of the interrupt controller include:

- 24 unique interrupt vectors:

- 12 GPIO port pin interrupt sources

- 12 on-chip peripheral interrupt sources

- Flexible GPIO interrupts

- Eight selectable rising and falling edge GPIO interrupts

- Four dual-edge interrupts

- Three levels of individually programmable interrupt priority

- Watchdog Timer can be configured to generate an interrupt

Interrupt requests (IRQs) allow peripheral devices to suspend CPU operation in an orderly manner and force the CPU to start an interrupt service routine (ISR). Usually this interrupt service routine is involved with the exchange of data, status information, or control information between the CPU and the interrupting peripheral. When the service routine is completed, the CPU returns to the operation from which it was interrupted.

The eZ8 CPU supports both vectored and polled interrupt handling. For polled interrupts, the interrupt control has no effect on operation. For more information about interrupt servicing by the eZ8 CPU, refer to the <u>eZ8 CPU Core User Manual (UM0128)</u>, which is available for download on <u>www.zilog.com</u>.

## **Interrupt Vector Listing**

Table 23 lists all of the interrupts available in order of priority. The interrupt vector is stored with the most significant byte (MSB) at the even program memory address and the least significant byte (LSB) at the following odd program memory address.

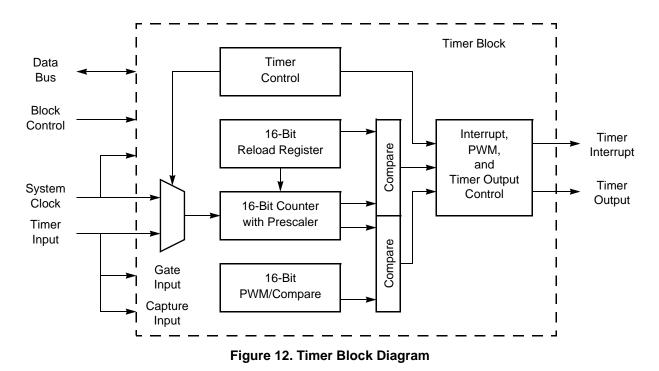

# Operation

The timers are 16-bit up-counters. Minimum time-out delay is set by loading the value 0001H into the Timer Reload High and Low Byte registers and setting the prescale value to 1. Maximum time-out delay is set by loading the value 0000H into the Timer Reload High and Low Byte registers and setting the prescale value to 128. If the Timer reaches FFFFH, the timer rolls over to 0000H and continues counting.

## **Timer Operating Modes**

The timers can be configured to operate in the following modes:

#### **ONE-SHOT Mode**

In ONE-SHOT Mode, the timer counts up to the 16-bit reload value stored in the Timer Reload High and Low Byte registers. The timer input is the system clock. Upon reaching the reload value, the timer generates an interrupt and the count value in the Timer High and Low Byte registers is reset to 0001H. Then, the timer is automatically disabled and stops counting.

Also, if the timer output alternate function is enabled, the timer output pin changes state for one system clock cycle (from Low to High or from High to Low) upon timer reload. If

63

## Timer 0–3 PWM High and Low Byte Registers

The Timer 0–3 PWM High and Low Byte (TxPWMH and TxPWML) registers, shown in Tables 43 and 44, are used for Pulse-Width Modulator (PWM) operations. These registers also store the capture values for the CAPTURE and CAPTURE/COMPARE modes.

#### Table 43. Timer 0–3 PWM High Byte Register (TxPWMH)

| Bit     | 7 | 6 | 5 | 4          | 3         | 2 | 1 | 0 |

|---------|---|---|---|------------|-----------|---|---|---|

| Field   |   |   |   | PW         | ΜH        |   |   |   |

| RESET   |   | 0 |   |            |           |   |   |   |

| R/W     |   |   |   | R/         | W         |   |   |   |

| Address |   |   | F | 04H, F0CH, | F14H, F1C | Н |   |   |

#### Table 44. Timer 0–3 PWM Low Byte Register (TxPWML)

| Bit     | 7 | 6 | 5 | 4          | 3         | 2 | 1 | 0 |

|---------|---|---|---|------------|-----------|---|---|---|

| Field   |   |   |   | PW         | 'ML       |   |   |   |

| RESET   |   |   |   | (          | )         |   |   |   |

| R/W     |   |   |   | R/         | W         |   |   |   |

| Address |   |   | F | 05H, F0DH, | F15H, F1D | Η |   |   |

| Bit           | Description                                                                                                                                                                                                                                                                                                                                                                                       |

|---------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| [7:0]         | Pulse-Width Modulator High and Low Bytes                                                                                                                                                                                                                                                                                                                                                          |

| PWMH,<br>PWML | These two bytes, {PWMH[7:0], PWML[7:0]}, form a 16-bit value that is compared to the current 16-bit timer count. When a match occurs, the PWM output changes state. The PWM output value is set by the TPOL bit in the Timer Control 1 Register (TxCTL1) Register. The TxPWMH and TxPWML registers also store the 16-bit captured timer value when operating in CAPTURE or CAPTURE/COMPARE modes. |

unlock the Watchdog Timer Reload Byte registers (WDTU, WDTH, and WDTL) for write access.

- 1. Write 55H to the Watchdog Timer Control Register (WDTCTL).

- 2. Write AAH to the Watchdog Timer Control Register (WDTCTL).

- 3. Write the Watchdog Timer Reload Upper Byte Register (WDTU).

- 4. Write the Watchdog Timer Reload High Byte Register (WDTH).

- 5. Write the Watchdog Timer Reload Low Byte Register (WDTL).

All steps of the Watchdog Timer reload unlock sequence must be written in the sequence described above; there must be no other register writes between each of these operations. If a register write occurs, the lock state machine resets and no further writes can occur, unless the sequence is restarted. The value in the Watchdog Timer Reload registers is loaded into the counter when the Watchdog Timer is first enabled and every time a WDT instruction is executed.

## Watchdog Timer Control Register Definitions

This section defines the features of the following Watchdog Timer Control registers.

Watchdog Timer Control Register: see page 83

Watchdog Timer Reload Upper, High and Low Byte Registers: see page 85

## Watchdog Timer Control Register

The Watchdog Timer Control (WDTCTL) Register, shown in Table 48, is a read-only register that indicates the source of the most recent Reset event, indicates a Stop Mode Recovery event, and indicates a Watchdog Timer time-out. Reading this register resets the upper four bits to 0.

Writing the 55H, AAH unlock sequence to the Watchdog Timer Control (WDTCTL) Register address unlocks the three Watchdog Timer Reload Byte registers (WDTU, WDTH, and WDTL) to allow changes to the time-out period. These write operations to the WDTCTL Register address produce no effect on the bits in the WDTCTL Register. The locking mechanism prevents spurious writes to the Reload registers.

## **UART Interrupts**

The UART features separate interrupts for the transmitter and the receiver. In addition, when the UART primary functionality is disabled, the Baud Rate Generator can also function as a basic timer with interrupt capability.

## **Transmitter Interrupts**

The transmitter generates a single interrupt when the Transmit Data Register Empty bit (TDRE) is set to 1. This indicates that the transmitter is ready to accept new data for transmission. The TDRE interrupt occurs after the Transmit Shift Register has shifted the first bit of data out. At this point, the Transmit Data Register can be written with the next character to send. This provides 7 bit-periods of latency to load the Transmit Data Register before the Transmit Shift Register completes shifting the current character. Writing to the UART Transmit Data Register clears the TDRE bit to 0.

## **Receiver Interrupts**

The receiver generates an interrupt when any of the following events occurs:

• A data byte has been received and is available in the UART Receive Data Register. This interrupt can be disabled independent of the other receiver interrupt sources. The received data interrupt occurs once the receive character has been received and placed in the Receive Data Register. Software must respond to this received data available condition before the next character is completely received to avoid an overrun error.

**Note:** In MULTIPROCESSOR Mode (MPEN=1), the receive data interrupts are dependent on the multiprocessor configuration and the most recent address byte.

- A break is received

- An overrun is detected

- A data framing error is detected

## **UART Overrun Errors**

When an overrun error condition occurs the UART prevents overwriting of the valid data currently in the Receive Data Register. The Break Detect and Overrun status bits are not displayed until after the valid data has been read.

After the valid data has been read, the UART Status 0 Register is updated to indicate the overrun condition (and Break Detect, if applicable). The RDA bit is set to 1 to indicate that the Receive Data Register contains a data byte. However, because the overrun error occurred, this byte may not contain valid data and should be ignored. The BRKD bit indicates if the overrun was caused by a break condition on the line. After reading the status

>

passed to the UART. Communication is half-duplex, which means simultaneous data transmission and reception is not allowed.

The baud rate is set by the UART's Baud Rate Generator and supports IrDA standard baud rates from 9600 baud to 115.2KBaud. Higher baud rates are possible, but do not meet IrDA specifications. The UART must be enabled to use the infrared endec. The infrared endec data rate is calculated using the following equation:

Infrared Data Rate (bits/s) =  $\frac{\text{System Clock Frequency (Hz)}}{16 \times \text{UART Baud Rate Divisor Value}}$

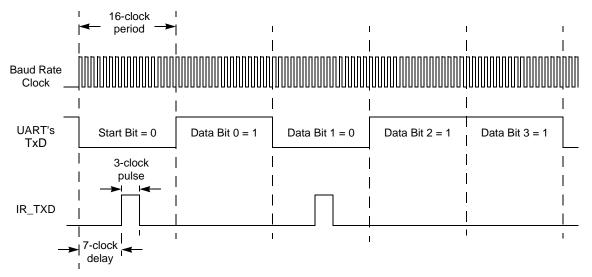

## **Transmitting IrDA Data**

The data to be transmitted using the infrared transceiver is first sent to the UART. The UART's transmit signal (TxD) and baud rate clock are used by the IrDA to generate the modulation signal (IR\_TXD) that drives the infrared transceiver. Each UART/Infrared data bit is 16-clock wide. If the data to be transmitted is 1, the **IR\_TXD** signal remains low for the full 16-clock period. If the data to be transmitted is 0, a 3-clock high pulse is output following a 7-clock low period. After the 3-clock high pulse, a 6-clock low pulse is output to complete the full 16-clock data period. Figure 20 displays IrDA data transmission. When the infrared endec is enabled, the UART's TxD signal is internal to the Z8 Encore! XP F64xx Series products while the IR\_TXD signal is output through the TxD pin.

Figure 20. Infrared Data Transmission

| Bit        | Description (Continued)                                                                                                                                                                                                                                                                                                                                                                                                                                        |

|------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| [4]        | Conversion                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

| CONT       | 0 = Single-shot conversion. ADC data is output once at completion of the 5129 system clock cycles.                                                                                                                                                                                                                                                                                                                                                             |

|            | 1 = Continuous conversion. ADC data updated every 256 system clock cycles.                                                                                                                                                                                                                                                                                                                                                                                     |

| [3:0]      | Analog Input Select                                                                                                                                                                                                                                                                                                                                                                                                                                            |

| ANAIN[3:0] | These bits select the analog input for conversion. For information about the Port pins avail-<br>able with each package style, see the <u>Signal and Pin Descriptions</u> chapter on page 7. Do<br>not enable unavailable analog inputs.<br>0000 = ANA0.<br>0001 = ANA1.<br>0010 = ANA2.<br>0011 = ANA3.<br>0100 = ANA4.<br>0101 = ANA5.<br>0110 = ANA6.<br>0111 = ANA7.<br>1000 = ANA8.<br>1001 = ANA9.<br>1010 = ANA10.<br>1011 = ANA11.<br>11xx = Reserved. |

166

Observe the following procedure to setup the Flash Sector Protect Register from user code:

- 1. Write 00H to the Flash Control Register to reset the Flash Controller.

- 2. Write 5EH to the Flash Control Register to select the Flash Sector Protect Register.

- 3. Read and/or write the Flash Sector Protect Register which is now at Register File address FF9H.

- 4. Write OOH to the Flash Control Register to return the Flash Controller to its reset state.

#### **Flash Write Protection Option Bit**

The Flash Write Protect option bit can be enabled to block all program and erase operations from user code. For more information, see the <u>Option Bits</u> chapter on page 180.

### **Byte Programming**

When the Flash Controller is unlocked, writes to Flash memory from user code will program a byte into the Flash if the address is located in the unlocked page. An erased Flash byte contains all ones (FFH). The programming operation can only be used to change bits from one to zero. To change a Flash bit (or multiple bits) from zero to one requires a Page Erase or Mass Erase operation.

Byte programming can be accomplished using the eZ8 CPU's LDC or LDCI instructions. For a description of the LDC and LDCI instructions, refer to the <u>eZ8 CPU Core User Manual (UM0128)</u>, which is available for download on <u>www.zilog.com</u>.

While the Flash Controller programs Flash memory, the eZ8 CPU idles but the system clock and on-chip peripherals continue to operate. Interrupts that occur when a programming operation is in progress are serviced after the programming operation is complete. To exit programming mode and lock the Flash Controller, write 00H to the Flash Control Register.

User code cannot program Flash memory on a page that resides in a protected sector. When user code writes memory locations, only addresses located in the unlocked page are programmed. Memory writes outside of the unlocked page are ignored.

#### **Caution:** Each memory location must not be programmed more than twice before an erase occurs.

Observe the following procedure to program the Flash from user code:

- 1. Write 00H to the Flash Control Register to reset the Flash Controller.

- 2. Write the page of memory to be programmed to the Page Select Register.

- 3. Write the first unlock command 73H to the Flash Control Register.

The write-only Flash Control Register shares its Register File address with the read-only Flash Status Register.

| Table 93. | Flash Con | trol Register | (FCTL)  |

|-----------|-----------|---------------|---------|

| 14010 001 |           |               | (·····/ |

| Bit     | 7 | 6 | 5 | 4  | 3  | 2 | 1 | 0 |

|---------|---|---|---|----|----|---|---|---|

| Field   |   |   |   | FC | MD |   |   |   |

| RESET   |   |   |   | (  | )  |   |   |   |

| R/W     |   |   |   | ۷  | V  |   |   |   |

| Address |   |   |   | FF | 8H |   |   |   |

| Bit   | Description                                 |  |

|-------|---------------------------------------------|--|

| [7:0] | Flash Command*                              |  |

| FCMD  | 73H = First unlock command.                 |  |

|       | 8CH = Second unlock command.                |  |

|       | 95H = Page erase command.                   |  |

|       | 63H = Mass erase command                    |  |

|       | 5EH = Flash Sector Protect Register select. |  |

# Flash Memory Address 0000H

### Table 99. Flash Option Bits At Flash Memory Address 0000H

| Bit                                             | 7                    | 6      | 5            | 5 4 |                   | 5 4 3 2 |                           | 2 | 1        | 0   |

|-------------------------------------------------|----------------------|--------|--------------|-----|-------------------|---------|---------------------------|---|----------|-----|

| Field                                           | WDT_RES              | WDT_AO | OSC_SEL[1:0] |     | C_SEL[1:0] VBO_AO |         | OSC_SEL[1:0] VBO_AO RP Re |   | Reserved | FWP |

| RESET                                           |                      | U      |              |     |                   |         |                           |   |          |     |

| R/W                                             | R/W                  |        |              |     |                   |         |                           |   |          |     |

| Address                                         | Program Memory 0000H |        |              |     |                   |         |                           |   |          |     |

| Note: U = Unchanged by Reset; R/W = Read/Write. |                      |        |              |     |                   |         |                           |   |          |     |

| Bit                   | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

|-----------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| [7]<br>WDT_RES        | <ul> <li>Watchdog Timer Reset</li> <li>0 = Watchdog Timer time-out generates an interrupt request. Interrupts must be globally enabled for the eZ8 CPU to acknowledge the interrupt request.</li> <li>1 = Watchdog Timer time-out causes a Short Reset. This setting is the default for unprogrammed (erased) Flash.</li> </ul>                                                                                                                                                                 |

| [6]<br>WDT_AO         | <ul> <li>Watchdog Timer Always On</li> <li>0 = Watchdog Timer is automatically enabled upon application of system power. Watchdog Timer can not be disabled except during STOP Mode (if configured to power down during STOP Mode).</li> <li>1 = Watchdog Timer is enabled upon execution of the WDT instruction. Once enabled, the Watchdog Timer can only be disabled by a Reset or Stop Mode Recovery. This setting is the default for unprogrammed (erased) Flash.</li> </ul>               |

| [5:4]<br>OSC_SEL[1:0] | <ul> <li>Oscillator Mode Selection</li> <li>00 = On-chip oscillator configured for use with external RC networks (&lt;4MHz).</li> <li>01 = Minimum power for use with very low frequency crystals (32kHz to 1.0MHz).</li> <li>10 = Medium power for use with medium frequency crystals or ceramic resonators (0.5MHz to 10.0MHz).</li> <li>11 = Maximum power for use with high frequency crystals (8.0MHz to 20.0MHz). This setting is the default for unprogrammed (erased) Flash.</li> </ul> |

| [3]<br>VBO_AO         | <ul> <li>Voltage Brown-Out Protection Always On</li> <li>0 = Voltage Brown-Out Protection is disabled in STOP Mode to reduce total power consumption.</li> <li>1 = Voltage Brown-Out Protection is always enabled including during STOP Mode. This setting is the default for unprogrammed (erased) Flash.</li> </ul>                                                                                                                                                                           |

| [2]<br>RP             | <ul> <li>Read Protect</li> <li>0 = User program code is inaccessible. Limited control features are available through the On-Chip Debugger.</li> <li>1 = User program code is accessible. All On-Chip Debugger commands are enabled. This setting is the default for unprogrammed (erased) Flash.</li> </ul>                                                                                                                                                                                     |

# **On-Chip Debugger Control Register Definitions**

This section describes the features of the On-Chip Debugger Control and Status registers.

# **OCD Control Register**

The OCD Control Register, shown in Table 103, controls the state of the On-Chip Debugger. This register enters or exits DEBUG Mode and enables the BRK instruction.

A *reset and stop* function can be achieved by writing 81H to this register. A *reset and go* function can be achieved by writing 41H to this register. If the device is operating in DEBUG Mode, a *run* function can be implemented by writing 40H to this register.

| Bit            | 7                                                                                                                                                                                                                                                                                                                                                                       | 6                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | 5      | 4       | 3 | 2        | 1 | 0       |  |  |  |

|----------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------|---------|---|----------|---|---------|--|--|--|

| Field          | DBGMODE                                                                                                                                                                                                                                                                                                                                                                 | BRKEN                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | DBGACK | BRKLOOP |   | Reserved |   | RST     |  |  |  |

| RESET          |                                                                                                                                                                                                                                                                                                                                                                         | 0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |        |         |   |          |   |         |  |  |  |

| R/W            |                                                                                                                                                                                                                                                                                                                                                                         | R/W R R                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |        |         |   |          |   |         |  |  |  |

| Bit            | Descriptio                                                                                                                                                                                                                                                                                                                                                              | on                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |        |         |   |          |   |         |  |  |  |

| [7]<br>DBGMODE | E Setting this<br>eZ8 CPU s<br>ning again<br>are enable<br>ting the de<br>0 = TheZ8                                                                                                                                                                                                                                                                                     | <b>DEBUG Mode</b><br>Setting this bit to 1 causes the device to enter DEBUG Mode. When in DEBUG Mode, the eZ8 CPU stops fetching new instructions. Clearing this bit causes the eZ8 CPU to start run ning again. This bit is automatically set when a BRK instruction is decoded and breakpoints are enabled. If the Read Protect option bit is enabled, this bit can only be cleared by resetting the device, it cannot be written to 0.<br>0 = TheZ8 Encore! XP F64xx Series device is operating in NORMAL Mode.<br>1 = The Z8 Encore! XP F64xx Series device is in DEBUG Mode. |        |         |   |          |   |         |  |  |  |

| [6]<br>BRKEN   | <b>Breakpoint Enable</b><br>This bit controls the behavior of the BRK instruction (op code 00H). By default, breakpoints are disabled and the BRK instruction behaves like a NOP. If this bit is set to 1 and a BRK instruction is decoded, the OCD takes action dependent upon the BRKLOOP bit.<br>0 = BRK instruction is disabled.<br>1 = BRK instruction is enabled. |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |        |         |   |          |   | d a BRK |  |  |  |

| [5]<br>DBGACK  | This bit en<br>an Debug<br>0 = Debug                                                                                                                                                                                                                                                                                                                                    | <ul> <li>Debug Acknowledge</li> <li>This bit enables the debug acknowledge feature. If this bit is set to 1, then the OCD sends an Debug Acknowledge character (FFH) to the host when a breakpoint occurs.</li> <li>0 = Debug Acknowledge is disabled.</li> <li>1 = Debug Acknowledge is enabled.</li> </ul>                                                                                                                                                                                                                                                                      |        |         |   |          |   |         |  |  |  |

#### Table 103. OCD Control Register (OCDCTL)

### Z8 Encore! XP<sup>®</sup> F64xx Series Product Specification

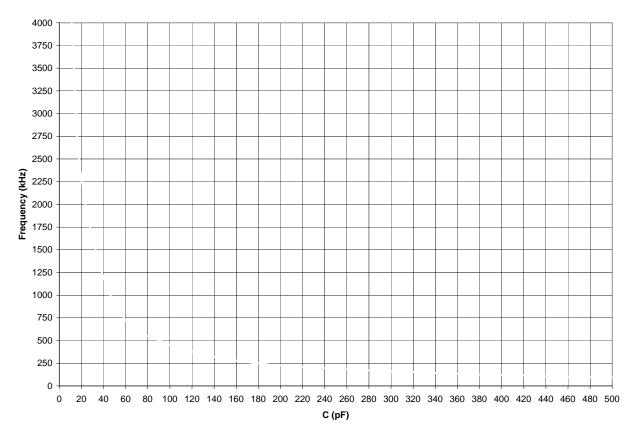

Figure 42. Typical RC Oscillator Frequency as a Function of the External Capacitance with a  $45k\Omega$  Resistor

**Caution:** When using the external RC oscillator mode, the oscillator may stop oscillating if the power supply drops below 2.7 V, but before the power supply drops to the voltage brown-out threshold. The oscillator will resume oscillation as soon as the supply voltage exceeds 2.7 V.

199

## Flash

For more information about these Flash Control registers, see the <u>Flash Control Register</u> <u>Definitions</u> section on page 175.

### Hex Address: FF8

#### Table 265. Flash Control Register (FCTL)

| Bit     | 7 | 6    | 5 | 4 | 3 | 2 | 1 | 0 |  |

|---------|---|------|---|---|---|---|---|---|--|

| Field   |   | FCMD |   |   |   |   |   |   |  |

| RESET   | 0 |      |   |   |   |   |   |   |  |

| R/W     | W |      |   |   |   |   |   |   |  |

| Address |   | FF8H |   |   |   |   |   |   |  |

#### Table 266. Flash Status Register (FSTAT)

| Bit     | 7    | 6     | 5     | 4 | 1 | 0 |  |  |  |  |

|---------|------|-------|-------|---|---|---|--|--|--|--|

| Field   | Rese | erved | FSTAT |   |   |   |  |  |  |  |

| RESET   |      | 0     |       |   |   |   |  |  |  |  |

| R/W     |      | R     |       |   |   |   |  |  |  |  |

| Address |      | FF8H  |       |   |   |   |  |  |  |  |

#### Hex Address: FF9

#### Table 267. Page Select Register (FPS)

| Bit     | 7       | 6    | 5    | 4 | 2 | 1 | 0 |  |  |  |

|---------|---------|------|------|---|---|---|---|--|--|--|

| Field   | INFO_EN |      | PAGE |   |   |   |   |  |  |  |

| RESET   |         | 0    |      |   |   |   |   |  |  |  |

| R/W     |         | R/W  |      |   |   |   |   |  |  |  |

| Address |         | FF9H |      |   |   |   |   |  |  |  |

|                         |            |          |           |            | -                   |                     |                  |     |                 |                                                |

|-------------------------|------------|----------|-----------|------------|---------------------|---------------------|------------------|-----|-----------------|------------------------------------------------|

| Part Number             | Flash      | RAM      | //O Lines | Interrupts | 16-Bit Timers w/PWM | 10-Bit A/D Channels | I <sup>2</sup> C | SPI | UARTs with IrDA | Description                                    |

| Z8F162x with 16KB Fla   | sh, 10-Bit | Analog   | -to-Di    | igital     | Со                  | nvert               | er               |     |                 |                                                |

| Standard Temperature:   | 0°C to 70  | °C       |           |            |                     |                     |                  |     |                 |                                                |

| Z8F1621PM020SG          | 16KB       | 2KB      | 29        | 23         | 3                   | 8                   | 1                | 1   | 2               | PDIP 40-pin package                            |

| Z8F1621AN020SG          | 16KB       | 2KB      | 31        | 23         | 3                   | 8                   | 1                | 1   | 2               | LQFP 44-pin package                            |

| Z8F1621VN020SG          | 16KB       | 2KB      | 31        | 23         | 3                   | 8                   | 1                | 1   | 2               | PLCC 44-pin package                            |

| Z8F1622AR020SG          | 16KB       | 2KB      | 46        | 24         | 4                   | 12                  | 1                | 1   | 2               | LQFP 64-pin package                            |

| Z8F1622VS020SG          | 16KB       | 2KB      | 46        | 24         | 4                   | 12                  | 1                | 1   | 2               | PLCC 68-pin package                            |

| Extended Temperature    | : –40°C to | +105°C   |           |            |                     |                     |                  |     |                 |                                                |

| Z8F1621PM020EG          | 16KB       | 2KB      | 29        | 23         | 3                   | 8                   | 1                | 1   | 2               | PDIP 40-pin package                            |

| Z8F1621AN020EG          | 16KB       | 2KB      | 31        | 23         | 3                   | 8                   | 1                | 1   | 2               | LQFP 44-pin package                            |

| Z8F1621VN020EG          | 16KB       | 2KB      | 31        | 23         | 3                   | 8                   | 1                | 1   | 2               | PLCC 44-pin package                            |

| Z8F1622AR020EG          | 16KB       | 2KB      | 46        | 24         | 4                   | 12                  | 1                | 1   | 2               | LQFP 64-pin package                            |

| Z8F1622VS020EG          | 16KB       | 2KB      | 46        | 24         | 4                   | 12                  | 1                | 1   | 2               | PLCC 68-pin package                            |

| Automotive/Industrial 1 | Femperatu  | re: –40° | C to      | +125       | 5°C                 |                     |                  |     |                 |                                                |

| Z8F1621PM020AG          | 16KB       | 2KB      | 29        | 23         | 3                   | 8                   | 1                | 1   | 2               | PDIP 40-pin package                            |

| Z8F1621AN020AG          | 16KB       | 2KB      | 31        | 23         | 3                   | 8                   | 1                | 1   | 2               | LQFP 44-pin package                            |

| Z8F1621VN020AG          | 16KB       | 2KB      | 31        | 23         | 3                   | 8                   | 1                | 1   | 2               | PLCC 44-pin package                            |

| Z8F1622AR020AG          | 16KB       | 2KB      | 46        | 24         | 4                   | 12                  | 1                | 1   | 2               | LQFP 64-pin package                            |

| Z8F1622VS020AG          | 16KB       | 2KB      | 46        | 24         | 4                   | 12                  | 1                | 1   | 2               | PLCC 68-pin package                            |

| Z8F64200100KITG         |            |          |           |            |                     |                     |                  |     |                 | Development Kit                                |

| ZUSBSC00100ZACG         |            |          |           |            |                     |                     |                  |     |                 | USB Smart Cable<br>Accessory Kit               |

| ZUSBOPTSC01ZACG         |            |          |           |            |                     |                     |                  |     |                 | Opto-Isolated USB Smart<br>Cable Accessory Kit |

| ZENETSC0100ZACG         |            |          |           |            |                     |                     |                  |     |                 | Ethernet Smart Cable<br>Accessory Kit          |

## Table 271. Z8 Encore! XP F64xx Series Ordering Matrix

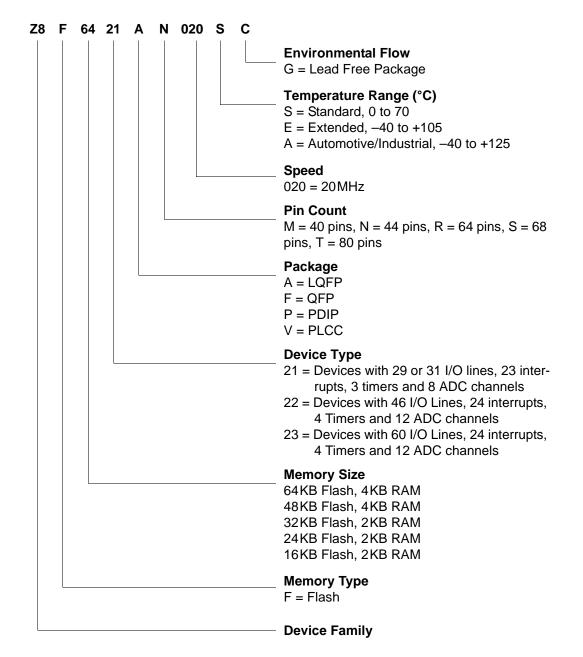

# **Part Number Suffix Designations**

Zilog part numbers consist of a number of component. In the following example, part number Z8F6421AN020SG is an 8-bit Flash MCU with 4KB of program memory in a 44-pin LQFP package, operating with a maximum 20MHz external clock frequency over a 0°C to +70°C temperature range and built using environmentally friendly (lead-free) solder.