Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

#### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Details                    |                                                           |

|----------------------------|-----------------------------------------------------------|

| Product Status             | Active                                                    |

| Core Processor             | eZ8                                                       |

| Core Size                  | 8-Bit                                                     |

| Speed                      | 20MHz                                                     |

| Connectivity               | I <sup>2</sup> C, IrDA, SPI, UART/USART                   |

| Peripherals                | Brown-out Detect/Reset, DMA, POR, PWM, WDT                |

| Number of I/O              | 46                                                        |

| Program Memory Size        | 16KB (16K x 8)                                            |

| Program Memory Type        | FLASH                                                     |

| EEPROM Size                | -                                                         |

| RAM Size                   | 2K x 8                                                    |

| Voltage - Supply (Vcc/Vdd) | 3V ~ 3.6V                                                 |

| Data Converters            | A/D 12x10b                                                |

| Oscillator Type            | Internal                                                  |

| Operating Temperature      | -40°C ~ 105°C (TA)                                        |

| Mounting Type              | Surface Mount                                             |

| Package / Case             | 64-LQFP                                                   |

| Supplier Device Package    | -                                                         |

| Purchase URL               | https://www.e-xfl.com/product-detail/zilog/z8f1622ar020eg |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

| Priority | Program Memory<br>Vector Address | Interrupt Source                                           |  |  |  |  |

|----------|----------------------------------|------------------------------------------------------------|--|--|--|--|

| Highest  | 0002H                            | Reset (not an interrupt)                                   |  |  |  |  |

|          | 0004H                            | Watchdog Timer (see the Watchdog Timer chapter on page 80) |  |  |  |  |

|          | 0006H                            | Illegal Instruction Trap (not an interrupt)                |  |  |  |  |

|          | 0008H                            | Timer 2                                                    |  |  |  |  |

|          | 000AH                            | Timer 1                                                    |  |  |  |  |

|          | 000CH                            | Timer 0                                                    |  |  |  |  |

|          | 000EH                            | UART 0 receiver                                            |  |  |  |  |

|          | 0010H                            | UART 0 transmitter                                         |  |  |  |  |

|          | 0012H                            | l <sup>2</sup> C                                           |  |  |  |  |

|          | 0014H                            | SPI                                                        |  |  |  |  |

|          | 0016H                            | ADC                                                        |  |  |  |  |

|          | 0018H                            | Port A7 or Port D7, rising or falling input edge           |  |  |  |  |

|          | 001AH                            | Port A6 or Port D6, rising or falling input edge           |  |  |  |  |

|          | 001CH                            | Port A5 or Port D5, rising or falling input edge           |  |  |  |  |

|          | 001EH                            | Port A4 or Port D4, rising or falling input edge           |  |  |  |  |

|          | 0020H                            | Port A3 or Port D3, rising or falling input edge           |  |  |  |  |

|          | 0022H                            | Port A2 or Port D2, rising or falling input edge           |  |  |  |  |

|          | 0024H                            | Port A1 or Port D1, rising or falling input edge           |  |  |  |  |

|          | 0026H                            | Port A0 or Port D0, rising or falling input edge           |  |  |  |  |

|          | 0028H                            | Timer 3 (not available in the 44-pin package)              |  |  |  |  |

|          | 002AH                            | UART 1 receiver                                            |  |  |  |  |

|          | 002CH                            | UART 1 transmitter                                         |  |  |  |  |

|          | 002EH                            | DMA                                                        |  |  |  |  |

|          | 0030H                            | Port C3, both input edges                                  |  |  |  |  |

|          | 0032H                            | Port C2, both input edges                                  |  |  |  |  |

|          | 0034H                            | Port C1, both input edges                                  |  |  |  |  |

| Lowest   | 0036H                            | Port C0, both input edges                                  |  |  |  |  |

## Table 23. Interrupt Vectors in Order of Priority

## 59

# Table 35. IRQ2 Enable Low Bit Register (IRQ2ENL)

| Bit           | 7           | 6                                               | 5           | 4            | 3       | 2     | 1     | 0     |

|---------------|-------------|-------------------------------------------------|-------------|--------------|---------|-------|-------|-------|

| Field         | T3ENL       | U1RENL                                          | U1TENL      | DMAENL       | C3ENL   | C2ENL | C1ENL | C0ENL |

| RESET         |             |                                                 |             | (            | )       |       |       |       |

| R/W           |             |                                                 |             | R/           | W       |       |       |       |

| Address       |             |                                                 |             | FC           | 8H      |       |       |       |

| Bit           | Descriptio  | n                                               |             |              |         |       |       |       |

| [7]<br>T3ENL  | Timer 3 Int | imer 3 Interrupt Request Enable Low Bit         |             |              |         |       |       |       |

| [6]<br>U1RENL | UART 1 Re   | UART 1 Receive Interrupt Request Enable Low Bit |             |              |         |       |       |       |

| [5]<br>U1TENL | UART 1 Tra  | ansmit Inte                                     | rrupt Reque | est Enable I | _ow Bit |       |       |       |

| [4]<br>DMAENL | DMA Interr  | DMA Interrupt Request Enable Low Bit            |             |              |         |       |       |       |

| [3]<br>C3ENL  | Port C3 Int | errupt Req                                      | uest Enable | E Low Bit    |         |       |       |       |

| [2]<br>C2ENL  | Port C2 Int | Port C2 Interrupt Request Enable Low Bit        |             |              |         |       |       |       |

| [1]<br>C1ENL  | Port C1 Int | errupt Req                                      | uest Enable | e Low Bit    |         |       |       |       |

| [0]<br>C0ENL  | Port C0 Int | errupt Req                                      | uest Enable | E Low Bit    |         |       |       |       |

- Disable the timer

- Configure the timer for CONTINUOUS Mode

- Set the prescale value

- If using the timer output alternate function, set the initial output level (High or Low)

- 2. Write to the Timer High and Low Byte registers to set the starting count value (usually 0001H), affecting only the first pass in CONTINUOUS Mode. After the first timer reload in CONTINUOUS Mode, counting always begins at the reset value of 0001H.

- 3. Write to the Timer Reload High and Low Byte registers to set the reload value.

- 4. If appropriate, enable the timer interrupt and set the timer interrupt priority by writing to the relevant interrupt registers.

- 5. If using the timer output function, configure the associated GPIO port pin for the timer output alternate function.

- 6. Write to the Timer Control 1 Register to enable the timer and initiate counting.

In CONTINUOUS Mode, the system clock always provides the timer input. The timer period is calculated using the following equation:

CONTINUOUS Mode Time-Out Period (s) =  $\frac{\text{Reload Value} \times \text{Prescale}}{\text{System Clock Frequency (Hz)}}$

If an initial starting value other than 0001H is loaded into the Timer High and Low Byte registers, the ONE-SHOT Mode equation must be used to determine the first time-out period.

## **COUNTER Mode**

In COUNTER Mode, the timer counts input transitions from a GPIO port pin. The timer input is taken from the GPIO port pin timer input alternate function. The TPOL bit in the Timer Control 1 Register selects whether the count occurs on the rising edge or the falling edge of the timer input signal. In COUNTER Mode, the prescaler is disabled.

**Caution:** The input frequency of the timer input signal must not exceed one-fourth the system clock frequency.

Upon reaching the reload value stored in the Timer Reload High and Low Byte registers, the timer generates an interrupt, the count value in the Timer High and Low Byte registers is reset to 0001H and counting resumes. Also, if the timer output alternate function is

## Table 48. Watchdog Timer Control Register (WDTCTL)

| Bit         | 7                                                                                                                                                                                                                                                                                                                                                                                                                                               | 6                                                                                                                                                                                                                                                  | 5   | 4   | 3 | 2        | 1 | 0 |  |

|-------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|-----|---|----------|---|---|--|

| Field       | POR                                                                                                                                                                                                                                                                                                                                                                                                                                             | STOP                                                                                                                                                                                                                                               | WDT | EXT |   | Reserved |   |   |  |

| RESET       | S                                                                                                                                                                                                                                                                                                                                                                                                                                               | See Table 49                                                                                                                                                                                                                                       | ).  |     |   | 0        |   |   |  |

| R/W         |                                                                                                                                                                                                                                                                                                                                                                                                                                                 | R                                                                                                                                                                                                                                                  |     |     |   |          |   |   |  |

| Address     |                                                                                                                                                                                                                                                                                                                                                                                                                                                 | FF0H                                                                                                                                                                                                                                               |     |     |   |          |   |   |  |

| Bit         | Doscriptio                                                                                                                                                                                                                                                                                                                                                                                                                                      | Description                                                                                                                                                                                                                                        |     |     |   |          |   |   |  |

| [7]<br>POR  | Power-On<br>If this bit is                                                                                                                                                                                                                                                                                                                                                                                                                      | <b>Description</b><br>Power-On Reset Indicator<br>If this bit is set to 1, a Power-On Reset event occurred. This bit is reset to 0 if a WDT time-out<br>If Stop Mode Recovery occurs. This bit is also reset to 0 when the register is read.       |     |     |   |          |   |   |  |

| [6]<br>STOP | <b>Stop Mode Recovery Indicator</b><br>If this bit is set to 1, a Stop Mode Recovery occurred. If the stop and WDT bits are both set to 1, the Stop Mode Recovery occurred due to a WDT time-out. If the stop bit is 1 and the WDT bit is 0, the Stop Mode Recovery was not caused by a WDT time-out. This bit is reset by a Power-On Reset or a WDT time-out that occurred while not in STOP Mode. Reading this register also resets this bit. |                                                                                                                                                                                                                                                    |     |     |   |          |   |   |  |

| [5]<br>WDT  | If this bit is                                                                                                                                                                                                                                                                                                                                                                                                                                  | <b>Watchdog Timer Time-Out Indicator</b><br>If this bit is set to 1, a WDT time-out occurred. A Power-On Reset resets this pin. A Stop Mode<br>Recovery from a change in an input pin also resets this bit. Reading this register resets this bit. |     |     |   |          |   |   |  |

| [4]<br>EXT  | If this bit is or a Stop M                                                                                                                                                                                                                                                                                                                                                                                                                      | <b>External Reset Indicator</b><br>If this bit is set to 1, a Reset initiated by the external RESET pin occurred. A Power-On Reset or a Stop Mode Recovery from a change in an input pin resets this bit. Reading this register resets this bit.   |     |     |   |          |   |   |  |

| [3:1]       | Reserved<br>These bits a                                                                                                                                                                                                                                                                                                                                                                                                                        | <b>Reserved</b><br>These bits are reserved and must be programmed to 000.                                                                                                                                                                          |     |     |   |          |   |   |  |

| [0]<br>SM   | 0 = Watchd                                                                                                                                                                                                                                                                                                                                                                                                                                      | <b>STOP Mode Configuration Indicator</b><br>0 = Watchdog Timer and its internal RC oscillator will continue to operate in STOP Mode.<br>1 = Watchdog Timer and its internal RC oscillator will be disabled in STOP Mode.                           |     |     |   |          |   |   |  |

89

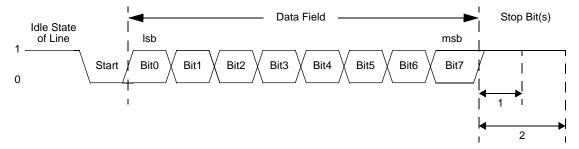

Figure 14. UART Asynchronous Data Format without Parity

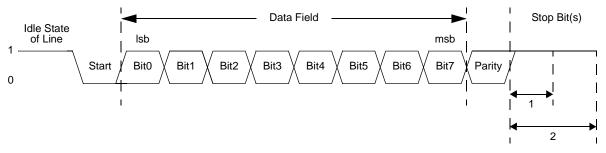

Figure 15. UART Asynchronous Data Format with Parity

# **Transmitting Data using the Polled Method**

Observe the following procedure to transmit data using the polled method of operation:

- 1. Write to the UART Baud Rate High and Low Byte registers to set the appropriate baud rate.

- 2. Enable the UART pin functions by configuring the associated GPIO port pins for alternate function operation.

- 3. If MULTIPROCESSOR Mode is appropriate, write to the UART Control 1 Register to enable MULTIPROCESSOR (9-Bit) Mode functions.

- Set the MULTIPROCESSOR Mode Select (MPEN) to Enable MULTIPROCES-SOR Mode

- 4. Write to the UART Control 0 Register to:

- Set the transmit enable bit (TEN) to enable the UART for data transmission

- If parity is appropriate and MULTIPROCESSOR Mode is not enabled, set the parity enable bit (PEN) and select either Even or Odd parity (PSEL)

In MULTIPROCESSOR (9-Bit) Mode, the parity bit location (9th bit) becomes the MUL-TIPROCESSOR control bit. The UART Control 1 and Status 1 registers provide MULTI-PROCESSOR (9-Bit) Mode control and status information. If an automatic address matching scheme is enabled, the UART Address Compare Register holds the network address of the device.

#### MULTIPROCESSOR (9-bit) Mode Receive Interrupts

When MULTIPROCESSOR Mode is enabled, the UART only processes frames addressed to it. The determination of whether a frame of data is addressed to the UART can be made in hardware, software or some combination of the two, depending on the multiprocessor configuration bits. In general, the address compare feature reduces the load on the CPU, since it does not need to access the UART when it receives data directed to other devices on the multinode network. The following three MULTIPROCESSOR modes are available in hardware:

- Interrupt on all address bytes

- Interrupt on matched address bytes and correctly framed data bytes

- Interrupt only on correctly framed data bytes

These modes are selected with MPMD[1:0] in the UART Control 1 Register. For all MULTIPROCESSOR modes, bit MPEN of the UART Control 1 Register must be set to 1.

The first scheme is enabled by writing 01b to MPMD[1:0]. In this mode, all incoming address bytes cause an interrupt, while data bytes never cause an interrupt. The interrupt service routine must manually check the address byte that caused triggered the interrupt. If it matches the UART address, the software clears MPMD[0]. At this point, each new incoming byte interrupts the CPU. The software is then responsible for determining the end of the frame. It checks for end-of-frame by reading the MPRX bit of the UART Status 1 Register for each incoming byte. If MPRX=1, a new frame has begun. If the address of this new frame is different from the UART's address, then set MPMD[0] to 1 causing the UART interrupts to go inactive until the next address byte. If the new frame's address matches the UART's, the data in the new frame is processed as well.

The second scheme is enabled by setting MPMD[1:0] to 10b and writing the UART's address into the UART Address Compare Register. This mode introduces more hardware control, interrupting only on frames that match the UART's address. When an incoming address byte does not match the UART's address, it is ignored. All successive data bytes in this frame are also ignored. When a matching address byte occurs, an interrupt is issued and further interrupts now occur on each successive data byte. The first data byte in the frame contains the NEWFRM=1 in the UART Status 1 Register. When the next address byte occurs, the hardware compares it to the UART's address. If there is a match, the interrupts continue sand the NEWFRM bit is set for the first byte of the new frame. If there is no match, then the UART ignores all incoming bytes until the next address match.

# **UART Address Compare Register**

The UART Address Compare Register, shown in Table 59, stores the multinode network address of the UART. When the MPMD[1] bit of UART Control Register 0 is set, all incoming address bytes are compared to the value stored in the Address Compare Register. Receive interrupts and RDA assertions only occur in the event of a match.

| Bit     | 7    | 6               | 5 | 4 | 3 | 2 | 1 | 0 |  |  |  |

|---------|------|-----------------|---|---|---|---|---|---|--|--|--|

| Field   |      | COMP_ADDR       |   |   |   |   |   |   |  |  |  |

| RESET   |      | 0               |   |   |   |   |   |   |  |  |  |

| R/W     |      | R/W             |   |   |   |   |   |   |  |  |  |

| Address |      | F45H and F4DH   |   |   |   |   |   |   |  |  |  |

| Bit     | Desc | Description     |   |   |   |   |   |   |  |  |  |

| [7:0]   | Com  | Compare Address |   |   |   |   |   |   |  |  |  |

# **UART Baud Rate High and Low Byte Registers**

COMP ADDR This 8-bit value is compared to the incoming address bytes.

The UART Baud Rate High and Low Byte registers, shown in Tables 60 and 61, combine to create a 16-bit baud rate divisor value (BRG[15:0]) that sets the data transmission rate (baud rate) of the UART. To configure the Baud Rate Generator as a timer with interrupt on time-out, complete the following procedure:

- 1. Disable the UART by clearing the REN and TEN bits in the UART Control 0 Register to 0.

- 2. Load the appropriate 16-bit count value into the UART Baud Rate High and Low Byte registers.

- 3. Enable the Baud Rate Generator timer function and associated interrupt by setting the BRGCTL bit in the UART Control 1 Register to 1.

When configured as a general-purpose timer, the UART BRG interrupt interval is calculated using the following equation:

UART BRG Interrupt Interval(s) = System Clock Period (s)  $\times$  BRG[15:0]

#### Table 60. UART Baud Rate High Byte Register (UxBRH)

| Bit     | 7 | 6   | 5 | 4       | 3       | 2 | 1 | 0 |  |

|---------|---|-----|---|---------|---------|---|---|---|--|

| Field   |   | BRH |   |         |         |   |   |   |  |

| RESET   | 1 |     |   |         |         |   |   |   |  |

| R/W     |   | R/W |   |         |         |   |   |   |  |

| Address |   |     |   | F46H ar | nd F4EH |   |   |   |  |

#### Table 61. UART Baud Rate Low Byte Register (UxBRL)

| Bit7    | 7   | 6   | 5 | 4       | 3       | 2 | 1 | 0 |

|---------|-----|-----|---|---------|---------|---|---|---|

| Field   |     | BRL |   |         |         |   |   |   |

| RESET   | 1   |     |   |         |         |   |   |   |

| R/W     | R/W |     |   |         |         |   |   |   |

| Address |     |     |   | F47H ar | nd F4FH |   |   |   |

For a given UART data rate, the integer baud rate divisor value is calculated using the following equation:

UART Baud Rate Divisor Value (BRG) = Round  $\left(\frac{\text{System Clock Frequency (Hz)}}{16 \times \text{UART Data Rate (bits/s)}}\right)$

The baud rate error relative to the appropriate baud rate is calculated using the following equation:

UART Baud Rate Error (%) =

$$100 \times \left(\frac{\text{Actual Data Rate} - \text{Desired Data Rate}}{\text{Desired Data Rate}}\right)$$

For reliable communication, the UART baud rate error must never exceed 5 percent. Table 62 lists data rate errors for popular baud rates and commonly used crystal oscillator frequencies.

# I<sup>2</sup>C Diagnostic Control Register

The I<sup>2</sup>C Diagnostic Register, shown in Table 77, provides control over diagnostic modes. This register is a read/write register that is used for I<sup>2</sup>C diagnostics purposes.

# Table 77. I<sup>2</sup>C Diagnostic Control Register (I2CDIAG)

| 7        | 6 | 5   | 4     | 3                    | 2                         | 1                  | 0                  |

|----------|---|-----|-------|----------------------|---------------------------|--------------------|--------------------|

| Reserved |   |     |       |                      |                           |                    | DIAG               |

| 0        |   |     |       |                      |                           |                    |                    |

| R        |   |     |       |                      |                           |                    | R/W                |

| F56H     |   |     |       |                      |                           |                    |                    |

| -        | 7 | 7 6 | 7 6 5 | Reserved<br>Reserved | Reserved<br>Reserved<br>R | Reserved<br>0<br>R | Reserved<br>0<br>R |

| Bit         | Description                                                                                                                                                                                                                                                                                                                                              |

|-------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| [7:1]       | <b>Reserved</b><br>These bits are reserved and must be programmed to 0000000.                                                                                                                                                                                                                                                                            |

| [0]<br>DIAG | <ul> <li>Diagnostic Control Bit</li> <li>Selects read back value of the Baud Rate Reload registers.</li> <li>0 = NORMAL Mode. Reading the Baud Rate High and Low Byte registers returns the baud rate reload value.</li> <li>1 = DIAGNOSTIC Mode. Reading the Baud Rate High and Low Byte registers returns the baud rate rate counter value.</li> </ul> |

# DMA\_ADC Address Register

The DMA\_ADC Address Register, shown in Table 84, points to a block of the Register File to store the ADC conversion values displayed in Table 83. This register contains the seven most significant bits of the 12-bit Register File addresses. The five least significant bits are calculated from the ADC analog input number (5-bit base address is equal to twice the ADC analog input number). The 10-bit ADC conversion data is stored as two bytes with the most significant byte of the ADC data stored at the even-numbered Register File address.

Table 83 provides an example of the Register File addresses if the DMA\_ADC Address Register contains the value 72H.

| ADC Analog Input    | Register File Address<br>(Hex)* |

|---------------------|---------------------------------|

| 0                   | 720H–721H                       |

| 1                   | 722H–723H                       |

| 2                   | 724H–725H                       |

| 3                   | 726H–727H                       |

| 4                   | 728H–729H                       |

| 5                   | 72AH–72BH                       |

| 6                   | 72CH–72DH                       |

| 7                   | 72EH–72FH                       |

| 8                   | 730H–731H                       |

| 9                   | 732H–733H                       |

| 10                  | 734H–735H                       |

| 11                  | 736H–737H                       |

| Note: *DMAA_ADDR is | set to 72H.                     |

Table 83. DMA\_ADC Register File Address Example

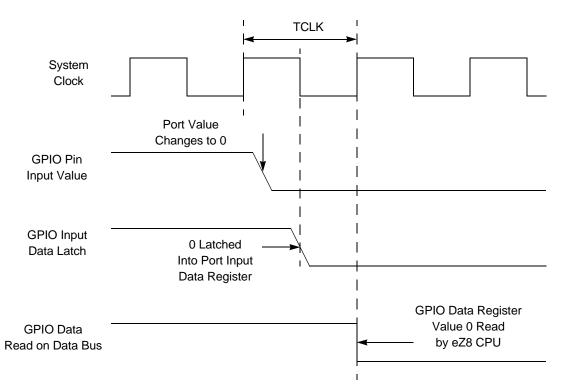

# General-Purpose I/O Port Input Data Sample Timing

Figure 50 displays timing of the GPIO Port input sampling. Table 115 lists the GPIO port input timing.

#### Table 115. GPIO Port Input Timing

|                     |                                                                                                    | Delay (ns) |     |  |

|---------------------|----------------------------------------------------------------------------------------------------|------------|-----|--|

| Parameter           | Abbreviation                                                                                       | Min        | Max |  |

| T <sub>S_PORT</sub> | Port Input Transition to X <sub>IN</sub> Fall Setup Time (not pictured)                            | 5          | _   |  |

| T <sub>H_PORT</sub> | X <sub>IN</sub> Fall to Port Input Transition Hold Time (not pictured)                             | 6          | _   |  |

| T <sub>SMR</sub>    | GPIO Port Pin Pulse Width to Insure Stop Mode Recovery (for GPIO Port pins enabled as SMR sources) | 1 μs       |     |  |

# **SPI Master Mode Timing**

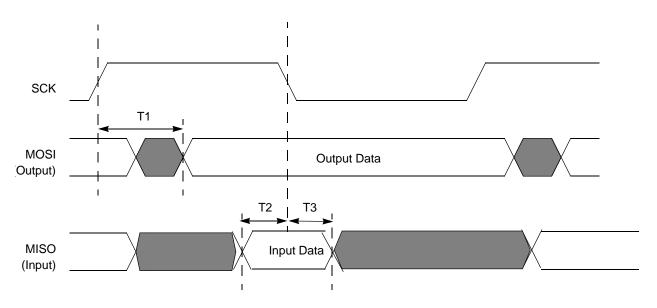

Figure 53 and Table 118 provide timing information for SPI Master Mode pins. Timing is shown with SCK rising edge used to source MOSI output data, SCK falling edge used to sample MISO input data. Timing on the SS output pin(s) is controlled by software.

Figure 53. SPI Master Mode Timing

|                |                                             | Delay (ns) |     |  |

|----------------|---------------------------------------------|------------|-----|--|

| Parameter      | Abbreviation                                | Min        | Max |  |

| SPI Master     |                                             |            |     |  |

| T <sub>1</sub> | SCK Rise to MOSI output Valid Delay         | -5         | +5  |  |

| T <sub>2</sub> | MISO input to SCK (receive edge) Setup Time | 20         |     |  |

| T <sub>3</sub> | MISO input to SCK (receive edge) Hold Time  | 0          |     |  |

#### Table 118. SPI Master Mode Timing

| Mnemonic | Operands | Instruction                                   |

|----------|----------|-----------------------------------------------|

| MULT     | dst      | Multiply                                      |

| SBC      | dst, src | Subtract with Carry                           |

| SBCX     | dst, src | Subtract with Carry using Extended Addressing |

| SUB      | dst, src | Subtract                                      |

| SUBX     | dst, src | Subtract using Extended Addressing            |

#### Table 129. Bit Manipulation Instructions

| Mnemonic | Operands    | Instruction                                          |

|----------|-------------|------------------------------------------------------|

| BCLR     | bit, dst    | Bit Clear                                            |

| BIT      | p, bit, dst | Bit Set or Clear                                     |

| BSET     | bit, dst    | Bit Set                                              |

| BSWAP    | dst         | Bit Swap                                             |

| CCF      |             | Complement Carry Flag                                |

| RCF      | —           | Reset Carry Flag                                     |

| SCF      |             | Set Carry Flag                                       |

| ТСМ      | dst, src    | Test Complement Under Mask                           |

| ТСМХ     | dst, src    | Test Complement Under Mask using Extended Addressing |

| ТМ       | dst, src    | Test Under Mask                                      |

| ТМХ      | dst, src    | Test Under Mask using Extended Addressing            |

#### Table 130. Block Transfer Instructions

| Mnemonic | Operands | Instruction                                                              |

|----------|----------|--------------------------------------------------------------------------|

| LDCI     | dst, src | Load Constant to/from program memory and Auto-Incre-<br>ment addresses   |

| LDEI     | dst, src | Load External Data to/from Data Memory and Auto-Incre-<br>ment addresses |

260

# Hex Address: F4A

#### Table 182. UART Control 0 Register (UxCTL0)

| Bit     | 7   | 6             | 5    | 4   | 3    | 2    | 1    | 0    |  |  |

|---------|-----|---------------|------|-----|------|------|------|------|--|--|

| Field   | TEN | REN           | CTSE | PEN | PSEL | SBRK | STOP | LBEN |  |  |

| RESET   | 0   |               |      |     |      |      |      |      |  |  |

| R/W     |     | R/W           |      |     |      |      |      |      |  |  |

| Address |     | F42H and F4AH |      |     |      |      |      |      |  |  |

# Hex Address: F4B

#### Table 183. UART Control 1 Register (UxCTL1)

| Bit     | 7       | 6    | 5       | 4       | 3       | 2      | 1      | 0    |  |  |  |

|---------|---------|------|---------|---------|---------|--------|--------|------|--|--|--|

| Field   | MPMD[1] | MPEN | MPMD[0] | MPBT    | DEPOL   | BRGCTL | RDAIRQ | IREN |  |  |  |

| RESET   |         | 0    |         |         |         |        |        |      |  |  |  |

| R/W     |         | R/W  |         |         |         |        |        |      |  |  |  |

| Address |         |      |         | F43H ar | nd F4BH |        |        |      |  |  |  |

# Hex Address: F4C

## Table 184. UART Status 1 Register (UxSTAT1)

| Bit     | 7                    | 6 | 5 | 4       | 3       | 2 | 1 | 0 |  |  |

|---------|----------------------|---|---|---------|---------|---|---|---|--|--|

| Field   | Reserved NEWFRM MPRX |   |   |         |         |   |   |   |  |  |

| RESET   | 0                    |   |   |         |         |   |   |   |  |  |

| R/W     | R R/W R              |   |   |         |         |   |   | 2 |  |  |

| Address |                      |   |   | F44H ar | nd F4CH |   |   |   |  |  |

# Hex Address: F4D

#### Table 185. UART Address Compare Register (UxADDR)

| Bit     | 7         | 6   | 5 | 4       | 3       | 2 | 1 | 0 |  |  |

|---------|-----------|-----|---|---------|---------|---|---|---|--|--|

| Field   | COMP_ADDR |     |   |         |         |   |   |   |  |  |

| RESET   | 0         |     |   |         |         |   |   |   |  |  |

| R/W     |           | R/W |   |         |         |   |   |   |  |  |

| Address |           |     |   | F45H ar | nd F4DH |   |   |   |  |  |

# Hex Address: F55

# Table 193. I<sup>2</sup>C Diagnostic State Register (I2CDST)

| Bit     | 7     | 6     | 5      | 4         | 3 | 2 | 1 | 0 |  |

|---------|-------|-------|--------|-----------|---|---|---|---|--|

| Field   | SCLIN | SDAIN | STPCNT | TXRXSTATE |   |   |   |   |  |

| RESET   | >     | <     |        | 0         |   |   |   |   |  |

| R/W     |       | R     |        |           |   |   |   |   |  |

| Address |       | F55H  |        |           |   |   |   |   |  |

# Hex Address: F56

# Table 194. I<sup>2</sup>C Diagnostic Control Register (I2CDIAG)

| Bit     | 7        | 6    | 5 | 4 | 3 | 2 | 1 | 0 |  |  |

|---------|----------|------|---|---|---|---|---|---|--|--|

| Field   | Reserved |      |   |   |   |   |   |   |  |  |

| RESET   | 0        |      |   |   |   |   |   |   |  |  |

| R/W     | R        |      |   |   |   |   |   |   |  |  |

| Address |          | F56H |   |   |   |   |   |   |  |  |

# Hex Addresses: F57–F5F

This address range is reserved.

# **Serial Peripheral Interface**

For more information about these SPI Control registers, see the <u>SPI Control Register Def-initions</u> section on page 121.

# Hex Address: F60

#### Table 195. SPI Data Register (SPIDATA)

| Bit     | 7    | 6   | 5 | 4  | 3  | 2 | 1 | 0 |  |  |

|---------|------|-----|---|----|----|---|---|---|--|--|

| Field   | DATA |     |   |    |    |   |   |   |  |  |

| RESET   | X    |     |   |    |    |   |   |   |  |  |

| R/W     |      | R/W |   |    |    |   |   |   |  |  |

| Address |      |     |   | F6 | 0H |   |   |   |  |  |

# Hex Address: F64

#### Table 199. SPI Diagnostic State Register (SPIDST)

| Bit     | 7     | 6     | 5        | 4  | 3  | 2 | 1 | 0 |  |  |

|---------|-------|-------|----------|----|----|---|---|---|--|--|

| Field   | SCKEN | TCKEN | SPISTATE |    |    |   |   |   |  |  |

| RESET   |       | 0     |          |    |    |   |   |   |  |  |

| R/W     |       | R     |          |    |    |   |   |   |  |  |

| Address |       |       |          | F6 | 4H |   |   |   |  |  |

# Hex Address: F65

This address is reserved.

## Hex Address: F66

#### Table 200. SPI Baud Rate High Byte Register (SPIBRH)

| Bit     | 7    | 6 | 5 | 4 | 3 | 2 | 1 | 0 |  |  |

|---------|------|---|---|---|---|---|---|---|--|--|

| Field   | BRH  |   |   |   |   |   |   |   |  |  |

| RESET   | 1    |   |   |   |   |   |   |   |  |  |

| R/W     | R/W  |   |   |   |   |   |   |   |  |  |

| Address | F66H |   |   |   |   |   |   |   |  |  |

## Hex Address: F67

#### Table 201. SPI Baud Rate Low Byte Register (SPIBRL)

| Bit     | 7   | 6   | 5 | 4  | 3  | 2 | 1 | 0 |  |  |  |

|---------|-----|-----|---|----|----|---|---|---|--|--|--|

| Field   | BRL |     |   |    |    |   |   |   |  |  |  |

| RESET   | 1   |     |   |    |    |   |   |   |  |  |  |

| R/W     |     | R/W |   |    |    |   |   |   |  |  |  |

| Address |     |     |   | F6 | 7H |   |   |   |  |  |  |

# Hex Addresses: F68–F6F

This address range is reserved.

# Hex Address: FC1

#### Table 218. IRQ0 Enable High Bit Register (IRQ0ENH)

| Bit     | 7     | 6     | 5     | 4             | 3      | 2      | 1      | 0      |  |  |  |

|---------|-------|-------|-------|---------------|--------|--------|--------|--------|--|--|--|

| Field   | T2ENH | T1ENH | T0ENH | <b>U0RENH</b> | U0TENH | I2CENH | SPIENH | ADCENH |  |  |  |

| RESET   | 0     |       |       |               |        |        |        |        |  |  |  |

| R/W     |       | R/W   |       |               |        |        |        |        |  |  |  |

| Address |       | FC1H  |       |               |        |        |        |        |  |  |  |

# Hex Address: FC2

#### Table 219. IRQ0 Enable Low Bit Register (IRQ0ENL)

| Bit     | 7     | 6     | 5     | 4             | 3             | 2      | 1      | 0      |  |  |  |

|---------|-------|-------|-------|---------------|---------------|--------|--------|--------|--|--|--|

| Field   | T2ENL | T1ENL | T0ENL | <b>U0RENL</b> | <b>U0TENL</b> | I2CENL | SPIENL | ADCENL |  |  |  |

| RESET   | 0     |       |       |               |               |        |        |        |  |  |  |

| R/W     |       | R/W   |       |               |               |        |        |        |  |  |  |

| Address |       |       |       | FC            | 2H            |        |        |        |  |  |  |

# Hex Address: FC3

#### Table 220. Interrupt Request 1 Register (IRQ1)

| Bit     | 7     | 6                                             | 5 | 4  | 3  | 2 | 1 | 0 |  |  |  |

|---------|-------|-----------------------------------------------|---|----|----|---|---|---|--|--|--|

| Field   | PAD7I | PAD7I PAD6I PAD5I PAD4I PAD3I PAD2I PAD1I PAD |   |    |    |   |   |   |  |  |  |

| RESET   | 0     |                                               |   |    |    |   |   |   |  |  |  |

| R/W     |       | R/W                                           |   |    |    |   |   |   |  |  |  |

| Address |       |                                               |   | FC | 3H |   |   |   |  |  |  |

## Hex Address: FC4

#### Table 221. IRQ1 Enable High Bit Register (IRQ1ENH)

| Bit     | 7       | 6       | 5       | 4       | 3       | 2       | 1       | 0       |  |  |  |

|---------|---------|---------|---------|---------|---------|---------|---------|---------|--|--|--|

| Field   | PAD7ENH | PAD6ENH | PAD5ENH | PAD4ENH | PAD3ENH | PAD2ENH | PAD1ENH | PAD0ENH |  |  |  |

| RESET   | 0       | 0       | 0       | 0       | 0       | 0       | 0       | 0       |  |  |  |

| R/W     |  |  |  |

| Address |         | FC4H    |         |         |         |         |         |         |  |  |  |

# Hex Address: FDF

#### Table 244. Port A–H Output Data Register (PxOUT)

| Bit     | 7     | 6                                              | 5 | 4 | 3 | 2 | 1 | 0 |  |  |  |

|---------|-------|------------------------------------------------|---|---|---|---|---|---|--|--|--|

| Field   | POUT7 | POUT7 POUT6 POUT5 POUT4 POUT3 POUT2 POUT1 POUT |   |   |   |   |   |   |  |  |  |

| RESET   | 0     |                                                |   |   |   |   |   |   |  |  |  |

| R/W     |       | R/W                                            |   |   |   |   |   |   |  |  |  |

| Address |       | FD3H, FD7H, FDBH, FDFH, FE3H, FE7H, FEBH, FEFH |   |   |   |   |   |   |  |  |  |

# Hex Address: FE0

#### Table 245. Port A–H GPIO Address Registers (PxADDR)

| Bit     | 7          | 6   | 5           | 4         | 3           | 2          | 1   | 0 |  |  |  |

|---------|------------|-----|-------------|-----------|-------------|------------|-----|---|--|--|--|

| Field   | PADDR[7:0] |     |             |           |             |            |     |   |  |  |  |

| RESET   | 00H        |     |             |           |             |            |     |   |  |  |  |

| R/W     |            | R/W |             |           |             |            |     |   |  |  |  |

| Address |            | FD0 | H, FD4H, FI | D8H, FDCH | , FE0H, FE4 | H, FE8H, F | ECH |   |  |  |  |

# Hex Address: FE1

## Table 246. Port A–H Control Registers (PxCTL)

| Bit     | 7    | 7 6 5 4 3 2 1 |             |            |           |            |     |  |  |  |

|---------|------|---------------|-------------|------------|-----------|------------|-----|--|--|--|

| Field   | PCTL |               |             |            |           |            |     |  |  |  |

| RESET   | 00H  |               |             |            |           |            |     |  |  |  |

| R/W     | R/W  |               |             |            |           |            |     |  |  |  |

| Address |      | FD1           | H, FD5H, Fl | D9H, FDDH, | FE1H, FE5 | H, FE9H, F | EDH |  |  |  |

## Hex Address: FE2

#### Table 247. Port A-H Input Data Registers (PxIN)

| Bit     | 7    | 6    | 5           | 4          | 3         | 2          | 1    | 0    |  |  |  |

|---------|------|------|-------------|------------|-----------|------------|------|------|--|--|--|

| Field   | PIN7 | PIN6 | PIN5        | PIN4       | PIN3      | PIN2       | PIN1 | PIN0 |  |  |  |

| RESET   | X    |      |             |            |           |            |      |      |  |  |  |

| R/W     |      | R    |             |            |           |            |      |      |  |  |  |

| Address |      | FD2  | H, FD6H, FD | DAH, FDEH, | FE2H, FE6 | H, FEAH, F | EEH  |      |  |  |  |

# Packaging

Zilog's F64xx Series of MCUs includes the Z8F1621, Z8F2421, Z8F3221, Z8F4821 and Z8F6421 devices, which are available in the following packages:

- 40-pin Pin Dual Inline Package (PDIP)

- 44-pin Low Profile Quad Flat Package (LQFP)

- 44-pin Plastic Lead Chip Carrier (PLCC)

Zilog's F64xx Series of MCUs also includes the Z8F1622, Z8F2422, Z8F3222, Z8F4822 and Z8F6422 devices, which are available in the following packages:

- 64-pin Low-Profile Quad Flat Package (LQFP)

- 68-pin Plastic Lead Chip Carrier (PLCC)

Lastly, Zilog's F64xx Series of MCUs includes the Z8F4823 and Z8F6423 devices, which are available in the following package:

• 80-pin Quad Flat Package (QFP)

Current diagrams for each of these packages are published in Zilog's <u>Packaging Product</u> <u>Specification (PS0072)</u>, which is available free for download from the Zilog website.

# **Customer Support**

To share comments, get your technical questions answered or report issues you may be experiencing with our products, please visit Zilog's Technical Support page at <a href="http://support.zilog.com">http://support.zilog.com</a>.

To learn more about this product, find additional documentation or to discover other facets about Zilog product offerings, please visit the Zilog Knowledge Base at <u>http://zilog.com/</u><u>kb</u> or consider participating in the Zilog Forum at <u>http://zilog.com/forum</u>.

This publication is subject to replacement by a later edition. To determine whether a later edition exists, please visit the Zilog website at <u>http://www.zilog.com</u>.