Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

#### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Details                    |                                                           |

|----------------------------|-----------------------------------------------------------|

| Product Status             | Active                                                    |

| Core Processor             | eZ8                                                       |

| Core Size                  | 8-Bit                                                     |

| Speed                      | 20MHz                                                     |

| Connectivity               | I <sup>2</sup> C, IrDA, SPI, UART/USART                   |

| Peripherals                | Brown-out Detect/Reset, DMA, POR, PWM, WDT                |

| Number of I/O              | 46                                                        |

| Program Memory Size        | 16KB (16K × 8)                                            |

| Program Memory Type        | FLASH                                                     |

| EEPROM Size                | -                                                         |

| RAM Size                   | 2K x 8                                                    |

| Voltage - Supply (Vcc/Vdd) | 3V ~ 3.6V                                                 |

| Data Converters            | A/D 12x10b                                                |

| Oscillator Type            | Internal                                                  |

| Operating Temperature      | 0°C ~ 70°C (TA)                                           |

| Mounting Type              | Surface Mount                                             |

| Package / Case             | 64-LQFP                                                   |

| Supplier Device Package    | -                                                         |

| Purchase URL               | https://www.e-xfl.com/product-detail/zilog/z8f1622ar020sg |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

#### **Warning:** DO NOT USE THIS PRODUCT IN LIFE SUPPORT SYSTEMS.

#### LIFE SUPPORT POLICY

ZILOG'S PRODUCTS ARE NOT AUTHORIZED FOR USE AS CRITICAL COMPONENTS IN LIFE SUPPORT DEVICES OR SYSTEMS WITHOUT THE EXPRESS PRIOR WRITTEN APPROVAL OF THE PRESIDENT AND GENERAL COUNSEL OF ZILOG CORPORATION.

#### As used herein

Life support devices or systems are devices which (a) are intended for surgical implant into the body, or (b) support or sustain life and whose failure to perform when properly used in accordance with instructions for use provided in the labeling can be reasonably expected to result in a significant injury to the user. A critical component is any component in a life support device or system whose failure to perform can be reasonably expected to cause the failure of the life support device or system or to affect its safety or effectiveness.

#### **Document Disclaimer**

©2013 Zilog, Inc. All rights reserved. Information in this publication concerning the devices, applications, or technology described is intended to suggest possible uses and may be superseded. ZILOG, INC. DOES NOT ASSUME LIABILITY FOR OR PROVIDE A REPRESENTATION OF ACCURACY OF THE INFORMATION, DEVICES, OR TECHNOLOGY DESCRIBED IN THIS DOCUMENT. ZILOG ALSO DOES NOT ASSUME LIABILITY FOR INTELLECTUAL PROPERTY INFRINGEMENT RELATED IN ANY MANNER TO USE OF INFORMATION, DEVICES, OR TECHNOLOGY DESCRIBED HEREIN OR OTHERWISE. The information contained within this document has been verified according to the general principles of electrical and mechanical engineering.

Z8, Z8 Encore!, Z8 Encore! XP and Z8 Encore! MC are trademarks or registered trademarks of Zilog, Inc. All other product or service names are the property of their respective owners.

| eZ8 CPU Instruction Set                                                                                  |

|----------------------------------------------------------------------------------------------------------|

| Assembly Language Programming Introduction                                                               |

| Assembly Language Syntax 226                                                                             |

| eZ8 CPU Instruction Notation                                                                             |

| Condition Codes 229                                                                                      |

| eZ8 CPU Instruction Classes                                                                              |

| eZ8 CPU Instruction Summary 234                                                                          |

| Flags Register    243                                                                                    |

| Op Code Maps                                                                                             |

| Appendix A. Register Tables                                                                              |

| General Purpose RAM                                                                                      |

| Timer 0                                                                                                  |

| Universal Asynchronous Receiver/Transmitter (UART)                                                       |

| Inter-Integrated Circuit (I <sup>2</sup> C)                                                              |

| Serial Peripheral Interface                                                                              |

| Analog-to-Digital Converter (ADC) 266                                                                    |

| Direct Memory Access (DMA) 266                                                                           |

| Interrupt Request (IRQ) 270                                                                              |

| General-Purpose Input/Output (GPIO) 274                                                                  |

| Watchdog Timer                                                                                           |

| Flash                                                                                                    |

| Packaging                                                                                                |

| Ordering Information                                                                                     |

| Part Number Suffix Designations                                                                          |

| Index                                                                                                    |

| Customer Support                                                                                         |

| Ordering Information       287         Part Number Suffix Designations       292         Index       293 |

#### Х

#### **System Reset**

During a system reset, the Z8 Encore! XP F64xx Series devices are held in Reset for 66 cycles of the Watchdog Timer oscillator followed by 16 cycles of the system clock. At the beginning of Reset, all GPIO pins are configured as inputs.

During Reset, the eZ8 CPU and on-chip peripherals are idle; however, the on-chip crystal oscillator and Watchdog Timer oscillator continue to run. The system clock begins operating following the Watchdog Timer oscillator cycle count. The eZ8 CPU and on-chip peripherals remain idle through the 16 cycles of the system clock.

Upon Reset, control registers within the Register File that have a defined Reset value are loaded with their reset values. Other control registers (including the Stack Pointer, Register Pointer, and Flags) and general-purpose RAM are undefined following Reset. The eZ8 CPU fetches the Reset vector at program memory addresses 0002H and 0003H and loads that value into the Program Counter. Program execution begins at the Reset vector address.

# **Reset Sources**

Table 9 lists the reset sources as a function of the operating mode. The text following provides more detailed information about the individual Reset sources. A Power-On Reset/ Voltage Brown-Out event always takes priority over all other possible reset sources to ensure a full system reset occurs.

| Operating Mode       | Reset Source                                             | Reset Type                                                          |  |  |

|----------------------|----------------------------------------------------------|---------------------------------------------------------------------|--|--|

| NORMAL or HALT modes | Power-On Reset/Voltage Brown-<br>Out                     | system reset                                                        |  |  |

|                      | Watchdog Timer time-out when configured for Reset        | system reset                                                        |  |  |

|                      | RESET pin assertion                                      | system reset                                                        |  |  |

|                      | On-Chip Debugger initiated Reset<br>(OCDCTL[0] set to 1) | system reset except the On-Chip Debugger is unaffected by the reset |  |  |

| STOP Mode            | Power-On Reset/Voltage Brown-<br>Out                     | system reset                                                        |  |  |

|                      | RESET pin assertion                                      | system reset                                                        |  |  |

|                      | DBG pin driven Low                                       | system reset                                                        |  |  |

#### Table 9. Reset Sources and Resulting Reset Type

### Watchdog Timer Reset

If the device is in normal or HALT Mode, the Watchdog Timer can initiate a system reset at time-out if the WDT\_RES option bit is set to 1. This capability is the default (unprogrammed) setting of the WDT\_RES option bit. The WDT status bit in the WDT Control Register is set to signify that the reset was initiated by the Watchdog Timer.

### **External Pin Reset**

The RESET pin has a Schmitt-triggered input, an internal pull-up, an analog filter and a digital filter to reject noise. Once the RESET pin is asserted for at least 4 system clock cycles, the devices progress through the system reset sequence. While the RESET input pin is asserted Low, the Z8 Encore! XP F64xx Series devices continue to be held in the Reset state. If the RESET pin is held Low beyond the system reset time-out, the devices exit the Reset state immediately following RESET pin deassertion. Following a system reset initiated by the external RESET pin, the EXT status bit in the Watchdog Timer Control (WDTCTL) Register is set to 1.

### **On-Chip Debugger Initiated Reset**

A Power-On Reset can be initiated using the On-Chip Debugger by setting the RST bit in the OCD Control Register. The On-Chip Debugger block is not reset but the rest of the chip goes through a normal system reset. The RST bit automatically clears during the system reset. Following the system reset the POR bit in the WDT Control Register is set.

# **Stop Mode Recovery**

STOP Mode is entered by the eZ8 executing a stop instruction. For detailed STOP Mode information, see the <u>Low-Power Modes</u> chapter on page 34. During Stop Mode Recovery, the devices are held in reset for 66 cycles of the Watchdog Timer oscillator followed by 16 cycles of the system clock. Stop Mode Recovery only affects the contents of the Watchdog Timer Control Register. Stop Mode Recovery does not affect any other values in the Register File, including the Stack Pointer, Register Pointer, Flags, peripheral control registers, and general-purpose RAM.

The eZ8 CPU fetches the Reset vector at program memory addresses 0002H and 0003H and loads that value into the Program Counter. Program execution begins at the Reset vector address. Following Stop Mode Recovery, the stop bit in the Watchdog Timer Control Register is set to 1. Table 10 lists the Stop Mode Recovery sources and resulting actions.

#### Port A–H Stop Mode Recovery Source Enable Subregisters

The Port A–H Stop Mode Recovery Source Enable Subregister, shown in Table 20, is accessed through the Port A–H Control Register by writing 05H to the Port A–H Address Register. Setting the bits in the Port A–H Stop Mode Recovery Source Enable subregisters to 1 configures the specified Port pins as a Stop Mode Recovery source. During STOP Mode, any logic transition on a Port pin enabled as a Stop Mode Recovery source initiates Stop Mode Recovery.

#### Table 20. Port A–H Stop Mode Recovery Source Enable Subregisters

| Bit                                                                                                             | 7         | 6      | 5      | 4      | 3      | 2      | 1      | 0      |  |

|-----------------------------------------------------------------------------------------------------------------|-----------|--------|--------|--------|--------|--------|--------|--------|--|

| Field                                                                                                           | PSMRE7    | PSMRE6 | PSMRE5 | PSMRE4 | PSMRE3 | PSMRE2 | PSMRE1 | PSMRE0 |  |

| RESET                                                                                                           | 0         |        |        |        |        |        |        |        |  |

| R/W                                                                                                             |           | R/W    |        |        |        |        |        |        |  |

| Address                                                                                                         | See note. |        |        |        |        |        |        |        |  |

| Note: If a 05H exists in the Port A–H Address Register, it is accessible through the Port A–H Control Register. |           |        |        |        |        |        |        |        |  |

|                                                                                                                 |           |        |        |        |        |        |        |        |  |

| Bit   | Description                                                                                                                                                                                                                                                                                                                 |

|-------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| [7:0] | Port Stop Mode Recovery Source Enabled                                                                                                                                                                                                                                                                                      |

| PSMRE | <ul> <li>0 = The port pin is not configured as a Stop Mode Recovery source. Transitions on this pin during STOP Mode do not initiate Stop Mode Recovery.</li> <li>1 = The port pin is configured as a Stop Mode Recovery source. Any logic transition on this pin during STOP Mode initiates Stop Mode Recovery.</li> </ul> |

Note: x indicates register bits in the range [7:0].

45

# Operation

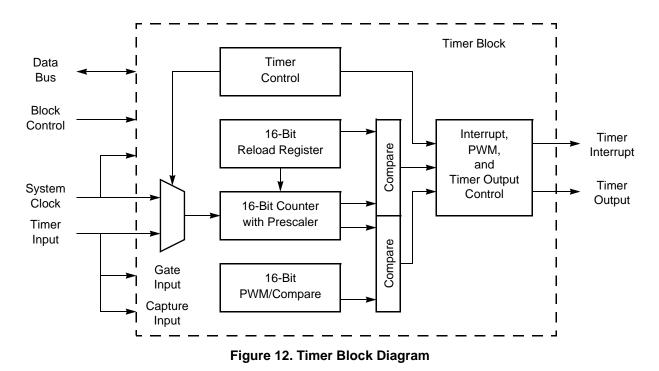

The timers are 16-bit up-counters. Minimum time-out delay is set by loading the value 0001H into the Timer Reload High and Low Byte registers and setting the prescale value to 1. Maximum time-out delay is set by loading the value 0000H into the Timer Reload High and Low Byte registers and setting the prescale value to 128. If the Timer reaches FFFFH, the timer rolls over to 0000H and continues counting.

### **Timer Operating Modes**

The timers can be configured to operate in the following modes:

#### **ONE-SHOT Mode**

In ONE-SHOT Mode, the timer counts up to the 16-bit reload value stored in the Timer Reload High and Low Byte registers. The timer input is the system clock. Upon reaching the reload value, the timer generates an interrupt and the count value in the Timer High and Low Byte registers is reset to 0001H. Then, the timer is automatically disabled and stops counting.

Also, if the timer output alternate function is enabled, the timer output pin changes state for one system clock cycle (from Low to High or from High to Low) upon timer reload. If

63

If TPOL is set to 0, the ratio of the PWM output High time to the total period is calculated using the following equation:

PWM Output High Time Ratio (%) =  $\frac{\text{Reload Value} - \text{PWM Value}}{\text{Reload Value}} \times 100$

If TPOL is set to 1, the ratio of the PWM output High time to the total period is calculated using the following equation:

PWM Output High Time Ratio (%) =  $\frac{\text{PWM Value}}{\text{Reload Value}} \times 100$

#### **CAPTURE Mode**

In CAPTURE Mode, the current timer count value is recorded when the appropriate external timer input transition occurs. The Capture count value is written to the Timer PWM High and Low Byte Registers. The timer input is the system clock. The TPOL bit in the Timer Control 1 Register determines if the Capture occurs on a rising edge or a falling edge of the timer input signal. When the capture event occurs, an interrupt is generated and the timer continues counting.

The timer continues counting up to the 16-bit reload value stored in the Timer Reload High and Low Byte registers. Upon reaching the reload value, the timer generates an interrupt and continues counting.

Observe the following procedure for configuring a timer for CAPTURE Mode and initiating the count:

- 1. Write to the Timer Control 1 Register to:

- Disable the timer

- Configure the timer for CAPTURE Mode

- Set the prescale value

- Set the Capture edge (rising or falling) for the timer input

- 2. Write to the Timer High and Low Byte registers to set the starting count value (typically 0001H).

- 3. Write to the Timer Reload High and Low Byte registers to set the reload value.

- 4. Clear the Timer PWM High and Low Byte registers to 0000H. This allows the software to determine if interrupts were generated by either a capture event or a reload. If the PWM High and Low Byte registers still contain 0000H after the interrupt, then the interrupt was generated by a reload.

- 5. If appropriate, enable the timer interrupt and set the timer interrupt priority by writing to the relevant interrupt registers.

## Timer 0–3 PWM High and Low Byte Registers

The Timer 0–3 PWM High and Low Byte (TxPWMH and TxPWML) registers, shown in Tables 43 and 44, are used for Pulse-Width Modulator (PWM) operations. These registers also store the capture values for the CAPTURE and CAPTURE/COMPARE modes.

#### Table 43. Timer 0–3 PWM High Byte Register (TxPWMH)

| Bit     | 7    | 6 | 5 | 4          | 3         | 2 | 1 | 0 |  |  |

|---------|------|---|---|------------|-----------|---|---|---|--|--|

| Field   | PWMH |   |   |            |           |   |   |   |  |  |

| RESET   | 0    |   |   |            |           |   |   |   |  |  |

| R/W     | R/W  |   |   |            |           |   |   |   |  |  |

| Address |      |   | F | 04H, F0CH, | F14H, F1C | Н |   |   |  |  |

#### Table 44. Timer 0–3 PWM Low Byte Register (TxPWML)

| Bit     | 7    | 6 | 5 | 4          | 3         | 2 | 1 | 0 |  |  |  |

|---------|------|---|---|------------|-----------|---|---|---|--|--|--|

| Field   | PWML |   |   |            |           |   |   |   |  |  |  |

| RESET   |      | 0 |   |            |           |   |   |   |  |  |  |

| R/W     | R/W  |   |   |            |           |   |   |   |  |  |  |

| Address |      |   | F | 05H, F0DH, | F15H, F1D | Η |   |   |  |  |  |

| Bit           | Description                                                                                                                                                                                                                                                                                                                                                                                       |

|---------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| [7:0]         | Pulse-Width Modulator High and Low Bytes                                                                                                                                                                                                                                                                                                                                                          |

| PWMH,<br>PWML | These two bytes, {PWMH[7:0], PWML[7:0]}, form a 16-bit value that is compared to the current 16-bit timer count. When a match occurs, the PWM output changes state. The PWM output value is set by the TPOL bit in the Timer Control 1 Register (TxCTL1) Register. The TxPWMH and TxPWML registers also store the 16-bit captured timer value when operating in CAPTURE or CAPTURE/COMPARE modes. |

#### Table 48. Watchdog Timer Control Register (WDTCTL)

| Bit         | 7                                                            | 6                                                                                                                                                                                                                                                                                                                                                                                                                                               | 5   | 4   | 3  | 2  | 1 | 0 |  |  |

|-------------|--------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|-----|----|----|---|---|--|--|

| Field       | POR                                                          | STOP                                                                                                                                                                                                                                                                                                                                                                                                                                            | WDT | EXT |    | SM |   |   |  |  |

| RESET       | S                                                            | See Table 49                                                                                                                                                                                                                                                                                                                                                                                                                                    | ).  |     |    | 0  |   |   |  |  |

| R/W         |                                                              |                                                                                                                                                                                                                                                                                                                                                                                                                                                 |     | ŀ   | २  |    |   |   |  |  |

| Address     |                                                              |                                                                                                                                                                                                                                                                                                                                                                                                                                                 |     | FF  | ОH |    |   |   |  |  |

| Bit         | Descriptio                                                   |                                                                                                                                                                                                                                                                                                                                                                                                                                                 |     |     |    |    |   |   |  |  |

| [7]<br>POR  | Power-On<br>If this bit is                                   | <b>Power-On Reset Indicator</b><br>If this bit is set to 1, a Power-On Reset event occurred. This bit is reset to 0 if a WDT time-out<br>for Stop Mode Recovery occurs. This bit is also reset to 0 when the register is read.                                                                                                                                                                                                                  |     |     |    |    |   |   |  |  |

| [6]<br>STOP | If this bit is<br>1, the Stop<br>bit is 0, the<br>Power-On F | <b>Stop Mode Recovery Indicator</b><br>If this bit is set to 1, a Stop Mode Recovery occurred. If the stop and WDT bits are both set to 1, the Stop Mode Recovery occurred due to a WDT time-out. If the stop bit is 1 and the WDT bit is 0, the Stop Mode Recovery was not caused by a WDT time-out. This bit is reset by a Power-On Reset or a WDT time-out that occurred while not in STOP Mode. Reading this register also resets this bit. |     |     |    |    |   |   |  |  |

| [5]<br>WDT  | If this bit is                                               | Watchdog Timer Time-Out Indicator<br>If this bit is set to 1, a WDT time-out occurred. A Power-On Reset resets this pin. A Stop Mode<br>Recovery from a change in an input pin also resets this bit. Reading this register resets this bit.                                                                                                                                                                                                     |     |     |    |    |   |   |  |  |

| [4]<br>EXT  | If this bit is or a Stop M                                   | External Reset Indicator<br>If this bit is set to 1, a Reset initiated by the external RESET pin occurred. A Power-On Reset<br>or a Stop Mode Recovery from a change in an input pin resets this bit. Reading this register<br>resets this bit.                                                                                                                                                                                                 |     |     |    |    |   |   |  |  |

| [3:1]       | Reserved<br>These bits a                                     | Reserved<br>These bits are reserved and must be programmed to 000.                                                                                                                                                                                                                                                                                                                                                                              |     |     |    |    |   |   |  |  |

| [0]<br>SM   | 0 = Watchd                                                   | <b>STOP Mode Configuration Indicator</b><br>0 = Watchdog Timer and its internal RC oscillator will continue to operate in STOP Mode.<br>1 = Watchdog Timer and its internal RC oscillator will be disabled in STOP Mode.                                                                                                                                                                                                                        |     |     |    |    |   |   |  |  |

| Bit           | Description (Continued)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

|---------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| [2]<br>BRGCTL | <ul> <li>Baud Rate Control This bit causes different UART behavior depending on whether the UART receiver is enabled (REN = 1 in the UART Control 0 Register). When the UART receiver is not enabled, this bit determines whether the Baud Rate Generator issues interrupts. 0 = Reads from the Baud Rate High and Low Byte registers return the BRG reload value 1 = The Baud Rate Generator generates a receive interrupt when it counts down to 0. Reads from the Baud Rate High and Low Byte registers return the current BRG count value. When the UART receiver is enabled, this bit allows reads from the Baud Rate Registers to return the BRG count value instead of the reload value. 0 = Reads from the Baud Rate High and Low Byte registers return the BRG reload value. 1 = Reads from the Baud Rate High and Low Byte registers return the BRG reload value. 1 = Reads from the Baud Rate High and Low Byte registers return the BRG reload value. 1 = Reads from the Baud Rate High and Low Byte registers return the DRG reload value. 1 = Reads from the Baud Rate High and Low Byte registers return the Current BRG count value. 1 = Reads from the Baud Rate High and Low Byte registers return the DRG reload value. 1 = Reads from the Baud Rate High and Low Byte registers return the Current BRG count value. 1 = Reads from the Baud Rate High and Low Byte registers return the Current BRG count value. Unlike the timers, there is no mechanism to latch the High Byte when the Low Byte is read.</li></ul> |

| [1]<br>RDAIRQ | <ul> <li>Receive Data Interrupt Enable</li> <li>0 = Received data and receiver errors generates an interrupt request to the Interrupt Controller.</li> <li>1 = Received data does not generate an interrupt request to the Interrupt Controller. Only receiver errors generate an interrupt request.</li> </ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

| [0]<br>IREN   | <ul> <li>Infrared Encoder/Decoder Enable</li> <li>0 = Infrared Encoder/Decoder is disabled. UART operates normally operation.</li> <li>1 = Infrared Encoder/Decoder is enabled. The UART transmits and receives data through the Infrared Encoder/Decoder.</li> </ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

104

#### Table 60. UART Baud Rate High Byte Register (UxBRH)

| Bit     | 7   | 6 | 5 | 4       | 3       | 2 | 1 | 0 |  |  |

|---------|-----|---|---|---------|---------|---|---|---|--|--|

| Field   | BRH |   |   |         |         |   |   |   |  |  |

| RESET   | 1   |   |   |         |         |   |   |   |  |  |

| R/W     | R/W |   |   |         |         |   |   |   |  |  |

| Address |     |   |   | F46H ar | nd F4EH |   |   |   |  |  |

#### Table 61. UART Baud Rate Low Byte Register (UxBRL)

| Bit7    | 7   | 6 | 5 | 4       | 3       | 2 | 1 | 0 |  |  |

|---------|-----|---|---|---------|---------|---|---|---|--|--|

| Field   | BRL |   |   |         |         |   |   |   |  |  |

| RESET   | 1   |   |   |         |         |   |   |   |  |  |

| R/W     | R/W |   |   |         |         |   |   |   |  |  |

| Address |     |   |   | F47H ar | nd F4FH |   |   |   |  |  |

For a given UART data rate, the integer baud rate divisor value is calculated using the following equation:

UART Baud Rate Divisor Value (BRG) = Round  $\left(\frac{\text{System Clock Frequency (Hz)}}{16 \times \text{UART Data Rate (bits/s)}}\right)$

The baud rate error relative to the appropriate baud rate is calculated using the following equation:

UART Baud Rate Error (%) =

$$100 \times \left(\frac{\text{Actual Data Rate} - \text{Desired Data Rate}}{\text{Desired Data Rate}}\right)$$

For reliable communication, the UART baud rate error must never exceed 5 percent. Table 62 lists data rate errors for popular baud rates and commonly used crystal oscillator frequencies.

| Bit        | Description (Continued)                                                                                                                                                                                                                                                                      |

|------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| [1]        | <b>Reserved</b><br>This bit is reserved and must be programmed to 0.                                                                                                                                                                                                                         |

| [0]<br>FWP | <ul> <li>Flash Write Protect (Flash version only)</li> <li>0 = Programming, Page Erase, and Mass Erase through User Code is disabled. Mass Erase is available through the On-Chip Debugger.</li> <li>1 = Programming, and Page Erase are enabled for all of Flash program memory.</li> </ul> |

# Flash Memory Address 0001H

| Table 100. Options Bits at Flash Memory Address 0001 |

|------------------------------------------------------|

|------------------------------------------------------|

| Bit       | 7           | 6                    | 5             | 4  | 3 | 2 | 1 | 0 |  |  |  |  |  |  |

|-----------|-------------|----------------------|---------------|----|---|---|---|---|--|--|--|--|--|--|

| Field     | Reserved    |                      |               |    |   |   |   |   |  |  |  |  |  |  |

| RESET     |             | U                    |               |    |   |   |   |   |  |  |  |  |  |  |

| R/W       |             |                      |               | R/ | W |   |   |   |  |  |  |  |  |  |

| Address   |             | Program Memory 0001H |               |    |   |   |   |   |  |  |  |  |  |  |

| Note: U = | Unchanged b | by Reset. R/W        | / = Read/Writ | e. |   |   |   |   |  |  |  |  |  |  |

# Bit Description

[7:0] Reserved

These option bits are reserved for future use and must always be 1. This setting is the default for unprogrammed (erased) Flash.

| Parameter                                                       | Minimum                                   | Maximum        | Units         | Notes        |

|-----------------------------------------------------------------|-------------------------------------------|----------------|---------------|--------------|

| 64-pin LQFP maximum ratings at -40°C to 70°C                    |                                           |                |               |              |

| Total power dissipation                                         |                                           | 1000           | mW            |              |

| Maximum current into $V_{DD}$ or out of $V_{SS}$                |                                           | 275            | mA            |              |

| 64-pin LQFP maximum ratings at 70°C to 125°C                    |                                           |                |               |              |

| Total power dissipation                                         |                                           | 540            | mW            |              |

| Maximum current into $V_{DD}$ or out of $V_{SS}$                |                                           | 150            | mA            |              |

| 44-pin PLCC maximum ratings at -40°C to 70°C                    |                                           |                |               |              |

| Total power dissipation                                         |                                           | 750            | mW            |              |

| Maximum current into $V_{DD}$ or out of $V_{SS}$                |                                           | 200            | mA            |              |

| 44-pin PLCC maximum ratings at 70°C to 125°C                    |                                           |                |               |              |

| Total power dissipation                                         |                                           | 295            | mW            |              |

| Maximum current into $V_{DD}$ or out of $V_{SS}$                |                                           | 83             | mA            |              |

| 44-pin LQFP maximum ratings at –40°C to 70°C                    |                                           |                |               |              |

| Total power dissipation                                         |                                           | 750            | mW            |              |

| Maximum current into $V_{DD}$ or out of $V_{SS}$                |                                           | 200            | mA            |              |

| 44-pin LQFP maximum ratings at 70°C to 125°C                    |                                           |                |               |              |

| Total power dissipation                                         |                                           | 360            | mW            |              |

| Maximum current into $V_{DD}$ or out of $V_{SS}$                |                                           | 100            | mA            |              |

| Note: This voltage applies to all pins, with the exception of V | / <sub>DD</sub> , AV <sub>DD</sub> , pins | supporting ana | log input (po | orts B and I |

#### Table 106. Absolute Maximum Ratings (Continued)

Note: This voltage applies to all pins, with the exception of V<sub>DD</sub>, AV<sub>DD</sub>, pins supporting analog input (ports B and H), RESET, and where noted otherwise.

#### 216

# **AC Characteristics**

This section provides AC characteristics and timing data which assumes a standard load of 50pF on all outputs. Table 114 lists the Z8 Encore! XP F64xx Series AC characteristics and timing.

|                     |                                    |                 | 0V–3.6V<br>C to 125°C |       |                                                                                                            |  |

|---------------------|------------------------------------|-----------------|-----------------------|-------|------------------------------------------------------------------------------------------------------------|--|

| Symbol              | Parameter                          | Minimum Maximum |                       | Units | Conditions                                                                                                 |  |

| F <sub>SYSCLK</sub> | System Clock Frequency             | -               | 20.0                  | MHz   | Read-only from Flash memory.                                                                               |  |

|                     |                                    | 0.032768        | 20.0                  | MHz   | Program or erasure of Flash memory.                                                                        |  |

| F <sub>XTAL</sub>   | Crystal Oscillator Frequency       | 0.032768        | 20.0                  | MHz   | System clock frequencies<br>below the crystal oscillator mini-<br>mum require an external clock<br>driver. |  |

| T <sub>XIN</sub>    | Crystal Oscillator Clock<br>Period | 50              | -                     | ns    | T <sub>CLK</sub> = 1/F <sub>SYSCLK</sub>                                                                   |  |

| T <sub>XINH</sub>   | System Clock High Time             | 20              |                       | ns    |                                                                                                            |  |

| T <sub>XINL</sub>   | System Clock Low Time              | 20              |                       | ns    |                                                                                                            |  |

| T <sub>XINR</sub>   | System Clock Rise Time             | -               | 3                     | ns    | $T_{CLK}$ = 50 ns. Slower rise times<br>can be tolerated with longer<br>clock periods.                     |  |

| T <sub>XINF</sub>   | System Clock Fall Time             | -               | 3                     | ns    | $T_{CLK}$ = 50 ns. Slower fall times<br>can be tolerated with longer<br>clock periods.                     |  |

| Table 114. / | AC Character | istics |

|--------------|--------------|--------|

|--------------|--------------|--------|

# **Flags Register**

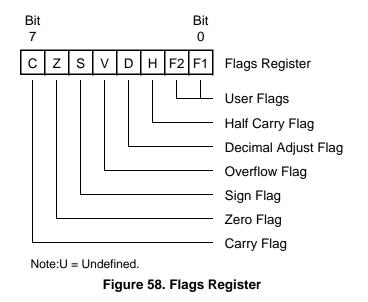

The Flags Register contains the status information regarding the most recent arithmetic, logical, bit manipulation or rotate and shift operation. The Flags Register contains six bits of status information that are set or cleared by CPU operations. Four of the bits (C, V, Z and S) can be tested for use with conditional jump instructions. Two flags, H and D, cannot be tested and are used for Binary-Coded Decimal (BCD) arithmetic.

The two remaining bits, user flags F1 and F2, are available as general-purpose status bits. User flags are unaffected by arithmetic operations and must be set or cleared by instructions. The user flags cannot be used with conditional jumps. They are undefined at initial power-up and are unaffected by Reset. Figure 58 displays the flags and their bit positions in the Flags Register.

Interrupts, the software trap (TRAP) instruction, and illegal instruction traps all write the value of the Flags Register to the stack. Executing an interrupt return (IRET) instruction restores the value saved on the stack into the Flags Register.

| 245 |

|-----|

|-----|

| Abbreviation | Description                    | Abbreviation                                      | Description           |

|--------------|--------------------------------|---------------------------------------------------|-----------------------|

| IM           | Immediate data value           | r2, R2, Ir2, Irr2,<br>IR2, rr2, RR2,<br>IRR2, ER2 | Source address        |

| Ir           | Indirect working register      | RA                                                | Relative              |

| IR           | Indirect register              | rr                                                | Working register pair |

| Irr          | Indirect working register pair | RR                                                | Register pair         |

#### Table 137. Op Code Map Abbreviations (Continued)

### Z8 Encore! XP<sup>®</sup> F64xx Series Product Specification

|   |                         |                          |                              |                                |                            |                               | LC                            | ower Nil                       | oble (He                      | X)                             |                            |                          |                           |                           |                  |                          |

|---|-------------------------|--------------------------|------------------------------|--------------------------------|----------------------------|-------------------------------|-------------------------------|--------------------------------|-------------------------------|--------------------------------|----------------------------|--------------------------|---------------------------|---------------------------|------------------|--------------------------|

| - | 0                       | 1                        | 2                            | 3                              | 4                          | 5                             | 6                             | 7                              | 8                             | 9                              | Α                          | В                        | С                         | D                         | Е                | F                        |

| 0 | 1.2<br>BRK              | 2.2<br>SRP<br>IM         | 2.3<br>ADD<br>r1,r2          | 2.4<br>ADD<br>r1,lr2           | 3.3<br><b>ADD</b><br>R2,R1 | 3.4<br>ADD<br>IR2,R1          | 3.3<br><b>ADD</b><br>R1,IM    | 3.4<br><b>ADD</b><br>IR1,IM    | 4.3<br>ADDX<br>ER2,ER1        | 4.3<br>ADDX<br>IM,ER1          | 2.3<br><b>DJNZ</b><br>r1,X | 2.2<br><b>JR</b><br>cc,X | 2.2<br><b>LD</b><br>r1,IM | 3.2<br><b>JP</b><br>cc,DA | 1.2<br>INC<br>r1 | 1.2<br>NOP               |

| 1 | 2.2<br><b>RLC</b><br>R1 | 2.3<br>RLC<br>IR1        | 2.3<br>ADC<br>r1,r2          | 2.4<br>ADC<br>r1,lr2           | 3.3<br>ADC<br>R2,R1        | 3.4<br>ADC<br>IR2,R1          | 3.3<br>ADC<br>R1,IM           | 3.4<br>ADC<br>IR1,IM           | 4.3<br>ADCX<br>ER2,ER1        | 4.3                            |                            |                          |                           |                           |                  | See 2nd<br>Opcode<br>Map |

| 2 | 2.2<br>INC<br>R1        | 2.3<br>INC<br>IR1        | 2.3<br>SUB<br>r1,r2          | 2.4<br>SUB<br>r1,lr2           | 3.3<br>SUB<br>R2,R1        | 3.4<br>SUB<br>IR2,R1          | 3.3<br>SUB<br>R1,IM           | 3.4<br>SUB<br>IR1,IM           | 4.3<br><b>SUBX</b><br>ER2,ER1 | 4.3<br><b>SUBX</b><br>IM,ER1   |                            |                          |                           |                           |                  | 1,2<br>ATM               |

| 3 | 2.2<br><b>DEC</b><br>R1 | 2.3<br><b>DEC</b><br>IR1 | 2.3<br>SBC<br>r1,r2          | 2.4<br>SBC<br>r1,lr2           | 3.3<br><b>SBC</b><br>R2,R1 | 3.4<br>SBC<br>IR2,R1          | 3.3<br><b>SBC</b><br>R1,IM    | 3.4<br>SBC<br>IR1,IM           | 4.3<br><b>SBCX</b><br>ER2,ER1 | 4.3<br><b>SBCX</b><br>IM,ER1   |                            |                          |                           |                           |                  |                          |

| 4 | 2.2<br><b>DA</b><br>R1  | 2.3<br><b>DA</b><br>IR1  | 2.3<br>OR<br>r1,r2           | 2.4<br>OR<br>r1,lr2            | 3.3<br><b>OR</b><br>R2,R1  | 3.4<br><b>OR</b><br>IR2,R1    | 3.3<br><b>OR</b><br>R1,IM     | 3.4<br><b>OR</b><br>IR1,IM     | 4.3<br><b>ORX</b><br>ER2,ER1  | 4.3<br><b>ORX</b><br>IM,ER1    |                            |                          |                           |                           |                  |                          |

| 5 | 2.2<br><b>POP</b><br>R1 | 2.3<br><b>POP</b><br>IR1 | 2.3<br>AND<br>r1,r2          | 2.4<br>AND<br>r1,lr2           | 3.3<br><b>AND</b><br>R2,R1 | 3.4<br>AND<br>IR2,R1          | 3.3<br><b>AND</b><br>R1,IM    | 3.4<br><b>AND</b><br>IR1,IM    | 4.3<br>ANDX<br>ER2,ER1        | 4.3<br>ANDX<br>IM,ER1          |                            |                          |                           |                           |                  | 1.2<br>WDT               |

| 6 | 2.2<br>COM<br>R1        | 2.3<br>COM<br>IR1        | 2.3<br>TCM<br>r1,r2          | 2.4<br>TCM<br>r1,lr2           | 3.3<br>TCM<br>R2,R1        | 3.4<br>TCM<br>IR2,R1          | 3.3<br><b>TCM</b><br>R1,IM    | 3.4<br><b>TCM</b><br>IR1,IM    | 4.3<br><b>TCMX</b><br>ER2,ER1 | 4.3<br><b>TCMX</b><br>IM,ER1   |                            |                          |                           |                           |                  | 1.2<br>STOP              |

| 7 | 2.2<br>PUSH<br>R2       | 2.3<br>PUSH<br>IR2       | 2.3<br>TM<br>r1,r2           | 2.4<br>TM<br>r1,lr2            | 3.3<br><b>TM</b><br>R2,R1  | 3.4<br>TM<br>IR2,R1           | 3.3<br>TM<br>R1,IM            | 3.4<br><b>TM</b><br>IR1,IM     | 4.3<br><b>TMX</b><br>ER2,ER1  | 4.3<br><b>TMX</b><br>IM,ER1    |                            |                          |                           |                           |                  | 1.2<br>HALT              |

| 8 | 2.5<br>DECW<br>RR1      | 2.6<br>DECW<br>IRR1      | 2.5<br>LDE<br>r1,lrr2        | 2.9<br>LDEI<br>Ir1,Irr2        | 3.2<br>LDX<br>r1,ER2       | 3.3<br>LDX<br>Ir1,ER2         | 3.4<br>LDX<br>IRR2,R1         | 3.5<br>LDX<br>IRR2,IR1         | 3.4<br>LDX<br>r1,rr2,X        | 3.4<br>LDX<br>rr1,r2,X         |                            |                          |                           |                           |                  | 1.2<br><b>DI</b>         |

| 9 | 2.2<br><b>RL</b><br>R1  | 2.3<br><b>RL</b><br>IR1  | 2.5<br>LDE<br>r2,Irr1        | 2.9<br><b>LDEI</b><br>Ir2,Irr1 | 3.2<br>LDX<br>r2,ER1       | 3.3<br>LDX<br>Ir2,ER1         | 3.4<br><b>LDX</b><br>R2,IRR1  | 3.5<br><b>LDX</b><br>IR2,IRR1  | 3.3<br><b>LEA</b><br>r1,r2,X  | 3.5<br><b>LEA</b><br>rr1,rr2,X |                            |                          |                           |                           |                  | 1.2<br>El                |

| А | 2.5<br>INCW<br>RR1      | 2.6<br>INCW<br>IRR1      | 2.3<br><b>CP</b><br>r1,r2    | 2.4<br><b>CP</b><br>r1,lr2     | 3.3<br><b>CP</b><br>R2,R1  | 3.4<br><b>CP</b><br>IR2,R1    | 3.3<br><b>CP</b><br>R1,IM     | 3.4<br><b>CP</b><br>IR1,IM     | 4.3<br><b>CPX</b><br>ER2,ER1  | 4.3<br><b>CPX</b><br>IM,ER1    |                            |                          |                           |                           |                  | 1.4<br>RET               |

| В | 2.2<br>CLR<br>R1        | 2.3<br>CLR<br>IR1        | 2.3<br><b>XOR</b><br>r1,r2   | 2.4<br><b>XOR</b><br>r1,lr2    | 3.3<br><b>XOR</b><br>R2,R1 | 3.4<br><b>XOR</b><br>IR2,R1   | 3.3<br><b>XOR</b><br>R1,IM    | 3.4<br><b>XOR</b><br>IR1,IM    | 4.3<br><b>XORX</b><br>ER2,ER1 | 4.3<br><b>XORX</b><br>IM,ER1   |                            |                          |                           |                           |                  | 1.5<br>IRET              |

| С | 2.2<br><b>RRC</b><br>R1 | 2.3<br><b>RRC</b><br>IR1 | 2.5<br><b>LDC</b><br>r1,lrr2 | 2.9<br><b>LDCI</b><br>Ir1,Irr2 | 2.3<br><b>JP</b><br>IRR1   | 2.9<br><b>LDC</b><br>lr1,lrr2 |                               | 3.4<br><b>LD</b><br>r1,r2,X    | 3.2<br>PUSHX<br>ER2           |                                |                            |                          |                           |                           |                  | 1.2<br>RCF               |

| D | 2.2<br><b>SRA</b><br>R1 | 2.3<br><b>SRA</b><br>IR1 | 2.5<br><b>LDC</b><br>r2,Irr1 | 2.9<br><b>LDCI</b><br>lr2,lrr1 | 2.6<br>CALL<br>IRR1        | 2.2<br><b>BSWAP</b><br>R1     | 3.3<br>CALL<br>DA             | 3.4<br><b>LD</b><br>r2,r1,X    | 3.2<br><b>POPX</b><br>ER1     |                                |                            |                          |                           |                           |                  | 1.2<br>SCF               |

| Е | 2.2<br><b>RR</b><br>R1  | 2.3<br><b>RR</b><br>IR1  | 2.2<br><b>BIT</b><br>p,b,r1  | 2.3<br><b>LD</b><br>r1,lr2     | 3.2<br><b>LD</b><br>R2,R1  | 3.3<br><b>LD</b><br>IR2,R1    | 3.2<br><b>LD</b><br>R1,IM     | 3.3<br><b>LD</b><br>IR1,IM     | 4.2<br><b>LDX</b><br>ER2,ER1  | 4.2<br><b>LDX</b><br>IM,ER1    |                            |                          |                           |                           |                  | 1.2<br>CCF               |

| F | 2.2<br>SWAP<br>R1       | 2.3<br>SWAP<br>IR1       | 2.6<br><b>TRAP</b><br>Vector | 2.3<br>LD<br>lr1,r2            | 2.8<br><b>MULT</b><br>RR1  | 3.3<br><b>LD</b><br>R2,IR1    | 3.3<br><b>BTJ</b><br>p,b,r1,X | 3.4<br><b>BTJ</b><br>p,b,lr1,X |                               |                                | ¥                          | ¥                        | ┥                         | ↓                         | •                |                          |

Lower Nibble (Hex)

Figure 60. First Op Code Map

Upper Nibble (Hex)

246

### Hex Address: FBE

#### Table 215. DMA\_ADC Control Register (DMAACTL)

| Bit     | 7    | 6     | 5                  | 4  | 3  | 2 | 1 | 0 |  |  |  |  |

|---------|------|-------|--------------------|----|----|---|---|---|--|--|--|--|

| Field   | DAEN | IRQEN | EN Reserved ADC_IN |    |    |   |   |   |  |  |  |  |

| RESET   |      | 0     |                    |    |    |   |   |   |  |  |  |  |

| R/W     |      | R/W   |                    |    |    |   |   |   |  |  |  |  |

| Address |      |       |                    | FB | EH |   |   |   |  |  |  |  |

### Hex Address: FBF

#### Table 216. DMA\_ADC Status Register (DMAA\_STAT)

| Bit     | 7 | 6                                 | 5 | 4  | 3  | 2 | 1 | 0 |  |  |  |  |  |  |

|---------|---|-----------------------------------|---|----|----|---|---|---|--|--|--|--|--|--|

| Field   |   | CADC[3:0] Reserved IRQA IRQ1 IRQ0 |   |    |    |   |   |   |  |  |  |  |  |  |

| RESET   |   | 0                                 |   |    |    |   |   |   |  |  |  |  |  |  |

| R/W     |   | R                                 |   |    |    |   |   |   |  |  |  |  |  |  |

| Address |   |                                   |   | FB | FH |   |   |   |  |  |  |  |  |  |

# Interrupt Request (IRQ)

For more information about these IRQ Control registers, see the <u>Interrupt Control Register</u> <u>Definitions</u> section on page 51.

### Hex Address: FC0

#### Table 217. Interrupt Request 0 Register (IRQ0)

| Bit     | 7   | 6   | 5   | 4            | 3     | 2    | 1    | 0    |  |  |  |  |  |

|---------|-----|-----|-----|--------------|-------|------|------|------|--|--|--|--|--|

| Field   | T2I | T1I | TOI | <b>U0RXI</b> | U0TXI | I2CI | SPII | ADCI |  |  |  |  |  |

| RESET   |     | 0   |     |              |       |      |      |      |  |  |  |  |  |

| R/W     |     | R/W |     |              |       |      |      |      |  |  |  |  |  |

| Address |     |     |     | FC           | 0H    |      |      |      |  |  |  |  |  |

#### Hex Address: FEF

#### Table 260. Port A–H Output Data Register (PxOUT)

| Bit     | 7     | 6                                              | 5     | 4     | 3     | 2     | 1     | 0     |  |

|---------|-------|------------------------------------------------|-------|-------|-------|-------|-------|-------|--|

| Field   | POUT7 | POUT6                                          | POUT5 | POUT4 | POUT3 | POUT2 | POUT1 | POUT0 |  |

| RESET   | 0     |                                                |       |       |       |       |       |       |  |

| R/W     | R/W   |                                                |       |       |       |       |       |       |  |

| Address |       | FD3H, FD7H, FDBH, FDFH, FE3H, FE7H, FEBH, FEFH |       |       |       |       |       |       |  |

# Watchdog Timer

For more information about these Watchdog Timer Control registers, see the <u>Watchdog</u> <u>Timer Control Register Definitions</u> section on page 83.

#### Hex Address: FF0

#### Table 261. Watchdog Timer Control Register (WDTCTL)

| Bit     | 7                                         | 6    | 5   | 4   | 3 | 2  | 1 | 0 |  |  |

|---------|-------------------------------------------|------|-----|-----|---|----|---|---|--|--|

| Field   | POR                                       | STOP | WDT | EXT |   | SM |   |   |  |  |

| RESET   | See <u>Table 48</u> on page 84.         0 |      |     |     |   |    |   |   |  |  |

| R/W     | R                                         |      |     |     |   |    |   |   |  |  |

| Address |                                           | FF0H |     |     |   |    |   |   |  |  |

#### Hex Address: FF1

#### Table 262. Watchdog Timer Reload Upper Byte Register (WDTU)

| Bit                                                                                             | 7    | 6    | 5 | 4 | 3 | 2 | 1 | 0 |  |

|-------------------------------------------------------------------------------------------------|------|------|---|---|---|---|---|---|--|

| Field                                                                                           |      | WDTU |   |   |   |   |   |   |  |

| RESET                                                                                           |      | 1    |   |   |   |   |   |   |  |

| R/W                                                                                             |      | R/W* |   |   |   |   |   |   |  |

| Address                                                                                         | FF1H |      |   |   |   |   |   |   |  |

| Note: *R/W = Read returns the current WDT count value; write sets the appropriate reload value. |      |      |   |   |   |   |   |   |  |

# Flash

For more information about these Flash Control registers, see the <u>Flash Control Register</u> <u>Definitions</u> section on page 175.

#### Hex Address: FF8

#### Table 265. Flash Control Register (FCTL)

| Bit     | 7    | 6    | 5 | 4 | 3 | 2 | 1 | 0 |  |  |

|---------|------|------|---|---|---|---|---|---|--|--|

| Field   | FCMD |      |   |   |   |   |   |   |  |  |

| RESET   |      | 0    |   |   |   |   |   |   |  |  |

| R/W     |      | W    |   |   |   |   |   |   |  |  |

| Address |      | FF8H |   |   |   |   |   |   |  |  |

#### Table 266. Flash Status Register (FSTAT)

| Bit     | 7              | 6 | 5 | 4 | 3 | 2 | 1 | 0 |  |

|---------|----------------|---|---|---|---|---|---|---|--|

| Field   | Reserved FSTAT |   |   |   |   |   |   |   |  |

| RESET   |                | 0 |   |   |   |   |   |   |  |

| R/W     |                | R |   |   |   |   |   |   |  |

| Address | FF8H           |   |   |   |   |   |   |   |  |

#### Hex Address: FF9

#### Table 267. Page Select Register (FPS)

| Bit     | 7       | 6            | 5 | 4 | 3 | 2 | 1 | 0 |  |  |

|---------|---------|--------------|---|---|---|---|---|---|--|--|

| Field   | INFO_EN | INFO_EN PAGE |   |   |   |   |   |   |  |  |

| RESET   |         | 0            |   |   |   |   |   |   |  |  |

| R/W     |         | R/W          |   |   |   |   |   |   |  |  |

| Address |         | FF9H         |   |   |   |   |   |   |  |  |