#### Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

#### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

| Details                    |                                                           |

|----------------------------|-----------------------------------------------------------|

| Product Status             | Obsolete                                                  |

| Core Processor             | eZ8                                                       |

| Core Size                  | 8-Bit                                                     |

| Speed                      | 20MHz                                                     |

| Connectivity               | I <sup>2</sup> C, IrDA, SPI, UART/USART                   |

| Peripherals                | Brown-out Detect/Reset, DMA, POR, PWM, WDT                |

| Number of I/O              | 46                                                        |

| Program Memory Size        | 16KB (16K x 8)                                            |

| Program Memory Type        | FLASH                                                     |

| EEPROM Size                |                                                           |

| RAM Size                   | 2K x 8                                                    |

| Voltage - Supply (Vcc/Vdd) | 3V ~ 3.6V                                                 |

| Data Converters            | A/D 12x10b                                                |

| Oscillator Type            | Internal                                                  |

| Operating Temperature      | -40°C ~ 105°C (TA)                                        |

| Mounting Type              | Surface Mount                                             |

| Package / Case             | 68-LCC (J-Lead)                                           |

| Supplier Device Package    | -                                                         |

| Purchase URL               | https://www.e-xfl.com/product-detail/zilog/z8f1622vs020eg |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

## Z8 Encore! XP<sup>®</sup> F64xx Series Product Specification

| Table 177. | UART Baud Rate High Byte Register (UxBRH)                | 258 |

|------------|----------------------------------------------------------|-----|

| Table 178. | UART Baud Rate Low Byte Register (UxBRL)                 | 259 |

| Table 179. | UART Transmit Data Register (UxTXD)                      | 259 |

| Table 180. | UART Receive Data Register (UxRXD)                       | 259 |

| Table 181. | UART Status 0 Register (UxSTAT0)                         | 259 |

| Table 182. | UART Control 0 Register (UxCTL0)                         | 260 |

| Table 183. | UART Control 1 Register (UxCTL1)                         | 260 |

| Table 184. | UART Status 1 Register (UxSTAT1)                         | 260 |

| Table 185. | UART Address Compare Register (UxADDR)                   | 260 |

| Table 186. | UART Baud Rate High Byte Register (UxBRH)                | 261 |

| Table 187. | UART Baud Rate Low Byte Register (UxBRL)                 | 261 |

| Table 188. | I <sup>2</sup> C Data Register (I2CDATA)                 | 261 |

| Table 189. | I <sup>2</sup> C Status Register (I2CSTAT)               | 262 |

| Table 190. | I <sup>2</sup> C Control Register (I2CCTL)               | 262 |

| Table 191. | I <sup>2</sup> C Baud Rate High Byte Register (I2CBRH)   | 262 |

| Table 192. | I <sup>2</sup> C Baud Rate Low Byte Register (I2CBRL)    | 262 |

| Table 193. | I <sup>2</sup> C Diagnostic State Register (I2CDST)      | 263 |

| Table 194. | I <sup>2</sup> C Diagnostic Control Register (I2CDIAG)   | 263 |

| Table 195. | SPI Data Register (SPIDATA)                              | 263 |

| Table 196. | SPI Control Register (SPICTL)                            | 264 |

| Table 197. | SPI Status Register (SPISTAT)                            | 264 |

| Table 198. | SPI Mode Register (SPIMODE)                              | 264 |

| Table 199. | SPI Diagnostic State Register (SPIDST)                   | 265 |

| Table 200. | SPI Baud Rate High Byte Register (SPIBRH)                | 265 |

| Table 201. | SPI Baud Rate Low Byte Register (SPIBRL)                 | 265 |

| Table 202. | ADC Data High Byte Register (ADCD_H)                     | 266 |

| Table 203. | ADC Data Low Bits Register (ADCD_L)                      | 266 |

| Table 204. | DMAx Control Register (DMAxCTL)                          | 267 |

| Table 205. | DMAx I/O Address Register (DMAxIO)                       | 267 |

| Table 206. | DMAx Address High Nibble Register (DMAxH)                | 267 |

| Table 207. | DMAx Start/Current Address Low Byte Register (DMAxSTART) | 267 |

| Table 208. | DMAx End Address Low Byte Register (DMAxEND)             | 268 |

| Table 209. | DMAx Control Register (DMAxCTL)                          | 268 |

|            | DMAx I/O Address Register (DMAxIO)                       |     |

|            | DMAx Address High Nibble Register (DMAxH)                |     |

|            | DMAx Start/Current Address Low Byte Register (DMAxSTART) |     |

|            | · · · · · · · · · · · · · · · · · · ·                    |     |

## I<sup>2</sup>C

The I<sup>2</sup>C controller makes the Z8 Encore! XP F64xx Series compatible with the I<sup>2</sup>C protocol. The I<sup>2</sup>C controller consists of two bidirectional bus lines, a serial data (SDA) line and a serial clock (SCL) line.

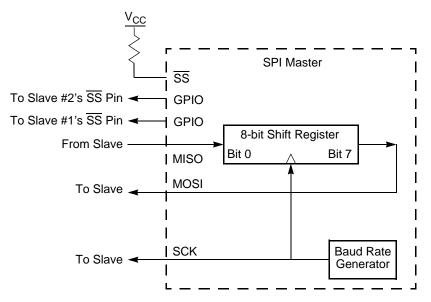

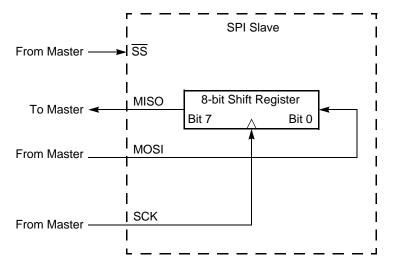

## Serial Peripheral Interface

The serial peripheral interface allows the Z8 Encore! XP F64xx Series to exchange data between other peripheral devices such as EEPROMs, A/D converters and ISDN devices. The SPI is a full-duplex, synchronous, character-oriented channel that supports a four-wire interface.

### Timers

Up to four 16-bit reloadable timers can be used for timing/counting events or for motor control operations. These timers provide a 16-bit programmable reload counter and operate in ONE-SHOT, CONTINUOUS, GATED, CAPTURE, COMPARE, CAPTURE AND COMPARE and PWM modes. Only 3 timers (Timer 0–2) are available in the 44-pin package.

## Interrupt Controller

The Z8 Encore! XP F64xx Series products support up to 24 interrupts. These interrupts consist of 12 internal and 12 GPIO pins. The interrupts have 3 levels of programmable interrupt priority.

## **Reset Controller**

The Z8 Encore! XP F64xx Series can be reset using the **RESET** pin, Power-On Reset, Watchdog Timer, STOP Mode exit, or Voltage Brown-Out (**VBO**) warning signal.

## **On-Chip Debugger**

The Z8 Encore! XP F64xx Series features an integrated On-Chip Debugger. The OCD provides a rich set of debugging capabilities, such as reading and writing registers, programming the Flash, setting breakpoints and executing code. A single-pin interface provides communication to the OCD.

## **Signal Descriptions**

Table 3 lists the Z8 Encore! XP signals. To determine the available signals for a specific package style, see the <u>Pin Configurations</u> section on page 8.

| Signal<br>Mnemonic         | I/O        | Description                                                                                                                                                                                                                                                                                                   |

|----------------------------|------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| General-Pur                | pose I/O P | Ports A–H                                                                                                                                                                                                                                                                                                     |

| PA[7:0]                    | I/O        | Port A[7:0]. These pins are used for general-purpose I/O and support 5V-tolerant inputs.                                                                                                                                                                                                                      |

| PB[7:0]                    | I/O        | Port B[7:0]. These pins are used for general-purpose I/O.                                                                                                                                                                                                                                                     |

| PC[7:0]                    | I/O        | Port C[7:0]. These pins are used for general-purpose I/O. These pins are used for general-purpose I/O and support 5V-tolerant inputs                                                                                                                                                                          |

| PD[7:0]                    | I/O        | Port D[7:0]. These pins are used for general-purpose I/O. These pins are used for general-purpose I/O and support 5V-tolerant inputs                                                                                                                                                                          |

| PE[7:0]                    | I/O        | Port E[7:0]. These pins are used for general-purpose I/O. These pins are used for general-purpose I/O and support 5V-tolerant inputs.                                                                                                                                                                         |

| PF[7:0]                    | I/O        | Port F[7:0]. These pins are used for general-purpose I/O. These pins are used for general-purpose I/O and support 5V-tolerant inputs.                                                                                                                                                                         |

| PG[7:0]                    | I/O        | Port G[7:0]. These pins are used for general-purpose I/O. These pins are used for general-purpose I/O and support 5V-tolerant inputs.                                                                                                                                                                         |

| PH[3:0]                    | I/O        | Port H[3:0]. These pins are used for general-purpose I/O.                                                                                                                                                                                                                                                     |

| I <sup>2</sup> C Controlle | er         |                                                                                                                                                                                                                                                                                                               |

| SCL                        | 0          | Serial Clock. This is the output clock for the I <sup>2</sup> C. This pin is multiplexed with a general-purpose I/O pin. When the general-purpose I/O pin is configured for alternate function to enable the SCL function, this pin is open-drain.                                                            |

| SDA                        | I/O        | Serial Data. This open-drain pin transfers data between the I <sup>2</sup> C and a slave.<br>This pin is multiplexed with a general-purpose I/O pin. When the general-pur-<br>pose I/O pin is configured for alternate function to enable the SDA function,<br>this pin is open-drain.                        |

| SPI Controlle              | er         |                                                                                                                                                                                                                                                                                                               |

| SS                         | I/O        | Slave Select. This signal can be an output or an input. If the Z8 Encore! XP F64xx Series is the SPI master, this pin may be configured as the Slave Select output. If the Z8 Encore! XP F64xx Series is the SPI slave, this pin is the input slave select. It is multiplexed with a general-purpose I/O pin. |

| SCK                        | I/O        | SPI Serial Clock. The SPI master supplies this pin. If the Z8 Encore! XP F64xx<br>Series is the SPI master, this pin is an output. If the Z8 Encore! XP F64xx<br>Series is the SPI slave, this pin is an input. It is multiplexed with a general-pur-<br>pose I/O pin.                                        |

### **Table 3. Signal Descriptions**

| Signal<br>Mnemonic                  | I/O        | Description                                                                                                                                                                                                                                                                                                     |  |  |  |  |  |

|-------------------------------------|------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|--|

| SPI Controlle                       | er (contin | ued)                                                                                                                                                                                                                                                                                                            |  |  |  |  |  |

| MOSI                                | I/O        | Master-Out/Slave-In. This signal is the data output from the SPI master device<br>and the data input to the SPI slave device. It is multiplexed with a general-pur-<br>pose I/O pin.                                                                                                                            |  |  |  |  |  |

| MISO                                | I/O        | Master-In/Slave-Out. This pin is the data input to the SPI master device and the data output from the SPI slave device. It is multiplexed with a general-purpose I/O pin.                                                                                                                                       |  |  |  |  |  |

| UART Contro                         | ollers     |                                                                                                                                                                                                                                                                                                                 |  |  |  |  |  |

| TXD0/TXD1                           | 0          | Transmit Data. These signals are the transmit outputs from the UARTs. The TxD signals are multiplexed with general-purpose I/O pins.                                                                                                                                                                            |  |  |  |  |  |

| RXD0/RXD1                           | I          | Receive Data. These signals are the receiver inputs for the UARTs and IrDAs.<br>The RxD signals are multiplexed with general-purpose I/O pins.                                                                                                                                                                  |  |  |  |  |  |

| CTS0/CTS1                           | I          | Clear To Send. These signals are control inputs for the UARTs. The $\overline{\text{CTS}}$ signals are multiplexed with general-purpose I/O pins.                                                                                                                                                               |  |  |  |  |  |

| DE0/DE1                             | 0          | Driver Enable. This signal allows automatic control of external RS-485 drivers.<br>This signal is approximately the inverse of the Transmit Empty (TXE) bit in the<br>UART Status 0 Register. The DE signal may be used to ensure an external<br>RS-485 driver is enabled when data is transmitted by the UART. |  |  |  |  |  |

| Timers                              |            |                                                                                                                                                                                                                                                                                                                 |  |  |  |  |  |

| T0OUT/<br>T1OUT/<br>T2OUT/<br>T3OUT | 0          | Timer Output 0-3. These signals are output pins from the timers. The timer output signals are multiplexed with general-purpose I/O pins. T3OUT is not available in 44-pin package devices.                                                                                                                      |  |  |  |  |  |

| T0IN/T1IN/<br>T2IN/T3IN             | I          | Timer Input 0-3. These signals are used as the capture, gating and counter inputs. The timer input signals are multiplexed with general-purpose I/O pins. T3IN is not available in 44-pin package devices.                                                                                                      |  |  |  |  |  |

| Analog                              |            |                                                                                                                                                                                                                                                                                                                 |  |  |  |  |  |

| ANA[11:0]                           | I          | Analog Input. These signals are inputs to the ADC. The ADC analog inputs are multiplexed with general-purpose I/O pins.                                                                                                                                                                                         |  |  |  |  |  |

| V <sub>REF</sub>                    | I          | Analog-to-Digital converter reference voltage input. The V <sub>REF</sub> pin must be left unconnected (or capacitively coupled to analog ground) if the internal voltage reference is selected as the ADC reference voltage.                                                                                   |  |  |  |  |  |

## Table 3. Signal Descriptions (Continued)

## Reset and Stop Mode Recovery

The Reset Controller within the Z8 Encore! XP F64xx Series controls Reset and Stop Mode Recovery operation. In typical operation, the following events cause a Reset to occur:

- Power-On Reset

- Voltage Brown-Out

- Watchdog Timer time-out (when configured via the WDT\_RES option bit to initiate a Reset)

- External **RESET** pin assertion

- On-Chip Debugger initiated Reset (OCDCTL[0] set to 1)

When the Z8 Encore! XP F64xx Series devices are in STOP Mode, a Stop Mode Recovery is initiated by either of the following events:

- Watchdog Timer time-out

- GPIO port input pin transition on an enabled Stop Mode Recovery source

- DBG pin driven Low

## **Reset Types**

The Z8 Encore! XP F64xx Series provides two different types of reset operation (system reset and Stop Mode Recovery). The type of Reset is a function of both the current operating mode of the Z8 Encore! XP F64xx Series devices and the source of the Reset. Table 8 lists the types of Reset and their operating characteristics.

| Table 8. Reset and Sto | p Mode Recover | y Characteristics | and Latency |

|------------------------|----------------|-------------------|-------------|

|------------------------|----------------|-------------------|-------------|

|                       | Reset Characteristics and Latency      |         |                                                   |  |  |  |

|-----------------------|----------------------------------------|---------|---------------------------------------------------|--|--|--|

| Reset Type            | <b>Control Registers</b>               | eZ8 CPU | Reset Latency (Delay)                             |  |  |  |

| System reset          | Reset (as applicable)                  | Reset   | 66 WDT Oscillator cycles + 16 System Clock cycles |  |  |  |

| Stop Mode<br>Recovery | Unaffected, except<br>WDT_CTL Register | Reset   | 66 WDT Oscillator cycles + 16 System Clock cycles |  |  |  |

### Port A–H Alternate Function Subregisters

The Port A–H Alternate Function Subregister, shown in Table 17, is accessed through the Port A–H Control Register by writing 02H to the Port A–H Address Register. The Port A–H Alternate Function subregisters select the alternate functions for the selected pins. To determine the alternate function associated with each port pin, see the <u>GPIO Alternate</u> <u>Functions</u> section on page 37.

**Caution:** Do not enable alternate function for GPIO port pins which do not have an associated alternate function. Failure to follow this guideline may result in unpredictable operation.

| Bit                                                                                                             | 7         | 6   | 5   | 4   | 3   | 2   | 1   | 0   |

|-----------------------------------------------------------------------------------------------------------------|-----------|-----|-----|-----|-----|-----|-----|-----|

| Field                                                                                                           | AF7       | AF6 | AF5 | AF4 | AF3 | AF2 | AF1 | AF0 |

| RESET                                                                                                           | 0         |     |     |     |     |     |     |     |

| R/W                                                                                                             |           |     |     | R/  | W   |     |     |     |

| Address                                                                                                         | See note. |     |     |     |     |     |     |     |

| Note: If a 02H exists in the Port A–H Address Register, it is accessible through the Port A–H Control Register. |           |     |     |     |     |     |     |     |

#### Table 17. Port A–H Alternate Function Subregisters

## Bit Description

### [7:0] **Port Alternate Function Enabled**

- AFx 0 = The port pin is in NORMAL Mode and the DDx bit in the Port A–H Data Direction Subregister determines the direction of the pin.

- 1 = The alternate function is selected. Port pin operation is controlled by the alternate function.

Note: x indicates register bits in the range [7:0].

To avoid missing interrupts, use the coding style in Example 2 to clear bits in the Interrupt Request 0 Register:

**Example 2.** A good coding style that avoids lost interrupt requests:

ANDX IRQ0, MASK

## Software Interrupt Assertion

Program code can generate interrupts directly. Writing a 1 to the appropriate bit in the Interrupt Request Register triggers an interrupt (assuming that interrupt is enabled). When the interrupt request is acknowledged by the eZ8 CPU, the bit in the Interrupt Request Register is automatically cleared to 0.

Caution: Zilog recommends not using a coding style to generate software interrupts by setting bits in the Interrupt Request registers. All incoming interrupts received between execution of the first LDX command and the final LDX command are lost. See Example 3, which follows.

**Example 3.** A poor coding style that can result in lost interrupt requests:

```

LDX r0, IRQ0

OR r0, MASK

LDX IRQ0, r0

```

To avoid missing interrupts, use the coding style in Example 4 to set bits in the Interrupt Request registers:

**Example 4.** A good coding style that avoids lost interrupt requests:

ORX IRQ0, MASK

## Interrupt Control Register Definitions

For all interrupts other than the Watchdog Timer interrupt, the interrupt control registers enable individual interrupts, set interrupt priorities, and indicate interrupt requests.

## Interrupt Request 0 Register

The Interrupt Request 0 (IRQ0) Register, shown in Table 24, stores the interrupt requests for both vectored and polled interrupts. When a request is presented to the interrupt controller, the corresponding bit in the IRQ0 Register becomes 1. If interrupts are globally enabled (vectored interrupts), the interrupt controller passes an interrupt request to the eZ8 CPU. If interrupts are globally disabled (polled interrupts), the eZ8 CPU can read the Interrupt Request 0 Register to determine if any interrupt requests are pending.

Every subsequent appropriate transition (after the first) of the timer input signal captures the current count value. The Capture value is written to the Timer PWM High and Low Byte Registers. When the capture event occurs, an interrupt is generated, the count value in the Timer High and Low Byte registers is reset to 0001H, and counting resumes.

If no capture event occurs, the timer counts up to the 16-bit compare value stored in the Timer Reload High and Low Byte registers. Upon reaching the compare value, the timer generates an interrupt, the count value in the Timer High and Low Byte registers is reset to 0001H and counting resumes.

Observe the following procedure for configuring a timer for CAPTURE/COMPARE Mode and initiating the count:

- 1. Write to the Timer Control 1 Register to:

- Disable the timer

- Configure the timer for CAPTURE/COMPARE Mode

- Set the prescale value

- Set the Capture edge (rising or falling) for the timer input

- 2. Write to the Timer High and Low Byte registers to set the starting count value (typically 0001H).

- 3. Write to the Timer Reload High and Low Byte registers to set the compare value.

- 4. If appropriate, enable the timer interrupt and set the timer interrupt priority by writing to the relevant interrupt registers.

- 5. Configure the associated GPIO port pin for the timer input alternate function.

- 6. Write to the Timer Control 1 Register to enable the timer.

- 7. Counting begins on the first appropriate transition of the timer input signal. No interrupt is generated by this first edge.

In COMPARE Mode, the elapsed time from timer start to capture event can be calculated using the following equation:

Capture Elapsed Time (s) =  $\frac{(Capture Value - Start Value) \times Prescale}{System Clock Frequency (Hz)}$

## **Reading the Timer Count Values**

The current count value in the timers can be read while counting (enabled). This capability has no effect on timer operation. When the timer is enabled and the Timer High Byte Register is read, the contents of the Timer Low Byte Register are placed in a holding register. A subsequent read from the Timer Low Byte Register returns the value in the holding reg-

| Bit         | Description (Continued)                                                                                                                                                                                                                                                                                                                                                                                |

|-------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| [2]<br>TDRE | <ul> <li>Transmitter Data Register Empty</li> <li>This bit indicates that the UART Transmit Data Register is empty and ready for additional data.</li> <li>Writing to the UART Transmit Data Register resets this bit.</li> <li>0 = Do not write to the UART Transmit Data Register.</li> <li>1 = The UART Transmit Data Register is ready to receive an additional byte to be transmitted.</li> </ul> |

| [1]<br>TXE  | <ul> <li>Transmitter Empty</li> <li>This bit indicates that the Transmit Shift Register is empty and character transmission is finished.</li> <li>0 = Data is currently transmitting.</li> <li>1 = Transmission is complete.</li> </ul>                                                                                                                                                                |

| [0]<br>CTS  | CTS Signal<br>When this bit is read, it returns the level of the CTS signal.                                                                                                                                                                                                                                                                                                                           |

## **UART Status 1 Register**

The UART Status 1 Register, shown in Table 56, contains multiprocessor control and UART status bits.

## Table 56. UART Status 1 Register (UxSTAT1)

| Bit     | 7                    | 6 | 5 | 4 | 3 | 2 | 1 | 0 |

|---------|----------------------|---|---|---|---|---|---|---|

| Field   | Reserved NEWFRM MPRX |   |   |   |   |   |   |   |

| RESET   | 0                    |   |   |   |   |   |   |   |

| R/W     | R R/W R              |   |   |   |   |   |   |   |

| Address | F44H and F4CH        |   |   |   |   |   |   |   |

| Bit           | Description                                                                                                                                                                                                                                                                                     |

|---------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| [7:2]         | Reserved<br>These bits are reserved and must be programmed to 000000.                                                                                                                                                                                                                           |

| [1]<br>NEWFRM | <ul> <li>New Frame</li> <li>Status bit denoting the start of a new frame. Reading the UART Receive Data Register resets this bit to 0.</li> <li>0 = The current byte is not the first data byte of a new frame.</li> <li>1 = The current byte is the first data byte of a new frame.</li> </ul> |

| [0]<br>MPRX   | Multiprocessor Receive<br>Returns the value of the last multiprocessor bit received. Reading from the UART Receive<br>Data Register resets this bit to 0.                                                                                                                                       |

101

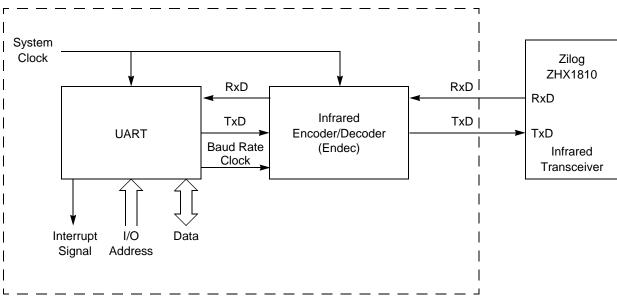

# Infrared Encoder/Decoder

The Z8 Encore! XP F64xx Series products contain two fully-functional, high-performance UART-to-infrared encoders/decoders (endecs). Each infrared endec is integrated with an on-chip UART to allow easy communication between the Z8 Encore! XP F64xx Series and IrDA Physical Layer Specification Version 1.3-compliant infrared transceivers. Infrared communication provides secure, reliable, low-cost, point-to-point communication between PCs, PDAs, cell phones, printers, and other infrared enabled devices.

## Architecture

Figure 19 displays the architecture of the infrared endec.

Figure 19. Infrared Data Communication System Block Diagram

## Operation

When the infrared endec is enabled, the transmit data from the associated on-chip UART is encoded as digital signals in accordance with the IrDA standard and output to the infrared transceiver via the TxD pin. Likewise, data received from the infrared transceiver is passed to the infrared endec via the RxD pin, decoded by the infrared endec, and then

Figure 23. SPI Configured as a Master in a Single-Master, Multiple-Slave System

Figure 24. SPI Configured as a Slave

# **Direct Memory Access Controller**

The Z8 Encore! XP F64xx Series Direct Memory Access (DMA) Controller provides three independent Direct Memory Access channels. Two of the channels, DMA0 and DMA1, transfer data between the on-chip peripherals and the Register File. The third channel, DMA\_ADC, controls the ADC operation and transfers SINGLE-SHOT Mode ADC output data to the Register File.

## Operation

DMA0 and DMA1, referred to collectively as DMAx, transfer data either from the on-chip peripheral control registers to the Register File, or from the Register File to the on-chip peripheral control registers. The sequence of operations in a DMAx data transfer is:

- 1. DMAx trigger source requests a DMA data transfer.

- 2. DMAx requests control of the system bus (address and data) from the eZ8 CPU.

- 3. After the eZ8 CPU acknowledges the bus request, DMA*x* transfers either a single byte or a two-byte word (depending upon configuration) and then returns system bus control to the eZ8 CPU.

- 4. If the Current Address equals the End Address, then the following conditions are true:

- DMAx reloads the original Start Address

- If configured to generate an interrupt, DMA*x* sends an interrupt request to the Interrupt Controller

- If configured for single-pass operation, DMAx resets the DEN bit in the DMAx Control Register to 0 and the DMA is disabled

If the Current Address does not equal the End Address, then the Current Address increments by 1 (single-byte transfer) or 2 (two-byte word transfer).

## Configuring DMA0 and DMA1 for Data Transfer

Observe the following procedure to configure and enable DMA0 or DMA1:

1. Write to the DMAx I/O Address Register to set the Register File address identifying the on-chip peripheral control register. The upper nibble of the 12-bit address for on-chip peripheral control registers is always FH. The full address is  $\{FH, DMAx\_IO[7:0]\}$ .

## **DMA Control of the ADC**

The Direct Memory Access (DMA) Controller can control operation of the ADC including analog input selection and conversion enable. For more information about the DMA and configuring for ADC operations, see the <u>Direct Memory Access Controller</u> chapter on page 150.

## **ADC Control Register Definitions**

This section defines the features of the following ADC Control registers.

ADC Control Register: see page 165

ADC Data High Byte Register: see page 167

ADC Data Low Bits Register: see page 168

## **ADC Control Register**

The ADC Control Register selects the analog input channel and initiates the analog-to-digital conversion.

| Bit     | 7   | 6        | 5    | 4    | 3              | 2 | 1 | 0 |

|---------|-----|----------|------|------|----------------|---|---|---|

| Field   | CEN | Reserved | VREF | CONT | ONT ANAIN[3:0] |   |   |   |

| RESET   | (   | )        | 1    | 0    |                |   |   |   |

| R/W     |     |          |      | R/W  |                |   |   |   |

| Address |     |          | F70H |      |                |   |   |   |

| Table 87. | ADC Control | Register | (ADCCTL) |

|-----------|-------------|----------|----------|

|-----------|-------------|----------|----------|

| Bit         | Description                                                                                                                                                                                                                                                                                                                                                                                                            |

|-------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| [7]<br>CEN  | <ul> <li>Conversion Enable</li> <li>0 = Conversion is complete. Writing a 0 produces no effect. The ADC automatically clears this bit to 0 when a conversion has been completed.</li> <li>1 = Begin conversion. Writing a 1 to this bit starts a conversion. If a conversion is already in progress, the conversion restarts. This bit remains 1 until the conversion is complete.</li> </ul>                          |

| [6]         | <b>Reserved</b><br>This bit is reserved and must be programmed to 0.                                                                                                                                                                                                                                                                                                                                                   |

| [5]<br>VREF | <ul> <li>Voltage Reference</li> <li>0 = Internal voltage reference generator enabled. The V<sub>REF</sub> pin should be left unconnected (or capacitively coupled to analog ground) if the internal voltage reference is selected as the ADC reference voltage.</li> <li>1 = Internal voltage reference generator disabled. An external voltage reference must be provided through the V<sub>REF</sub> pin.</li> </ul> |

# **Option Bits**

Option bits allow user configuration of certain aspects of the Z8 Encore! XP F64xx Series operation. The feature configuration data is stored in the Flash memory and read during Reset. The features available for control via the option bits are:

- Watchdog Timer time-out response selection-interrupt or Reset

- Watchdog Timer enabled at Reset

- The ability to prevent unwanted read access to user code in Flash memory

- The ability to prevent accidental programming and erasure of the user code in Flash memory

- Voltage Brown-Out configuration is always enabled or disabled during STOP Mode to reduce STOP Mode power consumption

- Oscillator mode selection for high-, medium-, and low-power crystal oscillators or an external RC oscillator

## Operation

This section describes the type and configuration of the programmable Flash option bits.

## **Option Bit Configuration By Reset**

Each time the option bits are programmed or erased, the device must be Reset for the change to take place. During any reset operation (System Reset, Reset, or Stop Mode Recovery), the option bits are automatically read from the Flash memory and written to Option Configuration registers. The Option Configuration registers control operation of the devices within the Z8 Encore! XP F64xx Series. Option bit control is established before the device exits Reset and the eZ8 CPU begins code execution. The Option Configuration registers are not part of the Register File and are not accessible for read or write access.

## **Option Bit Address Space**

The first two bytes of Flash memory at addresses 0000H (see Table 99) and 0001H (see Table 100) are reserved for the user option bits. The byte at Flash memory address 0000H configures user options. The byte at Flash memory address 0001H is reserved for future use and must remain unprogrammed.

## **On-Chip Debugger Control Register Definitions**

This section describes the features of the On-Chip Debugger Control and Status registers.

## **OCD Control Register**

The OCD Control Register, shown in Table 103, controls the state of the On-Chip Debugger. This register enters or exits DEBUG Mode and enables the BRK instruction.

A *reset and stop* function can be achieved by writing 81H to this register. A *reset and go* function can be achieved by writing 41H to this register. If the device is operating in DEBUG Mode, a *run* function can be implemented by writing 40H to this register.

| Bit            | 7                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | 6                                                                                                                                                                                                                                                                                                                                                                       | 5      | 4       | 3 | 2        | 1 | 0   |  |  |  |

|----------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------|---------|---|----------|---|-----|--|--|--|

| Field          | DBGMODE                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | BRKEN                                                                                                                                                                                                                                                                                                                                                                   | DBGACK | BRKLOOP |   | Reserved |   | RST |  |  |  |

| RESET          |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | 0                                                                                                                                                                                                                                                                                                                                                                       |        |         |   |          |   |     |  |  |  |

| R/W            |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | R/W                                                                                                                                                                                                                                                                                                                                                                     |        |         | F | २        |   | R/W |  |  |  |

| Bit            | Descriptio                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | Description                                                                                                                                                                                                                                                                                                                                                             |        |         |   |          |   |     |  |  |  |

| [7]<br>DBGMODE | <ul> <li>DEBUG Mode</li> <li>E Setting this bit to 1 causes the device to enter DEBUG Mode. When in DEBUG Mode, the eZ8 CPU stops fetching new instructions. Clearing this bit causes the eZ8 CPU to start running again. This bit is automatically set when a BRK instruction is decoded and breakpoints are enabled. If the Read Protect option bit is enabled, this bit can only be cleared by resetting the device, it cannot be written to 0.</li> <li>0 = TheZ8 Encore! XP F64xx Series device is operating in NORMAL Mode.</li> <li>1 = The Z8 Encore! XP F64xx Series device is in DEBUG Mode.</li> </ul> |                                                                                                                                                                                                                                                                                                                                                                         |        |         |   |          |   |     |  |  |  |

| [6]<br>BRKEN   | This bit co<br>are disable<br>instruction<br>0 = BRK in                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | <b>Breakpoint Enable</b><br>This bit controls the behavior of the BRK instruction (op code 00H). By default, breakpoints are disabled and the BRK instruction behaves like a NOP. If this bit is set to 1 and a BRK instruction is decoded, the OCD takes action dependent upon the BRKLOOP bit.<br>0 = BRK instruction is disabled.<br>1 = BRK instruction is enabled. |        |         |   |          |   |     |  |  |  |

| [5]<br>DBGACK  | This bit en<br>an Debug<br>0 = Debug                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | <ul> <li>Debug Acknowledge</li> <li>This bit enables the debug acknowledge feature. If this bit is set to 1, then the OCD sends an Debug Acknowledge character (FFH) to the host when a breakpoint occurs.</li> <li>0 = Debug Acknowledge is disabled.</li> <li>1 = Debug Acknowledge is enabled.</li> </ul>                                                            |        |         |   |          |   |     |  |  |  |

### Table 103. OCD Control Register (OCDCTL)

# **Electrical Characteristics**

The data in this chapter represents all known data prior to qualification and characterization of the Z8 Encore! XP F64xx Series of products, and is therefore subject to change. Additional electrical characteristics may be found in the individual chapters of this document.

## **Absolute Maximum Ratings**

Stresses greater than those listed in Table 106 may cause permanent damage to the device. These ratings are stress ratings only. Operation of the device at any condition outside those indicated in the operational sections of these specifications is not implied. Exposure to absolute maximum rating conditions for extended periods may affect device reliability. For improved reliability, unused inputs must be tied to one of the supply voltages ( $V_{DD}$  or  $V_{SS}$ ).

| Parameter                                                      | Minimum | Maximum | Units | Notes |

|----------------------------------------------------------------|---------|---------|-------|-------|

| Ambient temperature under bias                                 | -40     | +125    | С     |       |

| Storage temperature                                            | -65     | +150    | С     |       |

| Voltage on any pin with respect to V <sub>SS</sub>             | -0.3    | +5.5    | V     | 1     |

| Voltage on $V_{DD}$ pin with respect to $V_{SS}$               | -0.3    | +3.6    | V     |       |

| Maximum current on input and/or inactive output pin            | -5      | +5      | μA    |       |

| Maximum output current from active output pin                  | -25     | +25     | mA    |       |

| 80-pin QFP maximum ratings at –40°C to 70°C                    |         |         |       |       |

| Total power dissipation                                        |         | 550     | mW    |       |

| Maximum current into $V_{DD}$ or out of $V_{SS}$               |         | 150     | mA    |       |

| 80-pin QFP maximum ratings at 70°C to 125°C                    |         |         |       |       |

| Total power dissipation                                        |         | 200     | mW    |       |

| Maximum current into $V_{DD}$ or out of $V_{SS}$               |         | 56      | mA    |       |

| 68-pin PLCC maximum ratings at -40°C to 70°C                   |         |         |       |       |

| Total power dissipation                                        |         | 1000    | mW    |       |

| Maximum current into $V_{DD}$ or out of $V_{SS}$               |         | 275     | mA    |       |

| 68-pin PLCC maximum ratings at 70°C to 125°C                   |         |         |       |       |

| Total power dissipation                                        |         | 500     | mW    |       |

| Maximum current into V <sub>DD</sub> or out of V <sub>SS</sub> |         | 140     | mA    |       |

### Table 106. Absolute Maximum Ratings

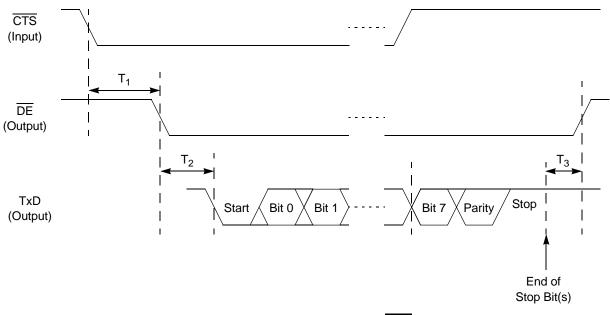

## **UART** Timing

Figure 56 and Table 121 provide timing information for UART pins for the case where the Clear To Send input pin ( $\overline{\text{CTS}}$ ) is used for flow control. In this example, it is assumed that the Driver Enable polarity has been configured to be Active Low and is represented here by  $\overline{\text{DE}}$ . The  $\overline{\text{CTS}}$  to  $\overline{\text{DE}}$  assertion delay (T1) assumes the UART Transmit Data Register has been loaded with data prior to  $\overline{\text{CTS}}$  assertion.

### Figure 56. UART Timing with CTS

### Table 121. UART Timing with CTS

|                |                                                                | Delay (ns)                 |                                              |  |  |  |

|----------------|----------------------------------------------------------------|----------------------------|----------------------------------------------|--|--|--|

| Parameter      | Abbreviation                                                   | Minimum                    | Maximum                                      |  |  |  |

| T <sub>1</sub> | CTS Fall to DE Assertion Delay                                 | 2 * X <sub>IN</sub> period | 2 * X <sub>IN</sub> period +<br>1 bit period |  |  |  |

| T <sub>2</sub> | DE Assertion to TxD Falling Edge (Start) Delay                 | 1 bit period               | 1 bit period +<br>1 * X <sub>IN</sub> period |  |  |  |

| T <sub>3</sub> | End of stop bit(s) to $\overline{\text{DE}}$ Deassertion Delay | 1 * X <sub>IN</sub> period | 2 * X <sub>IN</sub> period                   |  |  |  |

| Mnemonic | Operands | Instruction            |

|----------|----------|------------------------|

| ATM      | _        | Atomic Execution       |

| CCF      | _        | Complement Carry Flag  |

| DI       | —        | Disable Interrupts     |

| EI       | —        | Enable Interrupts      |

| HALT     | _        | HALT Mode              |

| NOP      | —        | No Operation           |

| RCF      | —        | Reset Carry Flag       |

| SCF      | —        | Set Carry Flag         |

| SRP      | src      | Set Register Pointer   |

| STOP     | —        | STOP Mode              |

| WDT      | —        | Watchdog Timer Refresh |

### Table 131. CPU Control Instructions

### Table 132. Load Instructions

| Mnemonic | Operands    | Instruction                                                              |

|----------|-------------|--------------------------------------------------------------------------|

| CLR      | dst         | Clear                                                                    |

| LD       | dst, src    | Load                                                                     |

| LDC      | dst, src    | Load Constant to/from program memory                                     |

| LDCI     | dst, src    | Load Constant to/from program memory and Auto-Incre-<br>ment addresses   |

| LDE      | dst, src    | Load External Data to/from Data Memory                                   |

| LDEI     | dst, src    | Load External Data to/from Data Memory and Auto-Incre-<br>ment addresses |

| LDWX     | dst, src    | Load Word using Extended Addressing                                      |

| LDX      | dst, src    | Load using Extended Addressing                                           |

| LEA      | dst, X(src) | Load Effective Address                                                   |

| POP      | dst         | Рор                                                                      |

| POPX     | dst         | Pop using Extended Addressing                                            |

| PUSH     | src         | Push                                                                     |

| PUSHX    | SIC         | Push using Extended Addressing                                           |

## Hex Address: F40

### Table 170. UART Transmit Data Register (UxTXD)

| Bit     | 7 | 6   | 5 | 4       | 3       | 2 | 1 | 0 |  |  |  |  |

|---------|---|-----|---|---------|---------|---|---|---|--|--|--|--|

| Field   |   | TXD |   |         |         |   |   |   |  |  |  |  |

| RESET   |   | X   |   |         |         |   |   |   |  |  |  |  |

| R/W     |   | W   |   |         |         |   |   |   |  |  |  |  |

| Address |   |     |   | F40H ar | nd F48H |   |   |   |  |  |  |  |

### Table 171. UART Receive Data Register (UxRXD)

| Bit     | 7 | 6   | 5 | 4       | 3       | 2 | 1 | 0 |  |  |  |

|---------|---|-----|---|---------|---------|---|---|---|--|--|--|

| Field   |   | RXD |   |         |         |   |   |   |  |  |  |

| RESET   |   | X   |   |         |         |   |   |   |  |  |  |

| R/W     |   | R   |   |         |         |   |   |   |  |  |  |

| Address |   |     |   | F40H ar | nd F48H |   |   |   |  |  |  |

## Hex Address: F41

### Table 172. UART Status 0 Register (UxSTAT0)

| Bit     | 7   | 6             | 5  | 4  | 3    | 2    | 1   | 0   |  |

|---------|-----|---------------|----|----|------|------|-----|-----|--|

| Field   | RDA | PE            | OE | FE | BRKD | TDRE | TXE | CTS |  |

| RESET   |     |               | 0  |    |      |      | 1   | Х   |  |

| R/W     |     | R             |    |    |      |      |     |     |  |

| Address |     | F41H and F49H |    |    |      |      |     |     |  |

## Hex Address: F42

## Table 173. UART Control 0 Register (UxCTL0)

| Bit     | 7   | 6   | 5    | 4       | 3       | 2    | 1    | 0    |  |  |

|---------|-----|-----|------|---------|---------|------|------|------|--|--|

| Field   | TEN | REN | CTSE | PEN     | PSEL    | SBRK | STOP | LBEN |  |  |

| RESET   |     | 0   |      |         |         |      |      |      |  |  |

| R/W     |     | R/W |      |         |         |      |      |      |  |  |

| Address |     |     |      | F42H ar | nd F4AH |      |      |      |  |  |

285

### Table 268. Flash Sector Protect Register (FPROT)

| Bit        | 7                                                                                                        | 6     | 5     | 4     | 3     | 2     | 1     | 0     |  |  |

|------------|----------------------------------------------------------------------------------------------------------|-------|-------|-------|-------|-------|-------|-------|--|--|

| Field      | SECT7                                                                                                    | SECT6 | SECT5 | SECT4 | SECT3 | SECT2 | SECT1 | SECT0 |  |  |

| RESET      |                                                                                                          | 0     |       |       |       |       |       |       |  |  |

| R/W        |                                                                                                          | R/W*  |       |       |       |       |       |       |  |  |

| Address    | FF9H                                                                                                     |       |       |       |       |       |       |       |  |  |

| Note: *R/V | Note: *R/W = This register is accessible for read operations; it can be written to 1 only via user code. |       |       |       |       |       |       |       |  |  |

### Hex Address: FFA

### Table 269. Flash Frequency High Byte Register (FFREQH)

| Bit     | 7 | 6      | 5 | 4   | 3  | 2 | 1 | 0 |  |  |  |

|---------|---|--------|---|-----|----|---|---|---|--|--|--|

| Field   |   | FFREQH |   |     |    |   |   |   |  |  |  |

| RESET   |   |        |   | (   | )  |   |   |   |  |  |  |

| R/W     |   | R/W    |   |     |    |   |   |   |  |  |  |

| Address |   |        |   | FF. | AH |   |   |   |  |  |  |

## Hex Address: FFB

### Table 270. Flash Frequency Low Byte Register (FFREQL)

| Bit     | 7      | 6 | 5 | 4 | 3 | 2 | 1 | 0 |

|---------|--------|---|---|---|---|---|---|---|

| Field   | FFREQL |   |   |   |   |   |   |   |

| RESET   | 0      |   |   |   |   |   |   |   |

| R/W     | R/W    |   |   |   |   |   |   |   |

| Address | FFBH   |   |   |   |   |   |   |   |

### Hex Addresses: FFC-FFF

Refer to the eZ8 CPU Core User Manual (UM0128)