Detaile

#### Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

#### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

| Product Status                            | Obsolete                                   |

|-------------------------------------------|--------------------------------------------|

| Core Processor                            | eZ8                                        |

| Core Size                                 | 8-Bit                                      |

| Speed                                     | 20MHz                                      |

| Connectivity                              | I <sup>2</sup> C, IrDA, SPI, UART/USART    |

| Peripherals                               | Brown-out Detect/Reset, DMA, POR, PWM, WDT |

| Number of I/O                             | 46                                         |

| Program Memory Size                       | 24KB (24K x 8)                             |

| Program Memory Type                       | FLASH                                      |

| EEPROM Size                               | -                                          |

| RAM Size                                  | 2K x 8                                     |

| Voltage - Supply (Vcc/Vdd)                | 3V ~ 3.6V                                  |

| Data Converters                           | A/D 12x10b                                 |

| Oscillator Type                           | Internal                                   |

| Operating Temperature                     | 0°C ~ 70°C (TA)                            |

| Mounting Type                             | Surface Mount                              |

|                                           |                                            |

| Package / Case                            | 68-LCC (J-Lead)                            |

| Package / Case<br>Supplier Device Package |                                            |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

### Z8 Encore! XP<sup>®</sup> F64xx Series Product Specification

9

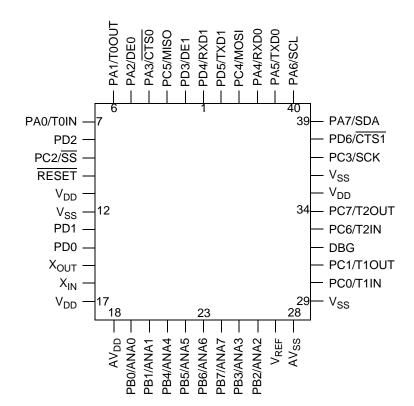

Figure 3. Z8 Encore! XP F64xx Series in 44-Pin Plastic Leaded Chip Carrier (PLCC)

**Note:** Timer 3 is not available in the 44-pin PLCC package.

| Priority | Program Memory<br>Vector Address | Interrupt Source                                           |

|----------|----------------------------------|------------------------------------------------------------|

| Highest  | 0002H                            | Reset (not an interrupt)                                   |

|          | 0004H                            | Watchdog Timer (see the Watchdog Timer chapter on page 80) |

|          | 0006H                            | Illegal Instruction Trap (not an interrupt)                |

|          | 0008H                            | Timer 2                                                    |

|          | 000AH                            | Timer 1                                                    |

|          | 000CH                            | Timer 0                                                    |

|          | 000EH                            | UART 0 receiver                                            |

|          | 0010H                            | UART 0 transmitter                                         |

|          | 0012H                            | l <sup>2</sup> C                                           |

|          | 0014H                            | SPI                                                        |

|          | 0016H                            | ADC                                                        |

|          | 0018H                            | Port A7 or Port D7, rising or falling input edge           |

|          | 001AH                            | Port A6 or Port D6, rising or falling input edge           |

|          | 001CH                            | Port A5 or Port D5, rising or falling input edge           |

|          | 001EH                            | Port A4 or Port D4, rising or falling input edge           |

|          | 0020H                            | Port A3 or Port D3, rising or falling input edge           |

|          | 0022H                            | Port A2 or Port D2, rising or falling input edge           |

|          | 0024H                            | Port A1 or Port D1, rising or falling input edge           |

|          | 0026H                            | Port A0 or Port D0, rising or falling input edge           |

|          | 0028H                            | Timer 3 (not available in the 44-pin package)              |

|          | 002AH                            | UART 1 receiver                                            |

|          | 002CH                            | UART 1 transmitter                                         |

|          | 002EH                            | DMA                                                        |

|          | 0030H                            | Port C3, both input edges                                  |

|          | 0032H                            | Port C2, both input edges                                  |

|          | 0034H                            | Port C1, both input edges                                  |

| Lowest   | 0036H                            | Port C0, both input edges                                  |

### Table 23. Interrupt Vectors in Order of Priority

- Set or clear the CTSE bit to enable or disable control from the remote receiver via the  $\overline{\text{CTS}}$  pin

- 8. Execute an EI instruction to enable interrupts.

The UART is now configured for interrupt-driven data transmission. Because the UART Transmit Data Register is empty, an interrupt is generated immediately. When the UART transmit interrupt is detected, the associated interrupt service routine performs the following functions:

- 1. Write the UART Control 1 Register to select the outgoing address bit:

- Set the MULTIPROCESSOR Bit Transmitter (MPBT) if sending an address byte; clear it if sending a data byte.

- 2. Write the data byte to the UART Transmit Data Register. The transmitter automatically transfers the data to the Transmit Shift Register and transmits the data.

- 3. Clear the UART transmit interrupt bit in the applicable Interrupt Request Register.

- 4. Execute the IRET instruction to return from the interrupt service routine and wait for the Transmit Data Register to again become empty.

## **Receiving Data using the Polled Method**

Observe the following procedure to configure the UART for polled data reception:

- 1. Write to the UART Baud Rate High and Low Byte registers to set the appropriate baud rate.

- 2. Enable the UART pin functions by configuring the associated GPIO port pins for alternate function operation.

- 3. Write to the UART Control 1 Register to enable MULTIPROCESSOR Mode functions, if appropriate.

- 4. Write to the UART Control 0 Register to:

- Set the receive enable bit (REN) to enable the UART for data reception

- Enable parity, if appropriate and if MULTIPROCESSOR Mode is not enabled, and select either even or odd parity

- 5. Check the RDA bit in the UART Status 0 Register to determine if the Receive Data Register contains a valid data byte (indicated by a 1). If RDA is set to 1 to indicate available data, continue to <u>Step 6</u>. If the Receive Data Register is empty (indicated by a 0), continue to monitor the RDA bit awaiting reception of the valid data.

## **UART Control 0 and Control 1 Registers**

The UART Control 0 and Control 1 Registers, shown in Tables 57 and 58, configure the properties of the UART's transmit and receive operations. The UART Control registers must not been written while the UART is enabled.

#### Table 57. UART Control 0 Register (UxCTL0)

| Bit         | 7                                          | 6                                                                            | 5                  | 4              | 3       | 2              | 1             | 0    |

|-------------|--------------------------------------------|------------------------------------------------------------------------------|--------------------|----------------|---------|----------------|---------------|------|

| Field       | TEN                                        | REN                                                                          | CTSE               | PEN            | PSEL    | SBRK           | STOP          | LBEN |

| RESET       |                                            |                                                                              |                    | (              | )       |                |               |      |

| R/W         |                                            |                                                                              |                    | R/             | W       |                |               |      |

| Address     |                                            |                                                                              |                    | F42H ar        | nd F4AH |                |               |      |

| Bit         | Descriptio                                 | n                                                                            |                    |                |         |                |               |      |

| [7]<br>TEN  | and the CT<br>0 = Transm                   | Enable<br>ables or disa<br>SE bit. If the<br>hitter disable<br>hitter enable | e CTS signal<br>d. |                |         |                |               |      |

| [6]<br>REN  | 0 = Receive                                | <b>nable</b><br>ables or disa<br>er disabled.<br>er enabled.                 | bles the rec       | eiver.         |         |                |               |      |

| [5]<br>CTSE |                                            | l <b>e</b><br>S signal has<br>RT recogniz                                    |                    |                |         | ntrol from the | e transmitter | :    |

| [4]<br>PEN  | by the MPE<br>0 = Parity is<br>1 = The tra | ables or disa<br>EN bit.                                                     |                    |                |         |                |               |      |

| [3]<br>PSEL |                                            | ect<br>arity is trans<br>rity is transr                                      |                    |                |         |                |               |      |

| [2]<br>SBRK | progress, s<br>0 = No brea                 | uses or brea                                                                 | at the transn      | nitter has fin | •       |                |               |      |

## **Slave Operation**

The SPI block is configured for SLAVE Mode operation by setting the SPIEN bit to 1 and the MMEN bit to 0 in the SPICTL Register and setting the SSIO bit to 0 in the SPIMODE Register. The IRQE, PHASE, CLKPOL, WOR bits in the SPICTL Register and the NUMBITS field in the SPIMODE Register must be set to be consistent with the other SPI devices. The STR bit in the SPICTL Register may be used if appropriate to force a *start-up* interrupt. The BIRQ bit in the SPICTL Register and the SSV bit in the SPIMODE Register are not used in SLAVE Mode. The SPI baud rate generator is not used in SLAVE Mode so the SPIBRH and SPIBRL registers need not be initialized.

If the slave has data to send to the master, the data must be written to the SPIDAT Register before the transaction starts (first edge of SCK when  $\overline{SS}$  is asserted). If the SPIDAT Register is not written prior to the slave transaction, the MISO pin outputs whatever value is currently in the SPIDAT Register.

Due to the delay resulting from synchronization of the SPI input signals to the internal system clock, the maximum SPICLK baud rate that can be supported in SLAVE Mode is the system clock frequency ( $X_{IN}$ ) divided by 8. This rate is controlled by the SPI master.

## **Error Detection**

The SPI contains error detection logic to support SPI communication protocols and recognize when communication errors have occurred. The SPI Status Register indicates when a data transmission error has been detected.

## **Overrun (Write Collision)**

An overrun error (write collision) indicates that a write to the SPI Data Register was attempted while a data transfer was in progress (in either MASTER or SLAVE modes). An overrun sets the OVR bit in the SPI Status Register to 1. Writing a 1 to OVR clears this error flag. The data register is not altered when a write occurs while data transfer is in progress.

### Mode Fault (Multimaster Collision)

A mode fault indicates when more than one Master is trying to communicate at the same time (a multimaster collision). The mode fault is detected when the enabled Master's  $\overline{SS}$  pin is asserted. A mode fault sets the COL bit in the SPI Status Register to 1. Writing a 1 to COL clears this error flag.

### Slave Mode Abort

In the SLAVE Mode of operation, if the  $\overline{SS}$  pin deasserts before all bits in a character have been transferred, the transaction is aborted. When this condition occurs, the ABT bit is set in the SPISTAT Register as well as the IRQ bit (indicating the transaction is complete).

| Bit         | Description (Continued)                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

|-------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| [5]<br>COL  | <ul> <li>Collision</li> <li>0 = A multimaster collision (mode fault) has not occurred.</li> <li>1 = A multimaster collision (mode fault) has been detected.</li> </ul>                                                                                                                                                                                                                                                                                                    |

| [4]<br>ABT  | <ul> <li>Slave Mode Transaction Abort</li> <li>This bit is set if the SPI is configured in slave mode, a transaction is occurring and SS deasserts before all bits of a character have been transferred as defined by the NUMBITS field of the SPIMODE Register. The IRQ bit also sets, indicating the transaction has completed.</li> <li>0 = A slave mode transaction abort has not occurred.</li> <li>1 = A slave mode transaction abort has been detected.</li> </ul> |

| [3:2]       | <b>Reserved</b><br>These bits are reserved and must be programmed to 00.                                                                                                                                                                                                                                                                                                                                                                                                  |

| [1]<br>TXST | Transmit Status<br>0 = No data transmission currently in progress.<br>1 = Data transmission currently in progress.                                                                                                                                                                                                                                                                                                                                                        |

| [0]<br>SLAS | Slave Select<br>If SPI enabled as a Slave, then the following conditions are true:<br>$0 = \frac{SS}{SS}$ input pin is asserted (Low).<br>$1 = \frac{SS}{SS}$ input is not asserted (High).<br>If SPI enabled as a Master, this bit is not applicable.                                                                                                                                                                                                                    |

I<sup>2</sup>C Interrupt

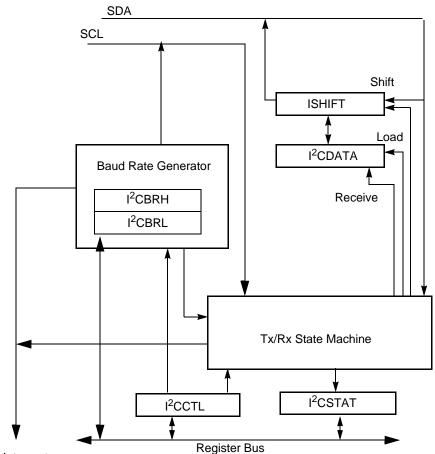

Figure 27. I<sup>2</sup>C Controller Block Diagram

# Operation

The I<sup>2</sup>C Controller operates in MASTER Mode to transmit and receive data. Only a single master is supported. Arbitration between two masters must be accomplished in software. I<sup>2</sup>C supports the following operations:

- Master transmits to a 7-bit slave

- Master transmits to a 10-bit slave

- Master receives from a 7-bit slave

- Master receives from a 10-bit slave

| S | Slave Address | W = 0 | А | Data | А | Data | А | Data | A/A | P/S |

|---|---------------|-------|---|------|---|------|---|------|-----|-----|

|   |               |       |   |      |   |      |   |      |     |     |

#### Figure 29. 7-Bit Addressed Slave Data Transfer Format

Observe the following procedure for a transmit operation to a 7-bit addressed slave:

- 1. Software asserts the IEN bit in the  $I^2C$  Control Register.

- 2. Software asserts the TXI bit of the  $I^2C$  Control Register to enable transmit interrupts.

- 3. The  $I^2C$  interrupt asserts, because the  $I^2C$  Data Register is empty

- 4. Software responds to the TDRE bit by writing a 7-bit slave address plus write bit (=0) to the  $I^2C$  Data Register.

- 5. Software asserts the start bit of the  $I^2C$  Control Register.

- 6. The  $I^2C$  Controller sends the start condition to the  $I^2C$  slave.

- 7. The I<sup>2</sup>C Controller loads the I<sup>2</sup>C Shift Register with the contents of the I<sup>2</sup>C Data Register.

- 8. After one bit of address has been shifted out by the SDA signal, the transmit interrupt is asserted (TDRE = 1).

- 9. Software responds by writing the transmit data into the  $I^2C$  Data Register.

- 10. The I<sup>2</sup>C Controller shifts the rest of the address and write bit out by the SDA signal.

- 11. If the I<sup>2</sup>C slave sends an acknowledge (by pulling the SDA signal Low) during the next High period of SCL the I<sup>2</sup>C Controller sets the ACK bit in the I<sup>2</sup>C Status Register. Continue with <u>Step 12</u>.

If the slave does not acknowledge, the Not Acknowledge interrupt occurs (NCKI bit is set in the Status Register, ACK bit is cleared). Software responds to the Not Acknowledge interrupt by setting the stop and flush bits and clearing the TXI bit. The I<sup>2</sup>C Controller sends the stop condition on the bus and clears the stop and NCKI bits. The transaction is complete (ignore the following steps).

- 12. The I<sup>2</sup>C Controller loads the contents of the I<sup>2</sup>C Shift Register with the contents of the I<sup>2</sup>C Data Register.

- 13. The I<sup>2</sup>C Controller shifts the data out of using the SDA signal. After the first bit is sent, the transmit interrupt is asserted.

- 14. If more bytes remain to be sent, return to Step 9.

- 15. Software responds by setting the stop bit of the I<sup>2</sup>C Control Register (or start bit to initiate a new transaction). In the stop case, software clears the TXI bit of the I<sup>2</sup>C Control Register at the same time.

- 10. The I<sup>2</sup>C Controller shifts the rest of the first byte of address and write bit out the SDA signal.

- If the I<sup>2</sup>C slave sends an acknowledge by pulling the SDA signal Low during the next High period of SCL the I<sup>2</sup>C Controller sets the ACK bit in the I<sup>2</sup>C Status Register. Continue with <u>Step 12</u>.

If the slave does not acknowledge the first address byte, the I<sup>2</sup>C Controller sets the NCKI bit and clears the ACK bit in the I<sup>2</sup>C Status Register. Software responds to the Not Acknowledge interrupt by setting the stop and flush bits and clearing the TXI bit. The I<sup>2</sup>C Controller sends the stop condition on the bus and clears the stop and NCKI bits. The transaction is complete (ignore following steps).

- 12. The I<sup>2</sup>C Controller loads the I<sup>2</sup>C Shift Register with the contents of the I<sup>2</sup>C Data Register (2nd byte of address).

- 13. The I<sup>2</sup>C Controller shifts the second address byte out the SDA signal. After the first bit has been sent, the transmit interrupt is asserted.

- 14. Software responds by setting the stop bit in the I<sup>2</sup>C Control Register. The TXI bit can be cleared at the same time.

- 15. Software polls the stop bit of the  $I^2C$  Control Register. Hardware deasserts the stop bit when the transaction is completed (stop condition has been sent).

- 16. Software checks the ACK bit of the  $I^2C$  Status Register. If the slave acknowledged, the ACK bit is = 1. If the slave does not acknowledge, the ACK bit is = 0. The NCKI interrupt do not occur because the stop bit was set.

## Write Transaction with a 10-Bit Address

Figure 31 displays the data transfer format for a 10-bit addressed slave. Shaded regions indicate data transferred from the  $I^2C$  Controller to slaves and unshaded regions indicate data transferred from the slaves to the  $I^2C$  Controller.

| S 1st 7 bits $W = 0$ A 2nd Byte A Data A | S | Slave Address<br>1st 7 bits | W = 0 | А | Slave Address<br>2nd Byte | А | Data | А | Data | A/A | P/S |

|------------------------------------------|---|-----------------------------|-------|---|---------------------------|---|------|---|------|-----|-----|

|------------------------------------------|---|-----------------------------|-------|---|---------------------------|---|------|---|------|-----|-----|

Figure 31. 10-Bit Addressed Slave Data Transfer Format

The first seven bits transmitted in the first byte are 11110xx. The two bits xx are the two most significant bits of the 10-bit address. The lowest bit of the first byte transferred is the read/write control bit (=0). The transmit operation is carried out in the same manner as 7-bit addressing.

Observe the following procedure for a transmit operation on a 10-bit addressed slave:

1. Software asserts the IEN bit in the  $I^2C$  Control Register.

The  $I^2C$  Control Register, shown in Table 73, enables  $I^2C$  operation.

## Table 73. I<sup>2</sup>C Control Register (I2CCTL)

|              |                                                                                                       | la                                                                                                          | ble /3. I <sup>-</sup> C                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | Control Reg                                                                                                                  | gister (12CC                                                                       | (IL)                                                                                  |                                                                                                 |                                                                                |

|--------------|-------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------|

| Bit          | 7                                                                                                     | 6                                                                                                           | 5                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | 4                                                                                                                            | 3                                                                                  | 2                                                                                     | 1                                                                                               | 0                                                                              |

| Field        | IEN                                                                                                   | START                                                                                                       | STOP                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | BIRQ                                                                                                                         | TXI                                                                                | NAK                                                                                   | FLUSH                                                                                           | FILTEN                                                                         |

| RESET        |                                                                                                       | L                                                                                                           | L                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | (                                                                                                                            | )                                                                                  |                                                                                       |                                                                                                 |                                                                                |

| R/W          | R/W                                                                                                   | R/W1                                                                                                        | R/W1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | R/W                                                                                                                          | R/W                                                                                | R/W1                                                                                  | W1                                                                                              | R/W                                                                            |

| Address      |                                                                                                       |                                                                                                             |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | F5                                                                                                                           | 2H                                                                                 |                                                                                       |                                                                                                 |                                                                                |

| Bit          | Descriptio                                                                                            | n                                                                                                           |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |                                                                                                                              |                                                                                    |                                                                                       |                                                                                                 |                                                                                |

| [7]<br>IEN   |                                                                                                       | transmitter                                                                                                 |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | er are enable<br>er are disable                                                                                              |                                                                                    |                                                                                       |                                                                                                 |                                                                                |

| [6]<br>START | sends the S<br>0 by writing<br>I <sup>2</sup> C Data Re<br>Controller w<br>shifting out<br>completes. | ds the Start<br>START cond<br>to the regis<br>egister or I <sup>2</sup><br>vaits until the<br>data, it gene | ition or if the<br>ter. After this<br>C Shift Regis<br>e Data Regis<br>erates a star<br>it is also set                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | Once asserte<br>E IEN bit is de<br>s bit is set, tl<br>ster. If there<br>ster is writter<br>t condition a<br>t, it also wait | easserted. I<br>he Start con<br>is no data ir<br>n. If this bit i<br>fter the byte | f this bit is 1<br>dition is sen<br>n one of thes<br>is set while t<br>e shifts and t | , it cannot be<br>at if there is c<br>se registers,<br>the I <sup>2</sup> C Cont<br>he acknowle | e cleared to<br>data in the<br>the I <sup>2</sup> C<br>roller is<br>edge phase |

| [5]<br>STOP  | ter has com<br>it is set, this                                                                        | ses the I <sup>2</sup> C<br>pleted trans<br>bit is reset                                                    | mission or a by the I <sup>2</sup> C C                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | o issue a Sto<br>after a byte h<br>Controller aft<br>cannot be cl                                                            | las been rec<br>er a Stop co                                                       | ceived in a rondition has                                                             | eceive opera<br>been sent o                                                                     | ation. AFter<br>r by deas-                                                     |

| [4]<br>BIRQ  | This bit allo<br>disabled. Th<br>1 = An inter                                                         | his bit is ign                                                                                              | Controller to<br>ored when the the oregan of th | be used as<br>he I <sup>2</sup> C Contr<br>the baud rate                                                                     | oller is enal                                                                      | oled.                                                                                 |                                                                                                 | ontroller is                                                                   |

| [3]<br>TXI   | This bit ena<br>1 = Transm                                                                            | it interrupt (a                                                                                             | nsmit interru<br>and DMA tra                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | ipt when the<br>ansmit reque<br>ansmit reque                                                                                 | est) is enable                                                                     | ed.                                                                                   | npty (TDRE                                                                                      | = 1).                                                                          |

| [2]<br>NAK   | l <sup>2</sup> C slave. C                                                                             | ids a Not Ac<br>Once asserte                                                                                | ed, it is deas                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | condition after<br>serted after<br>be cleared t                                                                              | a Not Ackn                                                                         | owledge is s                                                                          | sent or the IE                                                                                  |                                                                                |

| Bit           | Description (Continued)                                                                                                                                                                                                                                                                                                                                  |

|---------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| [1]<br>FLUSH  | <b>Flush Data</b><br>Setting this bit to 1 clears the $I^2C$ Data Register and sets the TDRE bit to 1. This bit allows flushing of the $I^2C$ Data Register when a Not Acknowledge interrupt is received after the data has been sent to the $I^2C$ Data Register. Reading this bit always returns 0.                                                    |

| [0]<br>FILTEN | $I^2C$ Signal Filter Enable<br>This bit enables low-pass digital filters on the SDA and SCL input signals. These filters reject<br>any input pulse with periods less than a full system clock cycle. The filters introduce a 3-sys-<br>tem clock cycle latency on the inputs.<br>1 = low-pass filters are enabled.<br>0 = low-pass filters are disabled. |

## I<sup>2</sup>C Baud Rate High and Low Byte Registers

The I<sup>2</sup>C Baud Rate High and Low Byte registers, shown in Tables 74 and 75, combine to form a 16-bit reload value, BRG[15:0], for the I<sup>2</sup>C Baud Rate Generator.

When the  $I^2C$  is disabled, the Baud Rate Generator can function as a basic 16-bit timer with interrupt on time-out. To configure the Baud Rate Generator as a timer with interrupt on time-out, complete the following procedure:

- 1. Disable the  $I^2C$  by clearing the IEN bit in the  $I^2C$  Control Register to 0.

- 2. Load the appropriate 16-bit count value into the I<sup>2</sup>C Baud Rate High and Low Byte registers.

- 3. Enable the Baud Rate Generator timer function and associated interrupt by setting the BIRQ bit in the I<sup>2</sup>C Control Register to 1.

When configured as a general purpose timer, the interrupt interval is calculated using the following equation:

Interrupt Interval (s) = System Clock Period (s)  $\times$  BRG[15:0]

Observe the following procedure to setup the Flash Sector Protect Register from user code:

- 1. Write 00H to the Flash Control Register to reset the Flash Controller.

- 2. Write 5EH to the Flash Control Register to select the Flash Sector Protect Register.

- 3. Read and/or write the Flash Sector Protect Register which is now at Register File address FF9H.

- 4. Write OOH to the Flash Control Register to return the Flash Controller to its reset state.

#### **Flash Write Protection Option Bit**

The Flash Write Protect option bit can be enabled to block all program and erase operations from user code. For more information, see the <u>Option Bits</u> chapter on page 180.

### **Byte Programming**

When the Flash Controller is unlocked, writes to Flash memory from user code will program a byte into the Flash if the address is located in the unlocked page. An erased Flash byte contains all ones (FFH). The programming operation can only be used to change bits from one to zero. To change a Flash bit (or multiple bits) from zero to one requires a Page Erase or Mass Erase operation.

Byte programming can be accomplished using the eZ8 CPU's LDC or LDCI instructions. For a description of the LDC and LDCI instructions, refer to the <u>eZ8 CPU Core User Manual (UM0128)</u>, which is available for download on <u>www.zilog.com</u>.

While the Flash Controller programs Flash memory, the eZ8 CPU idles but the system clock and on-chip peripherals continue to operate. Interrupts that occur when a programming operation is in progress are serviced after the programming operation is complete. To exit programming mode and lock the Flash Controller, write 00H to the Flash Control Register.

User code cannot program Flash memory on a page that resides in a protected sector. When user code writes memory locations, only addresses located in the unlocked page are programmed. Memory writes outside of the unlocked page are ignored.

#### **Caution:** Each memory location must not be programmed more than twice before an erase occurs.

Observe the following procedure to program the Flash from user code:

- 1. Write 00H to the Flash Control Register to reset the Flash Controller.

- 2. Write the page of memory to be programmed to the Page Select Register.

- 3. Write the first unlock command 73H to the Flash Control Register.

For more information about bypassing the Flash Controller, refer to the <u>Third Party Flash</u> <u>Programming Support for Z8 Encore! MCUs Application Note (AN0117)</u>, which is available for download at <u>www.zilog.com</u>.

## Flash Controller Behavior in Debug Mode

The following changes in Flash Controller behavior occur when the Flash Controller is accessed using the On-Chip Debugger:

- The Flash Write Protect option bit is ignored

- The Flash Sector Protect Register is ignored for programming and erase operations

- Programming operations are not limited to the page selected in the Page Select Register

- Bits in the Flash Sector Protect Register can be written to one or zero

- The second write of the Page Select Register to unlock the Flash Controller is not necessary

- The Page Select Register can be written when the Flash Controller is unlocked

- The Mass Erase command is enabled through the Flash Control Register

**Caution:** For security reasons, the Flash Controller allows only a single page to be opened for write/erase operations. When writing multiple Flash pages, the Flash Controller must go through the unlock sequence again to select another page.

## **Flash Control Register Definitions**

This section defines the features of the following Flash Control registers.

Flash Control Register: see page 175

Flash Status Register: see page 177

Page Select Register: see page 177

Flash Sector Protect Register: see page 178

Flash Frequency High and Low Byte Registers: see page 179

## **Flash Control Register**

The Flash Control Register, shown in Table 93, unlocks the Flash Controller for programming and erase operations, or to select the Flash Sector Protect Register.

PRELIMINARY

```

DBG \leftarrow Size[7:0]

DBG \leftarrow 1-256 data bytes

```

**Read Register (09H).** The Read Register command reads data from the Register File. Data can be read 1-256 bytes at a time (256 bytes can be read by setting size to zero). If the device is not in DEBUG Mode or if the Read Protect option bit is enabled, this command returns FFH for all the data values.

```

DBG \leftarrow 09H

DBG \leftarrow {4'h0,Register Address[11:8]

DBG \leftarrow Register Address[7:0]

DBG \leftarrow Size[7:0]

DBG 1-256 data bytes

```

**Write Program Memory (0AH).** The Write Program Memory command writes data to program memory. This command is equivalent to the LDC and LDCI instructions. Data can be written 1-65536 bytes at a time (65536 bytes can be written by setting size to zero). The on-chip Flash Controller must be written to and unlocked for the programming operation to occur. If the Flash Controller is not unlocked, the data is discarded. If the device is not in DEBUG Mode or if the Read Protect option bit is enabled, the data is discarded.

```

DBG \leftarrow 0AH

DBG \leftarrow Program Memory Address[15:8]

DBG \leftarrow Program Memory Address[7:0]

DBG \leftarrow Size[15:8]

DBG \leftarrow Size[7:0]

DBG \leftarrow 1-65536 data bytes

```

**Read Program Memory (0BH).** The Read Program Memory command reads data from program memory. This command is equivalent to the LDC and LDCI instructions. Data can be read 1-65536 bytes at a time (65536 bytes can be read by setting size to zero). If the device is not in DEBUG Mode or if the Read Protect option bit is enabled, this command returns FFH for the data.

```

DBG ← 0BH

DBG ← Program Memory Address[15:8]

DBG ← Program Memory Address[7:0]

DBG ← Size[15:8]

DBG ← Size[7:0]

DBG 1-65536 data bytes

```

Write Data Memory (0CH). The Write Data Memory command writes data to Data Memory. This command is equivalent to the LDE and LDEI instructions. Data can be written 1-65536 bytes at a time (65536 bytes can be written by setting size to zero). If the device is not in DEBUG Mode or if the Read Protect option bit is enabled, the data is discarded.

```

DBG \leftarrow 0CH

DBG \leftarrow Data Memory Address[15:8]

DBG \leftarrow Data Memory Address[7:0]

DBG \leftarrow Size[15:8]

DBG \leftarrow Size[7:0]

DBG \leftarrow 1-65536 data bytes

```

Table 111 list the Flash memory electrical characteristics and timing.

|                                                  |         | <sub>DD</sub> = 3.0–3.<br>–40°C to 1 |         |        |                                                                                                                                                                |

|--------------------------------------------------|---------|--------------------------------------|---------|--------|----------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Parameter                                        | Minimum | Typical                              | Maximum | Units  | Notes                                                                                                                                                          |

| Flash Byte Read Time                             | 50      | _                                    | -       | ns     |                                                                                                                                                                |

| Flash Byte Program<br>Time                       | 20      | _                                    | 40      | μs     |                                                                                                                                                                |

| Flash Page Erase Time                            | 10      | _                                    | -       | ms     |                                                                                                                                                                |

| Flash Mass Erase Time                            | 200     | _                                    | -       | ms     |                                                                                                                                                                |

| Writes to Single<br>Address Before Next<br>Erase | -       | _                                    | 2       |        |                                                                                                                                                                |

| Flash Row Program<br>Time                        | _       | _                                    | 8       | ms     | Cumulative program time for single<br>row cannot exceed limit before next<br>erase. This parameter is only an<br>issue when bypassing the Flash<br>Controller. |

| Data Retention                                   | 100     | _                                    | _       | years  | 25°C                                                                                                                                                           |

| Endurance, –40°C to 105°C                        | 10,000  | -                                    | -       | cycles | Program/erase cycles                                                                                                                                           |

| Endurance, 106°C to 125°C                        | 1,000   | -                                    | -       | cycles | Program/erase cycles                                                                                                                                           |

Table 112 lists the Watchdog Timer electrical characteristics and timing.

|                  |                                                               |         | <sub>DD</sub> = 3.0–3.<br>–40°C to 1 |         |       |            |

|------------------|---------------------------------------------------------------|---------|--------------------------------------|---------|-------|------------|

| Symbol           | Parameter                                                     | Minimum | Typical                              | Maximum | Units | Conditions |

| F <sub>WDT</sub> | WDT Oscillator<br>Frequency                                   | 5       | 10                                   | 20      | kHz   |            |

| I <sub>WDT</sub> | WDT Oscillator Current<br>including internal RC<br>Oscillator | _       | <1                                   | 5       | μA    |            |

213

## **SPI Master Mode Timing**

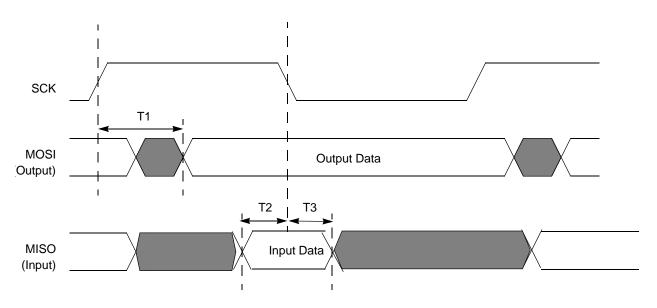

Figure 53 and Table 118 provide timing information for SPI Master Mode pins. Timing is shown with SCK rising edge used to source MOSI output data, SCK falling edge used to sample MISO input data. Timing on the SS output pin(s) is controlled by software.

Figure 53. SPI Master Mode Timing

|                |                                             | Delay | y (ns) |

|----------------|---------------------------------------------|-------|--------|

| Parameter      | Abbreviation                                | Min   | Max    |

| SPI Master     |                                             |       |        |

| T <sub>1</sub> | SCK Rise to MOSI output Valid Delay         | -5    | +5     |

| T <sub>2</sub> | MISO input to SCK (receive edge) Setup Time | 20    |        |

| T <sub>3</sub> | MISO input to SCK (receive edge) Hold Time  | 0     |        |

#### Table 118. SPI Master Mode Timing

## Z8 Encore! XP<sup>®</sup> F64xx Series Product Specification

|   |                         |                          |                              |                                |                            |                               | LC                            | ower Nil                       | oble (He                      | X)                             |                            |                          |                           |                           |                  |                          |

|---|-------------------------|--------------------------|------------------------------|--------------------------------|----------------------------|-------------------------------|-------------------------------|--------------------------------|-------------------------------|--------------------------------|----------------------------|--------------------------|---------------------------|---------------------------|------------------|--------------------------|

| - | 0                       | 1                        | 2                            | 3                              | 4                          | 5                             | 6                             | 7                              | 8                             | 9                              | Α                          | В                        | С                         | D                         | Е                | F                        |

| 0 | 1.2<br>BRK              | 2.2<br>SRP<br>IM         | 2.3<br>ADD<br>r1,r2          | 2.4<br>ADD<br>r1,lr2           | 3.3<br><b>ADD</b><br>R2,R1 | 3.4<br>ADD<br>IR2,R1          | 3.3<br><b>ADD</b><br>R1,IM    | 3.4<br><b>ADD</b><br>IR1,IM    | 4.3<br>ADDX<br>ER2,ER1        | 4.3<br>ADDX<br>IM,ER1          | 2.3<br><b>DJNZ</b><br>r1,X | 2.2<br><b>JR</b><br>cc,X | 2.2<br><b>LD</b><br>r1,IM | 3.2<br><b>JP</b><br>cc,DA | 1.2<br>INC<br>r1 | 1.2<br>NOP               |

| 1 | 2.2<br><b>RLC</b><br>R1 | 2.3<br>RLC<br>IR1        | 2.3<br>ADC<br>r1,r2          | 2.4<br>ADC<br>r1,lr2           | 3.3<br>ADC<br>R2,R1        | 3.4<br>ADC<br>IR2,R1          | 3.3<br>ADC<br>R1,IM           | 3.4<br>ADC<br>IR1,IM           | 4.3<br>ADCX<br>ER2,ER1        | 4.3                            |                            |                          |                           |                           |                  | See 2nd<br>Opcode<br>Map |

| 2 | 2.2<br>INC<br>R1        | 2.3<br>INC<br>IR1        | 2.3<br>SUB<br>r1,r2          | 2.4<br>SUB<br>r1,lr2           | 3.3<br>SUB<br>R2,R1        | 3.4<br>SUB<br>IR2,R1          | 3.3<br>SUB<br>R1,IM           | 3.4<br>SUB<br>IR1,IM           | 4.3<br><b>SUBX</b><br>ER2,ER1 | 4.3<br><b>SUBX</b><br>IM,ER1   |                            |                          |                           |                           |                  | 1,2<br>ATM               |

| 3 | 2.2<br><b>DEC</b><br>R1 | 2.3<br><b>DEC</b><br>IR1 | 2.3<br>SBC<br>r1,r2          | 2.4<br>SBC<br>r1,lr2           | 3.3<br><b>SBC</b><br>R2,R1 | 3.4<br>SBC<br>IR2,R1          | 3.3<br><b>SBC</b><br>R1,IM    | 3.4<br>SBC<br>IR1,IM           | 4.3<br><b>SBCX</b><br>ER2,ER1 | 4.3<br><b>SBCX</b><br>IM,ER1   |                            |                          |                           |                           |                  |                          |

| 4 | 2.2<br><b>DA</b><br>R1  | 2.3<br><b>DA</b><br>IR1  | 2.3<br>OR<br>r1,r2           | 2.4<br>OR<br>r1,lr2            | 3.3<br><b>OR</b><br>R2,R1  | 3.4<br><b>OR</b><br>IR2,R1    | 3.3<br><b>OR</b><br>R1,IM     | 3.4<br><b>OR</b><br>IR1,IM     | 4.3<br><b>ORX</b><br>ER2,ER1  | 4.3<br><b>ORX</b><br>IM,ER1    |                            |                          |                           |                           |                  |                          |