Welcome to **E-XFL.COM**

What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded - Microcontrollers</u>"

| Details                    |                                                           |

|----------------------------|-----------------------------------------------------------|

| Product Status             | Active                                                    |

| Core Processor             | eZ8                                                       |

| Core Size                  | 8-Bit                                                     |

| Speed                      | 20MHz                                                     |

| Connectivity               | I <sup>2</sup> C, IrDA, SPI, UART/USART                   |

| Peripherals                | Brown-out Detect/Reset, DMA, POR, PWM, WDT                |

| Number of I/O              | 31                                                        |

| Program Memory Size        | 32KB (32K x 8)                                            |

| Program Memory Type        | FLASH                                                     |

| EEPROM Size                | -                                                         |

| RAM Size                   | 2K x 8                                                    |

| Voltage - Supply (Vcc/Vdd) | 3V ~ 3.6V                                                 |

| Data Converters            | A/D 8x10b                                                 |

| Oscillator Type            | Internal                                                  |

| Operating Temperature      | -40°C ~ 105°C (TA)                                        |

| Mounting Type              | Surface Mount                                             |

| Package / Case             | 44-LCC (J-Lead)                                           |

| Supplier Device Package    | -                                                         |

| Purchase URL               | https://www.e-xfl.com/product-detail/zilog/z8f3221vn020eg |

# Z8 Encore! XP<sup>®</sup> F64xx Series Product Specification

xiv

| , | Γable 34. | IRQ2 Enable High Bit Register (IRQ2ENH)                               | 58    |

|---|-----------|-----------------------------------------------------------------------|-------|

| , | Γable 35. | IRQ2 Enable Low Bit Register (IRQ2ENL)                                | 59    |

| , | Γable 36. | Interrupt Edge Select Register (IRQES)                                | 60    |

| , | Гable 37. | Interrupt Port Select Register (IRQPS)                                | 60    |

| , | Γable 38. | Interrupt Control Register (IRQCTL)                                   | 61    |

| , | Гable 39. | Timer 0–3 High Byte Register (TxH)                                    | 73    |

| , | Γable 40. | Timer 0–3 Low Byte Register (TxL)                                     | 73    |

| , | Γable 41. | Timer 0–3 Reload High Byte Register (TxRH)                            | 74    |

| , | Гable 42. | Timer 0–3 Reload Low Byte Register (TxRL)                             | 74    |

| , | Гable 43. | Timer 0–3 PWM High Byte Register (TxPWMH)                             | 75    |

| , | Γable 44. | Timer 0–3 PWM Low Byte Register (TxPWML)                              | 75    |

| , | Гable 45. | Timer 0–3 Control 0 Register (TxCTL0)                                 | 76    |

| , | Гable 46. | Timer 0–3 Control 1 Register (TxCTL1)                                 | 77    |

| , | Γable 47. | Watchdog Timer Approximate Time-Out Delays                            | 81    |

| , | Γable 48. | Watchdog Timer Control Register (WDTCTL)                              | 84    |

| , | Гable 49. | Watchdog Timer Events                                                 | 85    |

| , | Γable 50. | Watchdog Timer Reload Upper Byte Register (WDTU)                      | 85    |

| , | Γable 51. | Watchdog Timer Reload High Byte Register (WDTH)                       | 86    |

| , | Γable 52. | Watchdog Timer Reload Low Byte Register (WDTL)                        | 86    |

| , | Γable 53. | UART Transmit Data Register (UxTXD)                                   | 99    |

| , | Γable 54. | UART Receive Data Register (UxRXD)                                    | 99    |

| , | Γable 55. | UART Status 0 Register (UxSTAT0)                                      | . 100 |

| , | Γable 56. | UART Status 1 Register (UxSTAT1)                                      | . 101 |

| , | Γable 57. | UART Control 0 Register (UxCTL0)                                      | . 102 |

| , | Γable 58. | UART Control 1 Register (UxCTL1)                                      | . 103 |

| , | Γable 59. | UART Address Compare Register (UxADDR)                                | . 105 |

| , | Гable 60. | UART Baud Rate High Byte Register (UxBRH)                             | . 106 |

| , | Γable 61. | UART Baud Rate Low Byte Register (UxBRL)                              | . 106 |

| , | Γable 62. | UART Baud Rates                                                       | . 107 |

| , | Гable 63. | SPI Clock Phase (PHASE) and Clock Polarity (CLKPOL) Operation $\ .$ . | . 117 |

| , | Γable 64. | SPI Data Register (SPIDATA)                                           | . 122 |

| , | Γable 65. | SPI Control Register (SPICTL)                                         | . 122 |

| , | Гable 66. | SPI Status Register (SPISTAT)                                         | . 123 |

| , | Гable 67. | SPI Mode Register (SPIMODE)                                           | . 125 |

| , | Гable 68. | SPI Diagnostic State Register (SPIDST)                                | . 126 |

| , | Гable 69. | SPI Baud Rate High Byte Register (SPIBRH)                             | . 127 |

# Z8 Encore! XP<sup>®</sup> F64xx Series Product Specification

XX

| Table 249. | Port A–H GPIO Address Registers (PxADDR)         | 279 |

|------------|--------------------------------------------------|-----|

| Table 250. | Port A-H Control Registers (PxCTL)               | 279 |

| Table 251. | Port A–H Input Data Registers (PxIN)             | 279 |

| Table 252. | Port A–H Output Data Register (PxOUT)            | 280 |

| Table 253. | Port A-H GPIO Address Registers (PxADDR)         | 280 |

| Table 254. | Port A–H Control Registers (PxCTL)               | 280 |

| Table 255. | Port A–H Input Data Registers (PxIN)             | 280 |

| Table 256. | Port A–H Output Data Register (PxOUT)            | 281 |

| Table 257. | Port A-H GPIO Address Registers (PxADDR)         | 281 |

| Table 258. | Port A-H Control Registers (PxCTL)               | 281 |

| Table 259. | Port A–H Input Data Registers (PxIN)             | 281 |

| Table 260. | Port A–H Output Data Register (PxOUT)            | 282 |

| Table 261. | Watchdog Timer Control Register (WDTCTL)         | 282 |

| Table 262. | Watchdog Timer Reload Upper Byte Register (WDTU) | 282 |

| Table 263. | Watchdog Timer Reload High Byte Register (WDTH)  | 283 |

| Table 264. | Watchdog Timer Reload Low Byte Register (WDTL)   | 283 |

| Table 265. | Flash Control Register (FCTL)                    | 284 |

| Table 266. | Flash Status Register (FSTAT)                    | 284 |

| Table 267. | Page Select Register (FPS)                       | 284 |

| Table 268. | Flash Frequency High Byte Register (FFREQH)      | 285 |

| Table 269. | Flash Frequency Low Byte Register (FFREQL)       | 285 |

| Table 270. | Flash Sector Protect Register (FPROT)            | 285 |

| Table 271  | 78 Encore! XP F64xx Series Ordering Matrix       | 287 |

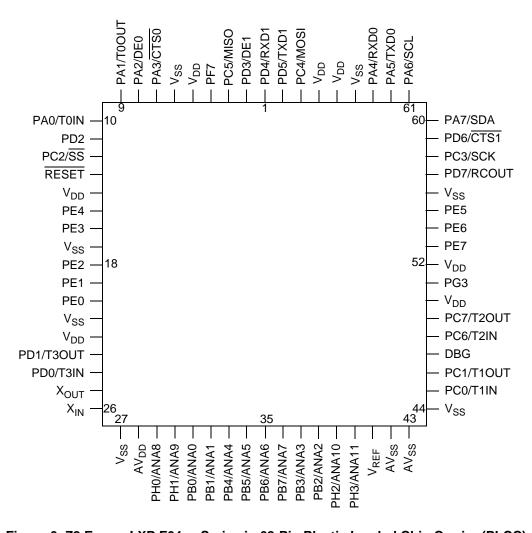

Figure 6. Z8 Encore! XP F64xx Series in 68-Pin Plastic Leaded Chip Carrier (PLCC)

Table 5. Z8 Encore! XP F64xx Series Program Memory Maps (Continued)

| Program Memory Address (Hex)                                               | Function                 |  |  |  |

|----------------------------------------------------------------------------|--------------------------|--|--|--|

| 0006-0007                                                                  | Illegal Instruction Trap |  |  |  |

| 0008-0037                                                                  | Interrupt Vectors*       |  |  |  |

| 0038-BFFF                                                                  | Program Memory           |  |  |  |

| Z8F642x Products                                                           |                          |  |  |  |

| 0000-0001                                                                  | Option Bits              |  |  |  |

| 0002-0003                                                                  | Reset Vector             |  |  |  |

| 0004-0005                                                                  | WDT Interrupt Vector     |  |  |  |

| 0006-0007                                                                  | Illegal Instruction Trap |  |  |  |

| 0008-0037                                                                  | Interrupt Vectors*       |  |  |  |

| 0038-FFFF                                                                  | Program Memory           |  |  |  |

| Note: *See <u>Table 23</u> on page 48 for a list of the interrupt vectors. |                          |  |  |  |

## **Data Memory**

The Z8 Encore! XP F64xx Series does not use the eZ8 CPU's 64KB data memory address space.

## **Information Area**

Table 6 describes the Z8 Encore! XP F64xx Series' Information Area. This 512-byte Information Area is accessed by setting bit 7 of the Page Select Register to 1. When access is enabled, the Information Area is mapped into program memory and overlays the 512 bytes at addresses FE00H to FFFFH. When the Information Area access is enabled, execution of the LDC and LDCI instructions from these program memory addresses return the Information Area data rather than the program memory data. Reads of these addresses through the On-Chip Debugger also returns the Information Area data. Execution of code from these addresses continues to correctly use program memory. Access to the Information Area is read-only.

## Reset and Stop Mode Recovery

The Reset Controller within the Z8 Encore! XP F64xx Series controls Reset and Stop Mode Recovery operation. In typical operation, the following events cause a Reset to occur:

- Power-On Reset

- Voltage Brown-Out

- Watchdog Timer time-out (when configured via the WDT\_RES option bit to initiate a Reset)

- External RESET pin assertion

- On-Chip Debugger initiated Reset (OCDCTL[0] set to 1)

When the Z8 Encore! XP F64xx Series devices are in STOP Mode, a Stop Mode Recovery is initiated by either of the following events:

- Watchdog Timer time-out

- GPIO port input pin transition on an enabled Stop Mode Recovery source

- DBG pin driven Low

## **Reset Types**

The Z8 Encore! XP F64xx Series provides two different types of reset operation (system reset and Stop Mode Recovery). The type of Reset is a function of both the current operating mode of the Z8 Encore! XP F64xx Series devices and the source of the Reset. Table 8 lists the types of Reset and their operating characteristics.

Table 8. Reset and Stop Mode Recovery Characteristics and Latency

|                       | Reset Characteristics and Latency   |         |                                                   |  |  |  |

|-----------------------|-------------------------------------|---------|---------------------------------------------------|--|--|--|

| Reset Type            | Control Registers                   | eZ8 CPU | Reset Latency (Delay)                             |  |  |  |

| System reset          | Reset (as applicable)               | Reset   | 66 WDT Oscillator cycles + 16 System Clock cycles |  |  |  |

| Stop Mode<br>Recovery | Unaffected, except WDT_CTL Register | Reset   | 66 WDT Oscillator cycles + 16 System Clock cycles |  |  |  |

• Writing a 1 to the IRQE bit in the Interrupt Control Register

Interrupts are globally disabled by any of the following operations:

- Execution of a Disable Interrupt (DI) instruction

- eZ8 CPU acknowledgement of an interrupt service request from the interrupt controller

- Writing a 0 to the IRQE bit in the Interrupt Control Register

- Reset

- Executing a trap instruction

- Illegal instruction trap

## **Interrupt Vectors and Priority**

The interrupt controller supports three levels of interrupt priority. Level 3 is the highest priority, Level 2 is the second highest priority, and Level 1 is the lowest priority. If all of the interrupts were enabled with identical interrupt priority (all as Level 2 interrupts, for example), then the interrupt priority would be assigned from highest to lowest, as specified in Table 23. Level 3 interrupts always have higher priority than Level 2 interrupts which, in turn, always have higher priority than Level 1 interrupts. Within each interrupt priority level (Level 1, Level 2, or Level 3), priority is assigned as specified in Table 23. Resets, Watchdog Timer interrupts (if enabled), and illegal instruction traps always have highest priority.

## **Interrupt Assertion**

Interrupt sources assert their interrupt requests for only a single system clock period (single pulse). When the interrupt request is acknowledged by the eZ8 CPU, the corresponding bit in the Interrupt Request Register is cleared until the next interrupt occurs. Writing a 0 to the corresponding bit in the Interrupt Request Register likewise clears the interrupt request.

**Caution:** Zilog recommends not using a coding style that clears bits in the Interrupt Request registers. All incoming interrupts received between execution of the first LDX command and the final LDX command are lost. See Example 1, which follows.

**Example 1.** A poor coding style that can result in lost interrupt requests:

```

LDX r0, IRQ0

AND r0, MASK

LDX IRQ0, r0

```

Table 39. Timer 0-3 High Byte Register (TxH)

| Bit     | 7                      | 6 | 5 | 4 | 3 | 2 | 1 | 0 |

|---------|------------------------|---|---|---|---|---|---|---|

| Field   |                        |   |   | Т | Н |   |   |   |

| RESET   | 0                      |   |   |   |   |   |   |   |

| R/W     | R/W                    |   |   |   |   |   |   |   |

| Address | F00H, F08H, F10H, F18H |   |   |   |   |   |   |   |

### Table 40. Timer 0-3 Low Byte Register (TxL)

| Bit     | 7                      | 6 | 5 | 4 | 3 | 2 | 1 | 0 |

|---------|------------------------|---|---|---|---|---|---|---|

| Field   | TL                     |   |   |   |   |   |   |   |

| RESET   | 0 1                    |   |   |   |   |   |   |   |

| R/W     | R/W                    |   |   |   |   |   |   |   |

| Address | F01H, F09H, F11H, F19H |   |   |   |   |   |   |   |

| Bit    | Description                                                                          |

|--------|--------------------------------------------------------------------------------------|

| [7:0]  | Timer High and Low Bytes                                                             |

| TH, TL | These 2 bytes, {TMRH[7:0], TMRL[7:0]}, contain the current 16-bit timer count value. |

| Bit | Description                 |

|-----|-----------------------------|

| [7] | Timer Enable                |

| TEN | 0 = Timer is disabled.      |

|     | 1 = Timer enabled to count. |

| [6] | Timer Input/Output Polarity |

TPOL Operation of this bit is a function of the current operating mode of the timer.

#### **ONE-SHOT Mode**

When the timer is disabled, the timer output signal is set to the value of this bit. When the timer is enabled, the timer output signal is complemented upon timer reload.

#### **CONTINUOUS Mode**

When the timer is disabled, the timer output signal is set to the value of this bit. When the timer is enabled, the timer output signal is complemented upon timer reload.

#### **COUNTER Mode**

When the timer is disabled, the timer output signal is set to the value of this bit. When the timer is enabled, the timer output signal is complemented upon timer reload.

- 0 = Count occurs on the rising edge of the timer input signal.

- 1 = Count occurs on the falling edge of the timer input signal.

#### **PWM Mode**

- 0 = timer output is forced Low (0) when the timer is disabled. When enabled, the timer output is forced High (1) upon PWM count match and forced Low (0) upon reload.

- 1 = timer output is forced High (1) when the timer is disabled. When enabled, the timer output is forced Low (0) upon PWM count match and forced High (1) upon reload.

#### **CAPTURE Mode**

- 0 = Count is captured on the rising edge of the timer input signal.

- 1 = Count is captured on the falling edge of the timer input signal.

#### **COMPARE Mode**

When the timer is disabled, the timer output signal is set to the value of this bit. When the timer is enabled, the timer output signal is complemented upon timer reload.

#### **GATED Mode**

- 0 = Timer counts when the timer input signal is High (1) and interrupts are generated on the falling edge of the timer input.

- 1 = Timer counts when the timer input signal is Low (0) and interrupts are generated on the rising edge of the timer input.

#### **CAPTURE/COMPARE Mode**

- 0 = Counting is started on the first rising edge of the timer input signal. The current count is captured on subsequent rising edges of the timer input signal.

- 1 = Counting is started on the first falling edge of the timer input signal. The current count is captured on subsequent falling edges of the timer input signal.

Caution: When the timer output alternate function TxOUT on a GPIO port pin is enabled, TxOUT will change to whatever state the TPOL bit is in. The timer does not need to be enabled for that to happen. Also, the Port Data Direction Subregister is not needed to be set to output on TxOUT. Changing the TPOL bit with the timer enabled and running does not immediately change the TxOUT.

- 5. After the first bit has been shifted out, a transmit interrupt is asserted.

- 6. Software responds by writing the lower eight bits of address to the I<sup>2</sup>C Data Register.

- 7. The  $I^2C$  Controller completes shifting of the two address bits and a 0 (write).

- 8. If the I<sup>2</sup>C slave acknowledges the first address byte by pulling the SDA signal Low during the next High period of SCL, the I<sup>2</sup>C Controller sets the ACK bit in the I<sup>2</sup>C Status Register. Continue with <u>Step 9</u>.

If the slave does not acknowledge the first address byte, the I<sup>2</sup>C Controller sets the NCKI bit and clears the ACK bit in the I<sup>2</sup>C Status Register. Software responds to the Not Acknowledge interrupt by setting the stop and flush bits and clearing the TXI bit. The I<sup>2</sup>C Controller sends the stop condition on the bus and clears the stop and NCKI bits. The transaction is complete (ignore following steps).

- 9. The I<sup>2</sup>C Controller loads the I<sup>2</sup>C Shift Register with the contents of the I<sup>2</sup>C Data Register (second address byte).

- 10. The I<sup>2</sup>C Controller shifts out the second address byte. After the first bit is shifted, the I<sup>2</sup>C Controller generates a transmit interrupt.

- 11. Software responds by setting the start bit of the I<sup>2</sup>C Control Register to generate a repeated start by clearing the TXI bit.

- 12. Software responds by writing 11110B followed by the 2-bit slave address and a 1 (read) to the I<sup>2</sup>C Data Register.

- 13. If only one byte is to be read, software sets the NAK bit of the I<sup>2</sup>C Control Register.

- 14. After the I<sup>2</sup>C Controller shifts out the 2nd address byte, the I<sup>2</sup>C slave sends an acknowledge by pulling the SDA signal Low during the next High period of SCL, the I<sup>2</sup>C Controller sets the ACK bit in the I<sup>2</sup>C Status Register. Continue with Step 15.

If the slave does not acknowledge the second address byte, the  $I^2C$  Controller sets the NCKI bit and clears the ACK bit in the  $I^2C$  Status Register. Software responds to the Not Acknowledge interrupt by setting the stop and flush bits and clearing the TXI bit. The  $I^2C$  Controller sends the stop condition on the bus and clears the stop and NCKI bits. The transaction is complete (ignore the following steps).

- 15. The I<sup>2</sup>C Controller sends the repeated start condition.

- 16. The I<sup>2</sup>C Controller loads the I<sup>2</sup>C Shift Register with the contents of the I<sup>2</sup>C Data Register (third address transfer).

- 17. The I<sup>2</sup>C Controller sends 11110B followed by the two most significant bits of the slave read address and a 1 (read).

- 18. The I<sup>2</sup>C slave sends an acknowledge by pulling the SDA signal Low during the next High period of SCL

| Bit          | Description (Continued)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

|--------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| [3]<br>WSEL  | <ul> <li>Word Select</li> <li>0 = DMAx transfers a single byte per request.</li> <li>1 = DMAx transfers a two-byte word per request. The address for the on-chip peripheral control register must be an even address.</li> </ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

| [2:0]<br>RSS | Request Trigger Source Select The Request Trigger Source Select field determines the peripheral that can initiate a DMA transfer. The corresponding interrupts do not need to be enabled within the Interrupt Controller to initiate a DMA transfer. However, if the Request Trigger Source can enable or disable the interrupt request sent to the Interrupt Controller, the interrupt request must be enabled within the Request Trigger Source block.  000 = Timer 0.  001 = Timer 1.  010 = Timer 2.  011 = Timer 3.  100 = DMA0 Control Register: UARTO Received Data Register contains valid data. DMA1 Control Register: UARTO Transmit Data Register empty.  101 = DMA0 Control Register: UART1 Received Data Register contains valid data. DMA1 Control Register: UART1 Transmit Data Register empty.  110 = DMA0 Control Register: I <sup>2</sup> C Receiver Interrupt. DMA1 Control Register: I <sup>2</sup> C Transmitter Interrupt Register empty. |

## DMAx I/O Address Register

The DMAx I/O Address Register, shown in Table 79, contains the low byte of the on-chip peripheral address for data transfer. The full 12-bit Register File address is provided by {FH, DMAx\_IO[7:0]}. When the DMA is configured for two-byte word transfers, the DMAx I/O Address Register must contain an even-numbered address.

Table 79. DMAx I/O Address Register (DMAxIO)

| Bit     | 7          | 6 | 5 | 4 | 3 | 2 | 1 | 0 |

|---------|------------|---|---|---|---|---|---|---|

| Field   | DMA_IO     |   |   |   |   |   |   |   |

| RESET   | X          |   |   |   |   |   |   |   |

| R/W     | R/W        |   |   |   |   |   |   |   |

| Address | FB1H, FB9H |   |   |   |   |   |   |   |

| Bit    | Description                                                                                     |

|--------|-------------------------------------------------------------------------------------------------|

| [7:0]  | DMA On-Chip Peripheral Control Register Address                                                 |

| DMA_IO | This byte sets the low byte of the on-chip peripheral control register address on Register File |

|        | Page FH (addresses F00H to FFFH).                                                               |

Table 84. DMA\_ADC Address Register (DMAA\_ADDR)

| Bit     | 7 | 6                  | 5 | 4  | 3  | 2 | 1 | 0 |  |  |  |  |

|---------|---|--------------------|---|----|----|---|---|---|--|--|--|--|

| Field   |   | DMAA_ADDR Reserved |   |    |    |   |   |   |  |  |  |  |

| RESET   |   |                    |   | >  | <  |   |   |   |  |  |  |  |

| R/W     |   | R/W                |   |    |    |   |   |   |  |  |  |  |

| Address |   |                    |   | FB | DH |   |   |   |  |  |  |  |

| Bit                | Description                                                                                                                                                                                                                                                                                                                 |

|--------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| [7:1]<br>DMAA_ADDR | DMA_ADC Address These bits specify the seven most significant bits of the 12-bit Register File addresses used for storing the ADC output data. The ADC analog input Number defines the five least significant bits of the Register File address. Full 12-bit address is {DMAA_ADDR[7:1], 4-bit ADC analog input Number, 0}. |

| 0                  | Reserved This bit is reserved and must be programmed to 0.                                                                                                                                                                                                                                                                  |

## **DMA\_ADC** Control Register

The DMA\_ADC Control Register, shown in Table 85, enables and sets options (DMA enable and interrupt enable) for ADC operation.

Table 85. DMA\_ADC Control Register (DMAACTL)

| Bit     | 7    | 6     | 5               | 4  | 3  | 2 | 1 | 0 |  |  |  |

|---------|------|-------|-----------------|----|----|---|---|---|--|--|--|

| Field   | DAEN | IRQEN | Reserved ADC_IN |    |    |   |   |   |  |  |  |

| RESET   |      | 0     |                 |    |    |   |   |   |  |  |  |

| R/W     |      | R/W   |                 |    |    |   |   |   |  |  |  |

| Address |      |       |                 | FB | EH |   |   |   |  |  |  |

| Bit          | Description                                                                                                                                                                               |

|--------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| [7]<br>DAEN  | DMA_ADC Enable  0 = DMA_ADC is disabled and the ADC analog input Number (ADC_IN) is reset to 0.  1 = DMA_ADC is enabled.                                                                  |

| [6]<br>IRQEN | Interrupt Enable  0 = DMA_ADC does not generate any interrupts.  1 = DMA_ADC generates an interrupt after transferring data from the last ADC analog input specified by the ADC_IN field. |

## Flash Memory Address 0000H

Table 99. Flash Option Bits At Flash Memory Address 0000H

| Bit       | 7                                               | 6                    | 5     | 4        | 3      | 2  | 1        | 0   |  |  |  |  |

|-----------|-------------------------------------------------|----------------------|-------|----------|--------|----|----------|-----|--|--|--|--|

| Field     | WDT_RES                                         | WDT_AO               | OSC_S | SEL[1:0] | VBO_AO | RP | Reserved | FWP |  |  |  |  |

| RESET     |                                                 | U                    |       |          |        |    |          |     |  |  |  |  |

| R/W       |                                                 |                      |       | RΛ       | V      |    |          |     |  |  |  |  |

| Address   |                                                 | Program Memory 0000H |       |          |        |    |          |     |  |  |  |  |

| Note: U = | Note: U = Unchanged by Reset; R/W = Read/Write. |                      |       |          |        |    |          |     |  |  |  |  |

| Bit                   | Description                                                                                                                                                                                                                                                                                                                                                                                                                                   |

|-----------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| [7]<br>WDT_RES        | Watchdog Timer Reset  0 = Watchdog Timer time-out generates an interrupt request. Interrupts must be globally enabled for the eZ8 CPU to acknowledge the interrupt request.  1 = Watchdog Timer time-out causes a Short Reset. This setting is the default for unprogrammed (erased) Flash.                                                                                                                                                   |

| [6]<br>WDT_AO         | Watchdog Timer Always On  0 = Watchdog Timer is automatically enabled upon application of system power. Watchdog Timer can not be disabled except during STOP Mode (if configured to power down during STOP Mode).  1 = Watchdog Timer is enabled upon execution of the WDT instruction. Once enabled, the Watchdog Timer can only be disabled by a Reset or Stop Mode Recovery. This setting is the default for unprogrammed (erased) Flash. |

| [5:4]<br>OSC_SEL[1:0] | Oscillator Mode Selection  00 = On-chip oscillator configured for use with external RC networks (<4MHz).  01 = Minimum power for use with very low frequency crystals (32kHz to 1.0MHz).  10 = Medium power for use with medium frequency crystals or ceramic resonators (0.5MHz to 10.0MHz).  11 = Maximum power for use with high frequency crystals (8.0MHz to 20.0MHz). This setting is the default for unprogrammed (erased) Flash.      |

| [3]<br>VBO_AO         | <ul> <li>Voltage Brown-Out Protection Always On</li> <li>0 = Voltage Brown-Out Protection is disabled in STOP Mode to reduce total power consumption.</li> <li>1 = Voltage Brown-Out Protection is always enabled including during STOP Mode. This setting is the default for unprogrammed (erased) Flash.</li> </ul>                                                                                                                         |

| [2]<br>RP             | Read Protect  0 = User program code is inaccessible. Limited control features are available through the On-Chip Debugger.  1 = User program code is accessible. All On-Chip Debugger commands are enabled. This setting is the default for unprogrammed (erased) Flash.                                                                                                                                                                       |

| Bit | Description (Continued)                                                                                                                                                                                                                    |

|-----|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| [1] | Reserved                                                                                                                                                                                                                                   |

|     | This bit is reserved and must be programmed to 0.                                                                                                                                                                                          |

| [0] | Flash Write Protect (Flash version only)                                                                                                                                                                                                   |

| FWP | <ul> <li>0 = Programming, Page Erase, and Mass Erase through User Code is disabled. Mass Erase is available through the On-Chip Debugger.</li> <li>1 = Programming, and Page Erase are enabled for all of Flash program memory.</li> </ul> |

## Flash Memory Address 0001H

Table 100. Options Bits at Flash Memory Address 0001H

| Bit       | 7                                               | 6                    | 5 | 4  | 3 | 2 | 1 | 0 |  |  |  |  |

|-----------|-------------------------------------------------|----------------------|---|----|---|---|---|---|--|--|--|--|

| Field     |                                                 | Reserved             |   |    |   |   |   |   |  |  |  |  |

| RESET     |                                                 | U                    |   |    |   |   |   |   |  |  |  |  |

| R/W       |                                                 |                      |   | R/ | W |   |   |   |  |  |  |  |

| Address   |                                                 | Program Memory 0001H |   |    |   |   |   |   |  |  |  |  |

| Note: U = | Note: U = Unchanged by Reset. R/W = Read/Write. |                      |   |    |   |   |   |   |  |  |  |  |

| Bit   | Description                                                                                     |

|-------|-------------------------------------------------------------------------------------------------|

| [7:0] | Reserved                                                                                        |

|       | These option bits are reserved for future use and must always be 1. This setting is the default |

|       | for unprogrammed (erased) Flash.                                                                |

## **Operation**

The following section describes the operation of the OCD.

#### **OCD** Interface

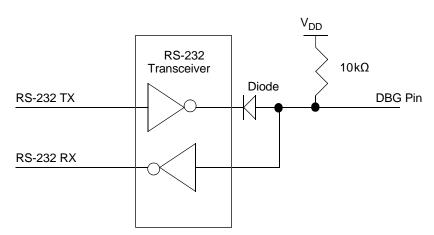

The On-Chip Debugger uses the DBG pin for communication with an external host. This one-pin interface is a bidirectional open-drain interface that transmits and receives data. Data transmission is half-duplex, meaning that transmit and receive operations cannot occur simultaneously. The serial data on the DBG pin is sent using the standard asynchronous data format defined in RS-232. This pin can interface the Z8 Encore! XP F64xx Series products to the serial port of a host PC using minimal external hardware. Two different methods for connecting the DBG pin to an RS-232 interface are depicted in Figures 37 and 38.

**Caution:** For proper operation of the On-Chip Debugger, all power pins (V<sub>DD</sub> and AV<sub>DD</sub>) must be supplied with power, and all ground pins (V<sub>SS</sub> and AV<sub>SS</sub>) must be properly grounded. The DBG pin is open-drain and must always be connected to V<sub>DD</sub> through an external pull-up resistor to ensure proper operation.

Figure 37. Interfacing the On-Chip Debugger's DBG Pin with an RS-232 Interface, #1 of 2

**Hex Address: F19**

Table 163. Timer 0-3 Low Byte Register (TxL)

| Bit     | 7   | 6 | 5 | 4           | 3          | 2 | 1 | 0 |  |  |  |  |

|---------|-----|---|---|-------------|------------|---|---|---|--|--|--|--|

| Field   | TL  |   |   |             |            |   |   |   |  |  |  |  |

| RESET   | 0 1 |   |   |             |            |   |   |   |  |  |  |  |

| R/W     | R/W |   |   |             |            |   |   |   |  |  |  |  |

| Address |     |   | F | F01H, F09H, | F11H, F19H | 1 |   |   |  |  |  |  |

**Hex Address: F1A**

Table 164. Timer 0–3 Reload High Byte Register (TxRH)

| Bit     | 7 | 6   | 5 | 4          | 3         | 2 | 1 | 0 |  |  |  |  |

|---------|---|-----|---|------------|-----------|---|---|---|--|--|--|--|

| Field   |   | TRH |   |            |           |   |   |   |  |  |  |  |

| RESET   |   | 1   |   |            |           |   |   |   |  |  |  |  |

| R/W     |   | R/W |   |            |           |   |   |   |  |  |  |  |

| Address |   |     | F | 02H, F0AH, | F12H, F1A | Н |   |   |  |  |  |  |

**Hex Address: F1B**

Table 165. Timer 0-3 Reload Low Byte Register (TxRL)

| Bit     | 7 | 6   | 5 | 4          | 3         | 2 | 1 | 0 |  |  |  |  |

|---------|---|-----|---|------------|-----------|---|---|---|--|--|--|--|

| Field   |   | TRL |   |            |           |   |   |   |  |  |  |  |

| RESET   |   | 1   |   |            |           |   |   |   |  |  |  |  |

| R/W     |   | R/W |   |            |           |   |   |   |  |  |  |  |

| Address |   |     | F | 03H, F0BH, | F13H, F1B | Н |   |   |  |  |  |  |

**Hex Address: F1C**

Table 166. Timer 0-3 PWM High Byte Register (TxPWMH)

| Bit     | 7                      | 6    | 5 | 4 | 3 | 2 | 1 | 0 |  |

|---------|------------------------|------|---|---|---|---|---|---|--|

| Field   |                        | PWMH |   |   |   |   |   |   |  |

| RESET   |                        | 0    |   |   |   |   |   |   |  |

| R/W     |                        | R/W  |   |   |   |   |   |   |  |

| Address | F04H, F0CH, F14H, F1CH |      |   |   |   |   |   |   |  |

**Hex Address: F4A**

Table 182. UART Control 0 Register (UxCTL0)

| Bit     | 7   | 6   | 5    | 4       | 3       | 2    | 1    | 0    |  |  |

|---------|-----|-----|------|---------|---------|------|------|------|--|--|

| Field   | TEN | REN | CTSE | PEN     | PSEL    | SBRK | STOP | LBEN |  |  |

| RESET   |     | 0   |      |         |         |      |      |      |  |  |

| R/W     |     |     |      | R/      | W       |      |      |      |  |  |

| Address |     |     |      | F42H ar | nd F4AH |      |      |      |  |  |

**Hex Address: F4B**

Table 183. UART Control 1 Register (UxCTL1)

| Bit     | 7       | 6    | 5       | 4       | 3       | 2             | 1      | 0    |  |  |  |  |  |  |

|---------|---------|------|---------|---------|---------|---------------|--------|------|--|--|--|--|--|--|

| Field   | MPMD[1] | MPEN | MPMD[0] | MPBT    | DEPOL   | BRGCTL        | RDAIRQ | IREN |  |  |  |  |  |  |

| RESET   |         | 0    |         |         |         |               |        |      |  |  |  |  |  |  |

| R/W     |         |      |         | R/      | W       |               |        |      |  |  |  |  |  |  |

| Address |         |      |         | F43H ar | nd F4BH | F43H and F4BH |        |      |  |  |  |  |  |  |

**Hex Address: F4C**

Table 184. UART Status 1 Register (UxSTAT1)

| Bit     | 7 | 6                   | 5 | 4       | 3       | 2 | 1 | 0 |  |  |

|---------|---|---------------------|---|---------|---------|---|---|---|--|--|

| Field   |   | Reserved NEWFRM MPR |   |         |         |   |   |   |  |  |

| RESET   |   | 0                   |   |         |         |   |   |   |  |  |

| R/W     |   | R R/W R             |   |         |         |   |   |   |  |  |

| Address |   |                     |   | F44H ar | nd F4CH |   |   |   |  |  |

**Hex Address: F4D**

Table 185. UART Address Compare Register (UxADDR)

| Bit     | 7 | 6         | 5 | 4       | 3       | 2 | 1             | 0 |  |  |  |  |  |  |  |

|---------|---|-----------|---|---------|---------|---|---------------|---|--|--|--|--|--|--|--|

| Field   |   | COMP_ADDR |   |         |         |   |               |   |  |  |  |  |  |  |  |

| RESET   |   | 0         |   |         |         |   |               |   |  |  |  |  |  |  |  |

| R/W     |   |           |   | R/      | W       |   |               |   |  |  |  |  |  |  |  |

| Address |   |           |   | F45H ar | nd F4DH |   | F45H and F4DH |   |  |  |  |  |  |  |  |

**Hex Address: F51**

Table 189. I<sup>2</sup>C Status Register (I2CSTAT)

| Bit     | 7    | 6    | 5   | 4   | 3  | 2   | 1   | 0    |  |

|---------|------|------|-----|-----|----|-----|-----|------|--|

| Field   | TDRE | RDRF | ACK | 10B | RD | TAS | DSS | NCKI |  |

| RESET   | 1    |      | 0   |     |    |     |     |      |  |

| R/W     |      |      | R   |     |    |     |     |      |  |

| Address |      | F51H |     |     |    |     |     |      |  |

**Hex Address: F52**

Table 190. I<sup>2</sup>C Control Register (I2CCTL)

| Bit     | 7   | 6     | 5    | 4    | 3   | 2    | 1     | 0      |  |  |

|---------|-----|-------|------|------|-----|------|-------|--------|--|--|

| Field   | IEN | START | STOP | BIRQ | TXI | NAK  | FLUSH | FILTEN |  |  |

| RESET   |     | 0     |      |      |     |      |       |        |  |  |

| R/W     | R/W | R/W1  | R/W1 | R/W  | R/W | R/W1 | W1    | R/W    |  |  |

| Address |     | F52H  |      |      |     |      |       |        |  |  |

**Hex Address: F53**

Table 191. I<sup>2</sup>C Baud Rate High Byte Register (I2CBRH)

| Bit     | 7 | 6   | 5 | 4  | 3  | 2 | 1 | 0 |

|---------|---|-----|---|----|----|---|---|---|

| Field   |   |     |   | BF | RH |   |   |   |

| RESET   |   | FFH |   |    |    |   |   |   |

| R/W     |   |     |   | R/ | W  |   |   |   |

| Address |   |     |   | F5 | 3H |   |   |   |

**Hex Address: F54**

Table 192. I<sup>2</sup>C Baud Rate Low Byte Register (I2CBRL)

| Bit     | 7 | 6    | 5 | 4  | 3  | 2 | 1 | 0 |  |

|---------|---|------|---|----|----|---|---|---|--|

| Field   |   |      |   | BF | ₹L |   |   |   |  |

| RESET   |   | FFH  |   |    |    |   |   |   |  |

| R/W     |   |      |   | R/ | W  |   |   |   |  |

| Address |   | F54H |   |    |    |   |   |   |  |

**Hex Address: F55**

Table 193. I<sup>2</sup>C Diagnostic State Register (I2CDST)

| Bit     | 7     | 6     | 5      | 5 4 3 2 1 0   |   |  |  |  |

|---------|-------|-------|--------|---------------|---|--|--|--|

| Field   | SCLIN | SDAIN | STPCNT | CNT TXRXSTATE |   |  |  |  |

| RESET   | X 0   |       |        |               |   |  |  |  |

| R/W     |       |       |        | F             | ₹ |  |  |  |

| Address |       | F55H  |        |               |   |  |  |  |

**Hex Address: F56**

Table 194. I<sup>2</sup>C Diagnostic Control Register (I2CDIAG)

| Bit     | 7 | 6    | 5 | 4        | 3 | 2 | 1 | 0    |  |  |

|---------|---|------|---|----------|---|---|---|------|--|--|

| Field   |   |      |   | Reserved |   |   |   | DIAG |  |  |

| RESET   |   | 0    |   |          |   |   |   |      |  |  |

| R/W     |   | R    |   |          |   |   |   |      |  |  |

| Address |   | F56H |   |          |   |   |   |      |  |  |

Hex Addresses: F57-F5F

This address range is reserved.

## **Serial Peripheral Interface**

For more information about these SPI Control registers, see the <u>SPI Control Register Definitions</u> section on page 121.

**Hex Address: F60**

Table 195. SPI Data Register (SPIDATA)

| Bit     | 7 | 6 | 5 | 4  | 3  | 2 | 1 | 0 |  |

|---------|---|---|---|----|----|---|---|---|--|

| Field   |   |   |   | DA | TA |   |   |   |  |

| RESET   |   | X |   |    |    |   |   |   |  |

| R/W     |   |   |   | R/ | W  |   |   |   |  |

| Address |   |   |   | F6 | 0H |   |   |   |  |

**Table 268. Flash Sector Protect Register (FPROT)**

| Bit                                                                                                      | 7     | 6     | 5     | 4     | 3     | 2     | 1     | 0     |

|----------------------------------------------------------------------------------------------------------|-------|-------|-------|-------|-------|-------|-------|-------|

| Field                                                                                                    | SECT7 | SECT6 | SECT5 | SECT4 | SECT3 | SECT2 | SECT1 | SECT0 |

| RESET                                                                                                    | 0     |       |       |       |       |       |       |       |

| R/W                                                                                                      | R/W*  |       |       |       |       |       |       |       |

| Address                                                                                                  | FF9H  |       |       |       |       |       |       |       |

| Note: *R/W = This register is accessible for read operations; it can be written to 1 only via user code. |       |       |       |       |       |       |       |       |

**Hex Address: FFA**

Table 269. Flash Frequency High Byte Register (FFREQH)

| Bit     | 7      | 6 | 5 | 4 | 3 | 2 | 1 | 0 |

|---------|--------|---|---|---|---|---|---|---|

| Field   | FFREQH |   |   |   |   |   |   |   |

| RESET   | 0      |   |   |   |   |   |   |   |

| R/W     | R/W    |   |   |   |   |   |   |   |

| Address | FFAH   |   |   |   |   |   |   |   |

**Hex Address: FFB**

Table 270. Flash Frequency Low Byte Register (FFREQL)

| Bit     | 7      | 6 | 5 | 4 | 3 | 2 | 1 | 0 |

|---------|--------|---|---|---|---|---|---|---|

| Field   | FFREQL |   |   |   |   |   |   |   |

| RESET   | 0      |   |   |   |   |   |   |   |

| R/W     | R/W    |   |   |   |   |   |   |   |

| Address | FFBH   |   |   |   |   |   |   |   |

**Hex Addresses: FFC-FFF**

Refer to the <u>eZ8 CPU Core User Manual (UM0128)</u>

| SPIBRL register 128, 266                                                        | continuous mode 65, 79                          |

|---------------------------------------------------------------------------------|-------------------------------------------------|

| SPICTL register 123, 265                                                        | counter mode 66                                 |

| SPIDATA register 123, 264                                                       | counter modes 79                                |

| SPIMODE register 126, 265                                                       | gated mode 71, 79                               |

| SPISTAT register 124, 265                                                       | one-shot mode 64, 79                            |

| SRA 235                                                                         | operating mode 64                               |

| src 229                                                                         | PWM mode 67, 79                                 |

| SRL 235                                                                         | reading the timer count values 72               |

| SRP 233                                                                         | reload high and low byte registers 75           |

| stack pointer 229                                                               | timer control register definitions 73           |

| status register, I2C 143                                                        | timer output signal operation 73                |

| STOP 233                                                                        | timers 0-3                                      |

| STOP mode 35, 233                                                               | control 0 registers 77                          |

| Stop Mode Recovery                                                              | control 1 registers 78                          |

| sources 33                                                                      | high and low byte registers 73, 76              |

| using a GPIO port pin transition 34                                             | TM 232                                          |

| using watchdog timer time-out 34                                                | TMX 232                                         |

| SUB 232                                                                         | transmit                                        |

| subtract 232                                                                    | IrDA data 111                                   |

| subtract - extended addressing 232                                              | transmit interrupt 131                          |

| subtract with carry 232                                                         | transmitting UART data-interrupt-driven method  |

| subtract with carry - extended addressing 232                                   | 91                                              |

| SUBX 232                                                                        | transmitting UART data-polled method 90         |

| SWAP 235                                                                        | TRAP 234                                        |

| swap nibbles 235                                                                |                                                 |

| symbols, additional 229                                                         |                                                 |

| system and core resets 30                                                       | U                                               |

|                                                                                 | UART 5, 88                                      |

|                                                                                 | architecture 88                                 |

| T                                                                               | asynchronous data format without/with parity    |

| TCM 232                                                                         | 90                                              |

| TCMX 232                                                                        | baud rate generator 99                          |

| test complement under mask 232                                                  | baud rates table 108                            |

| test complement under mask 252 test complement under mask - extended addressing | control register definitions 99                 |

| 232                                                                             | controller signals 16                           |

| test under mask 232                                                             | interrupts 97                                   |

| test under mask - extended addressing 232                                       | multiprocessor mode 94                          |

| timer signals 16                                                                | receiving data using interrupt-driven method 93 |

| timers 6, 63                                                                    | receiving data using the polled method 92       |

| architecture 63                                                                 | transmitting data using the interrupt-driven    |

| block diagram 64                                                                | method 91                                       |

| capture mode 69, 79                                                             | transmitting data using the polled method 90    |

| capture/compare mode 71, 79                                                     | x baud rate high and low registers 106          |

| compare mode 70, 79                                                             | x control 0 and control 1 registers 103         |

| compare mode 10, 17                                                             | A condoi o una common i registers 103           |