Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

#### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Product Status             | Active                                                    |

|----------------------------|-----------------------------------------------------------|

| Core Processor             | eZ8                                                       |

| Core Size                  | 8-Bit                                                     |

| Speed                      | 20MHz                                                     |

| Connectivity               | I <sup>2</sup> C, IrDA, SPI, UART/USART                   |

| Peripherals                | Brown-out Detect/Reset, DMA, POR, PWM, WDT                |

| Number of I/O              | 31                                                        |

| Program Memory Size        | 32KB (32K x 8)                                            |

| Program Memory Type        | FLASH                                                     |

| EEPROM Size                | -                                                         |

| RAM Size                   | 2K x 8                                                    |

| Voltage - Supply (Vcc/Vdd) | 3V ~ 3.6V                                                 |

| Data Converters            | A/D 8x10b                                                 |

| Oscillator Type            | Internal                                                  |

| Operating Temperature      | 0°C ~ 70°C (TA)                                           |

| Mounting Type              | Surface Mount                                             |

| Package / Case             | 44-LCC (J-Lead)                                           |

| Supplier Device Package    | -                                                         |

| Purchase URL               | https://www.e-xfl.com/product-detail/zilog/z8f3221vn020sg |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

| Watchdog Timer Reset                                     | . 32 |

|----------------------------------------------------------|------|

| External Pin Reset                                       | . 32 |

| On-Chip Debugger Initiated Reset                         | . 32 |

| Stop Mode Recovery                                       |      |

| Stop Mode Recovery Using Watchdog Timer Time-Out         | . 33 |

| Stop Mode Recovery Using a GPIO Port Pin Transition HALT | . 33 |

| Low-Power Modes                                          | . 34 |

| STOP Mode                                                | . 34 |

| HALT Mode                                                | . 35 |

| General-Purpose I/O                                      | 36   |

| GPIO Port Availability By Device                         |      |

| Architecture                                             |      |

| GPIO Alternate Functions                                 |      |

| GPIO Interrupts                                          |      |

| GPIO Control Register Definitions                        |      |

| Port A–H Address Registers                               |      |

| Port A–H Control Registers                               |      |

| Port A–H Input Data Registers                            |      |

| Port A–H Output Data Register                            |      |

| Interrupt Controller                                     |      |

| Interrupt Vector Listing                                 |      |

| Architecture                                             |      |

| Operation                                                |      |

| Master Interrupt Enable                                  |      |

| Interrupt Vectors and Priority                           |      |

| Interrupt Assertion                                      |      |

| Software Interrupt Assertion                             |      |

| Interrupt Control Register Definitions                   |      |

| Interrupt Request 0 Register                             |      |

| Interrupt Request 1 Register                             |      |

| Interrupt Request 2 Register                             |      |

| IRQ0 Enable High and Low Bit Registers                   |      |

| IRQ1 Enable High and Low Bit Registers                   |      |

| IRQ2 Enable High and Low Bit Registers                   |      |

| Interrupt Edge Select Register                           |      |

| Interrupt Port Select Register                           |      |

| Interrupt Control Register                               |      |

| Timers                                                   |      |

| Architecture                                             |      |

|                                                          | . 04 |

- Software stack allows much greater depth in subroutine calls and interrupts than hardware stacks

- Compatible with existing Z8 code

- Expanded internal Register File allows access of up to 4KB

- New instructions improve execution efficiency for code developed using higher-level programming languages, including C

- Pipelined instruction fetch and execution

- New instructions for improved performance including BIT, BSWAP, BTJ, CPC, LDC, LDCI, LEA, MULT and SRL

- New instructions support 12-bit linear addressing of the Register File

- Up to 10 MIPS operation

- C-Compiler friendly

- 2 to 9 clock cycles per instruction

For more information about the eZ8 CPU, refer to the <u>eZ8 CPU Core User Manual</u> (<u>UM0128</u>), which is available for download on <u>www.zilog.com</u>.

### **General-Purpose Input/Output**

The Z8 Encore! XP F64xx Series features seven 8-bit ports (ports A–G) and one 4-bit port (Port H) for general-purpose input/output (GPIO). Each pin is individually programmable. All ports (except B and H) support 5V-tolerant inputs.

### **Flash Controller**

The Flash Controller programs and erases the contents of Flash memory.

### **10-Bit Analog-to-Digital Converter**

The Analog-to-Digital Converter converts an analog input signal to a 10-bit binary number. The ADC accepts inputs from up to 12 different analog input sources.

### UARTs

Each UART is full-duplex and capable of handling asynchronous data transfers. The UARTs support 8- and 9-bit data modes, selectable parity, and an efficient bus transceiver Driver Enable signal for controlling a multitransceiver bus, such as RS-485.

| Program Memory<br>Address (Hex) | Function                                                                                                           |

|---------------------------------|--------------------------------------------------------------------------------------------------------------------|

| FE00H–FE3FH                     | Reserved                                                                                                           |

| FE40H–FE53H                     | Part Number<br>20-character ASCII alphanumeric code<br>Left-justified and filled with zeros (ASCII Null character) |

| FE54H–FFFFH                     | Reserved                                                                                                           |

#### Table 6. Z8 Encore! XP F64xx Series Information Area Map

Every subsequent appropriate transition (after the first) of the timer input signal captures the current count value. The Capture value is written to the Timer PWM High and Low Byte Registers. When the capture event occurs, an interrupt is generated, the count value in the Timer High and Low Byte registers is reset to 0001H, and counting resumes.

If no capture event occurs, the timer counts up to the 16-bit compare value stored in the Timer Reload High and Low Byte registers. Upon reaching the compare value, the timer generates an interrupt, the count value in the Timer High and Low Byte registers is reset to 0001H and counting resumes.

Observe the following procedure for configuring a timer for CAPTURE/COMPARE Mode and initiating the count:

- 1. Write to the Timer Control 1 Register to:

- Disable the timer

- Configure the timer for CAPTURE/COMPARE Mode

- Set the prescale value

- Set the Capture edge (rising or falling) for the timer input

- 2. Write to the Timer High and Low Byte registers to set the starting count value (typically 0001H).

- 3. Write to the Timer Reload High and Low Byte registers to set the compare value.

- 4. If appropriate, enable the timer interrupt and set the timer interrupt priority by writing to the relevant interrupt registers.

- 5. Configure the associated GPIO port pin for the timer input alternate function.

- 6. Write to the Timer Control 1 Register to enable the timer.

- 7. Counting begins on the first appropriate transition of the timer input signal. No interrupt is generated by this first edge.

In COMPARE Mode, the elapsed time from timer start to capture event can be calculated using the following equation:

Capture Elapsed Time (s) =  $\frac{(Capture Value - Start Value) \times Prescale}{System Clock Frequency (Hz)}$

### **Reading the Timer Count Values**

The current count value in the timers can be read while counting (enabled). This capability has no effect on timer operation. When the timer is enabled and the Timer High Byte Register is read, the contents of the Timer Low Byte Register are placed in a holding register. A subsequent read from the Timer Low Byte Register returns the value in the holding reg-

#### Table 48. Watchdog Timer Control Register (WDTCTL)

| Bit         | 7                                                            | 6                                                                                                                                                                                                                                                                                                                                                                                                                                               | 5          | 4             | 3                                | 2        | 1 | 0     |  |  |

|-------------|--------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------|---------------|----------------------------------|----------|---|-------|--|--|

| Field       | POR                                                          | STOP                                                                                                                                                                                                                                                                                                                                                                                                                                            | WDT        | EXT           |                                  | Reserved |   | SM    |  |  |

| RESET       | S                                                            | See Table 49                                                                                                                                                                                                                                                                                                                                                                                                                                    | ).         |               |                                  | 0        |   |       |  |  |

| R/W         |                                                              |                                                                                                                                                                                                                                                                                                                                                                                                                                                 |            | ŀ             | २                                |          |   |       |  |  |

| Address     |                                                              |                                                                                                                                                                                                                                                                                                                                                                                                                                                 |            | FF            | ОH                               |          |   |       |  |  |

| Bit         | Descriptio                                                   | n                                                                                                                                                                                                                                                                                                                                                                                                                                               |            |               |                                  |          |   |       |  |  |

| [7]<br>POR  | Power-On<br>If this bit is                                   | Reset Indic<br>set to 1, a P                                                                                                                                                                                                                                                                                                                                                                                                                    | ower-On Re |               | ccurred. This<br>reset to 0 w    |          |   |       |  |  |

| [6]<br>STOP | If this bit is<br>1, the Stop<br>bit is 0, the<br>Power-On F | <b>Stop Mode Recovery Indicator</b><br>If this bit is set to 1, a Stop Mode Recovery occurred. If the stop and WDT bits are both set to 1, the Stop Mode Recovery occurred due to a WDT time-out. If the stop bit is 1 and the WDT bit is 0, the Stop Mode Recovery was not caused by a WDT time-out. This bit is reset by a Power-On Reset or a WDT time-out that occurred while not in STOP Mode. Reading this register also resets this bit. |            |               |                                  |          |   |       |  |  |

| [5]<br>WDT  | If this bit is                                               | set to 1, a V                                                                                                                                                                                                                                                                                                                                                                                                                                   |            | t occurred. A | A Power-On sets this bit.        |          |   |       |  |  |

| [4]<br>EXT  | If this bit is or a Stop M                                   | External Reset Indicator<br>If this bit is set to 1, a Reset initiated by the external RESET pin occurred. A Power-On Reset<br>or a Stop Mode Recovery from a change in an input pin resets this bit. Reading this register<br>resets this bit.                                                                                                                                                                                                 |            |               |                                  |          |   |       |  |  |

| [3:1]       | Reserved<br>These bits a                                     | Reserved<br>These bits are reserved and must be programmed to 000.                                                                                                                                                                                                                                                                                                                                                                              |            |               |                                  |          |   |       |  |  |

| [0]<br>SM   | 0 = Watchd                                                   | log Timer ar                                                                                                                                                                                                                                                                                                                                                                                                                                    |            | I RC oscillat | or will contir<br>or will be dis |          |   | Mode. |  |  |

#### Table 60. UART Baud Rate High Byte Register (UxBRH)

| Bit     | 7 | 6   | 5 | 4       | 3       | 2 | 1 | 0 |  |  |  |  |

|---------|---|-----|---|---------|---------|---|---|---|--|--|--|--|

| Field   |   | BRH |   |         |         |   |   |   |  |  |  |  |

| RESET   |   |     |   | ,       | 1       |   |   |   |  |  |  |  |

| R/W     |   | R/W |   |         |         |   |   |   |  |  |  |  |

| Address |   |     |   | F46H ar | nd F4EH |   |   |   |  |  |  |  |

#### Table 61. UART Baud Rate Low Byte Register (UxBRL)

| Bit7    | 7   | 6   | 5 | 4       | 3       | 2 | 1 | 0 |  |  |  |

|---------|-----|-----|---|---------|---------|---|---|---|--|--|--|

| Field   | BRL |     |   |         |         |   |   |   |  |  |  |

| RESET   |     |     |   |         | 1       |   |   |   |  |  |  |

| R/W     |     | R/W |   |         |         |   |   |   |  |  |  |

| Address |     |     |   | F47H ar | nd F4FH |   |   |   |  |  |  |

For a given UART data rate, the integer baud rate divisor value is calculated using the following equation:

UART Baud Rate Divisor Value (BRG) = Round  $\left(\frac{\text{System Clock Frequency (Hz)}}{16 \times \text{UART Data Rate (bits/s)}}\right)$

The baud rate error relative to the appropriate baud rate is calculated using the following equation:

UART Baud Rate Error (%) =

$$100 \times \left(\frac{\text{Actual Data Rate} - \text{Desired Data Rate}}{\text{Desired Data Rate}}\right)$$

For reliable communication, the UART baud rate error must never exceed 5 percent. Table 62 lists data rate errors for popular baud rates and commonly used crystal oscillator frequencies.

## **SPI Mode Register**

The SPI Mode Register, shown in Table 67, configures the character bit width and the direction and value of the  $\overline{SS}$  pin.

#### Table 67. SPI Mode Register (SPIMODE)

| Bit     | 7    | 6     | 5                 | 4  | 3  | 2 | 1    | 0   |  |

|---------|------|-------|-------------------|----|----|---|------|-----|--|

| Field   | Rese | erved | DIAG NUMBITS[2:0] |    |    |   | SSIO | SSV |  |

| RESET   |      |       |                   | (  | )  |   |      |     |  |

| R/W     | F    | २     | R/W               |    |    |   |      |     |  |

| Address |      |       |                   | F6 | 3H |   |      |     |  |

| Bit                 | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

|---------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| [7:6]               | <b>Reserved</b><br>These bits are reserved and must be programmed to 00.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

| [5]<br>DIAG         | <ul> <li>Diagnostic Mode Control bit</li> <li>This bit is for SPI diagnostics. Setting this bit allows the Baud Rate Generator value to be read using the SPIBRH and SPIBRL Register locations.</li> <li>0 = Reading SPIBRH, SPIBRL returns the value in the SPIBRH and SPIBRL registers.</li> <li>1 = Reading SPIBRH returns bits [15:8] of the SPI Baud Rate Generator; and reading SPIBRL returns bits [7:0] of the SPI Baud Rate Counter. The Baud Rate Counter High and Low byte values are not buffered.</li> <li>Caution: Exercise caution if reading the values while the BRG is counting.</li> </ul> |

| [4]<br>NUMBITS[2:0] | Number of Data Bits Per Character to Transfer<br>This field contains the number of bits to shift for each character transfer. For information<br>about valid bit positions when the character length is less than 8 bits, see the <u>SPI Data</u><br><u>Register (SPIDATA)</u> description.<br>000 = 8 bits.<br>001 = 1 bit.<br>010 = 2 bits.<br>011 = 3 bits.<br>100 = 4 bits.<br>110 = 6 bits.<br>111 = 7 bits.                                                                                                                                                                                             |

| [1]<br>SSIO         | Slave Select I/O<br>$0 = \frac{SS}{SS}$ pin configured as an input.<br>1 = SS pin configured as an output (Master mode only).                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

| [0]<br>SSV          | Slave Select Value<br>If SSIO = 1 and SPI is configured as a Master, the following conditions are true:<br>$0 = \frac{SS}{SS}$ pin driven Low (0).<br>1 = SS pin driven High (1).<br>This bit has no effect if SSIO = 0 or if SPI is configured as a Slave.                                                                                                                                                                                                                                                                                                                                                   |

### Table 71. I<sup>2</sup>C Data Register (I2CDATA)

| Bit     | 7   | 6    | 5 | 4  | 3  | 2 | 1 | 0 |  |  |  |  |

|---------|-----|------|---|----|----|---|---|---|--|--|--|--|

| Field   |     | DATA |   |    |    |   |   |   |  |  |  |  |

| RESET   |     |      |   | (  | )  |   |   |   |  |  |  |  |

| R/W     | R/W |      |   |    |    |   |   |   |  |  |  |  |

| Address |     |      |   | F5 | 0H |   |   |   |  |  |  |  |

# I<sup>2</sup>C Status Register

The read-only  $I^2C$  Status Register, shown in Table 72, indicates the status of the  $I^2C$  Controller.

## Table 72. I<sup>2</sup>C Status Register (I2CSTAT)

| Bit     | 7    | 6    | 5   | 4   | 3  | 2   | 1   | 0    |  |  |  |

|---------|------|------|-----|-----|----|-----|-----|------|--|--|--|

| Field   | TDRE | RDRF | ACK | 10B | RD | TAS | DSS | NCKI |  |  |  |

| RESET   | 1    |      |     |     | 0  |     |     |      |  |  |  |

| R/W     |      | R    |     |     |    |     |     |      |  |  |  |

| Address |      |      |     | F5  | 1H |     |     |      |  |  |  |

| Bit  | Description                                                                                                                                                                                                                                                                                                                                                                                       |

|------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| [7]  | <b>Transmit Data Register Empty</b>                                                                                                                                                                                                                                                                                                                                                               |

| TDRE | When the I <sup>2</sup> C Controller is enabled, this bit is 1 when the I <sup>2</sup> C Data Register is empty. When this bit is set, an interrupt is generated if the TXI bit is set, except when the I <sup>2</sup> C Controller is shifting in data during the reception of a byte or when shifting an address and the RD bit is set. This bit is cleared by writing to the I2CDATA Register. |

| [6]  | <b>Receive Data Register Full</b>                                                                                                                                                                                                                                                                                                                                                                 |

| RDRF | This bit is set = 1 when the I <sup>2</sup> C Controller is enabled and the I <sup>2</sup> C Controller has received a byte of data. When asserted, this bit causes the I <sup>2</sup> C Controller to generate an interrupt. This bit is cleared by reading the I <sup>2</sup> C Data Register (unless the read is performed using execution of the On-Chip Debugger's Read Register command).   |

# Operation

This section describes the operational aspects of the ADC's power-down and conversion features.

## **Automatic Power-Down**

If the ADC is idle (i.e., no conversions are in progress) for 160 consecutive system clock cycles, portions of the ADC are automatically powered down. From this powered-down state, the ADC requires 40 system clock cycles to power up. The ADC powers up when a conversion is requested using the ADC Control Register.

## **Single-Shot Conversion**

When configured for single-shot conversion, the ADC performs a single analog-to-digital conversion on the selected analog input channel. After completion of the conversion, the ADC shuts down. Observe the following procedure for setting up the ADC and initiating a single-shot conversion:

- 1. Enable the appropriate analog inputs by configuring the general-purpose I/O pins for alternate function. This configuration disables the digital input and output drivers.

- 2. Write to the ADC Control Register to configure the ADC and begin the conversion. The bit fields in the ADC Control Register can be written simultaneously:

- Write to the ANAIN[3:0] field to select one of the 12 analog input sources

- Clear CONT to 0 to select a single-shot conversion

- Write to the  $\overline{\text{VREF}}$  bit to enable or disable the internal voltage reference generator

- Set CEN to 1 to start the conversion

- 3. CEN remains 1 while the conversion is in progress. A single-shot conversion requires 5129 system clock cycles to complete. If a single-shot conversion is requested from an ADC powered-down state, the ADC uses 40 additional clock cycles to power up before beginning the 5129 cycle conversion.

- 4. When the conversion is complete, the ADC control logic performs the following operations:

- 10-bit data result written to {ADCD\_H[7:0], ADCD\_L[7:6]}

- CEN resets to 0 to indicate the conversion is complete

- An interrupt request is sent to the Interrupt Controller

- 5. If the ADC remains idle for 160 consecutive system clock cycles, it is automatically powered down.

## **Continuous Conversion**

When configured for continuous conversion, the ADC continuously performs an analogto-digital conversion on the selected analog input. Each new data value over-writes the previous value stored in the ADC Data registers. An interrupt is generated after each conversion.

**Caution:** In CONTINUOUS Mode, you must be aware that ADC updates are limited by the input signal bandwidth of the ADC and the latency of the ADC and its digital filter. Step changes at the input are not seen at the next output from the ADC. The response of the ADC (in all modes) is limited by the input signal bandwidth and the latency.

Observe the following procedure for setting up the ADC and initiating continuous conversion:

- 1. Enable the appropriate analog input by configuring the general-purpose I/O pins for alternate function. This disables the digital input and output driver.

- 2. Write to the ADC Control Register to configure the ADC for continuous conversion. The bit fields in the ADC Control Register may be written simultaneously:

- Write to the ANAIN[3:0] field to select one of the 12 analog input sources

- Set CONT to 1 to select continuous conversion

- Write to the  $\overline{\text{VREF}}$  bit to enable or disable the internal voltage reference generator

- Set CEN to 1 to start the conversions

- 3. When the first conversion in continuous operation is complete (after 5129 system clock cycles, plus the 40 cycles required to power up, if necessary), the ADC control logic performs the following operations:

- CEN resets to 0 to indicate the first conversion is complete. CEN remains 0 for all subsequent conversions in continuous operation

- An interrupt request is sent to the Interrupt Controller to indicate the conversion is complete

- 4. Thereafter, the ADC writes a new 10-bit data result to {ADCD\_H[7:0], ADCD\_L[7:6]} every 256 system clock cycles. An interrupt request is sent to the Interrupt Controller when each conversion is complete.

- 5. To disable continuous conversion, clear the CONT bit in the ADC Control Register to 0.

## **ADC Data Low Bits Register**

The ADC Data Low Bits Register, Table 89, contains the lower two bits of the conversion value. The data in the ADC Data Low Bits Register is latched each time the ADC Data High Byte Register is read. Reading this register always returns the lower two bits of the conversion last read into the ADC High Byte Register. Access to the ADC Data Low Bits Register is read-only. The full 10-bit ADC result is provided by {ADCD\_H[7:0], ADCD\_L[7:6]}.

| Bit             | 7          | 6                                                                                                                                  | 5 | 4        | 3  | 2 | 1 | 0 |  |  |  |

|-----------------|------------|------------------------------------------------------------------------------------------------------------------------------------|---|----------|----|---|---|---|--|--|--|

| Field           | ADC        | D_L                                                                                                                                |   | Reserved |    |   |   |   |  |  |  |

| RESET           |            |                                                                                                                                    |   | )        | <  |   |   |   |  |  |  |

| R/W             |            |                                                                                                                                    |   | F        | १  |   |   |   |  |  |  |

| Address         |            |                                                                                                                                    |   | F7       | 3H |   |   |   |  |  |  |

| Bit             | Descriptio | n                                                                                                                                  |   |          |    |   |   |   |  |  |  |

| [7:6]<br>ADCD_L |            | ADC Data Low Bits<br>These are the least significant two bits of the 10-bit ADC output. These bits are undefined after<br>a Reset. |   |          |    |   |   |   |  |  |  |

| [5:0]           | Reserved   |                                                                                                                                    |   |          |    |   |   |   |  |  |  |

#### Table 89. ADC Data Low Bits Register (ADCD\_L)

These bits are reserved and are always undefined.

| Bit            | Description (Continued)                                                                                                                                                                                                                                                                                                                                                                                                  |

|----------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| [4]<br>BRKLOOP | <b>Breakpoint Loop</b><br>This bit determines what action the OCD takes when a BRK instruction is decoded if break-<br>points are enabled (BRKEN is 1). If this bit is 0, then the DBGMODE bit is automatically set<br>to 1 and the OCD entered DEBUG Mode. If BRKLOOP is set to 1, then the<br>eZ8 CPU loops on the BRK instruction.<br>0 = BRK instruction sets DBGMODE to 1.<br>1 = eZ8 CPU loops on BRK instruction. |

| [3:1]          | <b>Reserved</b><br>These bits are reserved and must be programmed to 000.                                                                                                                                                                                                                                                                                                                                                |

| [0]<br>RST     | ResetSetting this bit to 1 resets the Z8 Encore! XP F64xx Series devices. The devices go through<br>a normal Power-On Reset sequence with the exception that the On-Chip Debugger is not<br>reset. This bit is automatically cleared to 0 when the reset finishes.0 = No effect.1 = Reset the Z8 Encore! XP F64xx Series device.                                                                                         |

## **OCD Status Register**

The OCD Status Register, shown in Table 104, reports status information about the current state of the debugger and the system.

#### Table 104. OCD Status Register (OCDSTAT)

| Bit   | 7    | 6    | 5    | 4        | 3 | 2 | 1 | 0 |  |

|-------|------|------|------|----------|---|---|---|---|--|

| Field | IDLE | HALT | RPEN | Reserved |   |   |   |   |  |

| RESET |      | 0    |      |          |   |   |   |   |  |

| R/W   |      | R    |      |          |   |   |   |   |  |

| Bit         | Description                                                                                                                                                                                                                                                                                                                                                          |

|-------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| [7]<br>IDLE | <ul> <li>CPU Idle</li> <li>This bit is set if the part is in DEBUG Mode (DBGMODE is 1), or if a BRK instruction occurred since the last time OCDCTL was written. This can be used to determine if the CPU is running or if it is idling.</li> <li>0 = The eZ8 CPU is running.</li> <li>1 = The eZ8 CPU is either stopped or looping on a BRK instruction.</li> </ul> |

| [6]<br>HALT | HALT Mode<br>0 = The device is not in HALT Mode.<br>1 = The device is in HALT Mode.                                                                                                                                                                                                                                                                                  |

### Z8 Encore! XP<sup>®</sup> F64xx Series Product Specification

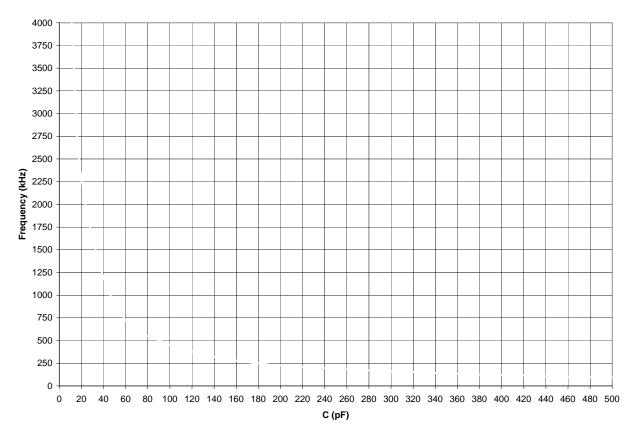

Figure 42. Typical RC Oscillator Frequency as a Function of the External Capacitance with a  $45k\Omega$  Resistor

**Caution:** When using the external RC oscillator mode, the oscillator may stop oscillating if the power supply drops below 2.7 V, but before the power supply drops to the voltage brown-out threshold. The oscillator will resume oscillation as soon as the supply voltage exceeds 2.7 V.

199

#### 216

# **AC Characteristics**

This section provides AC characteristics and timing data which assumes a standard load of 50pF on all outputs. Table 114 lists the Z8 Encore! XP F64xx Series AC characteristics and timing.

|                     |                                    | V <sub>DD</sub> = 3.0V–3.6V<br>T <sub>A</sub> = -40°C to 125°C |         |       |                                                                                                            |

|---------------------|------------------------------------|----------------------------------------------------------------|---------|-------|------------------------------------------------------------------------------------------------------------|

| Symbol              | Parameter                          | Minimum                                                        | Maximum | Units | Conditions                                                                                                 |

| F <sub>SYSCLK</sub> | System Clock Frequency             | -                                                              | 20.0    | MHz   | Read-only from Flash memory.                                                                               |

|                     |                                    | 0.032768                                                       | 20.0    | MHz   | Program or erasure of Flash memory.                                                                        |

| F <sub>XTAL</sub>   | Crystal Oscillator Frequency       | 0.032768                                                       | 20.0    | MHz   | System clock frequencies<br>below the crystal oscillator mini-<br>mum require an external clock<br>driver. |

| T <sub>XIN</sub>    | Crystal Oscillator Clock<br>Period | 50                                                             | -       | ns    | T <sub>CLK</sub> = 1/F <sub>SYSCLK</sub>                                                                   |

| T <sub>XINH</sub>   | System Clock High Time             | 20                                                             |         | ns    |                                                                                                            |

| T <sub>XINL</sub>   | System Clock Low Time              | 20                                                             |         | ns    |                                                                                                            |

| T <sub>XINR</sub>   | System Clock Rise Time             | -                                                              | 3       | ns    | $T_{CLK}$ = 50 ns. Slower rise times<br>can be tolerated with longer<br>clock periods.                     |

| T <sub>XINF</sub>   | System Clock Fall Time             | -                                                              | 3       | ns    | $T_{CLK}$ = 50 ns. Slower fall times<br>can be tolerated with longer<br>clock periods.                     |

| Table 114. / | AC Character | istics |

|--------------|--------------|--------|

|--------------|--------------|--------|

| Mnemonic | Operands | Instruction            |

|----------|----------|------------------------|

| ATM      | _        | Atomic Execution       |

| CCF      | _        | Complement Carry Flag  |

| DI       | —        | Disable Interrupts     |

| EI       | —        | Enable Interrupts      |

| HALT     | _        | HALT Mode              |

| NOP      | —        | No Operation           |

| RCF      | —        | Reset Carry Flag       |

| SCF      | —        | Set Carry Flag         |

| SRP      | src      | Set Register Pointer   |

| STOP     | —        | STOP Mode              |

| WDT      | —        | Watchdog Timer Refresh |

#### Table 131. CPU Control Instructions

#### Table 132. Load Instructions

| Mnemonic | Operands    | Instruction                                                              |

|----------|-------------|--------------------------------------------------------------------------|

| CLR      | dst         | Clear                                                                    |

| LD       | dst, src    | Load                                                                     |

| LDC      | dst, src    | Load Constant to/from program memory                                     |

| LDCI     | dst, src    | Load Constant to/from program memory and Auto-Incre-<br>ment addresses   |

| LDE      | dst, src    | Load External Data to/from Data Memory                                   |

| LDEI     | dst, src    | Load External Data to/from Data Memory and Auto-Incre-<br>ment addresses |

| LDWX     | dst, src    | Load Word using Extended Addressing                                      |

| LDX      | dst, src    | Load using Extended Addressing                                           |

| LEA      | dst, X(src) | Load Effective Address                                                   |

| POP      | dst         | Рор                                                                      |

| POPX     | dst         | Pop using Extended Addressing                                            |

| PUSH     | src         | Push                                                                     |

| PUSHX    | SIC         | Push using Extended Addressing                                           |

| Mnemonic | Operands | Instruction                                         |

|----------|----------|-----------------------------------------------------|

| AND      | dst, src | Logical AND                                         |

| ANDX     | dst, src | Logical AND using Extended Addressing               |

| COM      | dst      | Complement                                          |

| OR       | dst, src | Logical OR                                          |

| ORX      | dst, src | Logical OR using Extended Addressing                |

| XOR      | dst, src | Logical Exclusive OR                                |

| XORX     | dst, src | Logical Exclusive OR using Extended Address-<br>ing |

#### Table 133. Logical Instructions

#### Table 134. Program Control Instructions

| Mnemonic | Operands        | Instruction                   |

|----------|-----------------|-------------------------------|

| BRK      |                 | On-Chip Debugger Break        |

| BTJ      | p, bit, src, DA | Bit Test and Jump             |

| BTJNZ    | bit, src, DA    | Bit Test and Jump if Non-Zero |

| BTJZ     | bit, src, DA    | Bit Test and Jump if Zero     |

| CALL     | dst             | Call Procedure                |

| DJNZ     | dst, src, RA    | Decrement and Jump Non-Zero   |

| IRET     | —               | Interrupt Return              |

| JP       | dst             | Jump                          |

| JP cc    | dst             | Jump Conditional              |

| JR       | DA              | Jump Relative                 |

| JR cc    | DA              | Jump Relative Conditional     |

| RET      | —               | Return                        |

| TRAP     | vector          | Software Trap                 |

273

### Hex Addresses: FC9–FCC

This address range is reserved.

### Hex Address: FCD

#### Table 226. Interrupt Edge Select Register (IRQES)

| Bit     | 7    | 6    | 5    | 4    | 3    | 2    | 1    | 0    |  |  |

|---------|------|------|------|------|------|------|------|------|--|--|

| Field   | IES7 | IES6 | IES5 | IES4 | IES3 | IES2 | IES1 | IES0 |  |  |

| RESET   |      | 0    |      |      |      |      |      |      |  |  |

| R/W     |      | R/W  |      |      |      |      |      |      |  |  |

| Address |      | FCDH |      |      |      |      |      |      |  |  |

#### Hex Address: FCE

#### Table 227. Interrupt Port Select Register (IRQPS)

| Bit     | 7     | 6     | 5     | 4     | 3     | 2     | 1     | 0     |  |  |

|---------|-------|-------|-------|-------|-------|-------|-------|-------|--|--|

| Field   | PAD7S | PAD6S | PAD5S | PAD4S | PAD3S | PAD2S | PAD1S | PAD0S |  |  |

| RESET   |       | 0     |       |       |       |       |       |       |  |  |

| R/W     |       | R/W   |       |       |       |       |       |       |  |  |

| Address |       | FCEH  |       |       |       |       |       |       |  |  |

### Hex Address: FCF

#### Table 228. Interrupt Control Register (IRQCTL)

| Bit     | 7    | 6     | 5        | 4 | 3 | 2 | 1 | 0 |  |

|---------|------|-------|----------|---|---|---|---|---|--|

| Field   | IRQE |       | Reserved |   |   |   |   |   |  |

| RESET   |      | 0     |          |   |   |   |   |   |  |

| R/W     | R/W  | R/W R |          |   |   |   |   |   |  |

| Address |      | FCFH  |          |   |   |   |   |   |  |

|                                                             |             |          |           |            |                     |                     |                  | 5   |                 |                     |  |  |

|-------------------------------------------------------------|-------------|----------|-----------|------------|---------------------|---------------------|------------------|-----|-----------------|---------------------|--|--|

| Part Number                                                 | Flash       | RAM      | I/O Lines | Interrupts | 16-Bit Timers w/PWM | 10-Bit A/D Channels | l <sup>2</sup> C | SPI | UARTs with IrDA | Description         |  |  |

| Z8F482x with 48KB Flash, 10-Bit Analog-to-Digital Converter |             |          |           |            |                     |                     |                  |     |                 |                     |  |  |

| Standard Temperature                                        |             |          |           |            |                     |                     |                  |     |                 |                     |  |  |

| Z8F4821PM020SG                                              | 48KB        | 4KB      | 29        | 23         | 3                   | 8                   | 1                | 1   | 2               | PDIP 40-pin package |  |  |

| Z8F4821AN020SG                                              | 48KB        | 4KB      | 31        | 23         | 3                   | 8                   | 1                | 1   | 2               | LQFP 44-pin package |  |  |

| Z8F4821VN020SG                                              | 48 KB       | 4KB      | 31        | 23         | 3                   | 8                   | 1                | 1   | 2               | PLCC 44-pin package |  |  |

| Z8F4822AR020SG                                              | 48KB        | 4KB      | 46        | 24         | 4                   | 12                  | 1                | 1   | 2               | LQFP 64-pin package |  |  |

| Z8F4822VS020SG                                              | 48KB        | 4KB      | 46        | 24         | 4                   | 12                  | 1                | 1   | 2               | PLCC 68-pin package |  |  |

| Z8F4823FT020SG                                              | 48KB        | 4KB      | 60        | 24         | 4                   | 12                  | 1                | 1   | 2               | QFP 80-pin package  |  |  |

| Extended Temperature                                        | e: -40°C to | +105°C   |           |            |                     |                     |                  |     |                 |                     |  |  |

| Z8F4821PM020EG                                              | 48 K B      | 4KB      | 29        | 23         | 3                   | 8                   | 1                | 1   | 2               | PDIP 40-pin package |  |  |

| Z8F4821AN020EG                                              | 48KB        | 4KB      | 31        | 23         | 3                   | 8                   | 1                | 1   | 2               | LQFP 44-pin package |  |  |

| Z8F4821VN020EG                                              | 48KB        | 4KB      | 31        | 23         | 3                   | 8                   | 1                | 1   | 2               | PLCC 44-pin package |  |  |

| Z8F4822AR020EG                                              | 48KB        | 4KB      | 46        | 24         | 4                   | 12                  | 1                | 1   | 2               | LQFP 64-pin package |  |  |

| Z8F4822VS020EG                                              | 48KB        | 4KB      | 46        | 24         | 4                   | 12                  | 1                | 1   | 2               | PLCC 68-pin package |  |  |

| Z8F4823FT020EG                                              | 48KB        | 4KB      | 60        | 24         | 4                   | 12                  | 1                | 1   | 2               | QFP 80-pin package  |  |  |

| Automotive/Industrial                                       | Temperatu   | re: –40° | °C to     | +125       | 5°C                 |                     |                  |     |                 |                     |  |  |

| Z8F4821PM020AG                                              | 48KB        | 4KB      | 29        | 23         | 3                   | 8                   | 1                | 1   | 2               | PDIP 40-pin package |  |  |

| Z8F4821AN020AG                                              | 48KB        | 4KB      | 31        | 23         | 3                   | 8                   | 1                | 1   | 2               | LQFP 44-pin package |  |  |

| Z8F4821VN020AG                                              | 48KB        | 4KB      | 31        | 23         | 3                   | 8                   | 1                | 1   | 2               | PLCC 44-pin package |  |  |

| Z8F4822AR020AG                                              | 48KB        | 4KB      | 46        | 24         | 4                   | 12                  | 1                | 1   | 2               | LQFP 64-pin package |  |  |

| Z8F4822VS020AG                                              | 48KB        | 4KB      | 46        | 24         | 4                   | 12                  | 1                | 1   | 2               | PLCC 68-pin package |  |  |

| Z8F4823FT020AG                                              | 48KB        | 4KB      | 60        | 24         | 4                   | 12                  | 1                | 1   | 2               | QFP 80-pin package  |  |  |

|                                                             |             |          |           |            |                     |                     |                  |     |                 |                     |  |  |

### Table 271. Z8 Encore! XP F64xx Series Ordering Matrix

|                                                             |             |     | /O Lines | Interrupts | 6-Bit Timers w/PWM | 10-Bit A/D Channels |                  |     | JARTs with IrDA |                     |  |

|-------------------------------------------------------------|-------------|-----|----------|------------|--------------------|---------------------|------------------|-----|-----------------|---------------------|--|

| Part Number                                                 | Flash       | RAM | 10 L     | Inter      | 16-B               | 10-B                | I <sup>2</sup> C | SPI | UAR             | Description         |  |

| Z8F242x with 24KB Flash, 10-Bit Analog-to-Digital Converter |             |     |          |            |                    |                     |                  |     |                 |                     |  |

| Standard Temperature                                        | : 0°C to 70 | °C  |          |            |                    |                     |                  |     |                 |                     |  |

| Z8F2421PM020SG                                              | 24KB        | 2KB | 29       | 23         | 3                  | 8                   | 1                | 1   | 2               | PDIP 40-pin package |  |

| Z8F2421AN020SG                                              | 24KB        | 2KB | 31       | 23         | 3                  | 8                   | 1                | 1   | 2               | LQFP 44-pin package |  |

| Z8F2421VN020SG                                              | 24KB        | 2KB | 31       | 23         | 3                  | 8                   | 1                | 1   | 2               | PLCC 44-pin package |  |

| Z8F2422AR020SG                                              | 24KB        | 2KB | 46       | 24         | 4                  | 12                  | 1                | 1   | 2               | LQFP 64-pin package |  |

| Z8F2422VS020SG                                              | 24KB        | 2KB | 46       | 24         | 4                  | 12                  | 1                | 1   | 2               | PLCC 68-pin package |  |

| Extended Temperature: –40°C to 105°C                        |             |     |          |            |                    |                     |                  |     |                 |                     |  |

| Z8F2421PM020EG                                              | 24KB        | 2KB | 29       | 23         | 3                  | 8                   | 1                | 1   | 2               | PDIP 40-pin package |  |

| Z8F2421AN020EG                                              | 24KB        | 2KB | 31       | 23         | 3                  | 8                   | 1                | 1   | 2               | LQFP 44-pin package |  |

| Z8F2421VN020EG                                              | 24KB        | 2KB | 31       | 23         | 3                  | 8                   | 1                | 1   | 2               | PLCC 44-pin package |  |

| Z8F2422AR020EG                                              | 24KB        | 2KB | 46       | 24         | 4                  | 12                  | 1                | 1   | 2               | LQFP 64-pin package |  |

| Z8F2422VS020EG                                              | 24KB        | 2KB | 46       | 24         | 4                  | 12                  | 1                | 1   | 2               | PLCC 68-pin package |  |

| Automotive/Industrial Temperature: –40°C to 125°C           |             |     |          |            |                    |                     |                  |     |                 |                     |  |

| Z8F2421PM020AG                                              | 24KB        | 2KB | 29       | 23         | 3                  | 8                   | 1                | 1   | 2               | PDIP 40-pin package |  |

| Z8F2421AN020AG                                              | 24KB        | 2KB | 31       | 23         | 3                  | 8                   | 1                | 1   | 2               | LQFP 44-pin package |  |

| Z8F2421VN020AG                                              | 24KB        | 2KB | 31       | 23         | 3                  | 8                   | 1                | 1   | 2               | PLCC 44-pin package |  |

| Z8F2422AR020AG                                              | 24KB        | 2KB | 46       | 24         | 4                  | 12                  | 1                | 1   | 2               | LQFP 64-pin package |  |

| Z8F2422VS020AG                                              | 24KB        | 2KB | 46       | 24         | 4                  | 12                  | 1                | 1   | 2               | PLCC 68-pin package |  |

### Table 271. Z8 Encore! XP F64xx Series Ordering Matrix

295

first opcode map 247 FLAGS 229 flags register 229 flash controller 5 option bit address space 181 option bit configuration - reset 181 program memory address 0001H 183 flash memory arrangement 171 byte programming 174 code protection 173 configurations 170 control register definitions 176 controller bypass 175 electrical characteristics and timing 214 flash control register 177, 285 flash status register 178 frequency high and low byte registers 180 mass erase 175 operation 172 operation timing 172 page erase 175 page select register 178 FPS register 178 FSTAT register 178

## G

gated mode 79 general-purpose I/O 37 GPIO 5, 37 alternate functions 38 architecture 38 control register definitions 40 input data sample timing 218 interrupts 40 port A-H address registers 41 port A-H alternate function sub-registers 43 port A-H control registers 42 port A-H data direction sub-registers 42 port A-H high drive enable sub-registers 45 port A-H input data registers 47 port A-H output control sub-registers 44 port A-H output data registers 47 port A-H Stop Mode Recovery sub-registers 46 port availability by device 37 port input timing 218 port output timing 219

## Η

H 229 HALT 233 halt mode 36, 233 hexadecimal number prefix/suffix 229

#### | |2C 5

10-bit address read transaction 140 10-bit address transaction 137 10-bit addressed slave data transfer format 137 10-bit receive data format 140 7-bit address transaction 134 7-bit address, reading a transaction 139 7-bit addressed slave data transfer format 134, 135.136 7-bit receive data transfer format 139 baud high and low byte registers 146, 148, 150 C status register 143, 263 control register definitions 142 controller 129 controller signals 15 interrupts 131 operation 130 SDA and SCL signals 131 stop and start conditions 133 I2CBRH register 147, 148, 150, 263, 264 I2CBRL register 147, 263 I2CCTL register 145, 263 I2CDATA register 143, 262 I2CSTAT register 143, 263 IM 228 immediate data 228 immediate operand prefix 229 INC 231 increment 231