Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

#### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Product Status             | Active                                                    |

|----------------------------|-----------------------------------------------------------|

| Core Processor             | eZ8                                                       |

| Core Size                  | 8-Bit                                                     |

| Speed                      | 20MHz                                                     |

| Connectivity               | I <sup>2</sup> C, IrDA, SPI, UART/USART                   |

| Peripherals                | Brown-out Detect/Reset, DMA, POR, PWM, WDT                |

| Number of I/O              | 46                                                        |

| Program Memory Size        | 32KB (32K x 8)                                            |

| Program Memory Type        | FLASH                                                     |

| EEPROM Size                | -                                                         |

| RAM Size                   | 2K x 8                                                    |

| Voltage - Supply (Vcc/Vdd) | 3V ~ 3.6V                                                 |

| Data Converters            | A/D 12x10b                                                |

| Oscillator Type            | Internal                                                  |

| Operating Temperature      | 0°C ~ 70°C (TA)                                           |

| Mounting Type              | Surface Mount                                             |

| Package / Case             | 64-LQFP                                                   |

| Supplier Device Package    | -                                                         |

| Purchase URL               | https://www.e-xfl.com/product-detail/zilog/z8f3222ar020sg |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

#### Z8 Encore! XP<sup>®</sup> F64xx Series Product Specification

9

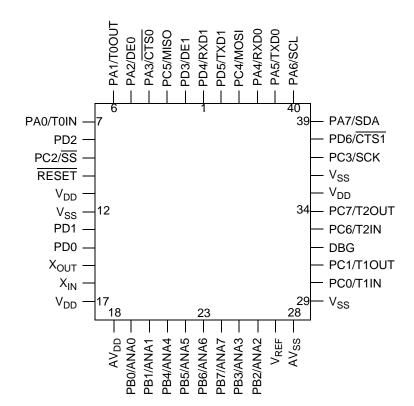

Figure 3. Z8 Encore! XP F64xx Series in 44-Pin Plastic Leaded Chip Carrier (PLCC)

**Note:** Timer 3 is not available in the 44-pin PLCC package.

#### **Power-On Reset**

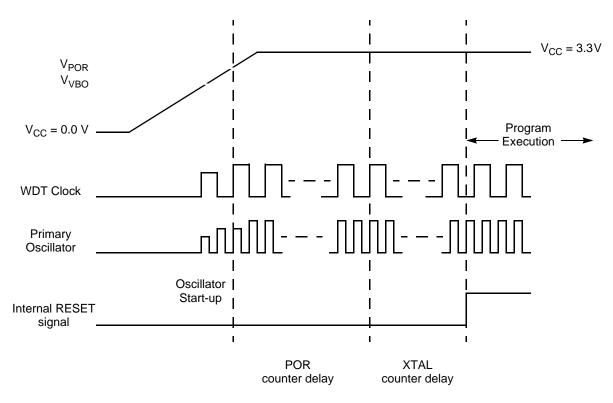

Each device in the Z8 Encore! XP F64xx Series contains an internal Power-On Reset circuit. The POR circuit monitors the supply voltage and holds the device in the Reset state until the supply voltage reaches a safe operating level. After the supply voltage exceeds the POR voltage threshold ( $V_{POR}$ ), the POR Counter is enabled and counts 66 cycles of the Watchdog Timer oscillator. After the POR counter times out, the XTAL Counter is enabled to count a total of 16 system clock pulses. The devices are held in the Reset state until both the POR Counter and XTAL counter have timed out. After the Z8 Encore! XP F64xx Series devices exit the POR reset state, the eZ8 CPU fetches the Reset vector. Following Power-On Reset, the POR status bit in the Watchdog Timer Control (WDTCTL) Register is set to 1.

Figure 8 displays Power-On Reset operation. For the POR threshold voltage ( $V_{POR}$ ), see the <u>Electrical Characteristics</u> chapter on page 200.

Figure 8. Power-On Reset Operation

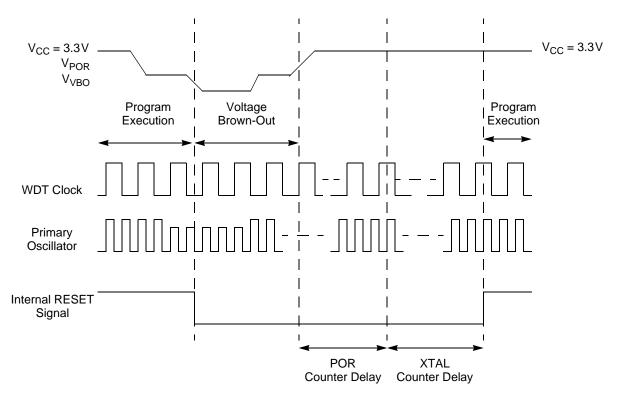

#### Voltage Brown-Out Reset

The devices in the Z8 Encore! XP F64xx Series provide low Voltage Brown-Out protection. The VBO circuit senses when the supply voltage drops to an unsafe level (below the VBO threshold voltage) and forces the device into the Reset state. While the supply voltage remains below the Power-On Reset voltage threshold ( $V_{POR}$ ), the VBO block holds the device in the Reset state.

After the supply voltage again exceeds the Power-On Reset voltage threshold, the devices progress through a full system reset sequence, as described in the Power-On Reset section. Following Power-On Reset, the POR status bit in the Watchdog Timer Control (WDTCTL) Register is set to 1. Figure 9 displays Voltage Brown-Out operation. For the VBO and POR threshold voltages ( $V_{VBO}$  and  $V_{POR}$ ), see the <u>Electrical Characteristics</u> chapter on page 200.

The Voltage Brown-Out circuit can be either enabled or disabled during STOP Mode. Operation during STOP Mode is set by the VBO\_AO option bit. For information about configuring VBO\_AO, see the <u>Option Bits</u> chapter on page 180.

Figure 9. Voltage Brown-Out Reset Operation

#### Table 24. Interrupt Request 0 Register (IRQ0)

| Bit          | 7            | 6                                                                                                                                                                                            | 5                                           | 4           | 3     | 2    | 1          | 0    |  |  |  |

|--------------|--------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------|-------------|-------|------|------------|------|--|--|--|

| Field        | T2I          | T1I                                                                                                                                                                                          | TOI                                         | U0RXI       | U0TXI | I2CI | SPII       | ADCI |  |  |  |

| RESET        |              | 0                                                                                                                                                                                            |                                             |             |       |      |            |      |  |  |  |

| R/W          |              |                                                                                                                                                                                              |                                             | R/          | W     |      |            |      |  |  |  |

| Address      |              |                                                                                                                                                                                              |                                             | FC          | 0H    |      |            |      |  |  |  |

| Bit          | Description  | n                                                                                                                                                                                            |                                             |             |       |      |            |      |  |  |  |

| [7]<br>T2I   | 0 = No inter | <b>Timer 2 Interrupt Request</b><br>0 = No interrupt request is pending for Timer 2.<br>1 = An interrupt request from Timer 2 is awaiting service.                                           |                                             |             |       |      |            |      |  |  |  |

| [6]<br>T1I   | 0 = No inter | <b>Timer 1 Interrupt Request</b><br>0 = No interrupt request is pending for Timer 1.<br>1 = An interrupt request from Timer 1 is awaiting service.                                           |                                             |             |       |      |            |      |  |  |  |

| [5]<br>T0I   | 0 = No inter | <b>Timer 0 Interrupt Request</b><br>0 = No interrupt request is pending for Timer 0.<br>1 = An interrupt request from Timer 0 is awaiting service.                                           |                                             |             |       |      |            |      |  |  |  |

| [4]<br>U0RXI | 0 = No inter | rrupt reques                                                                                                                                                                                 | rrupt Reque<br>t is pending<br>t from the U | for the UAR |       |      |            |      |  |  |  |

| [3]<br>UOTXI | 0 = No inter | UART 0 Transmitter Interrupt Request<br>0 = No interrupt request is pending for the UART 0 transmitter.<br>1 = An interrupt request from the UART 0 transmitter is awaiting service.         |                                             |             |       |      |            |      |  |  |  |

| [2]<br>I2CI  | 0 = No inter | <b>I</b> <sup>2</sup> <b>C</b> Interrupt Request<br>0 = No interrupt request is pending for the I <sup>2</sup> C.<br>1 = An interrupt request from the I <sup>2</sup> C is awaiting service. |                                             |             |       |      |            |      |  |  |  |

| [1]<br>SPII  | 0 = No inter | <b>SPI Interrupt Request</b><br>0 = No interrupt request is pending for the SPI.<br>1 = An interrupt request from the SPI is awaiting service.                                               |                                             |             |       |      |            |      |  |  |  |

| [0]<br>ADCI  | 0 = No inter |                                                                                                                                                                                              | <b>st</b><br>t is pending<br>t from the Ai  |             |       |      | g service. |      |  |  |  |

Every subsequent appropriate transition (after the first) of the timer input signal captures the current count value. The Capture value is written to the Timer PWM High and Low Byte Registers. When the capture event occurs, an interrupt is generated, the count value in the Timer High and Low Byte registers is reset to 0001H, and counting resumes.

If no capture event occurs, the timer counts up to the 16-bit compare value stored in the Timer Reload High and Low Byte registers. Upon reaching the compare value, the timer generates an interrupt, the count value in the Timer High and Low Byte registers is reset to 0001H and counting resumes.

Observe the following procedure for configuring a timer for CAPTURE/COMPARE Mode and initiating the count:

- 1. Write to the Timer Control 1 Register to:

- Disable the timer

- Configure the timer for CAPTURE/COMPARE Mode

- Set the prescale value

- Set the Capture edge (rising or falling) for the timer input

- 2. Write to the Timer High and Low Byte registers to set the starting count value (typically 0001H).

- 3. Write to the Timer Reload High and Low Byte registers to set the compare value.

- 4. If appropriate, enable the timer interrupt and set the timer interrupt priority by writing to the relevant interrupt registers.

- 5. Configure the associated GPIO port pin for the timer input alternate function.

- 6. Write to the Timer Control 1 Register to enable the timer.

- 7. Counting begins on the first appropriate transition of the timer input signal. No interrupt is generated by this first edge.

In COMPARE Mode, the elapsed time from timer start to capture event can be calculated using the following equation:

Capture Elapsed Time (s) =  $\frac{(Capture Value - Start Value) \times Prescale}{System Clock Frequency (Hz)}$

#### **Reading the Timer Count Values**

The current count value in the timers can be read while counting (enabled). This capability has no effect on timer operation. When the timer is enabled and the Timer High Byte Register is read, the contents of the Timer Low Byte Register are placed in a holding register. A subsequent read from the Timer Low Byte Register returns the value in the holding reg-

# Watchdog Timer

The Watchdog Timer (WDT) helps protect against corrupt or unreliable software, power faults and other system-level problems which can place the Z8 Encore! XP F64xx Series MCU into unsuitable operating states. The features of the Watchdog Timer include:

- On-chip RC oscillator

- A selectable time-out response

- WDT time-out response: Reset or interrupt

- 24-bit programmable time-out value

## Operation

The Watchdog Timer is a retriggerable one-shot timer that resets or interrupts the Z8 Encore! XP F64xx Series devices when the WDT reaches its terminal count. The Watchdog Timer uses its own dedicated on-chip RC oscillator as its clock source. The Watchdog Timer has only two modes of operation: ON and OFF. After it is enabled, it always counts and must be refreshed to prevent a time-out. An enable can be performed by executing the WDT instruction or by setting the WDT\_AO option bit. This WDT\_AO bit enables the Watchdog Timer to operate continuously, even if a WDT instruction has not been executed.

The Watchdog Timer is a 24-bit reloadable downcounter that uses three 8-bit registers in the eZ8 CPU register space to set the reload value. The nominal WDT time-out period is calculated using the following equation:

WDT Time-out Period (ms) =  $\frac{\text{WDT Reload Value}}{10}$

In the above equation, the WDT reload value is the decimal value of the 24-bit value provided by {WDTU[7:0], WDTH[7:0], WDTL[7:0]}; the typical Watchdog Timer RC oscillator frequency is 10kHz. The Watchdog Timer cannot be refreshed after it reaches 000002H. The WDT reload value must not be set to values below 000004H.

Table 47 lists approximate time-out delays for the minimum and maximum WDT reload values.

# Infrared Encoder/Decoder

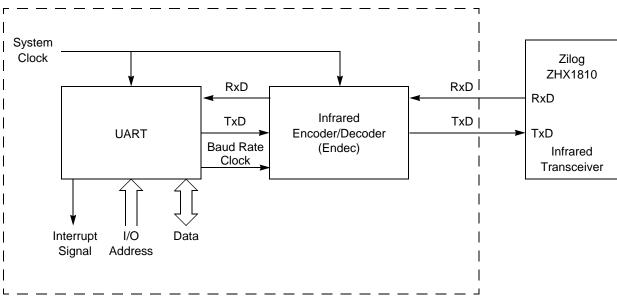

The Z8 Encore! XP F64xx Series products contain two fully-functional, high-performance UART-to-infrared encoders/decoders (endecs). Each infrared endec is integrated with an on-chip UART to allow easy communication between the Z8 Encore! XP F64xx Series and IrDA Physical Layer Specification Version 1.3-compliant infrared transceivers. Infrared communication provides secure, reliable, low-cost, point-to-point communication between PCs, PDAs, cell phones, printers, and other infrared enabled devices.

## Architecture

Figure 19 displays the architecture of the infrared endec.

Figure 19. Infrared Data Communication System Block Diagram

# Operation

When the infrared endec is enabled, the transmit data from the associated on-chip UART is encoded as digital signals in accordance with the IrDA standard and output to the infrared transceiver via the TxD pin. Likewise, data received from the infrared transceiver is passed to the infrared endec via the RxD pin, decoded by the infrared endec, and then

#### Transfer Format PHASE Equals One

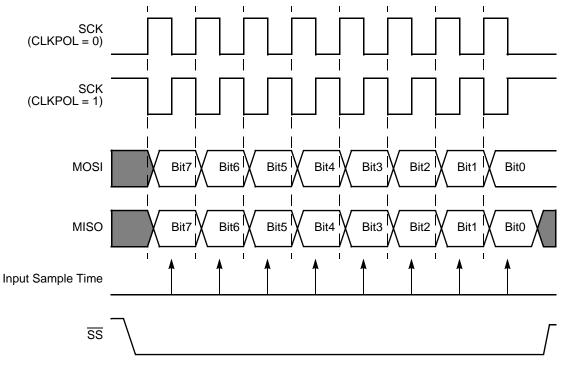

Figure 26 displays the timing diagram for an SPI transfer in which PHASE is 1. Two waveforms are depicted for SCK, one for CLKPOL reset to 0 and another for CLKPOL set to 1.

Figure 26. SPI Timing When PHASE is 1

#### **Multimaster Operation**

In a multimaster SPI system, all SCK pins are tied together, all MOSI pins are tied together and all MISO pins are tied together. All SPI pins must then be configured in OPEN-DRAIN mode to prevent bus contention. At any one time, only one SPI device is configured as the Master and all other SPI devices on the bus are configured as Slaves. The Master enables a single Slave by asserting the  $\overline{SS}$  pin on that Slave only. Then, the single Master drives data out its SCK and MOSI pins to the SCK and MOSI pins on the Slaves (including those which are not enabled). The enabled Slave drives data out its MISO pin to the MISO Master pin.

For a Master device operating in a multimaster system, if the  $\overline{SS}$  pin is configured as an input and is driven Low by another Master, the COL bit is set to 1 in the SPI Status Register. The COL bit indicates the occurrence of a multimaster collision (mode fault error condition).

## DMAx Control Register

The DMA*x* Control Register, shown in Table 78, enables and selects the mode of operation for DMA*x*.

#### Table 78. DMAx Control Register (DMAxCTL)

| Bit          | 7                                                                                                                                                                                                                                                                                   | 6           | 5    | 4     | 3    | 2   | 1 | 0         |

|--------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------|------|-------|------|-----|---|-----------|

| Field        | DEN                                                                                                                                                                                                                                                                                 | DLE         | DDIR | IRQEN | WSEL | RSS |   |           |

| RESET        |                                                                                                                                                                                                                                                                                     |             |      | (     | )    |     |   |           |

| R/W          |                                                                                                                                                                                                                                                                                     |             |      | R/    | W    |     |   |           |

| Address      |                                                                                                                                                                                                                                                                                     |             |      | FB0H, | FB8H |     |   |           |

| Bit          | Description                                                                                                                                                                                                                                                                         | Description |      |       |      |     |   |           |

| [7]<br>DEN   | <ul> <li>DMAx Enable</li> <li>0 = DMAx is disabled and data transfer requests are disregarded.</li> <li>1 = DMAx is enabled and initiates a data transfer upon receipt of a request from the trigger source.</li> </ul>                                                             |             |      |       |      |     |   | e trigger |

| [6]<br>DLE   | <ul> <li>DMAx Loop Enable</li> <li>0 = DMAx reloads the original Start Address and is then disabled after the End Address data is transferred.</li> <li>1 = DMAx, after the End Address data is transferred, reloads the original Start Address and continues operating.</li> </ul> |             |      |       |      |     |   |           |

| [5]<br>DDIR  | <b>DMA</b> <i>x</i> <b>Data Transfer Direction</b><br>$0 = \text{Register File} \rightarrow \text{on-chip peripheral control register.}$<br>$1 = \text{On-chip peripheral control} \rightarrow \text{Register File.}$                                                               |             |      |       |      |     |   |           |

| [4]<br>IRQEN | <ul> <li>DMAx Interrupt Enable</li> <li>0 = DMAx does not generate any interrupts.</li> <li>1 = DMAx generates an interrupt when the End Address data is transferred.</li> </ul>                                                                                                    |             |      |       |      |     |   |           |

### **DMA Control of the ADC**

The Direct Memory Access (DMA) Controller can control operation of the ADC including analog input selection and conversion enable. For more information about the DMA and configuring for ADC operations, see the <u>Direct Memory Access Controller</u> chapter on page 150.

# **ADC Control Register Definitions**

This section defines the features of the following ADC Control registers.

ADC Control Register: see page 165

ADC Data High Byte Register: see page 167

ADC Data Low Bits Register: see page 168

## **ADC Control Register**

The ADC Control Register selects the analog input channel and initiates the analog-to-digital conversion.

| Bit     | 7   | 6        | 5    | 4    | 3          | 2 | 1 | 0 |   |  |  |  |

|---------|-----|----------|------|------|------------|---|---|---|---|--|--|--|

| Field   | CEN | Reserved | VREF | CONT | ANAIN[3:0] |   |   |   |   |  |  |  |

| RESET   | (   | )        | 1    |      | 0          |   |   |   | 0 |  |  |  |

| R/W     |     |          |      | R/W  |            |   |   |   |   |  |  |  |

| Address |     |          |      | F7   | 0H         |   |   |   |   |  |  |  |

| Table 87. | ADC Control | Register | (ADCCTL) |

|-----------|-------------|----------|----------|

|-----------|-------------|----------|----------|

| Bit         | Description                                                                                                                                                                                                                                                                                                                                                                                                            |

|-------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| [7]<br>CEN  | <ul> <li>Conversion Enable</li> <li>0 = Conversion is complete. Writing a 0 produces no effect. The ADC automatically clears this bit to 0 when a conversion has been completed.</li> <li>1 = Begin conversion. Writing a 1 to this bit starts a conversion. If a conversion is already in progress, the conversion restarts. This bit remains 1 until the conversion is complete.</li> </ul>                          |

| [6]         | <b>Reserved</b><br>This bit is reserved and must be programmed to 0.                                                                                                                                                                                                                                                                                                                                                   |

| [5]<br>VREF | <ul> <li>Voltage Reference</li> <li>0 = Internal voltage reference generator enabled. The V<sub>REF</sub> pin should be left unconnected (or capacitively coupled to analog ground) if the internal voltage reference is selected as the ADC reference voltage.</li> <li>1 = Internal voltage reference generator disabled. An external voltage reference must be provided through the V<sub>REF</sub> pin.</li> </ul> |

## ADC Data High Byte Register

The ADC Data High Byte Register, shown in Table 88, contains the upper eight bits of the 10-bit ADC output. During a single-shot conversion, this value is invalid. Access to the ADC Data High Byte Register is read-only. The full 10-bit ADC result is provided by {ADCD\_H[7:0], ADCD\_L[7:6]}. Reading the ADC Data High Byte Register latches data in the ADC Low Bits Register.

| Bit     | 7           | 6 | 5 | 4 | 3 | 2 | 1 | 0 |  |

|---------|-------------|---|---|---|---|---|---|---|--|

| Field   | ADCD_H      |   |   |   |   |   |   |   |  |

| RESET   |             | Х |   |   |   |   |   |   |  |

| R/W     |             | R |   |   |   |   |   |   |  |

| Address | F72H        |   |   |   |   |   |   |   |  |

| Bit     | Description |   |   |   |   |   |   |   |  |

#### Table 88. ADC Data High Byte Register (ADCD\_H)

[7:0] ADC Data High Byte

ADCD\_H This byte contains the upper eight bits of the 10-bit ADC output. These bits are not valid during a single-shot conversion. During a continuous conversion, the last conversion output is held in this register. These bits are undefined after a Reset.

For more information about bypassing the Flash Controller, refer to the <u>Third Party Flash</u> <u>Programming Support for Z8 Encore! MCUs Application Note (AN0117)</u>, which is available for download at <u>www.zilog.com</u>.

### Flash Controller Behavior in Debug Mode

The following changes in Flash Controller behavior occur when the Flash Controller is accessed using the On-Chip Debugger:

- The Flash Write Protect option bit is ignored

- The Flash Sector Protect Register is ignored for programming and erase operations

- Programming operations are not limited to the page selected in the Page Select Register

- Bits in the Flash Sector Protect Register can be written to one or zero

- The second write of the Page Select Register to unlock the Flash Controller is not necessary

- The Page Select Register can be written when the Flash Controller is unlocked

- The Mass Erase command is enabled through the Flash Control Register

**Caution:** For security reasons, the Flash Controller allows only a single page to be opened for write/erase operations. When writing multiple Flash pages, the Flash Controller must go through the unlock sequence again to select another page.

## **Flash Control Register Definitions**

This section defines the features of the following Flash Control registers.

Flash Control Register: see page 175

Flash Status Register: see page 177

Page Select Register: see page 177

Flash Sector Protect Register: see page 178

Flash Frequency High and Low Byte Registers: see page 179

## **Flash Control Register**

The Flash Control Register, shown in Table 93, unlocks the Flash Controller for programming and erase operations, or to select the Flash Sector Protect Register.

PRELIMINARY

209

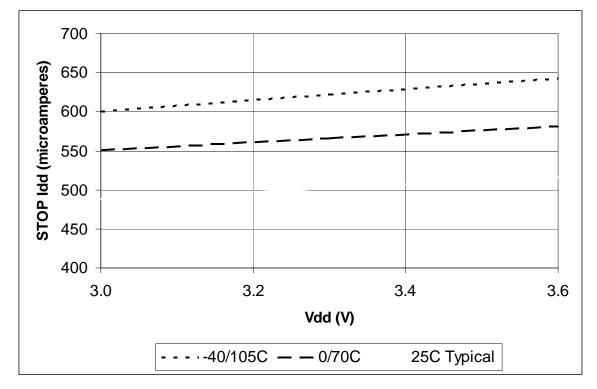

Figure 47 displays the maximum current consumption in STOP Mode with the VBO and Watchdog Timer enabled plotted opposite the power supply voltage. All GPIO pins are configured as outputs and driven High.

Figure 47. Maximum STOP Mode  $\mathrm{I}_{\mathrm{DD}}$  with VBO Enabled vs. Power Supply Voltage

Table 111 list the Flash memory electrical characteristics and timing.

|                                                  |         | <sub>DD</sub> = 3.0–3.<br>–40°C to 1 |         |        |                                                                                                                                                                |

|--------------------------------------------------|---------|--------------------------------------|---------|--------|----------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Parameter                                        | Minimum | Typical                              | Maximum | Units  | Notes                                                                                                                                                          |

| Flash Byte Read Time                             | 50      | _                                    | -       | ns     |                                                                                                                                                                |

| Flash Byte Program<br>Time                       | 20      | _                                    | 40      | μs     |                                                                                                                                                                |

| Flash Page Erase Time                            | 10      | _                                    | -       | ms     |                                                                                                                                                                |

| Flash Mass Erase Time                            | 200     | _                                    | -       | ms     |                                                                                                                                                                |

| Writes to Single<br>Address Before Next<br>Erase | -       | _                                    | 2       |        |                                                                                                                                                                |

| Flash Row Program<br>Time                        | _       | _                                    | 8       | ms     | Cumulative program time for single<br>row cannot exceed limit before next<br>erase. This parameter is only an<br>issue when bypassing the Flash<br>Controller. |

| Data Retention                                   | 100     | _                                    | _       | years  | 25°C                                                                                                                                                           |

| Endurance, –40°C to 105°C                        | 10,000  | -                                    | -       | cycles | Program/erase cycles                                                                                                                                           |

| Endurance, 106°C to 125°C                        | 1,000   | -                                    | -       | cycles | Program/erase cycles                                                                                                                                           |

Table 112 lists the Watchdog Timer electrical characteristics and timing.

|                  |                                                               |         | <sub>DD</sub> = 3.0–3.<br>–40°C to 1 |         |       |            |

|------------------|---------------------------------------------------------------|---------|--------------------------------------|---------|-------|------------|

| Symbol           | Parameter                                                     | Minimum | Typical                              | Maximum | Units | Conditions |

| F <sub>WDT</sub> | WDT Oscillator<br>Frequency                                   | 5       | 10                                   | 20      | kHz   |            |

| I <sub>WDT</sub> | WDT Oscillator Current<br>including internal RC<br>Oscillator | _       | <1                                   | 5       | μA    |            |

213

Table 113 provides electrical characteristics and timing information for the Analog-to-Digital Converter. Figure 49 displays the input frequency response of the ADC.

|                   |                                                             | V <sub>DI</sub><br>T <sub>A</sub> = | o = 3.0V–3<br>−40°C to 1 | .6V<br>25°C      |        |                                                                                                                                                        |

|-------------------|-------------------------------------------------------------|-------------------------------------|--------------------------|------------------|--------|--------------------------------------------------------------------------------------------------------------------------------------------------------|

| Symbol            | Parameter                                                   | Minimum                             | Typical                  | Maximum          | Units  | Conditions                                                                                                                                             |

|                   | Resolution                                                  | 10                                  | _                        | _                | bits   | External V <sub>REF</sub> = 3.0V;                                                                                                                      |

|                   | Differential Nonlinearity<br>(DNL)                          | -1.0                                |                          | +1.0             | lsb    | Guaranteed by design                                                                                                                                   |

|                   | Integral Nonlinearity<br>(INL)                              | -3.0                                | <u>+</u> 1.0             | 3.0              | lsb    | External $V_{REF} = 3.0 V$                                                                                                                             |

|                   | DC Offset Error                                             | -35                                 | -                        | 25               | mV     | 80-pin QFP and 64-pin<br>LQFP packages.                                                                                                                |

|                   | DC Offset Error                                             | -50                                 | _                        | 25               | mV     | 44-pin LQFP, 44-pin<br>PLCC, and 68-pin PLCC<br>packages.                                                                                              |

| V <sub>REF</sub>  | Internal Reference<br>Voltage                               | 1.9                                 | 2.0                      | 2.4              | V      | $V_{DD} = 3.0 V - 3.6 V$<br>$T_A = -40^{\circ}C \text{ to } 105^{\circ}C$                                                                              |

| VC <sub>REF</sub> | Voltage Coefficient of<br>Internal Reference<br>Voltage     | -                                   | 78                       | _                | mV/V   | $V_{REF}$ variation as a function of $AV_{DD}$ .                                                                                                       |

| TC <sub>REF</sub> | Temperature<br>Coefficient of Internal<br>Reference Voltage | -                                   | 1                        | _                | mV/°C  |                                                                                                                                                        |

|                   | Single-Shot<br>Conversion Period                            | _                                   | 5129                     | _                | cycles | System clock cycles                                                                                                                                    |

|                   | Continuous Conversion<br>Period                             | -                                   | 256                      | _                | cycles | System clock cycles                                                                                                                                    |

| R <sub>S</sub>    | Analog Source<br>Impedance                                  | -                                   | -                        | 150              | W      | Recommended                                                                                                                                            |

| Zin               | Input Impedance                                             |                                     | 150                      |                  | kΩ     | 20MHz system clock.<br>Input impedance<br>increases with lower system clock frequency.                                                                 |

| V <sub>REF</sub>  | External Reference<br>Voltage                               |                                     |                          | AV <sub>DD</sub> | V      | $AV_{DD} \le V_{DD}$ . When<br>using an external refer-<br>ence voltage, decouplin<br>capacitance should be<br>placed from $V_{REF}$ to<br>$AV_{SS}$ . |

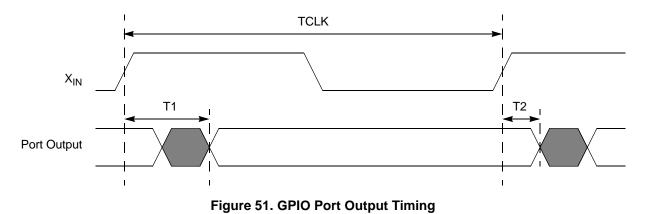

## General-Purpose I/O Port Output Timing

Figure 51 and Table 116 provide timing information for GPIO port pins.

| Table 116 | . GPIO | Port | Output | Timing |

|-----------|--------|------|--------|--------|

|           |        |      |        |        |

|                |                                                 | Delay (ns) |         |  |  |  |  |

|----------------|-------------------------------------------------|------------|---------|--|--|--|--|

| Parameter      | Abbreviation                                    | Minimum    | Maximum |  |  |  |  |

| GPIO port pins |                                                 |            |         |  |  |  |  |

| T <sub>1</sub> | X <sub>IN</sub> Rise to Port Output Valid Delay | -          | 20      |  |  |  |  |

| T <sub>2</sub> | X <sub>IN</sub> Rise to Port Output Hold Time   | 2          | -       |  |  |  |  |

| Mnemonic | Operands | Instruction                                         |

|----------|----------|-----------------------------------------------------|

| AND      | dst, src | Logical AND                                         |

| ANDX     | dst, src | Logical AND using Extended Addressing               |

| COM      | dst      | Complement                                          |

| OR       | dst, src | Logical OR                                          |

| ORX      | dst, src | Logical OR using Extended Addressing                |

| XOR      | dst, src | Logical Exclusive OR                                |

| XORX     | dst, src | Logical Exclusive OR using Extended Address-<br>ing |

#### Table 133. Logical Instructions

#### Table 134. Program Control Instructions

| Mnemonic | Operands        | Instruction                   |

|----------|-----------------|-------------------------------|

| BRK      |                 | On-Chip Debugger Break        |

| BTJ      | p, bit, src, DA | Bit Test and Jump             |

| BTJNZ    | bit, src, DA    | Bit Test and Jump if Non-Zero |

| BTJZ     | bit, src, DA    | Bit Test and Jump if Zero     |

| CALL     | dst             | Call Procedure                |

| DJNZ     | dst, src, RA    | Decrement and Jump Non-Zero   |

| IRET     | —               | Interrupt Return              |

| JP       | dst             | Jump                          |

| JP cc    | dst             | Jump Conditional              |

| JR       | DA              | Jump Relative                 |

| JR cc    | DA              | Jump Relative Conditional     |

| RET      | —               | Return                        |

| TRAP     | vector          | Software Trap                 |

| Assembly      |                                                                          | Address<br>Mode |     | _ Opcode(s) | Flags |   |   |   |   | Fetch | Instr. |        |

|---------------|--------------------------------------------------------------------------|-----------------|-----|-------------|-------|---|---|---|---|-------|--------|--------|

| Mnemonic      | Symbolic Operation                                                       | dst             | src | (Hex)       | С     | Ζ | S | ۷ | D | Н     |        | Cycles |

| POPX dst      | dst $\leftarrow @SP$<br>SP $\leftarrow$ SP + 1                           | ER              |     | D8          | -     | - | - | _ | _ | -     | 3      | 2      |

| PUSH src      | $SP \leftarrow SP - 1$                                                   | R               |     | 70          | _     | _ | _ | _ | _ | _     | 2      | 2      |

|               | $@SP \leftarrow src$                                                     | IR              |     | 71          | -     |   |   |   |   |       | 2      | 3      |

|               | -                                                                        | IM              |     | 1F 70       | -     |   |   |   |   |       | 3      | 2      |

| PUSHX src     | $SP \leftarrow SP - 1$<br>@SP \leftarrow src                             | ER              |     | C8          | -     | _ | _ | _ | _ | -     | 3      | 2      |

| RCF           | C ← 0                                                                    |                 |     | CF          | 0     | _ | _ | _ | _ | _     | 1      | 2      |

| RET           | $\begin{array}{l} PC \leftarrow @SP \\ SP \leftarrow SP + 2 \end{array}$ |                 |     | AF          | -     | - | - | _ | _ | -     | 1      | 4      |

| RL dst        |                                                                          | R               |     | 90          | *     | * | * | * | _ | -     | 2      | 2      |

|               | C 		 D7 D6 D5 D4 D3 D2 D1 D0 		 dst                                      | IR              |     | 91          | _     |   |   |   |   |       | 2      | 3      |

| RLC dst       |                                                                          | R               |     | 10          | *     | * | * | * | _ | -     | 2      | 2      |

|               | C                                                                        | IR              |     | 11          | -     |   |   |   |   |       | 2      | 3      |

| RR dst        |                                                                          | R               |     | E0          | *     | * | * | * | - | -     | 2      | 2      |

|               | ► D7 D6 D5 D4 D3 D2 D1 D0 ► C                                            | IR              |     | E1          | -     |   |   |   |   |       | 2      | 3      |

| RRC dst       |                                                                          | R               |     | C0          | *     | * | * | * | _ | -     | 2      | 2      |

|               | ► D7 D6 D5 D4 D3 D2 D1 D0 ► C                                            | IR              |     | C1          | -     |   |   |   |   |       | 2      | 3      |

| SBC dst, src  | $dst \gets dst - src - C$                                                | r               | r   | 32          | *     | * | * | * | 1 | *     | 2      | 3      |

|               | -                                                                        | r               | lr  | 33          | -     |   |   |   |   |       | 2      | 4      |

|               | -                                                                        | R               | R   | 34          | -     |   |   |   |   |       | 3      | 3      |

|               | -                                                                        | R               | IR  | 35          | _     |   |   |   |   |       | 3      | 4      |

|               | -                                                                        | R               | IM  | 36          | _     |   |   |   |   |       | 3      | 3      |

|               | -                                                                        | IR              | IM  | 37          | _     |   |   |   |   |       | 3      | 4      |

| SBCX dst, src | $dst \gets dst - src - C$                                                | ER              | ER  | 38          | *     | * | * | * | 1 | *     | 4      | 3      |

|               | -                                                                        | ER              | IM  | 39          | -     |   |   |   |   |       | 4      | 3      |

| SCF           | C ← 1                                                                    |                 |     | DF          | 1     | _ | - | _ | _ | -     | 1      | 2      |

#### Table 136. eZ8 CPU Instruction Summary (Continued)

Note: Flags Notation:

\* = Value is a function of the result of the operation.

- = Unaffected.

X = Undefined.

0 = Reset to 0.

1 = Set to 1.

# Packaging

Zilog's F64xx Series of MCUs includes the Z8F1621, Z8F2421, Z8F3221, Z8F4821 and Z8F6421 devices, which are available in the following packages:

- 40-pin Pin Dual Inline Package (PDIP)

- 44-pin Low Profile Quad Flat Package (LQFP)

- 44-pin Plastic Lead Chip Carrier (PLCC)

Zilog's F64xx Series of MCUs also includes the Z8F1622, Z8F2422, Z8F3222, Z8F4822 and Z8F6422 devices, which are available in the following packages:

- 64-pin Low-Profile Quad Flat Package (LQFP)

- 68-pin Plastic Lead Chip Carrier (PLCC)

Lastly, Zilog's F64xx Series of MCUs includes the Z8F4823 and Z8F6423 devices, which are available in the following package:

• 80-pin Quad Flat Package (QFP)

Current diagrams for each of these packages are published in Zilog's <u>Packaging Product</u> <u>Specification (PS0072)</u>, which is available free for download from the Zilog website.

SPI status (SPISTAT) 124, 265 status, I2C 143 status, SPI 124 UARTx baud rate high byte (UxBRH) 107, 259, 262 UARTx baud rate low byte (UxBRL) 107, 260, 262 UARTx Control 0 (UxCTL0) 103, 106, 258, 259, 261 UARTx control 1 (UxCTL1) 104, 259, 261 UARTx receive data (UxRXD) 100, 258, 260 UARTx status 0 (UxSTAT0) 101, 258, 260 UARTx status 1 (UxSTAT1) 102, 259, 261 UARTx transmit data (UxTXD) 100, 258, 260 watchdog timer control (WDTCTL) 85, 283 watchdog timer reload high byte (WDTH) 87, 284 watchdog timer reload low byte (WDTL) 87, 284 watchdog timer reload upper byte (WDTU) 86, 283 register file 19 register file address map 23 register pair 229 register pointer 229 reset and STOP mode characteristics 29 carry flag 232 controller 6 sources 30 **RET 234** return 234 RL 235 **RLC 235** rotate and shift instructions 235 rotate left 235 rotate left through carry 235 rotate right 235 rotate right through carry 235 RP 229 RR 229, 235 rr 229 **RRC 235**

## S

**SBC 232** SCF 232. 233 SDA and SCL (IrDA) signals 131 second opcode map after 1FH 248 serial clock 117 serial peripheral interface (SPI) 114 set carry flag 232, 233 set register pointer 233 shift right arithmetic 235 shift right logical 235 signal descriptions 15 single-shot conversion (ADC) 164 SIO 6 slave data transfer formats (I2C) 137 slave select 117 software trap 234 source operand 229 SP 229 SPI architecture 114 baud rate generator 121 baud rate high and low byte register 127 clock phase 117 configured as slave 115 control register 123 control register definitions 122 data register 122 error detection 120 interrupts 121 mode fault error 120 mode register 126 multi-master operation 119 operation 116 overrun error 120 signals 116 single master, multiple slave system 115 single master, single slave system 114 status register 124 timing, PHASE = 0.118timing, PHASE=1 119 SPI controller signals 15 SPI mode (SPIMODE) 126, 265 SPIBRH register 128, 266