# E·XFL

Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Product Status             | Active                                                    |

|----------------------------|-----------------------------------------------------------|

| Core Processor             | eZ8                                                       |

| Core Size                  | 8-Bit                                                     |

| Speed                      | 20MHz                                                     |

| Connectivity               | I <sup>2</sup> C, IrDA, SPI, UART/USART                   |

| Peripherals                | Brown-out Detect/Reset, DMA, POR, PWM, WDT                |

| Number of I/O              | 31                                                        |

| Program Memory Size        | 48KB (48K x 8)                                            |

| Program Memory Type        | FLASH                                                     |

| EEPROM Size                | -                                                         |

| RAM Size                   | 4K x 8                                                    |

| Voltage - Supply (Vcc/Vdd) | 3V ~ 3.6V                                                 |

| Data Converters            | A/D 8x10b                                                 |

| Oscillator Type            | Internal                                                  |

| Operating Temperature      | -40°C ~ 105°C (TA)                                        |

| Mounting Type              | Surface Mount                                             |

| Package / Case             | 44-LQFP                                                   |

| Supplier Device Package    | 44-LQFP (10x10)                                           |

| Purchase URL               | https://www.e-xfl.com/product-detail/zilog/z8f4821an020eg |

|                            |                                                           |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

## Z8 Encore! XP<sup>®</sup> F64xx Series Product Specification

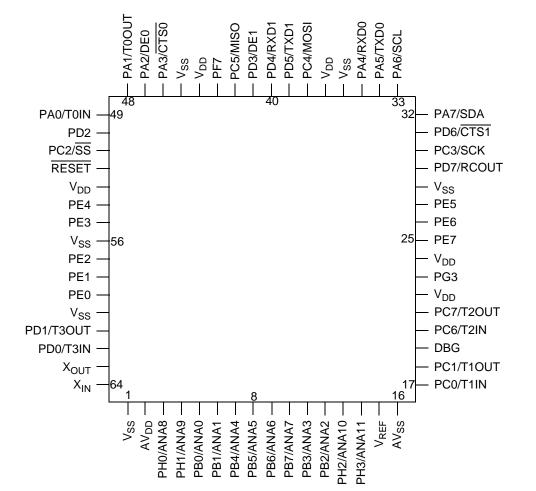

Figure 5. Z8 Encore! XP F64xx Series in 64-Pin Low-Profile Quad Flat Package (LQFP)

## Z8 Encore! XP<sup>®</sup> F64xx Series Product Specification

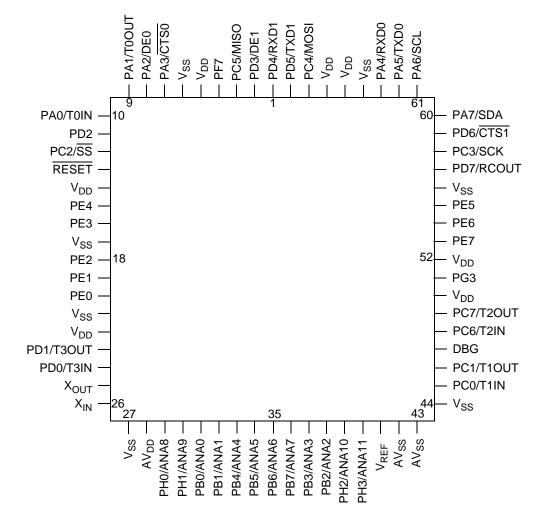

Figure 6. Z8 Encore! XP F64xx Series in 68-Pin Plastic Leaded Chip Carrier (PLCC)

|        |         |            | Alternate i unction mapping                       |

|--------|---------|------------|---------------------------------------------------|

| Port   | Pin     | Mnemonic   | Alternate Function Description                    |

| Port A | PA0     | TOIN       | Timer 0 Input                                     |

|        | PA1     | TOOUT      | Timer 0 Output                                    |

|        | PA2     | DE0        | UART 0 Driver Enable                              |

|        | PA3     | CTS0       | UART 0 Clear to Send                              |

|        | PA4     | RXD0/IRRX0 | UART 0/IrDA 0 Receive Data                        |

|        | PA5     | TXD0/IRTX0 | UART 0/IrDA 0 Transmit Data                       |

|        | PA6     | SCL        | I <sup>2</sup> C Clock (automatically open-drain) |

|        | PA7     | SDA        | I <sup>2</sup> C Data (automatically open-drain)  |

| Port B | PB0     | ANA0       | ADC analog input 0                                |

|        | PB1     | ANA1       | ADC analog input 1                                |

|        | PB2     | ANA2       | ADC analog input 2                                |

|        | PB3     | ANA3       | ADC analog input 3                                |

|        | PB4     | ANA4       | ADC analog input 4                                |

|        | PB5     | ANA5       | ADC analog input 5                                |

|        | PB6     | ANA6       | ADC analog input 6                                |

|        | PB7     | ANA7       | ADC analog input 7                                |

| Port C | PC0     | T1IN       | Timer 1 Input                                     |

|        | PC1     | T1OUT      | Timer 1 Output                                    |

|        | PC2     | SS         | SPI Slave Select                                  |

|        | PC3     | SCK        | SPI Serial Clock                                  |

|        | PC4     | MOSI       | SPI Master Out/Slave In                           |

|        | PC5     | MISO       | SPI Master In/Slave Out                           |

|        | PC6     | T2IN       | Timer 2 In                                        |

|        | PC7     | T2OUT      | Timer 2 Out                                       |

| Port D | PD0     | T3IN       | Timer 3 In (unavailable in the 44-pin package)    |

|        | PD1     | T3OUT      | Timer 3 Out (unavailable in the 44-pin package)   |

|        | PD2     | N/A        | No alternate function                             |

|        | PD3     | DE1        | UART 1 Driver Enable                              |

|        | PD4     | RXD1/IRRX1 | UART 1/IrDA 1 Receive Data                        |

|        | PD5     | TXD1/IRTX1 | UART 1/IrDA 1 Transmit Data                       |

|        | PD6     | CTS1       | UART 1 Clear to Send                              |

|        | PD7     | RCOUT      | Watchdog Timer RC Oscillator Output               |

| Port E | PE[7:0] | N/A        | No alternate functions                            |

|        |         |            |                                                   |

## Table 12. Port Alternate Function Mapping

#### Table 53. UART Transmit Data Register (UxTXD)

| Bit     | 7   | 6 | 5 | 4       | 3       | 2 | 1 | 0 |  |  |

|---------|-----|---|---|---------|---------|---|---|---|--|--|

| Field   | TXD |   |   |         |         |   |   |   |  |  |

| RESET   |     | X |   |         |         |   |   |   |  |  |

| R/W     |     | W |   |         |         |   |   |   |  |  |

| Address |     |   |   | F40H ar | nd F48H |   |   |   |  |  |

| Bit   | Description                                                        |

|-------|--------------------------------------------------------------------|

| [7:0] | Transmit Data                                                      |

| TXD   | UART transmitter data byte to be shifted out through the TXDx pin. |

# **UART Receive Data Register**

Data bytes received through the RXD*x* pin are stored in the UART Receive Data Register, shown in Table 54. The read-only UART Receive Data Register shares a Register File address with the write-only UART Transmit Data Register.

#### Table 54. UART Receive Data Register (UxRXD)

| Bit     | 7   | 6 | 5 | 4       | 3       | 2 | 1 | 0 |  |  |

|---------|-----|---|---|---------|---------|---|---|---|--|--|

| Field   | RXD |   |   |         |         |   |   |   |  |  |

| RESET   |     | X |   |         |         |   |   |   |  |  |

| R/W     |     | R |   |         |         |   |   |   |  |  |

| Address |     |   |   | F40H ar | nd F48H |   |   |   |  |  |

| Bit   | Description                                |

|-------|--------------------------------------------|

| [7:0] | Receive Data                               |

| RXD   | UART receiver data byte from the RXDx pin. |

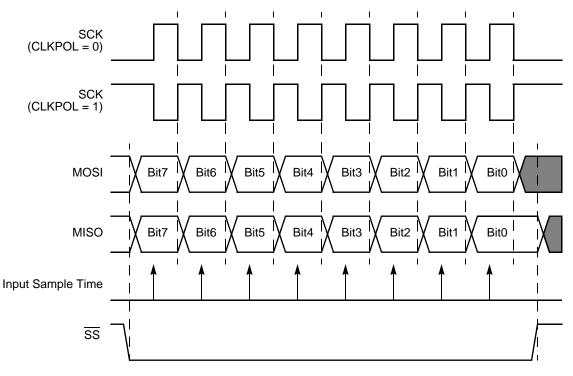

| PHASE | CLKPOL | SCK Transmit<br>Edge | SCK Receive<br>Edge | SCK Idle<br>State |

|-------|--------|----------------------|---------------------|-------------------|

| 0     | 0      | Falling              | Rising              | Low               |

| 0     | 1      | Rising               | Falling             | High              |

| 1     | 0      | Rising               | Falling             | Low               |

| 1     | 1      | Falling              | Rising              | High              |

#### Table 63. SPI Clock Phase (PHASE) and Clock Polarity (CLKPOL) Operation

## **Transfer Format PHASE Equals Zero**

Figure 25 displays the timing diagram for an SPI transfer in which PHASE is cleared to 0. The two SCK waveforms show polarity with CLKPOL reset to 0 and with CLKPOL set to one. The diagram may be interpreted as either a Master or Slave timing diagram because the SCK Master-In/Slave-Out (MISO) and Master-Out/Slave-In (MOSI) pins are directly connected between the Master and the Slave.

Figure 25. SPI Timing When PHASE is 0

- 2. Software asserts the TXI bit of the  $I^2C$  Control Register to enable transmit interrupts.

- 3. The  $I^2C$  interrupt asserts because the  $I^2C$  Data Register is empty.

- 4. Software responds to the TDRE interrupt by writing the first slave address byte to the I<sup>2</sup>C Data Register. The least significant bit must be 0 for the write operation.

- 5. Software asserts the start bit of the  $I^2C$  Control Register.

- 6. The I<sup>2</sup>C Controller sends the start condition to the I<sup>2</sup>C slave.

- 7. The I<sup>2</sup>C Controller loads the I<sup>2</sup>C Shift Register with the contents of the I<sup>2</sup>C Data Register.

- 8. After one bit of address is shifted out by the SDA signal, the transmit interrupt is asserted.

- 9. Software responds by writing the second byte of address into the contents of the I<sup>2</sup>C Data Register.

- 10. The I<sup>2</sup>C Controller shifts the rest of the first byte of address and write bit out the SDA signal.

- 11. If the I<sup>2</sup>C slave acknowledges the first address byte by pulling the SDA signal Low during the next High period of SCL, the I<sup>2</sup>C Controller sets the ACK bit in the I<sup>2</sup>C Status Register. Continue with <u>Step 12</u>.

If the slave does not acknowledge the first address byte, the I<sup>2</sup>C Controller sets the NCKI bit and clears the ACK bit in the I<sup>2</sup>C Status Register. Software responds to the Not Acknowledge interrupt by setting the stop and flush bits and clearing the TXI bit. The I<sup>2</sup>C Controller sends the stop condition on the bus and clears the stop and NCKI bits. The transaction is complete (ignore the following steps).

- 12. The I<sup>2</sup>C Controller loads the I<sup>2</sup>C Shift Register with the contents of the I<sup>2</sup>C Data Register.

- 13. The I<sup>2</sup>C Controller shifts the second address byte out the SDA signal. After the first bit has been sent, the transmit interrupt is asserted.

- 14. Software responds by writing a data byte to the  $I^2C$  Data Register.

- 15. The I<sup>2</sup>C Controller completes shifting the contents of the shift register on the SDA signal.

- 16. If the I<sup>2</sup>C slave sends an acknowledge by pulling the SDA signal Low during the next High period of SCL, the I<sup>2</sup>C Controller sets the ACK bit in the I<sup>2</sup>C Status Register. Continue with <u>Step 17</u>.

If the slave does not acknowledge the second address byte or one of the data bytes, the  $I^2C$  Controller sets the NCKI bit and clears the ACK bit in the  $I^2C$  Status Register. Software responds to the Not Acknowledge interrupt by setting the stop and flush bits and clearing the TXI bit. The  $I^2C$  Controller sends the stop condition on the bus and

# Table 71. I<sup>2</sup>C Data Register (I2CDATA)

| Bit     | 7    | 6   | 5 | 4  | 3  | 2 | 1 | 0 |  |  |

|---------|------|-----|---|----|----|---|---|---|--|--|

| Field   | DATA |     |   |    |    |   |   |   |  |  |

| RESET   |      | 0   |   |    |    |   |   |   |  |  |

| R/W     |      | R/W |   |    |    |   |   |   |  |  |

| Address |      |     |   | F5 | 0H |   |   |   |  |  |

# I<sup>2</sup>C Status Register

The read-only  $I^2C$  Status Register, shown in Table 72, indicates the status of the  $I^2C$  Controller.

# Table 72. I<sup>2</sup>C Status Register (I2CSTAT)

| Bit     | 7    | 6    | 5   | 4   | 3  | 2   | 1   | 0    |

|---------|------|------|-----|-----|----|-----|-----|------|

| Field   | TDRE | RDRF | ACK | 10B | RD | TAS | DSS | NCKI |

| RESET   | 1    |      |     |     | 0  |     |     |      |

| R/W     |      |      |     | F   | २  |     |     |      |

| Address |      |      |     | F5  | 1H |     |     |      |

| Bit  | Description                                                                                                                                                                                                                                                                                                                                                                                       |

|------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| [7]  | <b>Transmit Data Register Empty</b>                                                                                                                                                                                                                                                                                                                                                               |

| TDRE | When the I <sup>2</sup> C Controller is enabled, this bit is 1 when the I <sup>2</sup> C Data Register is empty. When this bit is set, an interrupt is generated if the TXI bit is set, except when the I <sup>2</sup> C Controller is shifting in data during the reception of a byte or when shifting an address and the RD bit is set. This bit is cleared by writing to the I2CDATA Register. |

| [6]  | <b>Receive Data Register Full</b>                                                                                                                                                                                                                                                                                                                                                                 |

| RDRF | This bit is set = 1 when the I <sup>2</sup> C Controller is enabled and the I <sup>2</sup> C Controller has received a byte of data. When asserted, this bit causes the I <sup>2</sup> C Controller to generate an interrupt. This bit is cleared by reading the I <sup>2</sup> C Data Register (unless the read is performed using execution of the On-Chip Debugger's Read Register command).   |

# DMAx Control Register

The DMA*x* Control Register, shown in Table 78, enables and selects the mode of operation for DMA*x*.

# Table 78. DMAx Control Register (DMAxCTL)

| Bit          | 7                              | 6                                                                                                                                                                                                                       | 5             | 4     | 3                              | 2              | 1      | 0 |  |  |  |

|--------------|--------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------|-------|--------------------------------|----------------|--------|---|--|--|--|

| Field        | DEN                            | DLE                                                                                                                                                                                                                     | DDIR          | IRQEN | WSEL                           |                | RSS    |   |  |  |  |

| RESET        |                                |                                                                                                                                                                                                                         |               | (     | )                              |                |        |   |  |  |  |

| R/W          |                                |                                                                                                                                                                                                                         |               | R/    | W                              |                |        |   |  |  |  |

| Address      |                                |                                                                                                                                                                                                                         |               | FB0H, | FB8H                           |                |        |   |  |  |  |

| Bit          | Description                    | Description                                                                                                                                                                                                             |               |       |                                |                |        |   |  |  |  |

| [7]<br>DEN   | 0 = DMAx is                    | <ul> <li>DMAx Enable</li> <li>0 = DMAx is disabled and data transfer requests are disregarded.</li> <li>1 = DMAx is enabled and initiates a data transfer upon receipt of a request from the trigger source.</li> </ul> |               |       |                                |                |        |   |  |  |  |

| [6]<br>DLE   | transfer<br>1 = DMA <i>x</i> , | eloads the c<br>red.                                                                                                                                                                                                    | d Address d   |       | d is then dis<br>erred, reload |                |        |   |  |  |  |

| [5]<br>DDIR  | 0 = Registe                    | <b>DMAx Data Transfer Direction</b><br>$0 = \text{Register File} \rightarrow \text{on-chip peripheral control register.}$<br>$1 = \text{On-chip peripheral control} \rightarrow \text{Register File.}$                  |               |       |                                |                |        |   |  |  |  |

| [4]<br>IRQEN | 0 = DMAx c                     | -                                                                                                                                                                                                                       | nerate any ir |       | l Address da                   | ata is transfe | erred. |   |  |  |  |

# DMAx Address High Nibble Register

The DMAx Address High Register, shown in Table 80, specifies the upper four bits of address for the Start/Current and End addresses of DMAx.

# Table 80. DMAx Address High Nibble Register (DMAxH)

| Bit     | 7                     | 6   | 5 | 4     | 3    | 2 | 1 | 0 |  |  |

|---------|-----------------------|-----|---|-------|------|---|---|---|--|--|

| Field   | DMA_END_H DMA_START_H |     |   |       |      |   |   |   |  |  |

| RESET   |                       | X   |   |       |      |   |   |   |  |  |

| R/W     |                       | R/W |   |       |      |   |   |   |  |  |

| Address |                       |     |   | FB2H, | FBAH |   |   |   |  |  |

| Bit                  | Description                                                                                                                                                                                                                                                       |

|----------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| [7:4]<br>DMA_END_H   | <b>DMAx End Address High Nibble</b><br>These bits, used with the DMAx End Address Low Register, form a 12-bit End Address.<br>The full 12-bit address is provided by {DMA_END_H[3:0], DMA_END[7:0]}.                                                              |

| [3:0]<br>DMA_START_H | <b>DMA</b> <i>x</i> <b>Start/Current Address High Nibble</b><br>These bits, used with the DMA <i>x</i> Start/Current Address Low Register, form a 12-bit Start/<br>Current Address. The full 12-bit address is provided by {DMA_START_H[3:0],<br>DMA_START[7:0]}. |

#### Table 95. Page Select Register (FPS)

| Bit     | 7       | 6 | 5 | 4  | 3    | 2 | 1 | 0 |

|---------|---------|---|---|----|------|---|---|---|

| Field   | INFO_EN |   |   |    | PAGE |   |   |   |

| RESET   |         |   |   | (  | )    |   |   |   |

| R/W     |         |   |   | R/ | W    |   |   |   |

| Address |         |   |   | FF | 9H   |   |   |   |

| Bit     | Description                                                                                                                               |

|---------|-------------------------------------------------------------------------------------------------------------------------------------------|

| [7]     | Information Area Enable                                                                                                                   |

| INFO_EN | 0 = Information Area is not selected.                                                                                                     |

|         | 1 = Information Area is selected. The Information area is mapped into the Flash memory<br>address space at addresses FE00H through FFFFH. |

| [6:0]   | Page Select                                                                                                                               |

| PAGE    | This 7-bit field selects the Flash memory page for programming and Page Erase operations.                                                 |

|         | Flash Memory Address[15:9] = PAGE[6:0].                                                                                                   |

# **Flash Sector Protect Register**

The Flash Sector Protect Register, shown in Table 96, protects Flash memory sectors from being programmed or erased from user code. The Flash Sector Protect Register shares its Register File address with the Page Select Register. The Flash Sector Protect Register can be accessed only after writing the Flash Control Register with 5EH.

User code can only write bits in this register to 1 (bits cannot be cleared to 0 by user code). To determine the appropriate Flash memory sector address range and sector number for your Z8F64xx Series product, please refer to <u>Table 91</u> on page 169.

| Bit        | 7              | 6              | 5              | 4               | 3             | 2             | 1          | 0     |

|------------|----------------|----------------|----------------|-----------------|---------------|---------------|------------|-------|

| Field      | SECT7          | SECT6          | SECT5          | SECT4           | SECT3         | SECT2         | SECT1      | SECT0 |

| RESET      |                |                |                | (               | )             |               |            |       |

| R/W        |                |                |                | R/              | N*            |               |            |       |

| Address    |                |                |                | FF              | 9H            |               |            |       |

| Note: *R/V | V = This regis | ter is accessi | ble for read o | perations; it c | an be written | to 1 only via | user code. |       |

| Bit       | Description                                                                         |

|-----------|-------------------------------------------------------------------------------------|

| [7:0]     | Sector Protect**                                                                    |

| SECTn     | 0 = Sector <i>n</i> can be programmed or erased from user code.                     |

|           | 1 = Sector <i>n</i> is protected and cannot be programmed or erased from user code. |

| Note: **U | ser code can only write bits from 0 to 1.                                           |

# **On-Chip Debugger Control Register Definitions**

This section describes the features of the On-Chip Debugger Control and Status registers.

# **OCD Control Register**

The OCD Control Register, shown in Table 103, controls the state of the On-Chip Debugger. This register enters or exits DEBUG Mode and enables the BRK instruction.

A *reset and stop* function can be achieved by writing 81H to this register. A *reset and go* function can be achieved by writing 41H to this register. If the device is operating in DEBUG Mode, a *run* function can be implemented by writing 40H to this register.

| Bit            | 7                                                                 | 6                                                                                              | 5                                                                           | 4                                                                                                                 | 3                                                             | 2                                                          | 1                                           | 0                            |

|----------------|-------------------------------------------------------------------|------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------|------------------------------------------------------------|---------------------------------------------|------------------------------|

| Field          | DBGMODE                                                           | BRKEN                                                                                          | DBGACK                                                                      | BRKLOOP                                                                                                           |                                                               | Reserved                                                   |                                             | RST                          |

| RESET          |                                                                   |                                                                                                |                                                                             | 0                                                                                                                 |                                                               |                                                            |                                             |                              |

| R/W            |                                                                   | R/W                                                                                            |                                                                             |                                                                                                                   | F                                                             | २                                                          |                                             | R/W                          |

| Bit            | Descriptio                                                        | on                                                                                             |                                                                             |                                                                                                                   |                                                               |                                                            |                                             |                              |

| [7]<br>DBGMODE | eZ8 CPU s<br>ning again<br>are enable<br>ting the de<br>0 = TheZ8 | s bit to 1 ca<br>stops fetchir<br>. This bit is<br>d. If the Re-<br>vice, it can<br>Encore! XF | ng new instr<br>automatical<br>ad Protect c<br>not be writte<br>P F64xx Ser | vice to enter<br>uctions. Clea<br>ly set when a<br>option bit is e<br>in to 0.<br>ies device is<br>ries device is | aring this bi<br>a BRK instru-<br>nabled, this<br>operating i | t causes the<br>uction is dee<br>s bit can onl<br>n NORMAL | e eZ8 CPU t<br>coded and b<br>ly be cleared | to start run-<br>preakpoints |

| [6]<br>BRKEN   | are disable<br>instruction<br>0 = BRK ir                          | ntrols the be<br>ed and the E                                                                  | BRK instruct<br>, the OCD ta<br>disabled.                                   | ne BRK instru<br>tion behaves<br>akes action c                                                                    | like a NOF                                                    | P. If this bit is                                          | s set to 1 an                               | d a BRK                      |

| [5]<br>DBGACK  | This bit en<br>an Debug<br>0 = Debug                              | Acknowled<br>Acknowled                                                                         | ebug acknov                                                                 |                                                                                                                   |                                                               |                                                            |                                             | CD sends                     |

#### Table 103. OCD Control Register (OCDCTL)

| Parameter                                                       | Minimum                                   | Maximum        | Units         | Notes        |

|-----------------------------------------------------------------|-------------------------------------------|----------------|---------------|--------------|

| 64-pin LQFP maximum ratings at -40°C to 70°C                    |                                           |                |               |              |

| Total power dissipation                                         |                                           | 1000           | mW            |              |

| Maximum current into $V_{DD}$ or out of $V_{SS}$                |                                           | 275            | mA            |              |

| 64-pin LQFP maximum ratings at 70°C to 125°C                    |                                           |                |               |              |

| Total power dissipation                                         |                                           | 540            | mW            |              |

| Maximum current into $V_{DD}$ or out of $V_{SS}$                |                                           | 150            | mA            |              |

| 44-pin PLCC maximum ratings at -40°C to 70°C                    |                                           |                |               |              |

| Total power dissipation                                         |                                           | 750            | mW            |              |

| Maximum current into $V_{DD}$ or out of $V_{SS}$                |                                           | 200            | mA            |              |

| 44-pin PLCC maximum ratings at 70°C to 125°C                    |                                           |                |               |              |

| Total power dissipation                                         |                                           | 295            | mW            |              |

| Maximum current into $V_{DD}$ or out of $V_{SS}$                |                                           | 83             | mA            |              |

| 44-pin LQFP maximum ratings at –40°C to 70°C                    |                                           |                |               |              |

| Total power dissipation                                         |                                           | 750            | mW            |              |

| Maximum current into $V_{DD}$ or out of $V_{SS}$                |                                           | 200            | mA            |              |

| 44-pin LQFP maximum ratings at 70°C to 125°C                    |                                           |                |               |              |

| Total power dissipation                                         |                                           | 360            | mW            |              |

| Maximum current into $V_{DD}$ or out of $V_{SS}$                |                                           | 100            | mA            |              |

| Note: This voltage applies to all pins, with the exception of V | / <sub>DD</sub> , AV <sub>DD</sub> , pins | supporting ana | log input (po | orts B and I |

#### Table 106. Absolute Maximum Ratings (Continued)

Note: This voltage applies to all pins, with the exception of V<sub>DD</sub>, AV<sub>DD</sub>, pins supporting analog input (ports B and H), RESET, and where noted otherwise.

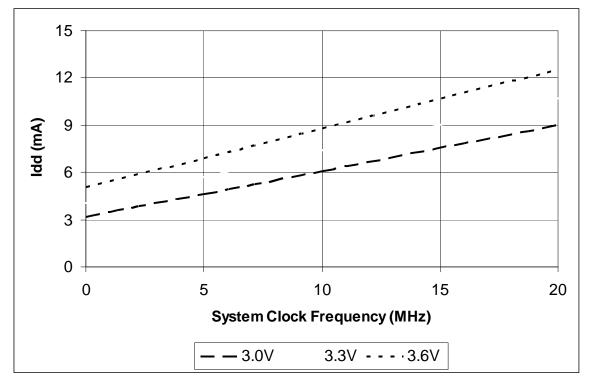

Figure 43 displays the typical active mode current consumption while operating at 25 °C plotted opposite the system clock frequency. All GPIO pins are configured as outputs and driven High.

Figure 43. Typical Active Mode  $I_{\text{DD}}$  vs. System Clock Frequency

Table 111 list the Flash memory electrical characteristics and timing.

|                                                  |         | <sub>DD</sub> = 3.0–3.<br>–40°C to 1 |         |        |                                                                                                                                                                |

|--------------------------------------------------|---------|--------------------------------------|---------|--------|----------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Parameter                                        | Minimum | Typical                              | Maximum | Units  | Notes                                                                                                                                                          |

| Flash Byte Read Time                             | 50      | _                                    | -       | ns     |                                                                                                                                                                |

| Flash Byte Program<br>Time                       | 20      | _                                    | 40      | μs     |                                                                                                                                                                |

| Flash Page Erase Time                            | 10      | _                                    | -       | ms     |                                                                                                                                                                |

| Flash Mass Erase Time                            | 200     | _                                    | -       | ms     |                                                                                                                                                                |

| Writes to Single<br>Address Before Next<br>Erase | -       | _                                    | 2       |        |                                                                                                                                                                |

| Flash Row Program<br>Time                        | _       | _                                    | 8       | ms     | Cumulative program time for single<br>row cannot exceed limit before next<br>erase. This parameter is only an<br>issue when bypassing the Flash<br>Controller. |

| Data Retention                                   | 100     | _                                    | _       | years  | 25°C                                                                                                                                                           |

| Endurance, –40°C to 105°C                        | 10,000  | -                                    | -       | cycles | Program/erase cycles                                                                                                                                           |

| Endurance, 106°C to 125°C                        | 1,000   | -                                    | -       | cycles | Program/erase cycles                                                                                                                                           |

Table 112 lists the Watchdog Timer electrical characteristics and timing.

|                  |                                                               |         | <sub>DD</sub> = 3.0–3.<br>–40°C to 1 |         |       |            |

|------------------|---------------------------------------------------------------|---------|--------------------------------------|---------|-------|------------|

| Symbol           | Parameter                                                     | Minimum | Typical                              | Maximum | Units | Conditions |

| F <sub>WDT</sub> | WDT Oscillator<br>Frequency                                   | 5       | 10                                   | 20      | kHz   |            |

| I <sub>WDT</sub> | WDT Oscillator Current<br>including internal RC<br>Oscillator | _       | <1                                   | 5       | μA    |            |

Z8 Encore! XP<sup>®</sup> F64xx Series Product Specification

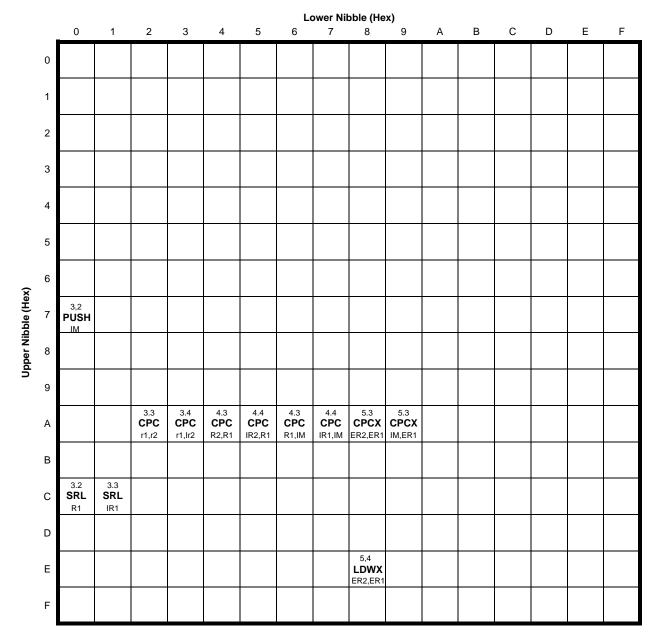

Figure 61. Second Op Code Map after 1FH

# Hex Address: F15

#### Table 159. Timer 0–3 PWM Low Byte Register (TxPWML)

| Bit     | 7 | 1                      | 0 |    |   |  |  |  |  |  |

|---------|---|------------------------|---|----|---|--|--|--|--|--|

| Field   |   | PWML                   |   |    |   |  |  |  |  |  |

| RESET   |   | 0                      |   |    |   |  |  |  |  |  |

| R/W     |   |                        |   | R/ | W |  |  |  |  |  |

| Address |   | F05H, F0DH, F15H, F1DH |   |    |   |  |  |  |  |  |

# Hex Address: F16

#### Table 160. Timer 0–3 Control 0 Register (TxCTL0)

| Bit     | 7 | 6                      | 5 | 4  | 3 | 2 | 1 | 0 |  |  |  |

|---------|---|------------------------|---|----|---|---|---|---|--|--|--|

| Field   |   | Reserved CSC Reserved  |   |    |   |   |   |   |  |  |  |

| RESET   |   | 0                      |   |    |   |   |   |   |  |  |  |

| R/W     |   |                        |   | R/ | W |   |   |   |  |  |  |

| Address |   | F06H, F0EH, F16H, F1EH |   |    |   |   |   |   |  |  |  |

# Hex Address: F17

#### Table 161. Timer 0–3 Control 1 Register (TxCTL1)

| Bit     | 7   | 6                      | 5 | 4    | 3 | 2     | 1 | 0 |  |  |  |

|---------|-----|------------------------|---|------|---|-------|---|---|--|--|--|

| Field   | TEN | TPOL                   |   | PRES |   | TMODE |   |   |  |  |  |

| RESET   |     | 0                      |   |      |   |       |   |   |  |  |  |

| R/W     |     |                        |   | R/   | W |       |   |   |  |  |  |

| Address |     | F07H, F0FH, F17H, F1FH |   |      |   |       |   |   |  |  |  |

## Hex Address: F18

#### Table 162. Timer 0–3 High Byte Register (TxH)

| Bit     | 7 | 6                      | 2 | 1  | 0 |  |  |  |  |  |  |

|---------|---|------------------------|---|----|---|--|--|--|--|--|--|

| Field   |   | TH                     |   |    |   |  |  |  |  |  |  |

| RESET   |   | 0                      |   |    |   |  |  |  |  |  |  |

| R/W     |   |                        |   | R/ | W |  |  |  |  |  |  |

| Address |   | F00H, F08H, F10H, F18H |   |    |   |  |  |  |  |  |  |

# Hex Address: FBA

#### Table 211. DMAx Address High Nibble Register (DMAxH)

| Bit     | 7 | 6                     | 5 | 4  | 3 2 1 |  |  |  |  |  |  |

|---------|---|-----------------------|---|----|-------|--|--|--|--|--|--|

| Field   |   | DMA_END_H DMA_START_H |   |    |       |  |  |  |  |  |  |

| RESET   |   | X                     |   |    |       |  |  |  |  |  |  |

| R/W     |   |                       |   | R/ | W     |  |  |  |  |  |  |

| Address |   | FB2H, FBAH            |   |    |       |  |  |  |  |  |  |

## Hex Address: FBB

#### Table 212. DMAx Start/Current Address Low Byte Register (DMAxSTART)

| Bit     | 7 | 1          | 0 |    |   |  |  |  |  |  |  |

|---------|---|------------|---|----|---|--|--|--|--|--|--|

| Field   |   | DMA_START  |   |    |   |  |  |  |  |  |  |

| RESET   |   | X          |   |    |   |  |  |  |  |  |  |

| R/W     |   |            |   | R/ | W |  |  |  |  |  |  |

| Address |   | FB3H, FBBH |   |    |   |  |  |  |  |  |  |

## Hex Address: FBC

#### Table 213. DMAx End Address Low Byte Register (DMAxEND)

| Bit     | 7 6 5 4 3 2 1 |            |  |    |   |  |  |  |  |  |  |

|---------|---------------|------------|--|----|---|--|--|--|--|--|--|

| Field   |               | DMA_END    |  |    |   |  |  |  |  |  |  |

| RESET   |               | X          |  |    |   |  |  |  |  |  |  |

| R/W     |               |            |  | R/ | W |  |  |  |  |  |  |

| Address |               | FB4H, FBCH |  |    |   |  |  |  |  |  |  |

## Hex Address: FBD

#### Table 214. DMA\_ADC Address Register (DMAA\_ADDR)

| Bit     | 7    | 1         | 0 |    |   |  |  |  |  |  |  |

|---------|------|-----------|---|----|---|--|--|--|--|--|--|

| Field   |      | DMAA_ADDR |   |    |   |  |  |  |  |  |  |

| RESET   |      | X         |   |    |   |  |  |  |  |  |  |

| R/W     |      |           |   | R/ | W |  |  |  |  |  |  |

| Address | FBDH |           |   |    |   |  |  |  |  |  |  |

# Hex Address: FF2

#### Table 263. Watchdog Timer Reload High Byte Register (WDTH)

| Bit        | 7                                                                                            | 6    | 5 | 4  | 3  | 1 | 0 |  |  |  |  |

|------------|----------------------------------------------------------------------------------------------|------|---|----|----|---|---|--|--|--|--|

| Field      |                                                                                              | WDTH |   |    |    |   |   |  |  |  |  |

| RESET      |                                                                                              | 1    |   |    |    |   |   |  |  |  |  |

| R/W        |                                                                                              |      |   | R/ | W* |   |   |  |  |  |  |

| Address    |                                                                                              | FF2H |   |    |    |   |   |  |  |  |  |

| Note: *R/V | e: *R/W = Read returns the current WDT count value; write sets the appropriate reload value. |      |   |    |    |   |   |  |  |  |  |

## Hex Address: FF3

## Table 264. Watchdog Timer Reload Low Byte Register (WDTL)

| Bit        | 7                                                                                         | 7 6 5 4 3 2 1 |  |    |    |  |  |  |  |  |  |

|------------|-------------------------------------------------------------------------------------------|---------------|--|----|----|--|--|--|--|--|--|

| Field      |                                                                                           | WDTL          |  |    |    |  |  |  |  |  |  |

| RESET      |                                                                                           | 1             |  |    |    |  |  |  |  |  |  |

| R/W        |                                                                                           |               |  | R/ | W* |  |  |  |  |  |  |

| Address    |                                                                                           | FF3H          |  |    |    |  |  |  |  |  |  |

| Note: *R/\ | *R/W = Read returns the current WDT count value; write sets the appropriate reload value. |               |  |    |    |  |  |  |  |  |  |

# Hex Addresses: FF4–FF7

This address range is reserved.

# **Ordering Information**

Order your F64xx Series products from Zilog using the part numbers shown in Table 271. For more information about ordering, please consult your local Zilog sales office. The <u>Sales Location page</u> on the Zilog website lists all regional offices.

|                       |              |          |           |            | 777                 | Serie               | 3 01             | uenni | <b>J</b> 1010   |                     |

|-----------------------|--------------|----------|-----------|------------|---------------------|---------------------|------------------|-------|-----------------|---------------------|

| Part Number           | Flash        | RAM      | I/O Lines | Interrupts | 16-Bit Timers w/PWM | 10-Bit A/D Channels | I <sup>2</sup> C | SPI   | UARTs with IrDA | Description         |

| Z8F642x with 64KB FI  |              | -        | to-Di     | igital     | Со                  | nvert               | er               |       |                 |                     |

| Standard Temperature  | e: 0°C to 70 | °C       |           |            |                     |                     |                  |       |                 |                     |

| Z8F6421PM020SG        | 64 KB        | 2KB      | 29        | 23         | 3                   | 8                   | 1                | 1     | 2               | PDIP 40-pin package |

| Z8F6421AN020SG        | 64KB         | 4KB      | 31        | 23         | 3                   | 8                   | 1                | 1     | 2               | LQFP 44-pin package |

| Z8F6421VN020SG        | 64 KB        | 4KB      | 31        | 23         | 3                   | 8                   | 1                | 1     | 2               | PLCC 44-pin package |

| Z8F6422AR020SG        | 64 KB        | 4KB      | 46        | 24         | 4                   | 12                  | 1                | 1     | 2               | LQFP 64-pin package |

| Z8F6422VS020SG        | 64KB         | 4KB      | 46        | 24         | 4                   | 12                  | 1                | 1     | 2               | PLCC 68-pin package |

| Z8F6423FT020SG        | 64KB         | 4KB      | 60        | 24         | 4                   | 12                  | 1                | 1     | 2               | QFP 80-pin package  |

| Extended Temperatur   | e: -40°C to  | +105°C   |           |            |                     |                     |                  |       |                 |                     |

| Z8F6421PM020EG        | 64 KB        | 2KB      | 29        | 23         | 3                   | 8                   | 1                | 1     | 2               | PDIP 40-pin package |

| Z8F6421AN020EG        | 64KB         | 4KB      | 31        | 23         | 3                   | 8                   | 1                | 1     | 2               | LQFP 44-pin package |

| Z8F6421VN020EG        | 64 KB        | 4KB      | 31        | 23         | 3                   | 8                   | 1                | 1     | 2               | PLCC 44-pin package |

| Z8F6422AR020EG        | 64 KB        | 4KB      | 46        | 24         | 4                   | 12                  | 1                | 1     | 2               | LQFP 64-pin package |

| Z8F6422VS020EG        | 64 KB        | 4KB      | 46        | 24         | 4                   | 12                  | 1                | 1     | 2               | PLCC 68-pin package |

| Z8F6423FT020EG        | 64KB         | 4KB      | 60        | 24         | 4                   | 12                  | 1                | 1     | 2               | QFP 80-pin package  |

| Automotive/Industrial | Temperatu    | re: –40° | C to      | +125       | 5°C                 |                     |                  |       |                 |                     |

| Z8F6421PM020AG        | 64KB         | 2KB      | 29        | 23         | 3                   | 8                   | 1                | 1     | 2               | PDIP 40-pin package |

| Z8F6421AN020AG        | 64KB         | 4KB      | 31        | 23         | 3                   | 8                   | 1                | 1     | 2               | LQFP 44-pin package |

| Z8F6421VN020AG        | 64KB         | 4KB      | 31        | 23         | 3                   | 8                   | 1                | 1     | 2               | PLCC 44-pin package |

| Z8F6422AR020AG        | 64KB         | 4KB      | 46        | 24         | 4                   | 12                  | 1                | 1     | 2               | LQFP 64-pin package |

| Z8F6422VS020AG        | 64KB         | 4KB      | 46        | 24         | 4                   | 12                  | 1                | 1     | 2               | PLCC 68-pin package |

| Z8F6423FT020AG        | 64KB         | 4KB      | 60        | 24         | 4                   | 12                  | 1                | 1     | 2               | QFP 80-pin package  |

#### Table 271. Z8 Encore! XP F64xx Series Ordering Matrix

|                         |            |          |           |            | -                   |                     |                  |     |                 |                                                |

|-------------------------|------------|----------|-----------|------------|---------------------|---------------------|------------------|-----|-----------------|------------------------------------------------|

| Part Number             | Flash      | RAM      | //O Lines | Interrupts | 16-Bit Timers w/PWM | 10-Bit A/D Channels | I <sup>2</sup> C | SPI | UARTs with IrDA | Description                                    |

| Z8F162x with 16KB Fla   | sh, 10-Bit | Analog   | -to-Di    | igital     | Со                  | nvert               | er               |     |                 |                                                |

| Standard Temperature:   | 0°C to 70  | °C       |           |            |                     |                     |                  |     |                 |                                                |

| Z8F1621PM020SG          | 16KB       | 2KB      | 29        | 23         | 3                   | 8                   | 1                | 1   | 2               | PDIP 40-pin package                            |

| Z8F1621AN020SG          | 16KB       | 2KB      | 31        | 23         | 3                   | 8                   | 1                | 1   | 2               | LQFP 44-pin package                            |

| Z8F1621VN020SG          | 16KB       | 2KB      | 31        | 23         | 3                   | 8                   | 1                | 1   | 2               | PLCC 44-pin package                            |

| Z8F1622AR020SG          | 16KB       | 2KB      | 46        | 24         | 4                   | 12                  | 1                | 1   | 2               | LQFP 64-pin package                            |

| Z8F1622VS020SG          | 16KB       | 2KB      | 46        | 24         | 4                   | 12                  | 1                | 1   | 2               | PLCC 68-pin package                            |

| Extended Temperature    | : –40°C to | +105°C   |           |            |                     |                     |                  |     |                 |                                                |

| Z8F1621PM020EG          | 16KB       | 2KB      | 29        | 23         | 3                   | 8                   | 1                | 1   | 2               | PDIP 40-pin package                            |

| Z8F1621AN020EG          | 16KB       | 2KB      | 31        | 23         | 3                   | 8                   | 1                | 1   | 2               | LQFP 44-pin package                            |

| Z8F1621VN020EG          | 16KB       | 2KB      | 31        | 23         | 3                   | 8                   | 1                | 1   | 2               | PLCC 44-pin package                            |

| Z8F1622AR020EG          | 16KB       | 2KB      | 46        | 24         | 4                   | 12                  | 1                | 1   | 2               | LQFP 64-pin package                            |

| Z8F1622VS020EG          | 16KB       | 2KB      | 46        | 24         | 4                   | 12                  | 1                | 1   | 2               | PLCC 68-pin package                            |

| Automotive/Industrial 1 | Femperatu  | re: –40° | C to      | +125       | 5°C                 |                     |                  |     |                 |                                                |

| Z8F1621PM020AG          | 16KB       | 2KB      | 29        | 23         | 3                   | 8                   | 1                | 1   | 2               | PDIP 40-pin package                            |

| Z8F1621AN020AG          | 16KB       | 2KB      | 31        | 23         | 3                   | 8                   | 1                | 1   | 2               | LQFP 44-pin package                            |

| Z8F1621VN020AG          | 16KB       | 2KB      | 31        | 23         | 3                   | 8                   | 1                | 1   | 2               | PLCC 44-pin package                            |

| Z8F1622AR020AG          | 16KB       | 2KB      | 46        | 24         | 4                   | 12                  | 1                | 1   | 2               | LQFP 64-pin package                            |

| Z8F1622VS020AG          | 16KB       | 2KB      | 46        | 24         | 4                   | 12                  | 1                | 1   | 2               | PLCC 68-pin package                            |

| Z8F64200100KITG         |            |          |           |            |                     |                     |                  |     |                 | Development Kit                                |

| ZUSBSC00100ZACG         |            |          |           |            |                     |                     |                  |     |                 | USB Smart Cable<br>Accessory Kit               |

| ZUSBOPTSC01ZACG         |            |          |           |            |                     |                     |                  |     |                 | Opto-Isolated USB Smart<br>Cable Accessory Kit |

| ZENETSC0100ZACG         |            |          |           |            |                     |                     |                  |     |                 | Ethernet Smart Cable<br>Accessory Kit          |

# Table 271. Z8 Encore! XP F64xx Series Ordering Matrix