#### Zilog - Z8F4821AN020SG Datasheet

Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

#### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Product Status             | Active                                                    |

|----------------------------|-----------------------------------------------------------|

| Core Processor             | eZ8                                                       |

| Core Size                  | 8-Bit                                                     |

| Speed                      | 20MHz                                                     |

| Connectivity               | I <sup>2</sup> C, IrDA, SPI, UART/USART                   |

| Peripherals                | Brown-out Detect/Reset, DMA, POR, PWM, WDT                |

| Number of I/O              | 31                                                        |

| Program Memory Size        | 48KB (48K x 8)                                            |

| Program Memory Type        | FLASH                                                     |

| EEPROM Size                | -                                                         |

| RAM Size                   | 4K x 8                                                    |

| Voltage - Supply (Vcc/Vdd) | 3V ~ 3.6V                                                 |

| Data Converters            | A/D 8x10b                                                 |

| Oscillator Type            | Internal                                                  |

| Operating Temperature      | 0°C ~ 70°C (TA)                                           |

| Mounting Type              | Surface Mount                                             |

| Package / Case             | 44-LQFP                                                   |

| Supplier Device Package    | 44-LQFP (10x10)                                           |

| Purchase URL               | https://www.e-xfl.com/product-detail/zilog/z8f4821an020sg |

|                            |                                                           |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

# **Revision History**

Each instance in the Revision History table reflects a change to this document from its previous revision. For more details, refer to the corresponding pages or appropriate links listed in the table below.

| Data        | Revision | Description                                                                                                                                                                                                                                                                                                                                                                            | Denn            |

|-------------|----------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------|

| Date        | Level    | Description                                                                                                                                                                                                                                                                                                                                                                            | Page            |

| Jan<br>2013 | 24       | Restored 40-pin PDIP package to Signal and Pin Descriptions and Packag-<br>ing chapters.                                                                                                                                                                                                                                                                                               | <u>7, 286</u>   |

| Feb<br>2012 | 23       | Corrected formatting of I <sub>DDS</sub> section, Table 107; corrected language in the General Purpose RAM section of Appendix A;                                                                                                                                                                                                                                                      | <u>202, 248</u> |

| Sep<br>2011 | 22       | Revised Flash Sector Protect Register description; revised Packaging chapter.                                                                                                                                                                                                                                                                                                          | <u>178, 286</u> |

| Mar<br>2008 | 21       | Changed title to Z8 Encore! XP F64xx Series.                                                                                                                                                                                                                                                                                                                                           | All             |

| Feb<br>2008 | 20       | Changed Z8 Encore! XP 64K Series Flash Microcontrollers to Z8 Encore!<br>XP F64xx Series Flash Microcontrollers. Deleted three sentences that men-<br>tioned Z8R642. Removed the 40 PDIP package. Added<br>ZENETSC0100ZACG to the end of the Ordering Information table.<br>Changed the flag status to unaffected for BIT, BSET, and BCLR in the eZ8<br>CPU Instruction Summary table. | <u>287, 234</u> |

| Dec<br>2007 | 19       | Updated Zilog logo, Disclaimer section, and implemented style guide.<br>Updated Table 113. Changed Z8 Encore! 64K Series to Z8 Encore! XP 64K<br>Series Flash Microcontrollers throughout the document.                                                                                                                                                                                | All             |

| Dec<br>2006 | 18       | Updated Flash Memory Electrical Characteristics and Timing table and Ordering Information chapter.                                                                                                                                                                                                                                                                                     | <u>213, 287</u> |

| Nov<br>2006 | 17       | Updated Part Number Suffix Designations section.                                                                                                                                                                                                                                                                                                                                       | <u>292</u>      |

# **Register File Address Map**

Table 7 provides the address map for the Register File of the Z8 Encore! XP F64xx Series products. Not all devices and package styles in the Z8 Encore! XP F64xx Series support Timer 3 and all of the GPIO ports. Consider registers for unimplemented peripherals to be reserved.

| Address (H | ex) Register Description          | Mnemonic | Reset (Hex) | Page      |

|------------|-----------------------------------|----------|-------------|-----------|

| General-Pu | rpose RAM                         |          |             |           |

| 000-EFF    | General-Purpose Register File RAM |          | XX          |           |

| Timer 0    |                                   |          |             |           |

| F00        | Timer 0 High Byte                 | T0H      | 00          | <u>72</u> |

| F01        | Timer 0 Low Byte                  | TOL      | 01          | <u>72</u> |

| F02        | Timer 0 Reload High Byte          | TORH     | FF          | <u>74</u> |

| F03        | Timer 0 Reload Low Byte           | TORL     | FF          | <u>74</u> |

| F04        | Timer 0 PWM High Byte             | TOPWMH   | 00          | <u>75</u> |

| F05        | Timer 0 PWM Low Byte              | TOPWML   | 00          | <u>75</u> |

| F06        | Timer 0 Control 0                 | TOCTLO   | 00          | <u>76</u> |

| F07        | Timer 0 Control 1                 | T0CTL1   | 00          | <u>77</u> |

| Timer 1    |                                   |          |             |           |

| F08        | Timer 1 High Byte                 | T1H      | 00          | <u>72</u> |

| F09        | Timer 1 Low Byte                  | T1L      | 01          | <u>72</u> |

| F0A        | Timer 1 Reload High Byte          | T1RH     | FF          | <u>74</u> |

| F0B        | Timer 1 Reload Low Byte           | T1RL     | FF          | <u>74</u> |

| F0C        | Timer 1 PWM High Byte             | T1PWMH   | 00          | <u>75</u> |

| F0D        | Timer 1 PWM Low Byte              | T1PWML   | 00          | <u>75</u> |

| F0E        | Timer 1 Control 0                 | T1CTL0   | 00          | <u>76</u> |

| F0F        | Timer 1 Control 1                 | T1CTL1   | 00          | <u>77</u> |

| Timer 2    |                                   |          |             |           |

| F10        | Timer 2 High Byte                 | T2H      | 00          | <u>72</u> |

| F11        | Timer 2 Low Byte                  | T2L      | 01          | <u>72</u> |

| F12        | Timer 2 Reload High Byte          | T2RH     | FF          | <u>74</u> |

| F13        | Timer 2 Reload Low Byte           | T2RL     | FF          | <u>74</u> |

#### Table 7. Z8 Encore! XP F64xx Series Register File Address Map

Note: XX = Undefined.

# Interrupt Controller

The interrupt controller on the Z8 Encore! XP F64xx Series products prioritizes the interrupt requests from the on-chip peripherals and the GPIO port pins. The features of the interrupt controller include:

- 24 unique interrupt vectors:

- 12 GPIO port pin interrupt sources

- 12 on-chip peripheral interrupt sources

- Flexible GPIO interrupts

- Eight selectable rising and falling edge GPIO interrupts

- Four dual-edge interrupts

- Three levels of individually programmable interrupt priority

- Watchdog Timer can be configured to generate an interrupt

Interrupt requests (IRQs) allow peripheral devices to suspend CPU operation in an orderly manner and force the CPU to start an interrupt service routine (ISR). Usually this interrupt service routine is involved with the exchange of data, status information, or control information between the CPU and the interrupting peripheral. When the service routine is completed, the CPU returns to the operation from which it was interrupted.

The eZ8 CPU supports both vectored and polled interrupt handling. For polled interrupts, the interrupt control has no effect on operation. For more information about interrupt servicing by the eZ8 CPU, refer to the <u>eZ8 CPU Core User Manual (UM0128)</u>, which is available for download on <u>www.zilog.com</u>.

## **Interrupt Vector Listing**

Table 23 lists all of the interrupts available in order of priority. The interrupt vector is stored with the most significant byte (MSB) at the even program memory address and the least significant byte (LSB) at the following odd program memory address.

- 6. Configure the associated GPIO port pin for the timer input alternate function.

- 7. Write to the Timer Control 1 Register to enable the timer and initiate counting.

In CAPTURE Mode, the elapsed time from timer start to capture event can be calculated using the following equation:

Capture Elapsed Time (s) =  $\frac{(Capture Value - Start Value) \times Prescale}{System Clock Frequency (Hz)}$

### **COMPARE Mode**

In COMPARE Mode, the timer counts up to the 16-bit maximum compare value stored in the Timer Reload High and Low Byte registers. The timer input is the system clock. Upon reaching the compare value, the timer generates an interrupt and counting continues (the timer value is not reset to 0001H). Also, if the timer output alternate function is enabled, the timer output pin changes state (from Low to High or from High to Low) upon compare.

If the Timer reaches FFFFH, the timer rolls over to 0000H and continue counting.

Observe the following procedure for configuring a timer for COMPARE Mode and initiating the count:

- 1. Write to the Timer Control 1 Register to:

- Disable the timer

- Configure the timer for COMPARE Mode

- Set the prescale value

- Set the initial logic level (High or Low) for the timer output alternate function, if appropriate

- 2. Write to the Timer High and Low Byte registers to set the starting count value.

- 3. Write to the Timer Reload High and Low Byte registers to set the compare value.

- 4. If appropriate, enable the timer interrupt and set the timer interrupt priority by writing to the relevant interrupt registers.

- 5. If using the timer output function, configure the associated GPIO port pin for the timer output alternate function.

- 6. Write to the Timer Control 1 Register to enable the timer and initiate counting.

In COMPARE Mode, the system clock always provides the timer input. The compare time is calculated using the following equation:

ister. This operation allows accurate reads of the full 16-bit timer count value while enabled. When the timers are not enabled, a read from the Timer Low Byte Register returns the actual value in the counter.

### **Timer Output Signal Operation**

A timer output is a GPIO port pin alternate function. Generally, the timer output is toggled every time the counter is reloaded.

## **Timer Control Register Definitions**

This section defines the features of the following Timer Control registers.

Timer 0-3 High and Low Byte Registers: see page 72

Timer Reload High and Low Byte Registers: see page 74

Timer 0-3 PWM High and Low Byte Registers: see page 75

Timer 0-3 Control 0 Registers: see page 76

Timer 0-3 Control 1 Registers: see page 77

Timers 0–2 are available in all packages. Timer 3 is only available in 64-, 68- and 80-pin packages.

### Timer 0–3 High and Low Byte Registers

The Timer 0–3 High and Low Byte (TxH and TxL) registers, shown in Tables 39 and 40, contain the current 16-bit timer count value. When the timer is enabled, a read from TxH causes the value in TxL to be stored in a temporary holding register. A read from TMRL always returns this temporary register when the timers are enabled. When the timer is disabled, reads from the TMRL read the register directly.

Writing to the Timer High and Low Byte registers while the timer is enabled is not recommended. There are no temporary holding registers available for write operations, so simultaneous 16-bit writes are not possible. If either the Timer High or Low Byte registers are written during counting, the 8-bit written value is placed in the counter (High or Low Byte) at the next clock edge. The counter continues counting from the new value.

Timer 3 is unavailable in 44-pin packages.

### **UART Control 0 and Control 1 Registers**

The UART Control 0 and Control 1 Registers, shown in Tables 57 and 58, configure the properties of the UART's transmit and receive operations. The UART Control registers must not been written while the UART is enabled.

#### Table 57. UART Control 0 Register (UxCTL0)

| Bit         | 7                                                                                                                                                                                                                                                                                                                                                                                            | 6                                                                                                                                                              | 5    | 4       | 3       | 2    | 1    | 0    |

|-------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------|------|---------|---------|------|------|------|

| Field       | TEN                                                                                                                                                                                                                                                                                                                                                                                          | REN                                                                                                                                                            | CTSE | PEN     | PSEL    | SBRK | STOP | LBEN |

| RESET       |                                                                                                                                                                                                                                                                                                                                                                                              | 0                                                                                                                                                              |      |         |         |      |      |      |

| R/W         |                                                                                                                                                                                                                                                                                                                                                                                              |                                                                                                                                                                |      | R/      | W       |      |      |      |

| Address     |                                                                                                                                                                                                                                                                                                                                                                                              |                                                                                                                                                                |      | F42H ar | nd F4AH |      |      |      |

| Bit         | Descriptio                                                                                                                                                                                                                                                                                                                                                                                   | Description                                                                                                                                                    |      |         |         |      |      |      |

| [7]<br>TEN  | <b>Transmit Enable</b><br>This bit enables or disables the transmitter. The enable is also controlled by the $\overline{\text{CTS}}$ signal and the CTSE bit. If the $\overline{\text{CTS}}$ signal is low and the CTSE bit is 1, the transmitter is enabled.<br>0 = Transmitter disabled.<br>1 = Transmitter enabled.                                                                       |                                                                                                                                                                |      |         |         |      |      |      |

| [6]<br>REN  | This bit ena<br>0 = Receive                                                                                                                                                                                                                                                                                                                                                                  | Receive Enable<br>This bit enables or disables the receiver.<br>0 = Receiver disabled.<br>1 = Receiver enabled.                                                |      |         |         |      |      |      |

| [5]<br>CTSE | $0 = \text{The } \overline{\text{CT}}$                                                                                                                                                                                                                                                                                                                                                       | <b>CTS Enable</b><br>0 = The CTS signal has no effect on the transmitter.<br>1 = The UART recognizes the CTS signal as an enable control from the transmitter. |      |         |         |      |      | :    |

| [4]<br>PEN  | <ul> <li>Parity Enable</li> <li>This bit enables or disables parity. Even or odd is determined by the PSEL bit. It is overridder by the MPEN bit.</li> <li>0 = Parity is disabled.</li> <li>1 = The transmitter sends data with an additional parity bit and the receiver receives an additional parity bit.</li> </ul>                                                                      |                                                                                                                                                                |      |         |         |      |      |      |

| [3]<br>PSEL | Parity Select<br>0 = Even parity is transmitted and expected on all received data.                                                                                                                                                                                                                                                                                                           |                                                                                                                                                                |      |         |         |      |      |      |

| [2]<br>SBRK | <ul> <li>1 = Odd parity is transmitted and expected on all received data.</li> <li>Send Break</li> <li>This bit pauses or breaks data transmission. Sending a break interrupts any transmission ir progress, so ensure that the transmitter has finished sending data before setting this bit.</li> <li>0 = No break is sent.</li> <li>1 = The output of the transmitter is zero.</li> </ul> |                                                                                                                                                                |      |         |         |      |      |      |

|                                                                | 10.0MHz Sy                               | stem Clock                                                      |                                                             | 5                                                                       | 5.5296 MHz S                              | ystem Clock                                                         |                                                            |

|----------------------------------------------------------------|------------------------------------------|-----------------------------------------------------------------|-------------------------------------------------------------|-------------------------------------------------------------------------|-------------------------------------------|---------------------------------------------------------------------|------------------------------------------------------------|

| Desired<br>Rate<br>(kHz)                                       | BRG<br>Divisor<br>(Decimal)              | Actual Rate<br>(kHz)                                            | Error<br>(%)                                                | Desired<br>Rate<br>(kHz)                                                | BRG<br>Divisor<br>(Decimal)               | Actual Rate<br>(kHz)                                                | Error<br>(%)                                               |

| 1250.0                                                         | N/A                                      | N/A                                                             | N/A                                                         | 1250.0                                                                  | N/A                                       | N/A                                                                 | N/A                                                        |

| 625.0                                                          | 1                                        | 625.0                                                           | 0.00                                                        | 625.0                                                                   | N/A                                       | N/A                                                                 | N/A                                                        |

| 250.0                                                          | 3                                        | 208.33                                                          | -16.67                                                      | 250.0                                                                   | 1                                         | 345.6                                                               | 38.24                                                      |

| 115.2                                                          | 5                                        | 125.0                                                           | 8.51                                                        | 115.2                                                                   | 3                                         | 115.2                                                               | 0.00                                                       |

| 57.6                                                           | 11                                       | 56.8                                                            | -1.36                                                       | 57.6                                                                    | 6                                         | 57.6                                                                | 0.00                                                       |

| 38.4                                                           | 16                                       | 39.1                                                            | 1.73                                                        | 38.4                                                                    | 9                                         | 38.4                                                                | 0.00                                                       |

| 19.2                                                           | 33                                       | 18.9                                                            | 0.16                                                        | 19.2                                                                    | 18                                        | 19.2                                                                | 0.00                                                       |

| 9.60                                                           | 65                                       | 9.62                                                            | 0.16                                                        | 9.60                                                                    | 36                                        | 9.60                                                                | 0.00                                                       |

| 4.80                                                           | 130                                      | 4.81                                                            | 0.16                                                        | 4.80                                                                    | 72                                        | 4.80                                                                | 0.00                                                       |

| 2.40                                                           | 260                                      | 2.40                                                            | -0.03                                                       | 2.40                                                                    | 144                                       | 2.40                                                                | 0.00                                                       |

| 1.20                                                           | 521                                      | 1.20                                                            | -0.03                                                       | 1.20                                                                    | 288                                       | 1.20                                                                | 0.00                                                       |

| 0.60                                                           | 1042                                     | 0.60                                                            | -0.03                                                       | 0.60                                                                    | 576                                       | 0.60                                                                | 0.00                                                       |

| 0.30                                                           | 2083                                     | 0.30                                                            | 0.2                                                         | 0.30                                                                    | 1152                                      | 0.30                                                                | 0.00                                                       |

| 3.                                                             | 579545MHz \$                             | System Clock                                                    |                                                             | 1                                                                       | .8432MHz S                                | ystem Clock                                                         |                                                            |

| Desired<br>Rate<br>(kHz)                                       | BRG<br>Divisor<br>(Decimal)              | Actual Rate<br>(kHz)                                            | Error<br>(%)                                                | Desired<br>Rate<br>(kHz)                                                | BRG<br>Divisor<br>(Decimal)               | Actual Rate<br>(kHz)                                                | Error<br>(%)                                               |

| 1250.0                                                         | N/A                                      | N/A                                                             | N/A                                                         | 1250.0                                                                  | N/A                                       |                                                                     | N/A                                                        |

| 625.0                                                          |                                          |                                                                 |                                                             | 1200.0                                                                  |                                           | N/A                                                                 | 1 1/7 1                                                    |

| 025.0                                                          | N/A                                      | N/A                                                             | N/A                                                         | 625.0                                                                   | N/A                                       | N/A<br>N/A                                                          | N/A                                                        |

| 250.0                                                          | N/A<br>1                                 | N/A<br>223.72                                                   | N/A<br>-10.51                                               |                                                                         | N/A<br>N/A                                |                                                                     |                                                            |

|                                                                |                                          |                                                                 |                                                             | 625.0                                                                   |                                           | N/A                                                                 | N/A                                                        |

| 250.0                                                          | 1                                        | 223.72                                                          | -10.51                                                      | 625.0<br>250.0                                                          | N/A                                       | N/A<br>N/A                                                          | N/A<br>N/A                                                 |

| 250.0<br>115.2                                                 | 1<br>2                                   | 223.72<br>111.9                                                 | -10.51<br>-2.90                                             | 625.0<br>250.0<br>115.2                                                 | N/A<br>1                                  | N/A<br>N/A<br>115.2                                                 | N/A<br>N/A<br>0.00                                         |

| 250.0<br>115.2<br>57.6                                         | 1<br>2<br>4                              | 223.72<br>111.9<br>55.9                                         | -10.51<br>-2.90<br>-2.90                                    | 625.0<br>250.0<br>115.2<br>57.6                                         | N/A<br>1<br>2                             | N/A<br>N/A<br>115.2<br>57.6                                         | N/A<br>N/A<br>0.00<br>0.00                                 |

| 250.0<br>115.2<br>57.6<br>38.4                                 | 1<br>2<br>4<br>6                         | 223.72<br>111.9<br>55.9<br>37.3                                 | -10.51<br>-2.90<br>-2.90<br>-2.90                           | 625.0<br>250.0<br>115.2<br>57.6<br>38.4                                 | N/A<br>1<br>2<br>3                        | N/A<br>N/A<br>115.2<br>57.6<br>38.4                                 | N/A<br>N/A<br>0.00<br>0.00<br>0.00                         |

| 250.0<br>115.2<br>57.6<br>38.4<br>19.2                         | 1<br>2<br>4<br>6<br>12                   | 223.72<br>111.9<br>55.9<br>37.3<br>18.6                         | -10.51<br>-2.90<br>-2.90<br>-2.90<br>-2.90                  | 625.0<br>250.0<br>115.2<br>57.6<br>38.4<br>19.2                         | N/A<br>1<br>2<br>3<br>6                   | N/A<br>N/A<br>115.2<br>57.6<br>38.4<br>19.2                         | N/A<br>N/A<br>0.00<br>0.00<br>0.00<br>0.00                 |

| 250.0<br>115.2<br>57.6<br>38.4<br>19.2<br>9.60                 | 1<br>2<br>4<br>6<br>12<br>23             | 223.72<br>111.9<br>55.9<br>37.3<br>18.6<br>9.73                 | -10.51<br>-2.90<br>-2.90<br>-2.90<br>-2.90<br>1.32          | 625.0<br>250.0<br>115.2<br>57.6<br>38.4<br>19.2<br>9.60                 | N/A<br>1<br>2<br>3<br>6<br>12             | N/A<br>N/A<br>115.2<br>57.6<br>38.4<br>19.2<br>9.60                 | N/A<br>N/A<br>0.00<br>0.00<br>0.00<br>0.00<br>0.00         |

| 250.0<br>115.2<br>57.6<br>38.4<br>19.2<br>9.60<br>4.80         | 1<br>2<br>4<br>6<br>12<br>23<br>47       | 223.72<br>111.9<br>55.9<br>37.3<br>18.6<br>9.73<br>4.76         | -10.51<br>-2.90<br>-2.90<br>-2.90<br>-2.90<br>1.32<br>-0.83 | 625.0<br>250.0<br>115.2<br>57.6<br>38.4<br>19.2<br>9.60<br>4.80         | N/A<br>1<br>2<br>3<br>6<br>12<br>24       | N/A<br>N/A<br>115.2<br>57.6<br>38.4<br>19.2<br>9.60<br>4.80         | N/A<br>N/A<br>0.00<br>0.00<br>0.00<br>0.00<br>0.00<br>0.00 |

| 250.0<br>115.2<br>57.6<br>38.4<br>19.2<br>9.60<br>4.80<br>2.40 | 1<br>2<br>4<br>6<br>12<br>23<br>47<br>93 | 223.72<br>111.9<br>55.9<br>37.3<br>18.6<br>9.73<br>4.76<br>2.41 | -10.51<br>-2.90<br>-2.90<br>-2.90<br>1.32<br>-0.83<br>0.23  | 625.0<br>250.0<br>115.2<br>57.6<br>38.4<br>19.2<br>9.60<br>4.80<br>2.40 | N/A<br>1<br>2<br>3<br>6<br>12<br>24<br>48 | N/A<br>N/A<br>115.2<br>57.6<br>38.4<br>19.2<br>9.60<br>4.80<br>2.40 | N/A<br>N/A<br>0.00<br>0.00<br>0.00<br>0.00<br>0.00<br>0.00 |

#### Table 62. UART Baud Rates (Continued) \_ \_\_

### **SPI Diagnostic State Register**

The SPI Diagnostic State Register, shown in Table 68, provides observability of internal state. This register is a read-only register that is used for SPI diagnostics.

#### Table 68. SPI Diagnostic State Register (SPIDST)

| Bit     | 7     | 6     | 5        | 4 | 3 | 2 | 1 | 0 |

|---------|-------|-------|----------|---|---|---|---|---|

| Field   | SCKEN | TCKEN | SPISTATE |   |   |   |   |   |

| RESET   |       | 0     |          |   |   |   |   |   |

| R/W     |       | R     |          |   |   |   |   |   |

| Address |       | F64H  |          |   |   |   |   |   |

| Bit               | Description                                                                                                                                                                                                                                                                       |

|-------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| [7]<br>SCKEN      | <ul> <li>Shift Clock Enable</li> <li>0 = The internal Shift Clock Enable signal is deasserted.</li> <li>1 = The internal Shift Clock Enable signal is asserted (shift register is updates on next system clock).</li> </ul>                                                       |

| [6]<br>TCKEN      | <ul> <li>Transmit Clock Enable</li> <li>0 = The internal Transmit Clock Enable signal is deasserted.</li> <li>1 = The internal Transmit Clock Enable signal is asserted. When this is asserted the serial data out is updated on the next system clock (MOSI or MISO).</li> </ul> |

| [5:0]<br>SPISTATE | SPI State Machine<br>Defines the current state of the internal SPI State Machine.                                                                                                                                                                                                 |

### SPI Baud Rate High and Low Byte Registers

The SPI Baud Rate High and Low Byte registers, shown in Tables 69 and 70, combine to form a 16-bit reload value, BRG[15:0], for the SPI Baud Rate Generator.

When configured as a general purpose timer, the SPI BRG interrupt interval is calculated using the following equation:

SPI BRG Interrupt Interval (s) = System Clock Period (s)  $\times$  BRG[15:0]

- The first bit of the byte of an address is shifting out and the RD bit of the I<sup>2</sup>C Status Register is deasserted.

- The first bit of a 10-bit address shifts out

- The first bit of write data shifts out

**Note:** Writing to the I<sup>2</sup>C Data Register always clears the TRDE bit to 0. When TDRE is asserted, the I<sup>2</sup>C Controller pauses at the beginning of the Acknowledge cycle of the byte currently shifting out. It does not resume until the Data Register is written with the next value to send or until the stop or start bits are set, indicating that the current byte is the last one to send.

The fourth interrupt source is the baud rate generator. If the I<sup>2</sup>C Controller is disabled (IEN bit in the I2CCTL Register = 0) and the BIRQ bit in the I2CCTL Register = 1, an interrupt is generated when the baud rate generator counts down to 1. This allows the I<sup>2</sup>C baud rate generator to be used by software as a general purpose timer when IEN = 0.

## Software Control of I<sup>2</sup>C Transactions

Software can control  $I^2C$  transactions by using the  $I^2C$  Controller interrupt, by polling the  $I^2C$  Status Register or by DMA. Note that not all products include a DMA Controller.

To use interrupts, the  $I^2C$  interrupt must be enabled in the Interrupt Controller. The TXI bit in the  $I^2C$  Control Register must be set to enable transmit interrupts.

To control transactions by polling, the interrupt bits (TDRE, RDRF and NCKI) in the  $I^2C$  Status Register should be polled. The TDRE bit asserts regardless of the state of the TXI bit.

Either or both transmit and receive data movement can be controlled by the DMA Controller. The DMA Controller channel(s) must be initialized to select the I<sup>2</sup>C transmit and receive requests. Transmit DMA requests require that the TXI bit in the I<sup>2</sup>C Control Register be set.

**Caution:** A transmit (write) DMA operation hangs if the slave responds with a Not Acknowledge before the last byte has been sent. After receiving the Not Acknowledge, the I<sup>2</sup>C Controller sets the NCKI bit in the Status Register and pauses until either the stop or start bits in the Control Register are set.

For a receive (read) DMA transaction to send a Not Acknowledge on the last byte, the receive DMA must be set up to receive n-1 bytes, then software must set the NAK bit and receive the last (nth) byte directly.

- 2. Software asserts the TXI bit of the  $I^2C$  Control Register to enable transmit interrupts.

- 3. The  $I^2C$  interrupt asserts because the  $I^2C$  Data Register is empty.

- 4. Software responds to the TDRE interrupt by writing the first slave address byte to the I<sup>2</sup>C Data Register. The least significant bit must be 0 for the write operation.

- 5. Software asserts the start bit of the  $I^2C$  Control Register.

- 6. The I<sup>2</sup>C Controller sends the start condition to the I<sup>2</sup>C slave.

- 7. The I<sup>2</sup>C Controller loads the I<sup>2</sup>C Shift Register with the contents of the I<sup>2</sup>C Data Register.

- 8. After one bit of address is shifted out by the SDA signal, the transmit interrupt is asserted.

- 9. Software responds by writing the second byte of address into the contents of the I<sup>2</sup>C Data Register.

- 10. The I<sup>2</sup>C Controller shifts the rest of the first byte of address and write bit out the SDA signal.

- 11. If the I<sup>2</sup>C slave acknowledges the first address byte by pulling the SDA signal Low during the next High period of SCL, the I<sup>2</sup>C Controller sets the ACK bit in the I<sup>2</sup>C Status Register. Continue with <u>Step 12</u>.

If the slave does not acknowledge the first address byte, the I<sup>2</sup>C Controller sets the NCKI bit and clears the ACK bit in the I<sup>2</sup>C Status Register. Software responds to the Not Acknowledge interrupt by setting the stop and flush bits and clearing the TXI bit. The I<sup>2</sup>C Controller sends the stop condition on the bus and clears the stop and NCKI bits. The transaction is complete (ignore the following steps).

- 12. The I<sup>2</sup>C Controller loads the I<sup>2</sup>C Shift Register with the contents of the I<sup>2</sup>C Data Register.

- 13. The I<sup>2</sup>C Controller shifts the second address byte out the SDA signal. After the first bit has been sent, the transmit interrupt is asserted.

- 14. Software responds by writing a data byte to the  $I^2C$  Data Register.

- 15. The I<sup>2</sup>C Controller completes shifting the contents of the shift register on the SDA signal.

- 16. If the I<sup>2</sup>C slave sends an acknowledge by pulling the SDA signal Low during the next High period of SCL, the I<sup>2</sup>C Controller sets the ACK bit in the I<sup>2</sup>C Status Register. Continue with <u>Step 17</u>.

If the slave does not acknowledge the second address byte or one of the data bytes, the  $I^2C$  Controller sets the NCKI bit and clears the ACK bit in the  $I^2C$  Status Register. Software responds to the Not Acknowledge interrupt by setting the stop and flush bits and clearing the TXI bit. The  $I^2C$  Controller sends the stop condition on the bus and

For more information about bypassing the Flash Controller, refer to the <u>Third Party Flash</u> <u>Programming Support for Z8 Encore! MCUs Application Note (AN0117)</u>, which is available for download at <u>www.zilog.com</u>.

### Flash Controller Behavior in Debug Mode

The following changes in Flash Controller behavior occur when the Flash Controller is accessed using the On-Chip Debugger:

- The Flash Write Protect option bit is ignored

- The Flash Sector Protect Register is ignored for programming and erase operations

- Programming operations are not limited to the page selected in the Page Select Register

- Bits in the Flash Sector Protect Register can be written to one or zero

- The second write of the Page Select Register to unlock the Flash Controller is not necessary

- The Page Select Register can be written when the Flash Controller is unlocked

- The Mass Erase command is enabled through the Flash Control Register

**Caution:** For security reasons, the Flash Controller allows only a single page to be opened for write/erase operations. When writing multiple Flash pages, the Flash Controller must go through the unlock sequence again to select another page.

# **Flash Control Register Definitions**

This section defines the features of the following Flash Control registers.

Flash Control Register: see page 175

Flash Status Register: see page 177

Page Select Register: see page 177

Flash Sector Protect Register: see page 178

Flash Frequency High and Low Byte Registers: see page 179

### **Flash Control Register**

The Flash Control Register, shown in Table 93, unlocks the Flash Controller for programming and erase operations, or to select the Flash Sector Protect Register.

PRELIMINARY

#### Table 95. Page Select Register (FPS)

| Bit     | 7       | 6    | 5 | 4 | 3 | 2 | 1 | 0 |

|---------|---------|------|---|---|---|---|---|---|

| Field   | INFO_EN | PAGE |   |   |   |   |   |   |

| RESET   |         | 0    |   |   |   |   |   |   |

| R/W     |         | R/W  |   |   |   |   |   |   |

| Address |         | FF9H |   |   |   |   |   |   |

| Bit     | Description                                                                                                                               |

|---------|-------------------------------------------------------------------------------------------------------------------------------------------|

| [7]     | Information Area Enable                                                                                                                   |

| INFO_EN | 0 = Information Area is not selected.                                                                                                     |

|         | 1 = Information Area is selected. The Information area is mapped into the Flash memory<br>address space at addresses FE00H through FFFFH. |

| [6:0]   | Page Select                                                                                                                               |

| PAGE    | This 7-bit field selects the Flash memory page for programming and Page Erase operations.                                                 |

|         | Flash Memory Address[15:9] = PAGE[6:0].                                                                                                   |

### **Flash Sector Protect Register**

The Flash Sector Protect Register, shown in Table 96, protects Flash memory sectors from being programmed or erased from user code. The Flash Sector Protect Register shares its Register File address with the Page Select Register. The Flash Sector Protect Register can be accessed only after writing the Flash Control Register with 5EH.

User code can only write bits in this register to 1 (bits cannot be cleared to 0 by user code). To determine the appropriate Flash memory sector address range and sector number for your Z8F64xx Series product, please refer to <u>Table 91</u> on page 169.

| Bit                                                                                                      | 7     | 6     | 5     | 4     | 3     | 2     | 1     | 0     |

|----------------------------------------------------------------------------------------------------------|-------|-------|-------|-------|-------|-------|-------|-------|

| Field                                                                                                    | SECT7 | SECT6 | SECT5 | SECT4 | SECT3 | SECT2 | SECT1 | SECT0 |

| RESET                                                                                                    |       | 0     |       |       |       |       |       |       |

| R/W                                                                                                      |       | R/W*  |       |       |       |       |       |       |

| Address                                                                                                  | FF9H  |       |       |       |       |       |       |       |

| Note: *R/W = This register is accessible for read operations; it can be written to 1 only via user code. |       |       |       |       |       |       |       |       |

| Bit       | Description                                                                         |

|-----------|-------------------------------------------------------------------------------------|

| [7:0]     | Sector Protect**                                                                    |

| SECTn     | 0 = Sector <i>n</i> can be programmed or erased from user code.                     |

|           | 1 = Sector <i>n</i> is protected and cannot be programmed or erased from user code. |

| Note: **U | ser code can only write bits from 0 to 1.                                           |

197

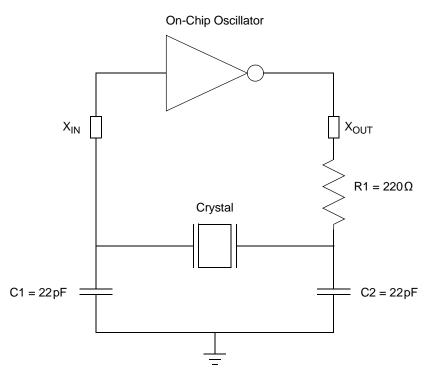

Figure 40. Recommended 20MHz Crystal Oscillator Configuration

| Parameter                           | Value       | Units | Comments |  |

|-------------------------------------|-------------|-------|----------|--|

| Frequency                           | 20          | MHz   |          |  |

| Resonance                           | Parallel    |       |          |  |

| Mode                                | Fundamental |       |          |  |

| Series Resistance (R <sub>S</sub> ) | 25          | W     | Maximum  |  |

| Load Capacitance (C <sub>L</sub> )  | 20          | pF    | Maximum  |  |

| Shunt Capacitance (C <sub>0</sub> ) | 7           | pF    | Maximum  |  |

| Drive Level                         | 1           | mW    | Maximum  |  |

Table 105. Recommended Crystal Oscillator Specifications (20MHz Operation)

# eZ8 CPU Instruction Classes

eZ8 CPU instructions can be divided functionally into the following groups:

- Arithmetic

- Bit Manipulation

- Block Transfer

- CPU Control

- Load

- Logical

- Program Control

- Rotate and Shift

Tables 128 through 135 contain the instructions belonging to each group and the number of operands required for each instruction. Some instructions appear in more than one table; these instructions can be considered to be a subset of more than one category. Within these tables, the source operand is identified as src, the destination operand is dst and a condition code is cc.

| Mnemonic | Operands | Instruction                                  |

|----------|----------|----------------------------------------------|

| ADC      | dst, src | Add with Carry                               |

| ADCX     | dst, src | Add with Carry using Extended Addressing     |

| ADD      | dst, src | Add                                          |

| ADDX     | dst, src | Add using Extended Addressing                |

| СР       | dst, src | Compare                                      |

| CPC      | dst, src | Compare with Carry                           |

| CPCX     | dst, src | Compare with Carry using Extended Addressing |

| CPX      | dst, src | Compare using Extended Addressing            |

| DA       | dst      | Decimal Adjust                               |

| DEC      | dst      | Decrement                                    |

| DECW     | dst      | Decrement Word                               |

| INC      | dst      | Increment                                    |

| INCW     | dst      | Increment Word                               |

Table 128. Arithmetic Instructions

| Mnemonic | Operands | Instruction                                   |

|----------|----------|-----------------------------------------------|

| MULT     | dst      | Multiply                                      |

| SBC      | dst, src | Subtract with Carry                           |

| SBCX     | dst, src | Subtract with Carry using Extended Addressing |

| SUB      | dst, src | Subtract                                      |

| SUBX     | dst, src | Subtract using Extended Addressing            |

#### Table 129. Bit Manipulation Instructions

| Mnemonic | Operands    | Instruction                                          |

|----------|-------------|------------------------------------------------------|

| BCLR     | bit, dst    | Bit Clear                                            |

| BIT      | p, bit, dst | Bit Set or Clear                                     |

| BSET     | bit, dst    | Bit Set                                              |

| BSWAP    | dst         | Bit Swap                                             |

| CCF      |             | Complement Carry Flag                                |

| RCF      | —           | Reset Carry Flag                                     |

| SCF      |             | Set Carry Flag                                       |

| ТСМ      | dst, src    | Test Complement Under Mask                           |

| ТСМХ     | dst, src    | Test Complement Under Mask using Extended Addressing |

| ТМ       | dst, src    | Test Under Mask                                      |

| ТМХ      | dst, src    | Test Under Mask using Extended Addressing            |

#### Table 130. Block Transfer Instructions

| Mnemonic | Operands | Instruction                                                              |

|----------|----------|--------------------------------------------------------------------------|

| LDCI     | dst, src | Load Constant to/from program memory and Auto-Incre-<br>ment addresses   |

| LDEI     | dst, src | Load External Data to/from Data Memory and Auto-Incre-<br>ment addresses |

| Mnemonic | Operands | Instruction                                         |

|----------|----------|-----------------------------------------------------|

| AND      | dst, src | Logical AND                                         |

| ANDX     | dst, src | Logical AND using Extended Addressing               |

| COM      | dst      | Complement                                          |

| OR       | dst, src | Logical OR                                          |

| ORX      | dst, src | Logical OR using Extended Addressing                |

| XOR      | dst, src | Logical Exclusive OR                                |

| XORX     | dst, src | Logical Exclusive OR using Extended Address-<br>ing |

#### Table 133. Logical Instructions

#### Table 134. Program Control Instructions

| Mnemonic | Operands        | Instruction                   |

|----------|-----------------|-------------------------------|

| BRK      |                 | On-Chip Debugger Break        |

| BTJ      | p, bit, src, DA | Bit Test and Jump             |

| BTJNZ    | bit, src, DA    | Bit Test and Jump if Non-Zero |

| BTJZ     | bit, src, DA    | Bit Test and Jump if Zero     |

| CALL     | dst             | Call Procedure                |

| DJNZ     | dst, src, RA    | Decrement and Jump Non-Zero   |

| IRET     | —               | Interrupt Return              |

| JP       | dst             | Jump                          |

| JP cc    | dst             | Jump Conditional              |

| JR       | DA              | Jump Relative                 |

| JR cc    | DA              | Jump Relative Conditional     |

| RET      | —               | Return                        |

| TRAP     | vector          | Software Trap                 |

| 245 |

|-----|

|-----|

| Abbreviation | Description                    | Abbreviation                                      | Description           |

|--------------|--------------------------------|---------------------------------------------------|-----------------------|

| IM           | Immediate data value           | r2, R2, Ir2, Irr2,<br>IR2, rr2, RR2,<br>IRR2, ER2 | Source address        |

| Ir           | Indirect working register      | RA                                                | Relative              |

| IR           | Indirect register              | rr                                                | Working register pair |

| Irr          | Indirect working register pair | RR                                                | Register pair         |

### Table 137. Op Code Map Abbreviations (Continued)

### Hex Address: FD7

#### Table 236. Port A–H Output Data Register (PxOUT)

| Bit     | 7     | 6                                              | 5     | 4     | 3     | 2     | 1     | 0     |  |  |

|---------|-------|------------------------------------------------|-------|-------|-------|-------|-------|-------|--|--|

| Field   | POUT7 | POUT6                                          | POUT5 | POUT4 | POUT3 | POUT2 | POUT1 | POUT0 |  |  |

| RESET   | 0     |                                                |       |       |       |       |       |       |  |  |

| R/W     |       | R/W                                            |       |       |       |       |       |       |  |  |

| Address |       | FD3H, FD7H, FDBH, FDFH, FE3H, FE7H, FEBH, FEFH |       |       |       |       |       |       |  |  |

### Hex Address: FD8

#### Table 237. Port A–H GPIO Address Registers (PxADDR)

| Bit     | 7   | 6          | 5           | 4         | 3           | 2          | 1   | 0 |  |  |

|---------|-----|------------|-------------|-----------|-------------|------------|-----|---|--|--|

| Field   |     | PADDR[7:0] |             |           |             |            |     |   |  |  |

| RESET   | 00H |            |             |           |             |            |     |   |  |  |

| R/W     |     | R/W        |             |           |             |            |     |   |  |  |

| Address |     | FD0        | H, FD4H, FI | D8H, FDCH | , FE0H, FE4 | H, FE8H, F | ECH |   |  |  |

### Hex Address: FD9

#### Table 238. Port A–H Control Registers (PxCTL)

| Bit     | 7    | 6   | 5           | 4          | 3         | 2          | 1   | 0 |  |

|---------|------|-----|-------------|------------|-----------|------------|-----|---|--|

| Field   | PCTL |     |             |            |           |            |     |   |  |

| RESET   | 00H  |     |             |            |           |            |     |   |  |

| R/W     | R/W  |     |             |            |           |            |     |   |  |

| Address |      | FD1 | H, FD5H, Fl | D9H, FDDH, | FE1H, FE5 | H, FE9H, F | EDH |   |  |

### Hex Address: FDA

#### Table 239. Port A-H Input Data Registers (PxIN)

| Bit     | 7    | 6    | 5           | 4          | 3           | 2          | 1    | 0    |  |

|---------|------|------|-------------|------------|-------------|------------|------|------|--|

| Field   | PIN7 | PIN6 | PIN5        | PIN4       | PIN3        | PIN2       | PIN1 | PIN0 |  |

| RESET   | X    |      |             |            |             |            |      |      |  |

| R/W     | R    |      |             |            |             |            |      |      |  |

| Address |      | FD2  | H, FD6H, FD | DAH, FDEH, | , FE2H, FE6 | H, FEAH, F | EEH  |      |  |

### Hex Address: FE7

#### Table 252. Port A–H Output Data Register (PxOUT)

| Bit     | 7     | 6                                              | 5     | 4     | 3     | 2     | 1     | 0     |  |

|---------|-------|------------------------------------------------|-------|-------|-------|-------|-------|-------|--|

| Field   | POUT7 | POUT6                                          | POUT5 | POUT4 | POUT3 | POUT2 | POUT1 | POUT0 |  |

| RESET   | 0     |                                                |       |       |       |       |       |       |  |

| R/W     | R/W   |                                                |       |       |       |       |       |       |  |

| Address |       | FD3H, FD7H, FDBH, FDFH, FE3H, FE7H, FEBH, FEFH |       |       |       |       |       |       |  |

### Hex Address: FE8

#### Table 253. Port A–H GPIO Address Registers (PxADDR)

| Bit     | 7 | 6          | 5          | 4         | 3           | 2          | 1   | 0 |  |  |

|---------|---|------------|------------|-----------|-------------|------------|-----|---|--|--|

| Field   |   | PADDR[7:0] |            |           |             |            |     |   |  |  |

| RESET   |   | 00H        |            |           |             |            |     |   |  |  |

| R/W     |   | R/W        |            |           |             |            |     |   |  |  |

| Address |   | FD0        | H, FD4H, F | D8H, FDCH | , FE0H, FE4 | H, FE8H, F | ECH |   |  |  |

### Hex Address: FE9

#### Table 254. Port A–H Control Registers (PxCTL)

| Bit     | 7 | 6    | 5           | 4          | 3           | 2          | 1   | 0 |  |  |

|---------|---|------|-------------|------------|-------------|------------|-----|---|--|--|

| Field   |   | PCTL |             |            |             |            |     |   |  |  |

| RESET   |   | 00H  |             |            |             |            |     |   |  |  |

| R/W     |   | R/W  |             |            |             |            |     |   |  |  |

| Address |   | FD1  | H, FD5H, Fl | D9H, FDDH, | , FE1H, FE5 | H, FE9H, F | EDH |   |  |  |

### Hex Address: FEA

#### Table 255. Port A–H Input Data Registers (PxIN)

| Bit     | 7    | 6                                              | 5    | 4    | 3    | 2    | 1    | 0    |  |  |

|---------|------|------------------------------------------------|------|------|------|------|------|------|--|--|

| Field   | PIN7 | PIN6                                           | PIN5 | PIN4 | PIN3 | PIN2 | PIN1 | PIN0 |  |  |

| RESET   |      | X                                              |      |      |      |      |      |      |  |  |

| R/W     |      | R                                              |      |      |      |      |      |      |  |  |

| Address |      | FD2H, FD6H, FDAH, FDEH, FE2H, FE6H, FEAH, FEEH |      |      |      |      |      |      |  |  |

counter 79 gated 79 one-shot 79 PWM 79 modes 79 MULT 232 multiply 232 multiprocessor mode, UART 94

### Ν

NOP (no operation) 233 not acknowledge interrupt 131 notation b 228 cc 228 DA 228 ER 228 IM 228 **IR 228** Ir 228 **IRR 228** Irr 228 p 228 R 228 r 228 RA 229 RR 229 rr 229 vector 229 X 229 notational shorthand 228

# 0

OCD architecture 184 auto-baud detector/generator 187 baud rate limits 187 block diagram 184 breakpoints 188 commands 189 control register 194 data format 187

DBG pin to RS-232 Interface 185 debug mode 186 debugger break 234 interface 185 serial errors 188 status register 195 timing 220 OCD commands execute instruction (12H) 193 read data memory (0DH) 193 read OCD control register (05H) 191 read OCD revision (00H) 190 read OCD status register (02H) 191 read program counter (07H) 191 read program memory (0BH) 192 read program memory CRC (0EH) 193 read register (09H) 192 step instruction (10H) 193 stuff instruction (11H) 193 write data memory (0CH) 192 write OCD control register (04H) 191 write program counter (06H) 191 write program memory (0AH) 192 write register (08H) 191 on-chip debugger 6 on-chip debugger (OCD) 184 on-chip debugger signals 17 on-chip oscillator 197 one-shot mode 79 opcode map abbreviations 245 cell description 245 first 247 second after 1FH 248 OR 234 ordering information 288 **ORX 234** oscillator signals 17

### Ρ

p 228 Packaging 287 part number description 293 298