#### Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

#### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

| Details                    |                                                           |

|----------------------------|-----------------------------------------------------------|

| Product Status             | Obsolete                                                  |

| Core Processor             | eZ8                                                       |

| Core Size                  | 8-Bit                                                     |

| Speed                      | 20MHz                                                     |

| Connectivity               | I <sup>2</sup> C, IrDA, SPI, UART/USART                   |

| Peripherals                | Brown-out Detect/Reset, DMA, POR, PWM, WDT                |

| Number of I/O              | 46                                                        |

| Program Memory Size        | 48KB (48K × 8)                                            |

| Program Memory Type        | FLASH                                                     |

| EEPROM Size                | -                                                         |

| RAM Size                   | 4K x 8                                                    |

| Voltage - Supply (Vcc/Vdd) | 3V ~ 3.6V                                                 |

| Data Converters            | A/D 12x10b                                                |

| Oscillator Type            | Internal                                                  |

| Operating Temperature      | 0°C ~ 70°C (TA)                                           |

| Mounting Type              | Surface Mount                                             |

| Package / Case             | 68-LCC (J-Lead)                                           |

| Supplier Device Package    | -                                                         |

| Purchase URL               | https://www.e-xfl.com/product-detail/zilog/z8f4822vs020sg |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

| Operation                                              | . 109 |

|--------------------------------------------------------|-------|

| Transmitting IrDA Data                                 | . 110 |

| Receiving IrDA Data                                    | . 111 |

| Infrared Encoder/Decoder Control Register Definitions  | . 112 |

| Serial Peripheral Interface                            | . 113 |

| Architecture                                           | . 113 |

| Operation                                              | . 115 |

| SPI Signals                                            | . 115 |

| SPI Clock Phase and Polarity Control                   | . 116 |

| Multimaster Operation                                  | . 118 |

| Slave Operation                                        | . 119 |

| Error Detection                                        | . 119 |

| SPI Interrupts                                         | . 120 |

| SPI Baud Rate Generator                                |       |

| SPI Control Register Definitions                       | . 121 |

| SPI Data Register                                      |       |

| SPI Control Register                                   |       |

| SPI Status Register                                    |       |

| SPI Mode Register                                      |       |

| SPI Diagnostic State Register                          |       |

| SPI Baud Rate High and Low Byte Registers              | . 126 |

| I <sup>2</sup> C Controller                            | . 128 |

| Architecture                                           | . 128 |

| Operation                                              | . 129 |

| SDA and SCL Signals                                    | . 130 |

| I <sup>2</sup> C Interrupts                            | . 130 |

| Software Control of I <sup>2</sup> C Transactions      | . 131 |

| Start and Stop Conditions                              | . 132 |

| Master Write and Read Transactions                     | . 132 |

| Address Only Transaction with a 7-bit Address          | . 133 |

| Write Transaction with a 7-Bit Address                 |       |

| Address Only Transaction with a 10-bit Address         | . 135 |

| Write Transaction with a 10-Bit Address                | . 136 |

| Read Transaction with a 7-Bit Address                  |       |

| Read Transaction with a 10-Bit Address                 |       |

| I <sup>2</sup> C Control Register Definitions          |       |

| I <sup>2</sup> C Data Register                         |       |

| I <sup>2</sup> C Status Register                       |       |

| $I^2C$ Control Register                                |       |

| I <sup>2</sup> C Baud Rate High and Low Byte Registers | . 145 |

#### vii

#### xi

# List of Figures

| Figure 1.  | Z8 Encore! XP F64xx Series Block Diagram                                   |

|------------|----------------------------------------------------------------------------|

| Figure 2.  | Z8 Encore! XP F64xx Series in 40-Pin Dual Inline Package (PDIP) 8          |

| Figure 3.  | Z8 Encore! XP F64xx Series in 44-Pin Plastic Leaded Chip Carrier (PLCC) 9  |

| Figure 4.  | Z8 Encore! XP F64xx Series in 44-Pin Low-Profile Quad Flat                 |

|            | Package (LQFP) 10                                                          |

| Figure 5.  | Z8 Encore! XP F64xx Series in 64-Pin Low-Profile Quad Flat                 |

| <b>F'</b>  | Package (LQFP)                                                             |

| Figure 6.  | Z8 Encore! XP F64xx Series in 68-Pin Plastic Leaded Chip<br>Carrier (PLCC) |

| Figure 7.  | Z8 Encore! XP F64xx Series in 80-Pin Quad Flat Package (QFP) 13            |

| Figure 8.  | Power-On Reset Operation                                                   |

| Figure 9.  | Voltage Brown-Out Reset Operation                                          |

| Figure 10. | GPIO Port Pin Block Diagram                                                |

| Figure 11. | Interrupt Controller Block Diagram                                         |

| Figure 12. | Timer Block Diagram                                                        |

| Figure 13. | UART Block Diagram                                                         |

| Figure 14. | UART Asynchronous Data Format without Parity                               |

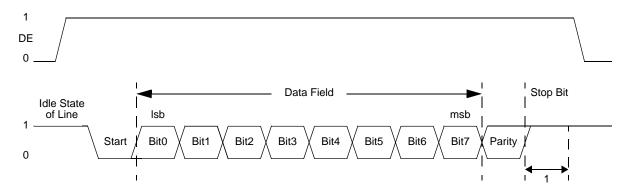

| Figure 15. | UART Asynchronous Data Format with Parity                                  |

| Figure 16. | UART Asynchronous MULTIPROCESSOR Mode Data Format                          |

| Figure 17. | UART Driver Enable Signal Timing (shown with 1 Stop Bit and Parity) . 95   |

| Figure 18. | UART Receiver Interrupt Service Routine Flow                               |

| Figure 19. | Infrared Data Communication System Block Diagram 109                       |

| Figure 20. | Infrared Data Transmission 110                                             |

| Figure 21. | Infrared Data Reception 111                                                |

| Figure 22. | SPI Configured as a Master in a Single-Master, Single-Slave System 113     |

| Figure 23. | SPI Configured as a Master in a Single-Master, Multiple-Slave System . 114 |

| Figure 24. | SPI Configured as a Slave 114                                              |

| Figure 25. | SPI Timing When PHASE is 0 117                                             |

| Figure 26. | SPI Timing When PHASE is 1 118                                             |

| Figure 27. | I <sup>2</sup> C Controller Block Diagram 129                              |

| Figure 28. | 7-Bit Address Only Transaction Format                                      |

| Figure 29. | 7-Bit Addressed Slave Data Transfer Format                                 |

| Figure 30. | 10-Bit Address Only Transaction Format                                     |

# Introduction

Zilog's Z8 Encore! XP F64xx Series MCU family of products are a line of Zilog microcontroller products based upon the 8-bit eZ8 CPU. The Z8 Encore! XP F64xx Series adds Flash memory to Zilog's extensive line of 8-bit microcontrollers. The Flash in-circuit programming capability allows for faster development time and program changes in the field. The new eZ8 CPU is upward-compatible with existing Z8 instructions. The rich-peripheral set of the Z8 Encore! XP F64xx Series makes it suitable for a variety of applications including motor control, security systems, home appliances, personal electronic devices, and sensors.

## Features

The features of Z8 Encore! XP F64xx Series include:

- 20MHz eZ8 CPU

- Up to 64KB Flash with in-circuit programming capability

- Up to 4KB register RAM

- 12-channel, 10-bit Analog-to-Digital Converter (ADC)

- Two full-duplex 9-bit UARTs with bus transceiver Driver Enable control

- Inter-integrated circuit (I<sup>2</sup>C)

- Serial Peripheral Interface (SPI)

- Two Infrared Data Association (IrDA)-compliant infrared encoder/decoders

- Up to four 16-bit timers with capture, compare and PWM capability

- Watchdog Timer (WDT) with internal RC oscillator

- Three-channel DMA

- Up to 60 input/output (I/O) pins

- 24 interrupts with configurable priority

- On-Chip Debugger

- Voltage Brown-Out (VBO) Protection

- Power-On Reset (POR)

- Operating voltage of 3.0V to 3.6V with 5V-tolerant inputs

- $0^{\circ}$ C to  $+70^{\circ}$ C,  $-40^{\circ}$ C to  $+105^{\circ}$ C, and  $-40^{\circ}$ C to  $+125^{\circ}$ C operating temperature ranges

| Signal<br>Mnemonic | I/O    | Description                                                                                                                                                                                                                                                                                                                          |

|--------------------|--------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Oscillators        |        |                                                                                                                                                                                                                                                                                                                                      |

| X <sub>IN</sub>    | I      | External Crystal Input. This is the input pin to the crystal oscillator. A crystal can be connected between it and the $X_{OUT}$ pin to form the oscillator. This signal is usable with external RC networks and an external clock driver.                                                                                           |

| X <sub>OUT</sub>   | 0      | External Crystal Output. This pin is the output of the crystal oscillator. A crystal can be connected between it and the $X_{IN}$ pin to form the oscillator. When the system clock is referred to in this manual, it refers to the frequency of the signal at this pin. This pin must be left unconnected when not using a crystal. |

| RC <sub>OUT</sub>  | 0      | RC Oscillator Output. This signal is the output of the RC oscillator. It is multi-<br>plexed with a general-purpose I/O pin. This signal must be left unconnected<br>when not using a crystal.                                                                                                                                       |

| On-Chip Deb        | ougger |                                                                                                                                                                                                                                                                                                                                      |

| DBG                | I/O    | Debug. This pin is the control and data input and output to and from the On-<br>Chip Debugger. This pin is open-drain.                                                                                                                                                                                                               |

|                    |        | <b>Caution:</b> For operation of the On-Chip Debugger, all power pins ( $V_{DD}$ and $AV_{DD}$ ) must be supplied with power and all ground pins ( $V_{SS}$ and $AV_{SS}$ ) must be properly grounded. The DBG pin is open-drain and must have an external pull-up resistor to ensure proper operation.                              |

| Reset              |        |                                                                                                                                                                                                                                                                                                                                      |

| RESET              | Ι      | RESET. Generates a Reset when asserted (driven Low).                                                                                                                                                                                                                                                                                 |

| Power Supp         | ly     |                                                                                                                                                                                                                                                                                                                                      |

| V <sub>DD</sub>    | I      | Power Supply.                                                                                                                                                                                                                                                                                                                        |

| AV <sub>DD</sub>   | Ι      | Analog Power Supply.                                                                                                                                                                                                                                                                                                                 |

| V <sub>SS</sub>    | I      | Ground.                                                                                                                                                                                                                                                                                                                              |

| AV <sub>SS</sub>   | Ι      | Analog Ground.                                                                                                                                                                                                                                                                                                                       |

### Table 3. Signal Descriptions (Continued)

## **Pin Characteristics**

Table 4 lists the characteristics for each pin available on the Z8 Encore! XP F64xx Series products and the data is sorted alphabetically by the pin symbol mnemonic.

| Symbol<br>Mnemonic | Direction | Reset<br>Direction | Active Low<br>or<br>Active High | Tri-State<br>Output  | Internal<br>Pull-Up or<br>Pull-Down | Schmitt-<br>Trigger<br>Input | Open-Drain<br>Output |

|--------------------|-----------|--------------------|---------------------------------|----------------------|-------------------------------------|------------------------------|----------------------|

| AV <sub>SS</sub>   | N/A       | N/A                | N/A                             | N/A                  | No                                  | No                           | N/A                  |

| AV <sub>DD</sub>   | N/A       | N/A                | N/A                             | N/A                  | No                                  | No                           | N/A                  |

| DBG                | I/O       | I                  | N/A                             | Yes                  | No                                  | Yes                          | Yes                  |

| V <sub>SS</sub>    | N/A       | N/A                | N/A                             | N/A                  | No                                  | No                           | N/A                  |

| PA[7:0]            | I/O       | I                  | N/A                             | Yes                  | No                                  | Yes                          | Yes,<br>programmable |

| PB[7:0]            | I/O       | I                  | N/A                             | Yes                  | No                                  | Yes                          | Yes,<br>programmable |

| PC[7:0]            | I/O       | I                  | N/A                             | Yes                  | No                                  | Yes                          | Yes,<br>programmable |

| PD[7:0]            | I/O       | I                  | N/A                             | Yes                  | No                                  | Yes                          | Yes,<br>programmable |

| PE7:0]             | I/O       | I                  | N/A                             | Yes                  | No                                  | Yes                          | Yes,<br>programmable |

| PF[7:0]            | I/O       | I                  | N/A                             | Yes                  | No                                  | Yes                          | Yes,<br>programmable |

| PG[7:0]            | I/O       | I                  | N/A                             | Yes                  | No                                  | Yes                          | Yes,<br>programmable |

| PH[3:0]            | I/O       | I                  | N/A                             | Yes                  | No                                  | Yes                          | Yes,<br>programmable |

| RESET              | I         | I                  | Low                             | N/A                  | Pull-up                             | Yes                          | N/A                  |

| V <sub>DD</sub>    | N/A       | N/A                | N/A                             | N/A                  | No                                  | No                           | N/A                  |

| X <sub>IN</sub>    | I         | I                  | N/A                             | N/A                  | No                                  | No                           | N/A                  |

| X <sub>OUT</sub>   | 0         | 0                  | N/A                             | Yes, in<br>STOP Mode | No                                  | No                           | No                   |

#### Table 4. Pin Characteristics of the Z8 Encore! XP F64xx Series

# **Address Space**

The eZ8 CPU can access three distinct address spaces:

- The Register File contains addresses for the general-purpose registers and the eZ8 CPU, peripheral and general-purpose I/O port control registers

- The program memory contains addresses for all memory locations having executable code and/or data

- The Data Memory consists of the addresses for all memory locations that hold only data

These three address spaces are covered briefly in the following sections. For more information about the eZ8 CPU and its address space, refer to the <u>eZ8 CPU Core User Manual</u> (<u>UM0128</u>), which is available for download on <u>www.zilog.com</u>.

## **Register File**

The Register File address space in the Z8 Encore! XP F64xx Series is 4KB (4096 bytes). The Register File is composed of two sections: control registers and general-purpose registers. When instructions are executed, registers are read from when defined as sources and written to when defined as destinations. The architecture of the eZ8 CPU allows all general-purpose registers to function as accumulators, address pointers, index registers, stack areas, or scratch pad memory.

The upper 256 bytes of the 4KB Register File address space are reserved for control of the eZ8 CPU, the on-chip peripherals, and the I/O ports. These registers are located at addresses from F00H to FFFH. Some of the addresses within the 256-byte control register section are reserved (unavailable). Reading from an reserved Register File addresses returns an undefined value. Writing to reserved Register File addresses is not recommended and can produce unpredictable results.

The on-chip RAM always begins at address 000H in the Register File address space. The Z8 Encore! XP F64xx Series provide 2KB to 4KB of on-chip RAM depending upon the device. Reading from Register File addresses outside the available RAM addresses (and not within the control register address space) returns an undefined value. Writing to these Register File addresses produces no effect. To determine the amount of RAM available for the specific Z8 Encore! XP F64xx Series device, see the <u>Part Selection Guide</u> section on page 2.

| Address ( | Hex) Register Description | Mnemonic | Reset (Hex) | Page      |

|-----------|---------------------------|----------|-------------|-----------|

| GPIO Port | A (continued)             |          |             |           |

| FD3       | Port A Output Data        | PAOUT    | 00          | <u>46</u> |

| GPIO Port | В                         |          |             |           |

| FD4       | Port B Address            | PBADDR   | 00          | <u>40</u> |

| FD5       | Port B Control            | PBCTL    | 00          | <u>41</u> |

| FD6       | Port B Input Data         | PBIN     | XX          | <u>46</u> |

| FD7       | Port B Output Data        | PBOUT    | 00          | <u>46</u> |

| GPIO Port | С                         |          |             |           |

| FD8       | Port C Address            | PCADDR   | 00          | <u>40</u> |

| FD9       | Port C Control            | PCCTL    | 00          | <u>41</u> |

| FDA       | Port C Input Data         | PCIN     | XX          | <u>46</u> |

| FDB       | Port C Output Data        | PCOUT    | 00          | <u>46</u> |

| GPIO Port | D                         |          |             |           |

| FDC       | Port D Address            | PDADDR   | 00          | <u>40</u> |

| FDD       | Port D Control            | PDCTL    | 00          | <u>41</u> |

| FDE       | Port D Input Data         | PDIN     | XX          | <u>46</u> |

| FDF       | Port D Output Data        | PDOUT    | 00          | <u>46</u> |

| GPIO Port | E                         |          |             |           |

| FE0       | Port E Address            | PEADDR   | 00          | <u>40</u> |

| FE1       | Port E Control            | PECTL    | 00          | <u>41</u> |

| FE2       | Port E Input Data         | PEIN     | XX          | <u>46</u> |

| FE3       | Port E Output Data        | PEOUT    | 00          | <u>46</u> |

| GPIO Port | F                         |          |             |           |

| FE4       | Port F Address            | PFADDR   | 00          | <u>40</u> |

| FE5       | Port F Control            | PFCTL    | 00          | <u>41</u> |

| FE6       | Port F Input Data         | PFIN     | XX          | <u>46</u> |

| FE7       | Port F Output Data        | PFOUT    | 00          | <u>46</u> |

| GPIO Port | G                         |          |             |           |

| FE8       | Port G Address            | PGADDR   | 00          | <u>40</u> |

| FE9       | Port G Control            | PGCTL    | 00          | <u>41</u> |

| FEA       | Port G Input Data         | PGIN     | XX          | <u>46</u> |

| FEB       | Port G Output Data        | PGOUT    | 00          | <u>46</u> |

### Table 7. Z8 Encore! XP F64xx Series Register File Address Map (Continued)

Note: XX = Undefined.

## **Port A–H Control Registers**

The Port A–H Control registers, shown in Table 15, set the GPIO port operation. The value in the corresponding Port A–H Address Register determines the control subregisters accessible using the Port A–H Control Register.

#### Table 15. Port A–H Control Registers (PxCTL)

| Bit     | 7    | 6   | 5           | 4         | 3           | 2          | 1   | 0 |

|---------|------|-----|-------------|-----------|-------------|------------|-----|---|

| Field   | PCTL |     |             |           |             |            |     |   |

| RESET   | 00H  |     |             |           |             |            |     |   |

| R/W     | R/W  |     |             |           |             |            |     |   |

| Address |      | FD1 | H, FD5H, FI | D9H, FDDH | , FE1H, FE5 | H, FE9H, F | EDH |   |

| Bit   | Description                                                                                           |

|-------|-------------------------------------------------------------------------------------------------------|

| [7:0] | <b>Port Control</b>                                                                                   |

| PCTL  | The Port Control Register provides access to all subregisters that configure the GPIO Port operation. |

#### Port A–H Data Direction Subregisters

The Port A–H Data Direction Subregister, shown in Table 16, is accessed through the Port A–H Control Register by writing 01H to the Port A–H Address Register.

| Table 16. | Port A–H | Data Direction | Subregisters |

|-----------|----------|----------------|--------------|

|-----------|----------|----------------|--------------|

| Bit          | 7                                                                                                           | 6   | 5   | 4   | 3   | 2   | 1   | 0   |

|--------------|-------------------------------------------------------------------------------------------------------------|-----|-----|-----|-----|-----|-----|-----|

| Field        | DD7                                                                                                         | DD6 | DD5 | DD4 | DD3 | DD2 | DD1 | DD0 |

| RESET        |                                                                                                             | 1   |     |     |     |     |     |     |

| R/W          | R/W                                                                                                         |     |     |     |     |     |     |     |

| Address      | See note.                                                                                                   |     |     |     |     |     |     |     |

| Note: If a ( | e. If a 01H exists in the Port A-H Address Register, it is accessible through the Port A-H Control Register |     |     |     |     |     |     |     |

| 0 |

|---|

|   |

| BIt   | Description                                                                                                                                                                                                                                                                                                                                                                                             |

|-------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| [7:0] | Data Direction                                                                                                                                                                                                                                                                                                                                                                                          |

| DDx   | <ul> <li>These bits control the direction of the associated port pin. Port Alternate Function operation overrides the Data Direction Register setting.</li> <li>0 = Output. Data in the Port A–H Output Data Register is driven onto the port pin.</li> <li>1 = Input. The port pin is sampled and the value written into the Port A–H Input Data Register. The output driver is tri-stated.</li> </ul> |

| Note: | x indicates register bits in the range [7:0].                                                                                                                                                                                                                                                                                                                                                           |

D:4

Decerintien

#### Port A–H Alternate Function Subregisters

The Port A–H Alternate Function Subregister, shown in Table 17, is accessed through the Port A–H Control Register by writing 02H to the Port A–H Address Register. The Port A–H Alternate Function subregisters select the alternate functions for the selected pins. To determine the alternate function associated with each port pin, see the <u>GPIO Alternate</u> <u>Functions</u> section on page 37.

**Caution:** Do not enable alternate function for GPIO port pins which do not have an associated alternate function. Failure to follow this guideline may result in unpredictable operation.

| Bit                                                                                                             | 7         | 6   | 5   | 4   | 3   | 2   | 1   | 0   |  |  |  |

|-----------------------------------------------------------------------------------------------------------------|-----------|-----|-----|-----|-----|-----|-----|-----|--|--|--|

| Field                                                                                                           | AF7       | AF6 | AF5 | AF4 | AF3 | AF2 | AF1 | AF0 |  |  |  |

| RESET                                                                                                           |           | 0   |     |     |     |     |     |     |  |  |  |

| R/W                                                                                                             |           | R/W |     |     |     |     |     |     |  |  |  |

| Address                                                                                                         | See note. |     |     |     |     |     |     |     |  |  |  |

| Note: If a 02H exists in the Port A–H Address Register, it is accessible through the Port A–H Control Register. |           |     |     |     |     |     |     |     |  |  |  |

#### Table 17. Port A–H Alternate Function Subregisters

### Bit Description

#### [7:0] **Port Alternate Function Enabled**

- AFx 0 = The port pin is in NORMAL Mode and the DDx bit in the Port A–H Data Direction Subregister determines the direction of the pin.

- 1 = The alternate function is selected. Port pin operation is controlled by the alternate function.

Note: x indicates register bits in the range [7:0].

The third scheme is enabled by setting MPMD[1:0] to 11b and by writing the UART's address into the UART Address Compare Register. This mode is identical to the second scheme, except that there are no interrupts on address bytes. The first data byte of each frame is still accompanied by a NEWFRM assertion.

## **External Driver Enable**

The UART provides a Driver Enable (DE) signal for off-chip bus transceivers. This feature reduces the software overhead associated with using a GPIO pin to control the transceiver when communicating on a multitransceiver bus, such as RS-485.

Driver Enable is an active High signal that envelopes the entire transmitted data frame including parity and stop bits as displayed in Figure 17. The Driver Enable signal asserts when a byte is written to the UART Transmit Data Register. The Driver Enable signal asserts at least one UART bit period and no greater than two UART bit periods before the start bit is transmitted. This timing allows a setup time to enable the transceiver. The Driver Enable signal deasserts one system clock period after the last stop bit is transmitted. This one system clock delay allows both time for data to clear the transceiver before disabling it, as well as the ability to determine if another character follows the current character. In the event of back to back characters (new data must be written to the Transmit Data Register before the previous character is completely transmitted) the DE signal is not deasserted between characters. The DEPOL bit in the UART Control Register 1 sets the polarity of the Driver Enable signal.

The Driver Enable-to-start-bit set-up time is calculated as:

$$\left(\frac{1}{\text{Baud Rate (Hz)}}\right) \le \text{DE to Start Bit Setup Time (s)} \le \left(\frac{2}{\text{Baud Rate (Hz)}}\right)$$

## **UART Control 0 and Control 1 Registers**

The UART Control 0 and Control 1 Registers, shown in Tables 57 and 58, configure the properties of the UART's transmit and receive operations. The UART Control registers must not been written while the UART is enabled.

#### Table 57. UART Control 0 Register (UxCTL0)

| Bit         | 7                                                                                                                                                                                                                                                                                                                                                                                            | 6                                                                                                                                                                                                                                                                                                                      | 5    | 4   | 3    | 2              | 1             | 0    |  |  |  |

|-------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------|-----|------|----------------|---------------|------|--|--|--|

| Field       | TEN                                                                                                                                                                                                                                                                                                                                                                                          | REN                                                                                                                                                                                                                                                                                                                    | CTSE | PEN | PSEL | SBRK           | STOP          | LBEN |  |  |  |

| RESET       | 0                                                                                                                                                                                                                                                                                                                                                                                            |                                                                                                                                                                                                                                                                                                                        |      |     |      |                |               |      |  |  |  |

| R/W         |                                                                                                                                                                                                                                                                                                                                                                                              |                                                                                                                                                                                                                                                                                                                        |      | R/  | W    |                |               |      |  |  |  |

| Address     |                                                                                                                                                                                                                                                                                                                                                                                              | F42H and F4AH                                                                                                                                                                                                                                                                                                          |      |     |      |                |               |      |  |  |  |

| Bit         | Descriptio                                                                                                                                                                                                                                                                                                                                                                                   | Description                                                                                                                                                                                                                                                                                                            |      |     |      |                |               |      |  |  |  |

| [7]<br>TEN  | This bit ena<br>and the CT<br>0 = Transm                                                                                                                                                                                                                                                                                                                                                     | <b>Transmit Enable</b><br>This bit enables or disables the transmitter. The enable is also controlled by the $\overline{\text{CTS}}$ signal and the CTSE bit. If the $\overline{\text{CTS}}$ signal is low and the CTSE bit is 1, the transmitter is enabled.<br>0 = Transmitter disabled.<br>1 = Transmitter enabled. |      |     |      |                |               |      |  |  |  |

| [6]<br>REN  | This bit ena<br>0 = Receive                                                                                                                                                                                                                                                                                                                                                                  | <b>Receive Enable</b><br>This bit enables or disables the receiver.<br>0 = Receiver disabled.<br>1 = Receiver enabled.                                                                                                                                                                                                 |      |     |      |                |               |      |  |  |  |

| [5]<br>CTSE |                                                                                                                                                                                                                                                                                                                                                                                              | l <u>e</u><br>S signal has<br>RT recogniz                                                                                                                                                                                                                                                                              |      |     |      | ntrol from the | e transmitter | :    |  |  |  |

| [4]<br>PEN  | <ul> <li>Parity Enable</li> <li>This bit enables or disables parity. Even or odd is determined by the PSEL bit. It is overridden by the MPEN bit.</li> <li>0 = Parity is disabled.</li> <li>1 = The transmitter sends data with an additional parity bit and the receiver receives an additional parity bit.</li> </ul>                                                                      |                                                                                                                                                                                                                                                                                                                        |      |     |      |                |               |      |  |  |  |

| [3]<br>PSEL | Parity Select<br>0 = Even parity is transmitted and expected on all received data.<br>1 = Odd parity is transmitted and expected on all received data.                                                                                                                                                                                                                                       |                                                                                                                                                                                                                                                                                                                        |      |     |      |                |               |      |  |  |  |

| [2]<br>SBRK | <ul> <li>1 = Odd parity is transmitted and expected on all received data.</li> <li>Send Break</li> <li>This bit pauses or breaks data transmission. Sending a break interrupts any transmission in progress, so ensure that the transmitter has finished sending data before setting this bit.</li> <li>0 = No break is sent.</li> <li>1 = The output of the transmitter is zero.</li> </ul> |                                                                                                                                                                                                                                                                                                                        |      |     |      |                |               |      |  |  |  |

## **UART Address Compare Register**

The UART Address Compare Register, shown in Table 59, stores the multinode network address of the UART. When the MPMD[1] bit of UART Control Register 0 is set, all incoming address bytes are compared to the value stored in the Address Compare Register. Receive interrupts and RDA assertions only occur in the event of a match.

| Bit     | 7               | 6 | 5 | 4 | 3 | 2 | 1 | 0 |  |  |  |  |

|---------|-----------------|---|---|---|---|---|---|---|--|--|--|--|

| Field   | COMP_ADDR       |   |   |   |   |   |   |   |  |  |  |  |

| RESET   | 0               |   |   |   |   |   |   |   |  |  |  |  |

| R/W     | R/W             |   |   |   |   |   |   |   |  |  |  |  |

| Address | F45H and F4DH   |   |   |   |   |   |   |   |  |  |  |  |

| Bit     | Description     |   |   |   |   |   |   |   |  |  |  |  |

| [7:0]   | Compare Address |   |   |   |   |   |   |   |  |  |  |  |

## **UART Baud Rate High and Low Byte Registers**

COMP ADDR This 8-bit value is compared to the incoming address bytes.

The UART Baud Rate High and Low Byte registers, shown in Tables 60 and 61, combine to create a 16-bit baud rate divisor value (BRG[15:0]) that sets the data transmission rate (baud rate) of the UART. To configure the Baud Rate Generator as a timer with interrupt on time-out, complete the following procedure:

- 1. Disable the UART by clearing the REN and TEN bits in the UART Control 0 Register to 0.

- 2. Load the appropriate 16-bit count value into the UART Baud Rate High and Low Byte registers.

- 3. Enable the Baud Rate Generator timer function and associated interrupt by setting the BRGCTL bit in the UART Control 1 Register to 1.

When configured as a general-purpose timer, the UART BRG interrupt interval is calculated using the following equation:

UART BRG Interrupt Interval(s) = System Clock Period (s)  $\times$  BRG[15:0]

| Bit           | Description (Continued)                                                                                                                                                                                                                                                                                                                                                                        |

|---------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| [1]<br>FLUSH  | <b>Flush Data</b><br>Setting this bit to 1 clears the $I^2C$ Data Register and sets the TDRE bit to 1. This bit allows flushing of the $I^2C$ Data Register when a Not Acknowledge interrupt is received after the data has been sent to the $I^2C$ Data Register. Reading this bit always returns 0.                                                                                          |

| [0]<br>FILTEN | <ul> <li>I<sup>2</sup>C Signal Filter Enable</li> <li>This bit enables low-pass digital filters on the SDA and SCL input signals. These filters reject any input pulse with periods less than a full system clock cycle. The filters introduce a 3-system clock cycle latency on the inputs.</li> <li>1 = low-pass filters are enabled.</li> <li>0 = low-pass filters are disabled.</li> </ul> |

## I<sup>2</sup>C Baud Rate High and Low Byte Registers

The I<sup>2</sup>C Baud Rate High and Low Byte registers, shown in Tables 74 and 75, combine to form a 16-bit reload value, BRG[15:0], for the I<sup>2</sup>C Baud Rate Generator.

When the  $I^2C$  is disabled, the Baud Rate Generator can function as a basic 16-bit timer with interrupt on time-out. To configure the Baud Rate Generator as a timer with interrupt on time-out, complete the following procedure:

- 1. Disable the  $I^2C$  by clearing the IEN bit in the  $I^2C$  Control Register to 0.

- 2. Load the appropriate 16-bit count value into the I<sup>2</sup>C Baud Rate High and Low Byte registers.

- 3. Enable the Baud Rate Generator timer function and associated interrupt by setting the BIRQ bit in the I<sup>2</sup>C Control Register to 1.

When configured as a general purpose timer, the interrupt interval is calculated using the following equation:

Interrupt Interval (s) = System Clock Period (s)  $\times$  BRG[15:0]

| 148 |  |

|-----|--|

|-----|--|

| Bit                | Description (0                                                          | Continued)                                                           |  |  |  |  |  |

|--------------------|-------------------------------------------------------------------------|----------------------------------------------------------------------|--|--|--|--|--|

| [4:0]<br>TXRXSTATE | Internal State<br>Value of the internal I <sup>2</sup> C state machine. |                                                                      |  |  |  |  |  |

|                    | TXRXSTATE                                                               | State Description                                                    |  |  |  |  |  |

| [4:0]              | 0_000                                                                   | Idle State.                                                          |  |  |  |  |  |

| TXRXSTATE          | 0_0001                                                                  | Start State.                                                         |  |  |  |  |  |

| (continued)        | 0_0010                                                                  | Send/Receive data bit 7.                                             |  |  |  |  |  |

|                    | 0_0011                                                                  | Send/Receive data bit 6.                                             |  |  |  |  |  |

|                    | 0_0100                                                                  | Send/Receive data bit 5.                                             |  |  |  |  |  |

|                    | 0_0101                                                                  | Send/Receive data bit 4.                                             |  |  |  |  |  |

|                    | 0_0110                                                                  | Send/Receive data bit 3.                                             |  |  |  |  |  |

|                    | 0_0111                                                                  | Send/Receive data bit 2.                                             |  |  |  |  |  |

|                    | 0_1000                                                                  | Send/Receive data bit 1.                                             |  |  |  |  |  |

|                    | 0_1001                                                                  | Send/Receive data bit 0.                                             |  |  |  |  |  |

|                    | 0_1010                                                                  | Data Acknowledge State.                                              |  |  |  |  |  |

|                    | 0_1011                                                                  | Second half of data Acknowledge State used only for not acknowledge. |  |  |  |  |  |

|                    | 0_1100                                                                  | First part of stop state.                                            |  |  |  |  |  |

|                    | 0_1101                                                                  | Second part of stop state.                                           |  |  |  |  |  |

|                    | 0_1110                                                                  | 10-bit addressing: Acknowledge State for 2nd address byte            |  |  |  |  |  |

|                    |                                                                         | 7-bit addressing: Address Acknowledge State.                         |  |  |  |  |  |

|                    | 0_1111                                                                  | 10-bit address: Bit 0 (Least significant bit) of 2nd address byte    |  |  |  |  |  |

|                    |                                                                         | 7-bit address: Bit 0 (Least significant bit) (R/W) of address byte.  |  |  |  |  |  |

|                    | 1_0000                                                                  | 10-bit addressing: Bit 7 (Most significant bit) of 1st address byte. |  |  |  |  |  |

|                    | 1_0001                                                                  | 10-bit addressing: Bit 6 of 1st address byte.                        |  |  |  |  |  |

|                    | 1_0010                                                                  | 10-bit addressing: Bit 5 of 1st address byte.                        |  |  |  |  |  |

|                    | 1_0011                                                                  | 10-bit addressing: Bit 4 of 1st address byte.                        |  |  |  |  |  |

|                    | 1_0100                                                                  | 10-bit addressing: Bit 3 of 1st address byte.                        |  |  |  |  |  |

|                    | 1_0101                                                                  | 10-bit addressing: Bit 2 of 1st address byte.                        |  |  |  |  |  |

|                    | 1_0110                                                                  | 10-bit addressing: Bit 1 of 1st address byte.                        |  |  |  |  |  |

|                    | 1_0111                                                                  | 10-bit addressing: Bit 0 (R/W) of 1st address byte.                  |  |  |  |  |  |

|                    | 1_1000                                                                  | 10-bit addressing: Acknowledge state for 1st address byte.           |  |  |  |  |  |

|                    | 1_1001                                                                  | 10-bit addressing: Bit 7 of 2nd address byte                         |  |  |  |  |  |

|                    |                                                                         | 7-bit addressing: Bit 7 of address byte.                             |  |  |  |  |  |

|                    | 1_1010                                                                  | 10-bit addressing: Bit 6 of 2nd address byte                         |  |  |  |  |  |

|                    |                                                                         | 7-bit addressing: Bit 6 of address byte.                             |  |  |  |  |  |

|                    | 1_1011                                                                  | 10-bit addressing: Bit 5 of 2nd address byte                         |  |  |  |  |  |

|                    |                                                                         | 7-bit addressing: Bit 5 of address byte.                             |  |  |  |  |  |

|                    | 1_1100                                                                  | 10-bit addressing: Bit 4 of 2nd address byte                         |  |  |  |  |  |

|                    | _                                                                       | 7-bit addressing: Bit 4 of address byte.                             |  |  |  |  |  |

|                    | 1_1101                                                                  | 10-bit addressing: Bit 3 of 2nd address byte                         |  |  |  |  |  |

|                    | —                                                                       | 7-bit addressing: Bit 3 of address byte.                             |  |  |  |  |  |

|                    | 1_1110                                                                  | 10-bit addressing: Bit 2 of 2nd address byte                         |  |  |  |  |  |

|                    |                                                                         | 7-bit addressing: Bit 2 of address byte.                             |  |  |  |  |  |

|                    | 1_1111                                                                  | 10-bit addressing: Bit 1 of 2nd address byte                         |  |  |  |  |  |

|                    |                                                                         | 7-bit addressing: Bit 1 of address byte.                             |  |  |  |  |  |

# Flash Memory

The products in the Z8 Encore! XP F64xx Series feature up to 64KB (65,536 bytes) of non-volatile Flash memory with read/write/erase capability. The Flash memory can be programmed and erased in-circuit by either user code or through the On-Chip Debugger.

The Flash memory array is arranged in 512 byte per page. The 512 byte page is the minimum Flash block size that can be erased. The Flash memory is also divided into 8 sectors which can be protected from programming and erase operations on a per sector basis.

Table 90 describes the Flash memory configuration for each device in the Z8 Encore! XP F64xx Series. Table 91 lists the sector address ranges. Figure 35 displays the Flash memory arrangement.

| Part<br>Number | Flash Size   | Number of<br>Pages | Flash Memory<br>Addresses | Sector Size | Number of<br>Sectors | Pages per<br>Sector |

|----------------|--------------|--------------------|---------------------------|-------------|----------------------|---------------------|

| Z8F162x        | 16K (16,384) | 32                 | 0000H–3FFFH               | 2K (2048)   | 8                    | 4                   |

| Z8F242x        | 24K (24,576) | 48                 | 0000H–5FFFH               | 4K (4096)   | 6                    | 8                   |

| Z8F322x        | 32K (32,768) | 64                 | 0000H-7FFFH               | 4K (4096)   | 8                    | 8                   |

| Z8F482x        | 48K (49,152) | 96                 | 0000H-BFFFH               | 8K (8192)   | 6                    | 16                  |

| Z8F642x        | 64K (65,536) | 128                | 0000H-FFFFH               | 8K (8192)   | 8                    | 16                  |

#### Table 90. Flash Memory Configurations

#### Table 91. Flash Memory Sector Addresses

| Sector | Flash Sector Address Ranges |             |             |             |             |  |  |  |  |  |

|--------|-----------------------------|-------------|-------------|-------------|-------------|--|--|--|--|--|

| Number | Z8F162x                     | Z8F242x     | Z8F322x     | Z8F482x     | Z8F642x     |  |  |  |  |  |

| 0      | 0000H-07FFH                 | 0000H-0FFFH | 0000H-0FFFH | 0000H-1FFFH | 0000H–1FFFH |  |  |  |  |  |

| 1      | 0800H–0FFFH                 | 1000H–1FFFH | 1000H–1FFFH | 2000H-3FFFH | 2000H-3FFFH |  |  |  |  |  |

| 2      | 1000H–17FFH                 | 2000H–2FFFH | 2000H–2FFFH | 4000H–5FFFH | 4000H–5FFFH |  |  |  |  |  |

| 3      | 1800H–1FFFH                 | 3000H–3FFFH | 3000H–3FFFH | 6000H–7FFFH | 6000H–7FFFH |  |  |  |  |  |

| 4      | 2000H–27FFH                 | 4000H–4FFFH | 4000H–4FFFH | 8000H–9FFFH | 8000H–9FFFH |  |  |  |  |  |

| 5      | 2800H–2FFFH                 | 5000H–5FFFH | 5000H–5FFFH | A000H-BFFFH | A000H–BFFFH |  |  |  |  |  |

| 6      | 3000H–37FFH                 | N/A         | 6000H–6FFFH | N/A         | C000H-DFFFH |  |  |  |  |  |

| 7      | 3800H–3FFFH                 | N/A         | 7000H–7FFFH | N/A         | E000H–FFFFH |  |  |  |  |  |

#### Table 95. Page Select Register (FPS)

| Bit     | 7       | 6           | 5 | 4 | 3 | 2 | 1 | 0 |  |  |

|---------|---------|-------------|---|---|---|---|---|---|--|--|

| Field   | INFO_EN | NFO_EN PAGE |   |   |   |   |   |   |  |  |

| RESET   |         | 0           |   |   |   |   |   |   |  |  |

| R/W     |         | R/W         |   |   |   |   |   |   |  |  |

| Address |         | FF9H        |   |   |   |   |   |   |  |  |

| Bit     | Description                                                                                                                               |

|---------|-------------------------------------------------------------------------------------------------------------------------------------------|

| [7]     | Information Area Enable                                                                                                                   |

| INFO_EN | 0 = Information Area is not selected.                                                                                                     |

|         | 1 = Information Area is selected. The Information area is mapped into the Flash memory<br>address space at addresses FE00H through FFFFH. |

| [6:0]   | Page Select                                                                                                                               |

| PAGE    | This 7-bit field selects the Flash memory page for programming and Page Erase operations.                                                 |

|         | Flash Memory Address[15:9] = PAGE[6:0].                                                                                                   |

## **Flash Sector Protect Register**

The Flash Sector Protect Register, shown in Table 96, protects Flash memory sectors from being programmed or erased from user code. The Flash Sector Protect Register shares its Register File address with the Page Select Register. The Flash Sector Protect Register can be accessed only after writing the Flash Control Register with 5EH.

User code can only write bits in this register to 1 (bits cannot be cleared to 0 by user code). To determine the appropriate Flash memory sector address range and sector number for your Z8F64xx Series product, please refer to <u>Table 91</u> on page 169.

| Bit                                                                                                      | 7     | 6     | 5     | 4     | 3     | 2     | 1     | 0     |  |  |  |

|----------------------------------------------------------------------------------------------------------|-------|-------|-------|-------|-------|-------|-------|-------|--|--|--|

| Field                                                                                                    | SECT7 | SECT6 | SECT5 | SECT4 | SECT3 | SECT2 | SECT1 | SECT0 |  |  |  |

| RESET                                                                                                    |       | 0     |       |       |       |       |       |       |  |  |  |

| R/W                                                                                                      |       | R/W*  |       |       |       |       |       |       |  |  |  |

| Address                                                                                                  |       | FF9H  |       |       |       |       |       |       |  |  |  |

| Note: *R/W = This register is accessible for read operations; it can be written to 1 only via user code. |       |       |       |       |       |       |       |       |  |  |  |

| Bit           | Description                                                                         |

|---------------|-------------------------------------------------------------------------------------|

| [7:0]         | Sector Protect**                                                                    |

| SECT <i>n</i> | 0 = Sector <i>n</i> can be programmed or erased from user code.                     |

|               | 1 = Sector <i>n</i> is protected and cannot be programmed or erased from user code. |

| Note: **U     | lser code can only write bits from 0 to 1.                                          |

## Flash Frequency High and Low Byte Registers

The Flash Frequency High and Low Byte registers, shown in Tables 97 and 98, combine to form a 16-bit value, FFREQ, to control timing for Flash program and erase operations. The 16-bit Flash Frequency registers must be written with the system clock frequency in kHz for Program and Erase operations. Calculate the Flash Frequency value using the following equation:

$FFREQ[15:0] = \{FFREQH[7:0], FFREQL[7:0]\} = \frac{System Clock Frequency}{1000}$

**Caution:** Flash programming and erasure is not supported for system clock frequencies below 20kHz, above 20MHz, or outside of the valid operating frequency range for the device. The Flash Frequency High and Low Byte registers must be loaded with the correct value to ensure proper program and erase times.

### Table 97. Flash Frequency High Byte Register (FFREQH)

| Bit     | 7    | 6      | 5 | 4 | 3 | 2 | 1 | 0 |  |  |

|---------|------|--------|---|---|---|---|---|---|--|--|

| Field   |      | FFREQH |   |   |   |   |   |   |  |  |

| RESET   | 0    |        |   |   |   |   |   |   |  |  |

| R/W     |      | R/W    |   |   |   |   |   |   |  |  |

| Address | FFAH |        |   |   |   |   |   |   |  |  |

### Table 98. Flash Frequency Low Byte Register (FFREQL)

| Bit     | 7    | 6 | 5 | 4   | 3      | 2 | 1 | 0 |  |  |  |  |

|---------|------|---|---|-----|--------|---|---|---|--|--|--|--|

| Field   |      |   |   | FFR | FFREQL |   |   |   |  |  |  |  |

| RESET   | 0    |   |   |     |        |   |   |   |  |  |  |  |

| R/W     | R/W  |   |   |     |        |   |   |   |  |  |  |  |

| Address | FFBH |   |   |     |        |   |   |   |  |  |  |  |

#### Bit Description

| [7:0]   | Flash Frequency High and Low Bytes                                                     |

|---------|----------------------------------------------------------------------------------------|

| FFREQH, | , These 2 bytes, {FFREQH[7:0], FFREQL[7:0]}, contain the 16-bit Flash Frequency value. |

| FFREQL  |                                                                                        |

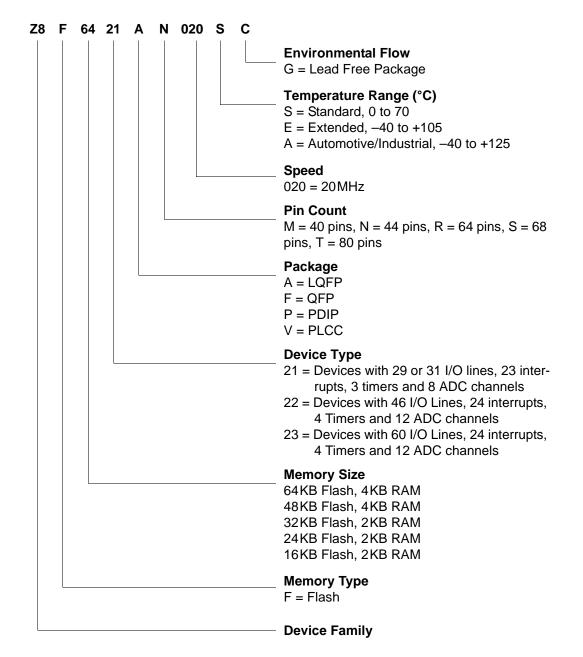

# **Ordering Information**

Order your F64xx Series products from Zilog using the part numbers shown in Table 271. For more information about ordering, please consult your local Zilog sales office. The <u>Sales Location page</u> on the Zilog website lists all regional offices.

| Table 271. 20 Elicore: XI T 04XX Genes Ordening Matrix |              |        |           |            |                     |                     |                  |     |                 |                     |

|--------------------------------------------------------|--------------|--------|-----------|------------|---------------------|---------------------|------------------|-----|-----------------|---------------------|

| Part Number                                            | Flash        | RAM    | I/O Lines | Interrupts | 16-Bit Timers w/PWM | 10-Bit A/D Channels | I <sup>2</sup> C | SPI | UARTs with IrDA | Description         |

| Z8F642x with 64KB FI                                   |              | -      | to-Di     | igital     | Со                  | nvert               | er               |     |                 |                     |

| Standard Temperature                                   | e: 0°C to 70 | °C     |           |            |                     |                     |                  |     |                 |                     |

| Z8F6421PM020SG                                         | 64 KB        | 2KB    | 29        | 23         | 3                   | 8                   | 1                | 1   | 2               | PDIP 40-pin package |

| Z8F6421AN020SG                                         | 64KB         | 4KB    | 31        | 23         | 3                   | 8                   | 1                | 1   | 2               | LQFP 44-pin package |

| Z8F6421VN020SG                                         | 64 KB        | 4KB    | 31        | 23         | 3                   | 8                   | 1                | 1   | 2               | PLCC 44-pin package |

| Z8F6422AR020SG                                         | 64 KB        | 4KB    | 46        | 24         | 4                   | 12                  | 1                | 1   | 2               | LQFP 64-pin package |

| Z8F6422VS020SG                                         | 64 KB        | 4KB    | 46        | 24         | 4                   | 12                  | 1                | 1   | 2               | PLCC 68-pin package |

| Z8F6423FT020SG                                         | 64KB         | 4KB    | 60        | 24         | 4                   | 12                  | 1                | 1   | 2               | QFP 80-pin package  |

| Extended Temperatur                                    | e: –40°C to  | +105°C |           |            |                     |                     |                  |     |                 |                     |

| Z8F6421PM020EG                                         | 64 KB        | 2KB    | 29        | 23         | 3                   | 8                   | 1                | 1   | 2               | PDIP 40-pin package |

| Z8F6421AN020EG                                         | 64KB         | 4KB    | 31        | 23         | 3                   | 8                   | 1                | 1   | 2               | LQFP 44-pin package |

| Z8F6421VN020EG                                         | 64 K B       | 4KB    | 31        | 23         | 3                   | 8                   | 1                | 1   | 2               | PLCC 44-pin package |

| Z8F6422AR020EG                                         | 64 KB        | 4KB    | 46        | 24         | 4                   | 12                  | 1                | 1   | 2               | LQFP 64-pin package |

| Z8F6422VS020EG                                         | 64 KB        | 4KB    | 46        | 24         | 4                   | 12                  | 1                | 1   | 2               | PLCC 68-pin package |

| Z8F6423FT020EG                                         | 64KB         | 4KB    | 60        | 24         | 4                   | 12                  | 1                | 1   | 2               | QFP 80-pin package  |

| Automotive/Industrial Temperature: –40°C to +125°C     |              |        |           |            |                     |                     |                  |     |                 |                     |

| Z8F6421PM020AG                                         | 64KB         | 2KB    | 29        | 23         | 3                   | 8                   | 1                | 1   | 2               | PDIP 40-pin package |

| Z8F6421AN020AG                                         | 64KB         | 4KB    | 31        | 23         | 3                   | 8                   | 1                | 1   | 2               | LQFP 44-pin package |

| Z8F6421VN020AG                                         | 64KB         | 4KB    | 31        | 23         | 3                   | 8                   | 1                | 1   | 2               | PLCC 44-pin package |

| Z8F6422AR020AG                                         | 64KB         | 4KB    | 46        | 24         | 4                   | 12                  | 1                | 1   | 2               | LQFP 64-pin package |

| Z8F6422VS020AG                                         | 64KB         | 4KB    | 46        | 24         | 4                   | 12                  | 1                | 1   | 2               | PLCC 68-pin package |

| Z8F6423FT020AG                                         | 64KB         | 4KB    | 60        | 24         | 4                   | 12                  | 1                | 1   | 2               | QFP 80-pin package  |

#### Table 271. Z8 Encore! XP F64xx Series Ordering Matrix

## **Part Number Suffix Designations**

Zilog part numbers consist of a number of component. In the following example, part number Z8F6421AN020SG is an 8-bit Flash MCU with 4KB of program memory in a 44-pin LQFP package, operating with a maximum 20MHz external clock frequency over a 0°C to +70°C temperature range and built using environmentally friendly (lead-free) solder.

counter 79 gated 79 one-shot 79 PWM 79 modes 79 MULT 232 multiply 232 multiprocessor mode, UART 94

## Ν

NOP (no operation) 233 not acknowledge interrupt 131 notation b 228 cc 228 DA 228 ER 228 IM 228 **IR 228** Ir 228 **IRR 228** Irr 228 p 228 R 228 r 228 RA 229 RR 229 rr 229 vector 229 X 229 notational shorthand 228

# 0

OCD architecture 184 auto-baud detector/generator 187 baud rate limits 187 block diagram 184 breakpoints 188 commands 189 control register 194 data format 187

DBG pin to RS-232 Interface 185 debug mode 186 debugger break 234 interface 185 serial errors 188 status register 195 timing 220 OCD commands execute instruction (12H) 193 read data memory (0DH) 193 read OCD control register (05H) 191 read OCD revision (00H) 190 read OCD status register (02H) 191 read program counter (07H) 191 read program memory (0BH) 192 read program memory CRC (0EH) 193 read register (09H) 192 step instruction (10H) 193 stuff instruction (11H) 193 write data memory (0CH) 192 write OCD control register (04H) 191 write program counter (06H) 191 write program memory (0AH) 192 write register (08H) 191 on-chip debugger 6 on-chip debugger (OCD) 184 on-chip debugger signals 17 on-chip oscillator 197 one-shot mode 79 opcode map abbreviations 245 cell description 245 first 247 second after 1FH 248 OR 234 ordering information 288 **ORX 234** oscillator signals 17

## Ρ

p 228 Packaging 287 part number description 293 298